# EFFECTS OF PARALLEL PROGRAMMING DESIGN PATTERNS ON THE PERFORMANCE OF MULTI-CORE PROCESSOR BASED REAL TIME EMBEDDED SYSTEMS

# A THESIS SUBMITTED TO THE GRADUATE SCHOOL OF NATURAL AND APPLIED SCIENCES OF MIDDLE EAST TECHNICAL UNIVERSITY

ΒY

BURAK KEKEÇ

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE IN ELECTRICAL AND ELECTRONICS ENGINEERING

JUNE 2010

Approval of the thesis:

## EFFECTS OF PARALLEL PROGRAMMING DESIGN PATTERNS ON THE PERFORMANCE OF MULTI-CORE PROCESSOR BASED REAL TIME EMBEDDED SYSTEMS

submitted by **Burak KEKEÇ** in partial fulfillment of the requirements for the degree of Master of Science in Electrical and Electronics Engineering Department, Middle East Technical University by,

| Prof. Dr. Canan ÖZGEN<br>Dean, Graduate School of <b>Nat</b> i     | ural and Applied Science | 2S         |

|--------------------------------------------------------------------|--------------------------|------------|

| Prof. Dr. İsmet ERKMEN<br>Head of Department, <b>Electrica</b>     | l and Electronics Engine | ering      |

| Prof. Dr. Semih BİLGEN<br>Supervisor, <b>Electrical and Elec</b>   | tronics Engineering Dept | t., METU   |

| Examining Committee Membe                                          | ers:                     |            |

| Prof. Dr. Hasan GÜRAN<br>Electrical and Electronics Engir          | neering Dept., METU      |            |

| Prof. Dr. Semih BİLGEN<br>Electrical and Electronics Engir         | neering Dept., METU      |            |

| Assoc. Prof. Dr. Cüneyt BAZLAI<br>Electrical and Electronics Engir | •                        |            |

| Asst. Prof. Dr. Şenan Ece SCHN<br>Electrical and Electronics Engir |                          |            |

| Şafak ŞEKER<br>Lead Design Engineer, ASELSAI                       | N INC.                   |            |

|                                                                    | Date:                    | 30.06.2010 |

I hereby declare that all information in this document has been obtained and presented in accordance with academic rules and ethical conduct. I also declare that, as required by these rules and conduct, I have fully cited and referenced all material and results that are not original to this work.

Name, Last name : Burak KEKEÇ

Signature :

# ABSTRACT

## EFFECTS OF PARALLEL PROGRAMMING DESIGN PATTERNS ON THE PERFORMANCE OF MULTI-CORE PROCESSOR BASED REAL TIME EMBEDDED SYSTEMS

KEKEÇ, Burak M.Sc., Department of Electrical and Electronics Engineering Supervisor: Prof. Dr. Semih BİLGEN

June 2010, 114 pages

Increasing usage of multi-core processors has led to their use in real time embedded systems (RTES). This entails high performance requirements which may not be easily met when software development follows traditional techniques long used for single processor systems. In this study, parallel programming design patterns especially developed and reported in the literature will be used to improve RTES implementations on multi-core systems. Specific performance parameters will be selected for assessment, and performance of traditionally developed software will be compared with that of software developed using parallel programming patterns.

**Key Words:** Multicore programming, real-time embedded systems, design patterns

# PARALEL PROGRAMLAMA TASARIM ÖRÜNTÜLERİNİN ÇOK İŞLEMCİLİ GERÇEK ZAMANLI GÖMÜLÜ SİSTEM PERFORMANSI ÜZERİNDEKİ ETKİSİ

KEKEÇ, Burak Yüksek Lisans, Elektrik ve Elektronik Mühendisliği Bölümü Tez Yöneticisi: Prof. Dr. Semih BİLGEN

Haziran 2010, 114 sayfa

Çok çekirdekli işlemcilerin yaygınlaşması, bunların gerçek zamanlı gömülü sistemlerde (GZGS) de kullanılmasına yol açmıştır. Ancak bunun gerektirdiği yüksek performans, tek işlemcili sistemler için kullanılan geleneksel yöntemlerle geliştirilmiş yazılımlarla sağlanamayabilmektedir. Bu çalışmada, GZGS performansı ölçütleri seçilecek ve özel olarak bu amaca yönelik olarak tanımlanmış ve literatürde tartışılmış bulunan paralel programlama tasarım örüntüleri kullanılarak elde edilen performans ile geleneksel yöntemlerle geliştirilmiş yazılımlarısı karşılaştırılacaktır.

Anahtar Kelimeler: Çok çekirdekli işlemci programlama, gerçek zamanlı gömülü sistemler, tasarım örüntüleri

To Melik Gazi...

# ACKNOWLEDGMENTS

I would like to thank Prof. Dr. Semih BİLGEN for his valuable supervision, support and guidance throughout the thesis work.

I am grateful to Şafak ŞEKER and my other colleagues for their supports throughout the thesis work. I am also grateful to Aselsan Electronics Industries Inc. for encouragements and resources that are supported for this thesis.

I would like to thank to TUBİTAK for scholarship throughout this study.

Finally, I owe my deepest gratitude to my parents and my brothers for their encouragements and to my dear who is my everything.

# TABLE OF CONTENTS

| ABSTRACT                                                   | iv     |

|------------------------------------------------------------|--------|

| ÖZ                                                         | v      |

| ACKNOWLEDGMENTS                                            | vii    |

| TABLE OF CONTENTS                                          | . viii |

| LIST OF ABBREVIATIONS                                      | xi     |

| LIST OF TABLES                                             | xii    |

| LIST OF FIGURES                                            | . xiii |

| INTRODUCTION                                               | 1      |

| BACKGROUND                                                 | 4      |

| 2.1 Multicore Processors                                   | 4      |

| 2.2 Parallel Computing and Symmetric Multiprocessing (SMP) | 5      |

| 2.3 Multicore Programming Challenges and Approaches        | 6      |

| 2.4 Patterns for Parallel Programming Design Approach      | . 10   |

| 2.4.1 Design Patterns & Pattern Language:                  | . 10   |

| 2.4.2 Design Patterns in Real-Time Systems:                | . 11   |

| 2.4.3 Parallel Programming Patterns                        | . 11   |

| 2.4.3.1 Parallel Programming Pattern Language              | . 12   |

| 2.4.3.2 Our Pattern Language (OPL)                         | . 18   |

| 2.5 Real Time Performance Metrics                          | . 20   |

| IMPLEMENTATION                                             | . 24   |

| 3.1 VxWorks OS & VxWorks 6.6 with SMP                      | . 24   |

| 3.2 Wind River WorkBench 3.0                               | . 28   |

| 3.2.1 VxWorks Image Project:                               | . 30   |

| 3.2.2 VxWorks Downloadable Kernel Module Project:          | . 30   |

| 3.2.3 Debugger                                             | . 31   |

| 3.2.4 Additional Tools                                     | . 31   |

| 3.2.4.1 System Viewer                                      | . 31   |

| 3.2.4.2 VxWorks Simulator                                  | . 32   |

| 3.2.4.3 Function Tracer                                    | . 33   |

| 3.3 Experiment Setup                                       | . 34   |

| 3.3.1 Host Machine                                         | . 34   |

| rget Machine                         | 36                                                             |

|--------------------------------------|----------------------------------------------------------------|

| Wind River SBC8641D:                 | 37                                                             |

| Freescale MPC8641D                   | 37                                                             |

| roject                               | 38                                                             |

| t Management Software:               | 38                                                             |

| sign of Parallel Test Software:      | 45                                                             |

| Finding Concurrency Phase            | 45                                                             |

| Algorithm Structure Phase            | 55                                                             |

| Supporting Structure Phase           | 58                                                             |

| Implementation Mechanism Phase       | 60                                                             |

|                                      | 73                                                             |

| ethod:                               | 73                                                             |

| efine"s in Software:                 | 74                                                             |

| xiliary Testing Program:             | 75                                                             |

| Set:                                 | 77                                                             |

| ases:                                | 78                                                             |

| st Case 1: Timeline Measurement Test | 78                                                             |

| est:                                 | 78                                                             |

| Method:                              | 78                                                             |

| on Method:                           | 78                                                             |

| tions:                               | 79                                                             |

|                                      | 81                                                             |

| st Case 2: Consistency Test          | 85                                                             |

| test:                                | 85                                                             |

| Method:                              | 85                                                             |

| on Method:                           | 86                                                             |

| tions:                               | 86                                                             |

|                                      | 86                                                             |

| st Case 3: Computation Time Test     | 86                                                             |

| est:                                 | 86                                                             |

| Method:                              | 87                                                             |

| on Method:                           | 87                                                             |

| tions:                               | 87                                                             |

|                                      | 88                                                             |

| st Case 4: Time Constraint Test      | 103                                                            |

| test:                                | 103                                                            |

| Method:                              | 103                                                            |

|                                      | Wind River SBC8641D:         Freescale MPC8641D         roject |

| 104 |

|-----|

| 104 |

| 104 |

| 106 |

| 109 |

| 113 |

|     |

# LIST OF ABBREVIATIONS

- **OS:** Operating System

- SMP: Symmetric Multiprocessing

- SISD: Single instruction single data

- **SIMD:** Single instruction multiple data

- MISD: Multiple instruction single data

- MIMD: Multiple instruction multiple data

- RT: Real-Time

- **UE:** Unit of execution

- **PE:** Processing Element

# LIST OF TABLES

| Table   | 2.1:   | Relationship    | between     | Supporting      | Structures  | patterns | and |

|---------|--------|-----------------|-------------|-----------------|-------------|----------|-----|

| Algorit | hm St  | ructure pattern | s [1]       |                 |             |          | 15  |

| Table   | 2.2:   | Relationship    | between     | Supporting      | Structures  | patterns | and |

| progra  | mming  | g environments  | s [1]       |                 |             |          | 16  |

| Table 4 | 4.1: C | omputation tim  | ie change i | in usec for the | e same inpu | t        | 104 |

| Table / | 4.1: T | est Input Set   |             |                 |             |          | 113 |

# LIST OF FIGURES

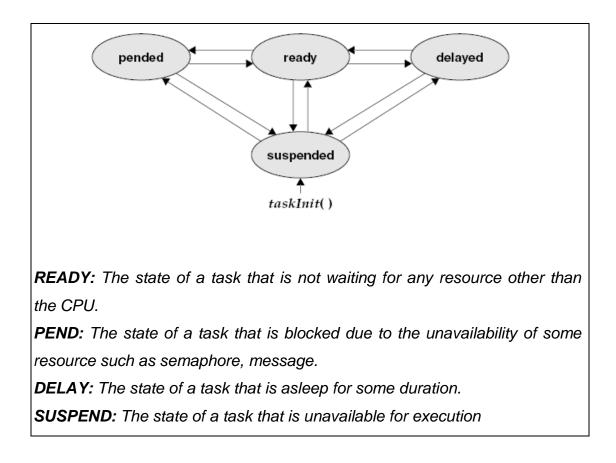

| Figure 3.1: VxWorks Tasks25                                                      |

|----------------------------------------------------------------------------------|

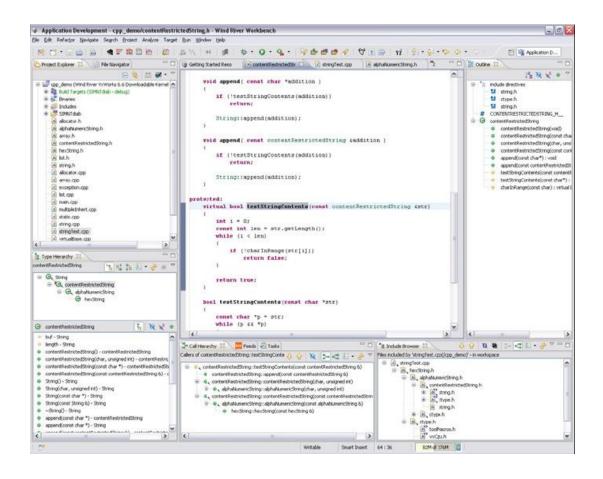

| Figure 3.2: User Interface of Wind River Workbench                               |

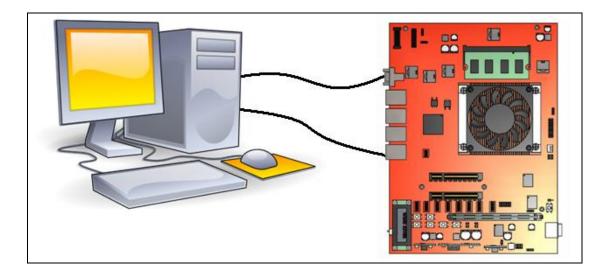

| Figure 3.3: Experiment Setup                                                     |

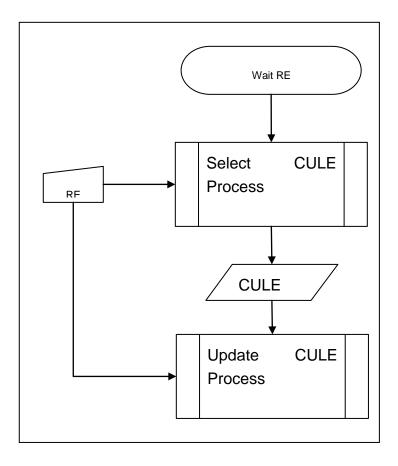

| Figure 3.4 Flow Chart of the List Management Algorithm                           |

| Figure 3.5: Flow Chart of Update Decision Algorithm                              |

| Figure 3.6: Flow Chart of Updating algorithm                                     |

| Figure 3.7: Task group ordering for Design Approach 150                          |

| Figure 3.8: Class Diagram Of List Management Problem                             |

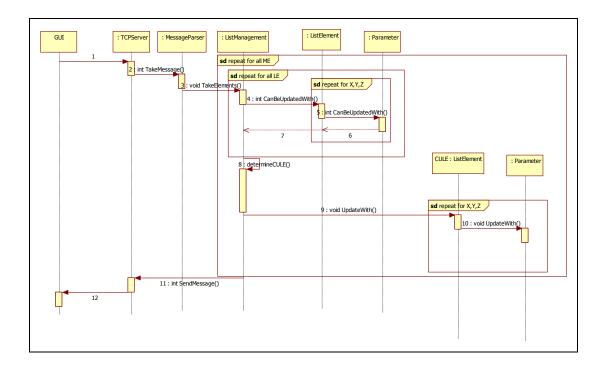

| Figure 3.9: Message Sequence Diagram of the List Management Software 64          |

| Figure 4.1 Auxiliary testing Program76                                           |

| Figure 4.2: Timing for 3 <sup>rd</sup> input arrival for Serial Design           |

| Figure 4.3: Timing for 3rd input arrival for Parallel Design 1                   |

| Figure 4.4: Timing for 3rd input arrival for Parallel Design 2                   |

| Figure 4.5: Timing for 3rd input arrival for Parallel Design 3                   |

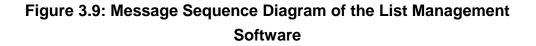

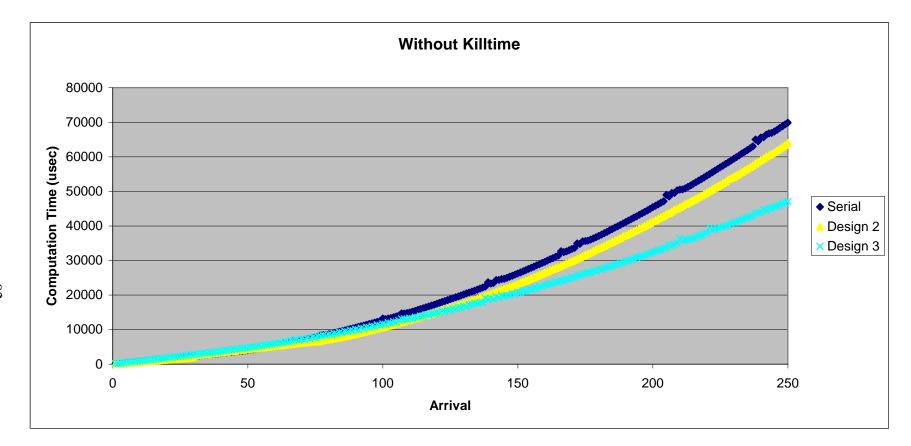

| Figure 4.6: Arrival - computation time graph for 1 to 250 elements of input      |

| file for all design when there is no kill time                                   |

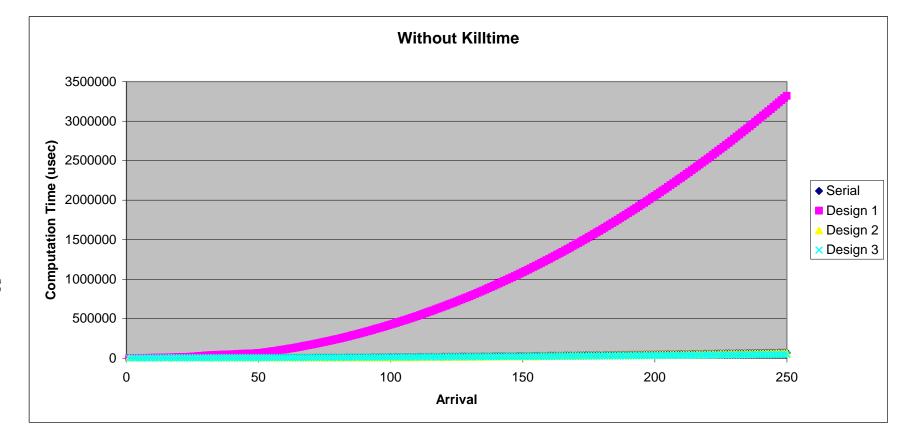

| Figure 4.7: Arrival - computation time graph for 1 to 100 elements of input file |

| for all design when there is no kill time90                                      |

| Figure 4.8: Arrival - computation time graph for 1 to 250 elements of input file |

| for all design except Design 1 when there is no kill time92                      |

| Figure 4.9: Arrival - computation time graph for 1 to 100 elements of input file |

| for all design except Design 1 when there is no kill time93                      |

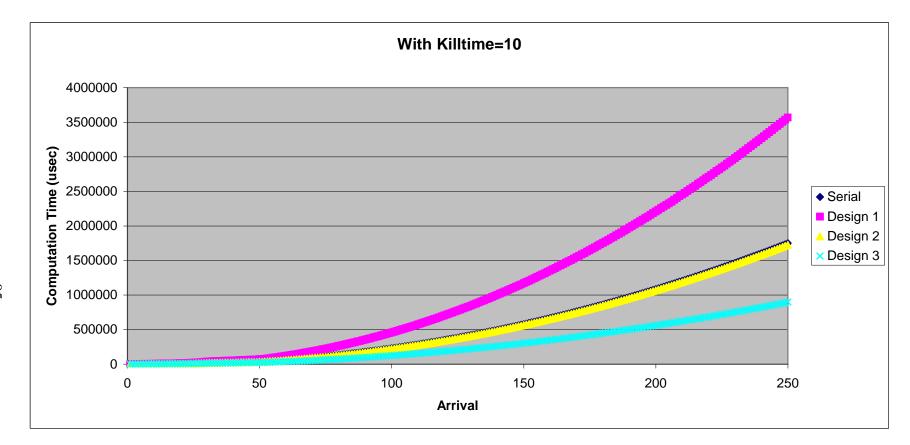

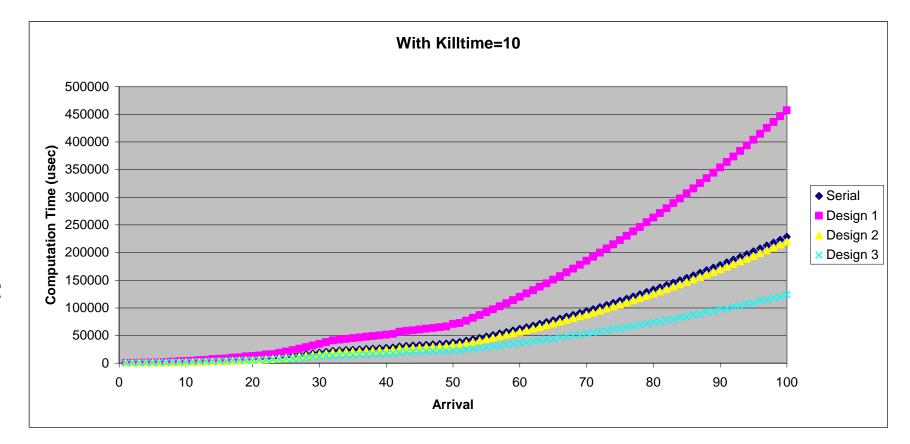

| Figure 4.10: Arrival - computation time graph for 1 to 250 elements of input     |

| file when killtime is set to 10 usec                                             |

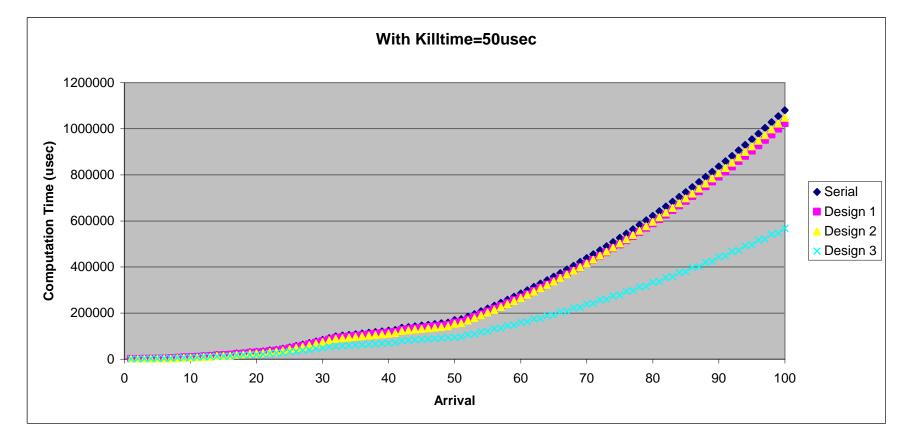

| Figure 4.11: Arrival - computation time graph for 1 to 50 elements of input file |

| when killtime is set to 10 usec96                                                |

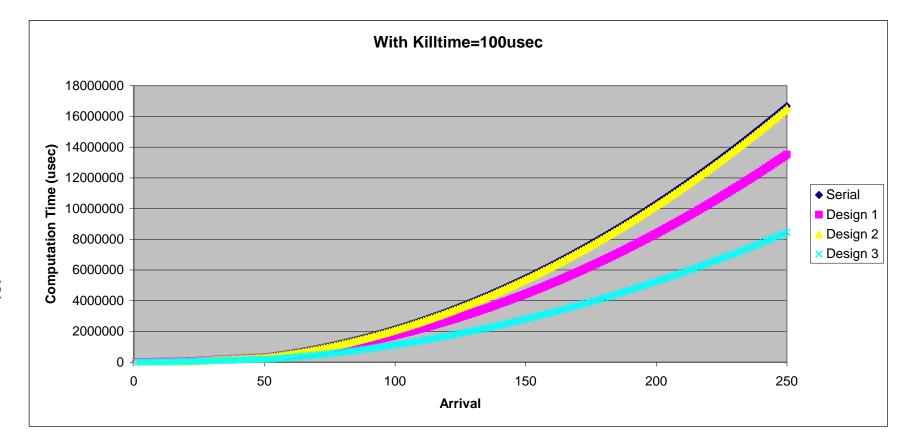

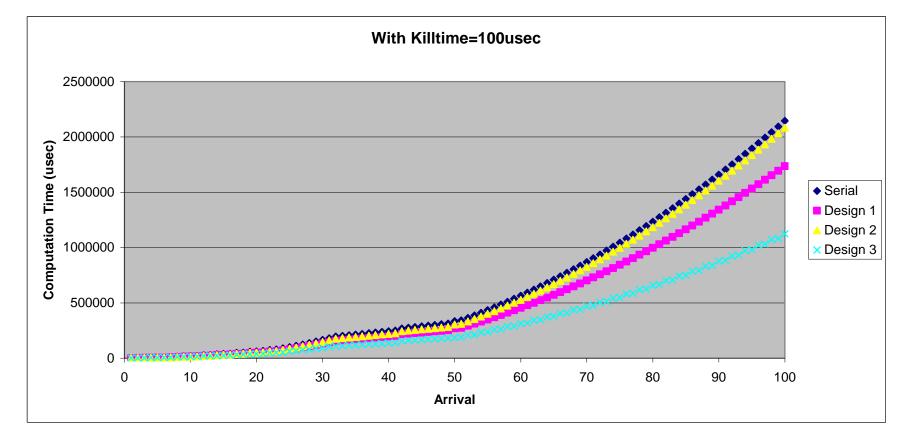

| Figure 4.12: Arrival - computation time graph for 1 to 250 elements of input     |

| file when killtime is set to 10 usec                                             |

| Figure 4.13: Arrival - computation time graph for 1 to 50 elements of input file |

| when killtime is set to 10 usec                                                  |

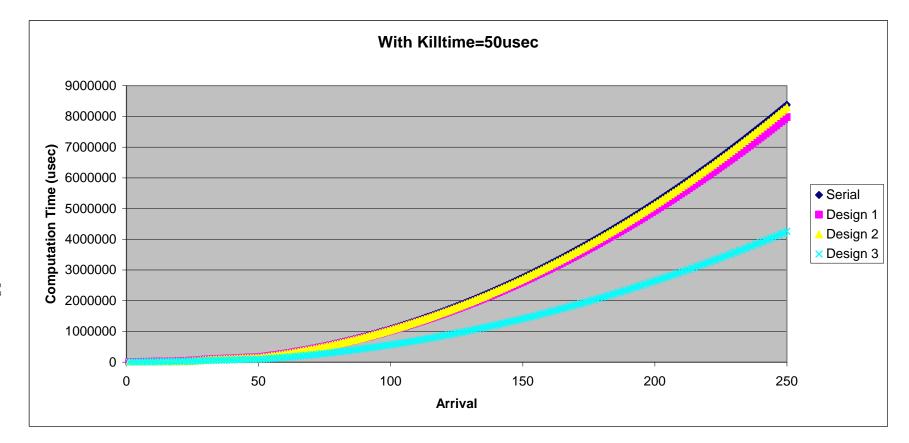

| Figure 4.14: Arrival - computation time graph for 1 to 250 elements of input     |

| file when killtime is set to 100 usec.                                |               |

|-----------------------------------------------------------------------|---------------|

| Figure 4.15: Arrival - computation time graph for 1 to 50 elements of | of input file |

| when killtime is set to 100 usec.                                     |               |

# **CHAPTER 1**

# INTRODUCTION

Development in science and the technology has triggered many improvements in the computation area. The problems to be solved by computers become bigger and more complex. This requires faster computers. To meet this requirement multicore processors have been introduced. Multicore processors are composed of two or more independent processing elements with fast interface between the processing elements.

While multicore processors are new in computing technology, actually, parallel computing and multithreading concepts are not new. However with multicore processors these concepts have become more important.

To obtain better performance from multicore processors, software developers must respond to multicore processors solutions of chip developers by developing proper software with parallel programming effort. However to perform this, software developers face lots of challenges such as parallelizing tasks, data synchronization, load balancing, avoiding race conditions etc.

Parallel programming design patterns or pattern languages are helpful solutions to overcome these challenges.

The aim of this thesis study is to evaluate the effectiveness of a specific parallel programming design pattern language proposed by Mattson et.al. [1],

via a case study that involves a real time list management algorithm implementation.

In the scope of the present study, the list management algorithm which has been implemented as serial by traditional coding style, is re-implemented using the parallel programming design pattern language in [1] to exploit the concurrency provided by the multicore processors. Parallel implementation is made using three different design approaches which include different patterns from that pattern language.

After implementations of the serial and three different parallel designs, each parallel implementation will be compared with the serial implementation and other parallel implementations with respect to the real time performance metrics. Then this comparison results will be evaluated and some inferences are derived about parallel programming.

The remaining chapters of the thesis are organized as follows:

In Chapter 2 background information about multicore processors, parallel computing and symmetric multiprocessing, multicore programming and its challenges, pattern, pattern language concepts and parallel programming patterns is presented. Moreover information about real rime software and real time performance metrics are also introduced.

In Chapter 3 experimental work in the thesis is explained. The software development environment, hardware components and connections between them in the experiment setup, and the software and tools are introduced. Also the list management algorithm that is implemented in the thesis, implementation details of serial and three parallel software design tested, parallel programming patterns and their usage in the software are also presented.

In Chapter 4 test method to compare the one serial and three parallel implementations with respect to the real time performance metrics is explained. Different test cases to evaluate the software with respect to the different real time performance metrics are explained in details. Moreover, some graphs and tables are formed with the output data obtained from the described test cases.

In Chapter 5 the one serial and three parallel different implementations of the list management algorithm are summarized and compared with respect to the real time performance metrics. Also suitability of the selected patterns for the parallel designed software is discussed and some inferences about the pattern selection for the different versions of the algorithm are stated. After a review of achievements and shortcomings of the study, suggestions for future work are also presented in this concluding chapter.

# **CHAPTER 2**

# BACKGROUND

## 2.1 Multicore Processors

Traditional methods to increase performance of a processor were using more transistors on chips and increasing clock rate. However, this solution has reached its limit. Since they cause high heat dissipation and too much power consumption, chip developers have changed their methods. The new trend is building chips with multiple cores instead of single core. This new method is more power efficient and supplies better performance. [2] Thus, nowadays multicore processors are preferred instead of single core processors.

Actually, multicore processor technology is an important solution for many computing problems because some present problems and possible future problems in human life require better performance. Multicore processors will be indispensable for all areas of computing that require high performance such as management of big databases, high quality PC animations and games, high quality digital media, internet, data security etc. [3] As a result usage of multicore processors has been increasing gradually with time.

# 2.2 Parallel Computing and Symmetric Multiprocessing (SMP)

Sometimes single processor can not be practicable to solve some problems that require high performance. Using more than one processor to work concurrently is the solution for these problems. Processors can be connected together in different ways. There are different kinds of parallel computing architectures. These architectures can be roughly classified with Flynn's taxonomy which classifies parallel computing architectures with regard to memory and instruction coherency. There are four types of structure in Flynn's taxonomy: SISD, SIMD, MISD, MIMD. [4] In SISD systems single instructions access the single data and no parallelism can be exploited, in SIMD systems single instruction access different data simultaneously, in MISD systems multiple instructions process on the same data and in MIMD systems multiple instructions process on different data. [5]

In parallel computing architectures processing elements can be on the same machine or on distributed machines. If processing elements are on the same machine, this kind of computing is named as multiprocessing. Multicore processors are a kind of multiprocessing architecture with a difference that parallelism is achieved not by processors but by processor cores. For multicore processors, more than one core exists in a single processor. That is, multicore processors are chip-level multiprocessing systems.

Symmetric Multiprocessing (SMP) is one of various parallel processing approaches in which more than one identical processor can access a single shared memory via a common bus. An identical copy of an operating system runs on each processor. Also each processor has its own caches. Since processors have identical architecture and instruction sets, a process or thread can run on any of them. Thus workload can be balanced. SMP approach can be used for multicore processors. SMP Multicore processors can run a single OS which supports SMP such as VxWorks 6.6 SMP [6], Linux 2.6 [7] These OS can fulfill load balancing which is fairly sharing out the overall processing workload to the processing elements.

## 2.3 Multicore Programming Challenges and Approaches

Before release of multicore processors, most software developers did not have to consider parallelism, so serial programming was efficient. However after beginning to use multicore processors, software developers must also improve their code writing skills and they also rewrite their code that was written for single core processors to reap the benefits of multi processors. They must parallelize their codes, divide serial program into tasks that can be run parallel on different cores simultaneously.

However this kind of programming is not easy. There are lots of challenges in multicore programming. Sometimes difficulty arises from the problem characteristic. Some problems can not be parallelized. Management of data used for solving a problem is another major challenge. Sharing data between tasks running in parallel and synchronizing the shared data are also significant issues for parallel programming. Software developers must avoid deadlocks and race conditions. [8] Partitioning of software into threads is another important issue that developers must be careful. It must be adequate for efficiency i.e. not too much and not too little. Also handling communication mechanism between these threads is another challenge. Proper load balancing must be ensured for avoiding mistakes due to disordered execution of available threads in software. Beside multicore software design, debugging is also a challenge for developers. [9]

Multiprocessing and multithreading are not new issues in programming but

with usage of multicore processors, they have become more popular. Presently there are some software development tools (compilers, frameworks etc.) that ease multithreading. [10] Nowadays companies continue to improve their tools to overcome multicore programming challenges. [9] Some static analysis tools have been developed to identify deadlocks and race conditions. Also there are compilers and operating systems that support development of multithreaded software. Moreover debugging tools have been improved to perform multicore debugging. Also some Parallel programming frameworks are available that ease the parallel programming.

However to be able to use these tools and to overcome multicore programming challenges software developers must also improve their writing skills and also change their viewpoint about problem analysis. Parallel thought is a fundamental starting point of parallel programming. [11]

To overcome these challenges and to make parallel programming easier, there are lots of studies. In the scope of these studies new parallel programming languages, frameworks, design patterns, parallel software architectures, libraries, run time environments are being introduced gradually. There are some research groups that study on this area.

Parallel Computing Laboratory (Par Lab) at the University of California, Berkeley is one of research group that study on parallel programming. According to [12] Par Lab has a top-down from the application approach instead of traditional bottom-up from the hardware approach. In parallel program development approach of Par Lab, there are two layers. First one is efficiency layer that includes optimized libraries and parallel programming frameworks developed by the parallel programmer experts. Second one is the productivity layer that includes composition and coordination language which are used to develop applications by the help of the efficiency layer. Application programmers or domain experts use the productivity of this layer.

7

Finally, autotuners which map the software efficiently to a particular parallel computer are involved in Par Lab approach. [12]

Pervasive Parallelism Laboratory (PPL) at Stanford University is another research group that study on parallel programming. PPL aims to make parallel programming easier. PPL studies on specific applications in different areas, programming models, software systems such as virtual machines, optimized compilers etc. and hardware architectures. The key concepts of PPL approach are domain specific languages, combining implicit or dynamic and explicit or static management of parallelism in a common parallel runtime, flexible hardware features. [13]

The Universal Parallel Computing Research Center (UPCRC) at the University of Illinois is another research group that study on parallel programming. UPCRC aims to develop a disciplined parallel programming model that supported by sophisticated development and execution environments as existing models in sequential programming. Also UPCRC study on parallelism of all levels from application to hardware such as parallel languages, autotuners, domain-specific environments, adaptive runtime environments, hardware mechanisms, refactoring tools. Moreover UPCRC aims to make future applications human centric. [14]

In [15], parallel computing approaches in ubiquitous programming of three different groups involved three universities are maintained. The first group is Parallel Computing Laboratory (Par Lab) at the University of California, Berkeley. Par Lab team has defined their pattern language which includes architectural and software patterns. Also they have formed a pattern-oriented software framework to build the software architecture of the parallel program. The second group is The Universal Parallel Computing Research Center at the University of Illinois. They focus on programming language, compiler, and runtime technologies supporting parallel programming. The third group

Stanford University's Pervasive Parallelism Laboratory (PPL). Their goal is to make parallelism accessible to average software developers. To do they develop parallel domain-specific languages. Moreover all three groups study on some other areas different from ubiquitous programming to develop parallel programs.

In [16] a pattern language for distributed computing is introduced. Although patterns involved in this pattern language are about distributed computing, some of them can be used for parallel programming such as patterns about concurrency, synchronization, message passing, data access.

In [17] Berkeley Par Lab's approach to the parallel programming and their studies are explained. Their studies are focused on both hardware and software parts of the computation. They have developed application-driven projects in different area by the helps of the domain experts. Par Lab introduces a pattern language, frameworks, productive environments to provide the abstraction of low level operations from the programmer. At the last part of [17] four other projects related with the parallel programming challenge are mentioned. One of them is The Universal Parallel Computing Research Center of the University of Illinois. They focus on productivity in specific domains than on generality or performance. They are advancing compiler to determine potential parallel parts. Also they develop frameworks that generate domain specific environment that provide an abstraction of parallel programming details. Another project is belongs to The Pervasive Parallelism Laboratory at Stanford University. Their approach includes domain specific languages and a common parallel runtime environment. Georgia Tech University is another group which develops different applications for Cell Broadband Engine Processor. Another project is The Habanero Multicore Software Project at Rice University. Languages, compilers, libraries, and tools are being developed in this project.

In [18] a new language for multicore processors, Manticore, is introduced. This language is a general-purpose programming language i.e. it is not developed for a specific field and it is also a parallel programming language.

Parallel programming patterns or pattern languages can be a common solution to parallel programming challenges for different domains. Two parallel programming pattern languages are reviewed in further detail in the next chapter.

## 2.4 Patterns for Parallel Programming Design Approach

## 2.4.1 Design Patterns & Pattern Language:

The concept of design patterns was first introduced by architect C. Alexander and some design patterns were offered to some common problems in area of architecture. In course of time this concept was entrenched in the area of software development. [19]

Software design patterns are generalized, time-tested and high-quality solutions to recurring problems that software developers frequently face with. These solutions are recorded within a predefined context which generally contains the name of pattern, problem, forces, solution etc. Thanks to this well-defined context, readers can understand design patterns quickly. Design patterns are also good method for sharing experience between experts of an area. Furthermore, design patterns generate a common vocabulary between people working in the same area. This provides better communication in the domain. [1]

Pattern languages are structured collection of patterns, or "the web of patterns". Pattern languages help developers to select appropriate patterns in complex designs.

There is a strong relation between some patterns in other words; actually some patterns complete each other. Thus, in design process, each selected pattern in pattern language leads to some other patterns. [1][20]

#### 2.4.2 Design Patterns in Real-Time Systems:

Although design patterns concept has been used in software for years, their usage in Real-Time (RT) software has not been soon. Some reasons for this delay stem from the nature of RT software. Mostly RT software must run on a particular hardware and this hardware has some limitations on memory, size, power etc. Since software patterns consume some of these limited hardware features, RT software developers could adapt to design patterns after improvements in hardware technologies.

Another reason for the delay in design pattern usage in RT software is that generally RT software developers are domain experts but not software development experts. Thus, enhancement of their software developing skills took some time. [21]

After usage of design patterns in RT software, some additional patterns that offer solutions to problems concerning RT software specifically have been developed.

#### 2.4.3 Parallel Programming Patterns

After parallel computing became popular, software developers started to develop new skills to exploit concurrency. Then, some software design patterns and pattern languages have been developed for parallel programming software to overcome some common problems and also to form better parallel software architecture. The first parallel programming pattern language was introduced in [1] by experts of parallel computing. Another pattern language for parallel programming is currently being developed by Berkeley Par Lab. [20]

## 2.4.3.1 Parallel Programming Pattern Language

In [1], Mattson, Sanders and Massingill collect and combine the experiences of experts in the parallel programming field. They present this collection as a pattern language which is a familiar method for software developers.

This pattern language is composed of four phases of parallel programming. Visiting these four phases sequentially with a top-down approach is recommended to parallel software developers. From top to down these phases are Finding Concurrencies, Algorithm Structure, Supporting Structures and Implementation Mechanisms.

## 2.4.3.1.1 Finding Concurrency Design Space:

In this design space of pattern language, the problem that is tried to solve with a parallel program is analyzed by the developer. This analysis is focused on problem size, possible tasks that solve the problem and data that would be used by tasks. After this analysis, the developer decides whether the parallel program effort is worthwhile or not for this problem. Also the developer determines the tasks, data and possible concurrent parts in the program.

The patterns in this design space can be divided into three groups.

#### **Decomposition Patterns:**

There are two patterns under this group which are **Task Decomposition Pattern** and **Data Decomposition Pattern**. By the help of these patterns the problem is decomposed into tasks that can be executed concurrently and data used by the tasks. Actually there is a strong interaction between these two patterns but according to the problem, one of them is selected for start.

#### **Dependency Analysis Patterns:**

*Group Tasks Pattern, Order Tasks Pattern, and Data Sharing Pattern* are included in this group. Thanks to these patterns dependencies between tasks are defined.

#### **Design Evaluation Patterns:**

Owing to this pattern the software developer can evaluate the design made in this design space. After the evaluation software developer decides whether to continue with this design or turn back and correct the design.

### 2.4.3.1.2 Algorithm Structure Design Space

In this design space, the software developer tries to distribute the concurrency found in the first phase to the unit of executions (UEs), namely threads or processes, by using patterns involved in this design space.

Most appropriate pattern or patterns must be selected for the problem. While making this selection, the developer must consider some software forces such as Efficiency, Simplicity, Portability and Scalability and also features of the target platform on which the parallel program run. Sometimes these factors can lead to conflicts. Thus the developer must optimize the selection.

Appropriate pattern selection depends on the specific problem. The potential

concurrent part of the problem is the major factor for this selection. This factor is named as major organizing principle. According to the problem, a task group, data or flow of data may be the major organizing principle.

Eventually the developer determines to the major organizing principle, the most appropriate pattern or patterns for design is selected. The developer must also consider the software quality factors and sometimes the hardware on which the program will run.

#### Organize By Tasks:

If execution of tasks is the major organizing principle, patterns in this group can be selected. **Task Parallelism Pattern** and **Divide and Conquer Pattern** are patterns in this group. Selection of one of these patterns is made according to the enumeration of the tasks. If tasks are enumerated linearly then **Task Parallelism Pattern** is selected else if they are enumerated recursively then **Divide and Conquer Pattern** can be selected.

#### Organize By Data Decomposition:

If decomposition of the data is the major organizing principle patterns in this group can be selected. *Geometric Decomposition Pattern* and *Recursive Data Pattern* are patterns in this group. Selection of one of these patterns is made according to the structure of data decomposition of the problem. If data is decomposed linearly then *Geometric Decomposition Pattern* is selected else if data has a recursive data structure then *Recursive Data Pattern* can be selected.

#### Organize By Flow of Data:

If flow of the data is major organizing principle patterns in this group can be selected. *Pipeline Pattern* and *Event-Based Coordination Pattern* are patterns in this group. Selection of one of these patterns is made according to the data flow order. If data flow regular and static then *Pipeline Pattern*

can be selected else if it is irregular and/or dynamic then *Event-Based Coordination Pattern* can be selected.

## 2.4.3.1.3 Supporting Structures Design Space

Patterns in this phase map the algorithm that was defined in Finding Concurrency and Algorithm Structure design spaces to the program source code. Patterns involved in this design space can be divided into two groups which are program structures and data structures.

Selection of patterns in this phase depends on the programming environment and selected patterns of previous phases. Table 2.1 shows relationships between supporting structure patterns and algorithm structure patterns and Table 2.2 shows relationships between supporting structure patterns and programming environments. In tables, number of stars shows the relevance of the supporting structure pattern in different cases.

| Table 2.1: Relationship between Supporting Structures patterns and |

|--------------------------------------------------------------------|

| Algorithm Structure patterns [1]                                   |

|                     | Task<br>Parallelism | Divide<br>and<br>Conquer | Geometric<br>Decomposition | Recursive<br>Data | Pipeline | Event-Based<br>Coordination |

|---------------------|---------------------|--------------------------|----------------------------|-------------------|----------|-----------------------------|

| SPMD                | ****                | ***                      | ****                       | **                | ***      | **                          |

| Loop<br>Parallelism | ***                 | **                       | ***                        |                   |          |                             |

| Master/Worker       | ****                | **                       | *                          | *                 | *        | *                           |

| Fork/Join           | **                  | ****                     | **                         |                   | ****     | ****                        |

# Table 2.2: Relationship between Supporting Structures patterns andprogramming environments [1]

|                  | OpenMP | MPI  | Java |

|------------------|--------|------|------|

| SPMD             | ***    | **** | **   |

| Loop Parallelism | ****   | *    | ***  |

| Master/Worker    | **     | ***  | ***  |

| Fork/Join        | ***    |      | **** |

#### **Program Structuring Patterns:**

This group contains patterns which are used for structuring the program source code.

*SPMD Pattern, Master/Worker Pattern, Loop Parallelism Pattern* and *Fork/Join Pattern* are the patterns in this group. Some of these patterns can be used simultaneously in a program. According to the programming environment and patterns selected in algorithm structure phase, appropriate pattern or patterns are selected from this group.

#### **Data Structuring Patterns:**

This group contains patterns which are used to structure the data to manage data dependencies. *Shared Data Pattern, Shared Queue Pattern* and *Distributed Array Pattern* are the patterns in this group.

## 2.4.3.1.4 Implementation Mechanisms Design Space

In this phase patterns of the previous phases are mapped to the codes for a specific environment. Methods in this phase can not be considered as design patterns. But this phase is important to complete the pattern language. Methods in this phase are UE management, Synchronization and Communication.

#### UE management:

There are different methods of creation, destruction, and management of the UEs (processes and threads) for different environments. Threads are created and destroyed with less cost with respect to he processes.

#### Synchronization:

Synchronization is very important issue for parallel programming. Because if task running order change, result of the program may change. For serial computation ordering is supplied by nature of sequential execution but in parallel computation more attention must be taken.

Moreover mutual exclusion is necessary to avoid parallel access to the shared data. If while one task writes to data and another task reads it at the same time, wrong data is read.

For both synchronization and mutual exclusion, there are different methods for different environments.

#### **Communication:**

Data transfer between the UEs is indispensable for most parallel programs. Communication mechanism is changed for different environments. Thus methods for communication are also changed.

## 2.4.3.1.5 Comments on Parallel Programming Pattern Language

Mattson, Sanders and Massingill's book [1] was written thanks to many years of experience of parallel computing. However the pattern language introduced in this book is not definitively completed but it was a start point for an iterative process of improvement. In course of time sufficiency of patterns are expected to be determined by users of this language and missing parts will be removed with some new patterns. [1]

Moreover, patterns in this book are high level patterns which are hard to learn. This pattern language needs small scaled patterns that support it. Also there may be some technology dependent and domain dependent patterns beside the patterns involved in this pattern language. [23]

# 2.4.3.2 Our Pattern Language (OPL) (Berkeley Par Lab Pattern Language for Parallel Programming)

OPL (Our Programming Language) developed by Berkeley Par Lab [24] is another pattern language for parallel programming. This pattern language is organized with a layered structure and it focuses on patterns for parallel programming and their usage. Other concepts of computer science are out of scope of this pattern language. Also OPL is domain independent, i.e., it is appropriate to application programmers in any field.

## 2.4.3.2.1 Structure of OPL

OPL is organized with a layered structure that contains five main groups of patterns. These groups are Architectural patterns, Computational patterns, Parallel Algorithm strategy patterns, Implementation strategy patterns and Concurrent execution patterns.

Architectural patterns and Computational patterns layers are at the same level and there is strong relation between them. An ordinary software developer visits layers from top to bottom but there can be some back and forth transitions.

#### 2.4.3.2.2 Architectural Patterns:

This group of patterns defines the overall architecture of a program. Patterns in this group are *Pipe-and-filter, Agent and Repository, Process control, Event based implicit invocation, Model-view-controller, Bulk Iterative, Map reduce, Layered systems, Arbitrary static task graph.*

#### 2.4.3.2.3 Computational Patterns:

Patterns involved in this group define the computations made by components of the program. Patterns in this group are **Backtrack**, **Banch and bound**, *Circuits*, *Dynamic programming*, *Dense linear algebra*, *Finite state machine*, *Graph algorithms*, *Graphical models*, *Monte Carlo*, *N-body*, *Sparse Linear Algebra*, *Spectral methods*, *Structured mesh*, *Unstructured mesh*.

#### 2.4.3.2.4 Parallel Algorithm Strategy Patterns:

This group is composed of high level strategies for better software to exploit concurrency. Patterns in this group are **Task parallelism**, **Data parallelism**, **Recursive splitting**, **Pipeline**, **Geometric decomposition**, **Discrete event**, **Graph partitioning**, **Digital Circuits**.

#### 2.4.3.2.5 Implementation Strategy Patterns:

This group of patterns defines implementation of the parallel program. There are two types of patterns in this group, namely program structure patterns and data structure patterns. Program structure patterns that describe program organization are *Single-Program Multiple Data (SPMD), Strict data parallel, Loop-level parallelism, Fork/join, Master-worker/Task-queue, Actors, BSP. Also data structure patterns are Shared queue, Distributed array, Shared hash table, Shared data, Data Locality.*

### 2.4.3.2.6 Concurrent Execution Patterns:

Patterns in this group illustrate the mapping of the parallel algorithm to the program. These patterns are strongly related with hardware and parallel programming model.

There are two types of patterns in this group. First type is process/thread control patterns and *CSP* or *Communicating Sequential Processes, Data flow, Task-graph, Single-Instruction Multiple Data (SIMD), Thread pool, Speculation* are the patterns of this type. The second type is coordination patterns that include *Message passing, Collective communication, Mutual exclusion, Point to point synchronization, Collective synchronization, Transactional memory* patterns. [24]

## 2.5 Real Time Performance Metrics

Real time systems are systems that must respond to an event within operational deadlines. If such a system cannot complete its work before a deadline then it is said to have failed. Thus correctness of the system depends not only on the correctness of solution but also response time.

Hard real time systems always require response time within given constraints. If even the system responds late only once, then it is said to have failed.

Soft real time systems can tolerate such delays but if these occur consistently then the system is said to have failed.

A real time system does not necessarily run as fast as possible. But it runs within deterministic time constraints. These constraints are defined specifically by system requirements.

In real-time embedded systems performance and low power consumption is very important. Multicore processors are good choices to satisfy these two criteria.

There are a number of metrics used to measure real time system performance. According to [25], some metrics to measure performance are grouped under **performance profiles** that include constraints that specify the time spent in functions, **A-B timing** which is the time between two specified points, **response to external events** which is the time between an external event and system response (e.g. interrupt latency), **RTOS task performance** i.e. task deadline performance according to a specific **task profile**.

In [26], three types of performance metrics for real-time systems are stated:

- Qualitative binary criteria (criteria either being fulfilled or not):

- o Timeliness, the ability to meet all deadlines

- No unbounded delays nor arbitrarily long executions

- Safety licensable, or better, safety licensed

- Functional correctness

- o Deterministic behavior

- Permanent readiness

- Simultaneous operation towards the outside

- All applicable physical constraints met

- Only static and real features used

- Deadlocks prevented

- Qualitative gradual criteria (one system may have a property to a higher degree than another one, but the property cannot be quantified):

- o Safety

- o Dependability

- o Behavioral predictability, even in error situations

- Complexity, or better, simplicity (the simpler the better)

- o Reliability

- o Robustness

- Fault tolerance

- Graceful degradation upon malfunctions

- o Portability

- o Flexibility

- Quantitative criteria (criteria giving rise to measurable numbers):

- o Worst-case response times to occurring events

- Worst-case times to detect and correct errors

- o Signal to noise ratio and noise suppression

- MTBF, MTDF, MTTF, and MTTR

- o Capacity reserves

- Overall project costs ("the bottom-line")

For different cases different subset of these metrics can be used. For example in [27] **responsiveness** (worst-case time to response time to an event) and **timeliness** (worst-case time to process after responding event) are mentioned as the metrics that determine the system performance.

Beside these real time system performance metrics, there are some performance metrics for parallel applications such as Sequential Time, Parallel Time, Critical Path Time, Speed, Speedup, Efficiency, Utilization, and Total Overhead. [28]

In [1] and in [24], parallel programming patterns from different sources have been brought together and pattern languages have been introduced. Since accessing to [1] is easier than accessing to [24] and [1] is well documented than [24], the pattern language in [1] is selected as guide for this thesis.

# **CHAPTER 3**

# **IMPLEMENTATION**

In this chapter, implementation of parallel software design for the test project in the thesis, multicore programming skills, development environment and test setup are described. The test project is designed both as sequential program and as parallel program by using the pattern language in [1]. Moreover, the test project is developed with attention to embedded real time software concerns.

Executable code of the project is run on an embedded environment. Wind River SBC8641D multicore evaluation board is used as hardware on which embedded real-time WindRiver VxWorks 6.6 SMP operating system operates.

Also Wind River WorkBench 3.0 development environment and its tools are used to develop the test project and to obtain the measurements.

## 3.1 VxWorks OS & VxWorks 6.6 with SMP

VxWorks is a real time operating system which is developed by WindRiver Company.

Main unit of execution elements for VxWorks OS are tasks. Task states and

transitions are described in Figure 3.1.

Figure 3.1: VxWorks Tasks

The VxWorks real-time kernel provides a multitasking environment that makes the tasks run concurrently on a processing unit (PU). Tasks have a task control block (TCB) in which context (state) of some system information about the task such as program counter, CPU registers, a stack for dynamic variables and function calls are saved. While running task on PU changes previous task context is stored on its TCB and new task context is restored from its TCB. This is called as context switching. [30]

Multitasking on VxWorks OS is performed by two scheduling algorithms:

- **Preemptive Scheduling:** CPU is allocated to the higher priority task among ready tasks by the preemptive priority-based scheduler.

- Round-robin scheduling: CPU is allocated fairly among all ready tasks of the same priority by executing tasks for same time interval or time slice.

For VxWorks previous releases until VxWorks 6.6 SMP, although tasks are seems as they run concurrently, this concurrency was virtual. In fact, at any moment only one task can be executed and to execute any other task, tasks must be switched by the operating system.

With VxWorks 6.6 SMP real parallel operating is performed on different cores of the multicore hardware. At a moment one task can be executed on one core and another one on another core. Beside this, the multitasking is still provided on any cores of the hardware.

In VxWorks 6.6 SMP OS with default settings, ready tasks are assigned to any idle core. But a task can be assigned to a specific core by user. This is called as CPU affinity.

Mutual exclusion is one of the most important issues for multitasking systems which means that avoiding the simultaneous use of a common resource by two execution unit. This resource can be a global variable or a piece of code called critical sections. Semaphores, message queues, task preemption locks are standard methods for performing the mutual exclusion in VxWorks OS.

Beside these methods, some new methods are required for VxWorks SMP to exploit concurrency and to solve some problems such as memory access

disorders which can be occurred only in multicore systems.

- Spinlocks: Spinlocks are like semaphore as both usage and mechanism. But main difference is that while task wait for a spinlock it does not make state transition from running to pending as in semaphore. Instead, task spin in a tight loop while it take spinlock. This is called spinning or busy wait. When spinlock is given by the task taken it, it is taken immediately by the task make busy wait without any context switch. Spinlock must be taken for a short and deterministic period of time because it may make the both PEs (CPU core on which task that took spinlock run and CPU core on which task making busy wait to take spinlock run) be busy. Spinlocks must be used carefully to avoid live locks.

- Live Lock occurs when such a case that task1 took spinlockA and waits for spinlockB when task2 had taken spinlock B and waits for spinlockA.

- Memory Barrier: Modern CPUs reorder the memory access (read and write) request. Sometimes this may cause errors. Actually this is not a problem for unicore CPUs but it is only for multicore CPUs. To avoid this problem memory barriers which prevents the memory access reordering are used. Example adapted from [30] shows how can memory access reorder be problem.

```

/* CPU 0 - announce the availability of work */

pWork = &work_item; /*store pointer to work item to be performed*/

workAvailable = 1;

/* CPU 1 - wait for work to be performed */

while (!workAvailable);

doWork (pWork); /*error - pWork might not be visible to this CPU yet*/

```

- Atomic Operations: Atomic operations are small operations that atomically access memory. Mutual exclusion is guaranteed while these operations are made. These operations are add, subtract, increment, decrement, OR, XOR, AND, NAND, set, clear, compare and swap. [30]

- **CPU-Specific Mutual Exclusion:** For a specific CPU task switching can be locked for a time to provide mutual exclusion. [30]

## 3.2 Wind River WorkBench 3.0

Wind River Workbench 3.0 is development tool for embedded real-time applications running on VxWorks OS. This tool is constructed on Eclipse-IDE which is an open source multi-language software development environment. In Figure 3.2 user interface of Wind River Workbench is shown.

Figure 3.2: User Interface of Wind River Workbench

Workbench is not only for developing software but it also supplies some features to control target by means of its cross development environment which is defined in [29] as "Cross-development is the process of writing code on one system, known as a host, that will run on another system, known as a target".

Workbench supports some different kinds of project as VxWorks Image Project, VxWorks Boot Loader/BSP Project, VxWorks Downloadable Kernel Module Project, VxWorks Real-time Process Project, VxWorks Shared Library Project, VxWorks ROMFS File System Project, User-Defined Project and Native Application Project. Among these project types VxWorks Image Project and VxWorks Downloadable Kernel Module Project are used in thesis. Additionally, VxWorks Boot Loader/BSP Project executable supplied by Wind River with SBC8641D is also used.

[29]

## 3.2.1 VxWorks Image Project:

VxWorks kernel image that is booted to the target is configured by VxWorks Image project. The most appropriate image projects for this thesis were created and used. Necessary configurations were set to be able measure performance parameters on running application. Moreover two image projects were created for thesis. One of them was built as only uniprocessor (UP) features included in it and other were built with symmetric multiprocessor (SMP) features addition to the UP features. Other configuration parameters were kept same between these two projects. [29]

## 3.2.2 VxWorks Downloadable Kernel Module Project:

VxWorks Downloadable Kernel Module projects are developed and built to add its executable into operating system kernel as module. This executables can be downloaded to and unloaded from target after image boots. Since these modules are added to the kernel space they can use system resources directly. Also operating system operations can be called from these modules. [29] Test program in this thesis were developed as a downloadable kernel module.

### 3.2.3 Debugger

As well as being a good development tool Workbench also offers a useful debugger that can be enable to debug kernel tasks and Real-time processes (RTPs). This debugger supports breakpoints, watching variables and registers, basic execution control (step into, step over, step out, go, and stop), advanced execution control (go all, stop all), system and task mode debugging on SMP systems and most of other debugging issues.

#### 3.2.4 Additional Tools

Moreover thanks to additional tools workbench enable developers to test the software in early phase of development process.

## 3.2.4.1 System Viewer

Wind River System Viewer is a logic analyzer that captures interactions between the operating system, application and target hardware in a time interval dynamically. These interactions are kernel activities such as semaphore gives and takes, task spawns and deletions, timer expirations, interrupts, message queue sends and receives, watchdog time activity, exceptions, signal activity, system calls, I/O activity, networking activity, memory allocation, freeing and partitioning, task switch, task states and also user events coded by user.

After capturing these interactions it can demonstrates the events in timeline, task by task graph or table. By using this tool race conditions, deadlocks, CPU starvation, and other problems relating to task interaction can be detected. [31]

## 3.2.4.2 VxWorks Simulator

The Wind River VxWorks Simulator is a hardware simulator that runs on the host machine. VxWorks applications can be developed, run, and tested on host machine without hardware thanks to VxWorks Simulator. VxWorks Simulator supports most of standard VxWorks features as followings:

- Real-Time Processes (RTPs)

- Error Detection and Reporting

- ISR Stack Protection (Solaris and Linux hosts only)

- Shared Data Regions

- Shared Libraries (Windows and Linux hosts only)

- ROMFS

- VxMP (shared-memory objects)

- VxFusion (distributed message queues)

- Wind River System Viewer

Also simulated hardware supports following features:

- a VxWorks console

- a system timer

- a memory management unit (MMU)—MMU support is required to take

- Advantage of the VxWorks real-time process (RTP) feature.

- non-volatile RAM (NVRAM)

- virtual disk support—Virtual disk support allows you to simulate a disk block

- device. The simulated disk block device can then be used with any file system

- supported by VxWorks.

- a timestamp driver

- a real-time clock

#### • symmetric multiprocessing (SMP) environment

[32]

Moreover, VxWorks Simulator supports networking application and it can be used to test complex networking applications. However since it does not simulates machine-level instructions for a target architecture, it is not suitable develop hardware device drivers. Also for more accurate SMP simulation multicore host machine must be used instead of simulator.

In this thesis both UP and SMP VxWorks Simulators are used to test software in early development phases. Then test program run on real hardware.

[32]

## 3.2.4.3 Function Tracer

Wind River Function Tracer is a dynamic execution-tracing tool that monitors the calls to a traced function while the application runs. It gives the information about which task make call, which parameters are passed, what is the return of function and also execution time of call. [33]

In this thesis System Viewer tool is used while coding and testing the software. VxWorks simulator tool is used to run the executable of the software in early phases to verify and debug the executable. When source code is verified at a sufficient depth on the simulator, the real hardware SBC8641D is replaced with the simulator. Debugger and Function Tracer tools are frequently used throughout the work to debug the program. Tools such as Performance profiler, Memory Analyzer, Data Monitor and Code Coverage Analyzer are not used in this thesis and have not been included in the review presented above; but they can be useful for parallel programming. For example Performance profiler can be used to determine the computationally insensitive parts which are potentially parallelizable in the

source code.

## 3.3 Experiment Setup

Experiment setup in this thesis is formed with two nodes and two connections between them as shown in Figure 3.3. One node is host machine which is a standard PC and other is target machine which WindRiver SBC8641D evaluation board.

Figure 3.3: Experiment Setup

## 3.3.1 Host Machine

Host machine that is used in this thesis is a standard a computer with Intel Core2 Quad CPU Q9400 @2.66Hz 1.97Hz, 3.46 GB of RAM. As an OS, Windows XP is run on the host machine. This machine has one Ethernet port and one serial port to connect with target.

Some necessary programs are installed on the host machine. For this work an FTP server, an NFS server and Wind River WorkBench will run on host machine.

#### **Connections with target:**

- As an FTP server, the FTP server supplied by Wind River in WorkBench installation directories is used. FTP server is necessary to boot VxWorks Image which is configured instance of VxWorks OS. To use this FTP server user rights must be set. Also board must be configured as to be able to boot from host and user name and password must be set same as FTP server rights.

- WorkBench supplies a useful interface to board by its target server connection facility. Thanks to target server connection, download a Kernel Module to the board is very easy as drag and drop. Running tasks, downloaded modules, vb. can be watched by target server connection. Also some VxWorks tools such as system viewer, performance scope, debugger, console, shell vb. can be run owing to the target server connection. Another feature supplied by target server connection is The Target Server File System (TSFS). It is a full-featured, easy to use file system that can be used to mount on host file system. However since its slow, in this thesis an external NFS server tool is used. But System Viewer tool actually uses TSFS.

- WorkBench also supplies terminal view to open serial connection with target. Terminal view can be used to watch the output text from target and to send input text to the target. An alternative program to terminal is Hyperterminal supplied by Windows XP.

- As NFS server an open source NFS server Truegrid Pro NFS is used for this thesis. Thanks to this server some directories on host machine are exported to the target use. Configuration files are read from these directories and log files are written to them in this thesis. This program runs as windows service on the host.

- Windows Telnet client is used to input text to board and output text from board. It is used as an alternative to the terminal feature of Workbench.

#### Other Used Programs:

#### PuTTY:

This tool is described as "*PuTTY is a free SSH, Telnet and Rlogin client for 32-bit Windows systems*" in its manual. Additionally it can be used to listen serial channel. This tool can log the output to a specified log file. In this thesis it is used both serial channel and telnet client.

## UltraEdit:

UltraEdit is commercial text editor software. Also it has a useful file comparison tool. This tool will be used to compare the output log files.

## 3.3.2 Target Machine

Target machine, namely the hardware that the application will run on is WindRiver SBC8641D for this thesis.

## 3.3.2.1 Wind River SBC8641D:

The SBC8641D evaluation board is produced by Wind River to enable software engineers to develop and test parallel applications. This single board computer is in a 6U form factor and contains the Freescale® MPC8641D<sup>™</sup> dual core processor.

Features available on the SBC8641D evaluation board are listed as followings:

- Freescale MPC8641D processor

- 2 banks of 256MB of DDR2 SDRAM running at DDR400 speed (each bank on different DDRMC).

- 128MB of Local Bus SDRAM using a 100-pin DIMM.

- (2) 16MB of on-board Flash memory (Dual boot ROM).

- 64MB One Nand, Flash File System.

- 8KB EEPROM.

- Four Gigabit Ethernet (GbE) ports via front-panel RJ45 connectors.

- Two RS-232 serial communication ports via mini-DB9 connectors.

- (2) x8 PCIe connectors

- Hard reset switch.

- 8 user switches.

- 2x16 LCD character display.

- 16-pin JTAG header for emulator communication

- 52-pin Universal Debug header for emulator communication.

[34]

## 3.3.2.2 Freescale MPC8641D

The MPC8641D is a dual core processor developed by Freescale. This processor has two 32-bit Power Architecture microprocessor cores e600

running at up to 1.5 GHz, two L2 cache for each core, dual 64 bit (72b with ECC) DDR2 memory controllers which can be assigned to the cores or shared between them, Dual 8-lane PCI Express ports, 4-lane serial RapidIO port, four Ethernet controllers supporting QoS and 10 Mbps, 100 Mbps, and 1000 Mbps.

The MPC8641D supports both symmetric multiprocessing (SMP) and Asymmetric multiprocessing (AMP). [35]

## 3.4 Test Project

#### 3.4.1 List Management Software:

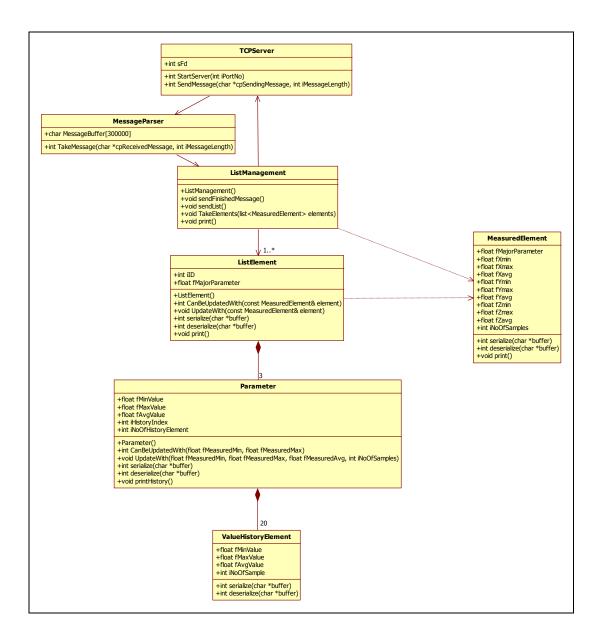

A dynamically changing list is managed by the test program within real time constraints. Members of the list that be managed are called ListElements. All ListElements are specified by an ID and they have three types of specific parameters and one major parameter. Specific parameters are called XParameter, YParameter, ZParameter which have similar properties. They are determined by their values. Each has minimum, maximum, average values. Major parameter has a single value for each element.

Parameters of a ListElement are measured by some devices. Measurements are made from some numbers of samples and minimum, maximum and average values are determined. Then ListElements that parameters values are determined are sent to the test program by another program via TCP interface. Any number of ListElements can be sent at one time.

After ListElements reach to the test program, program decides whether newly received element (RE) can update any present ListElement in the list or it is new element for the list. This decision is made with update decision algorithm. If RE can update an existing ListElement than this elements

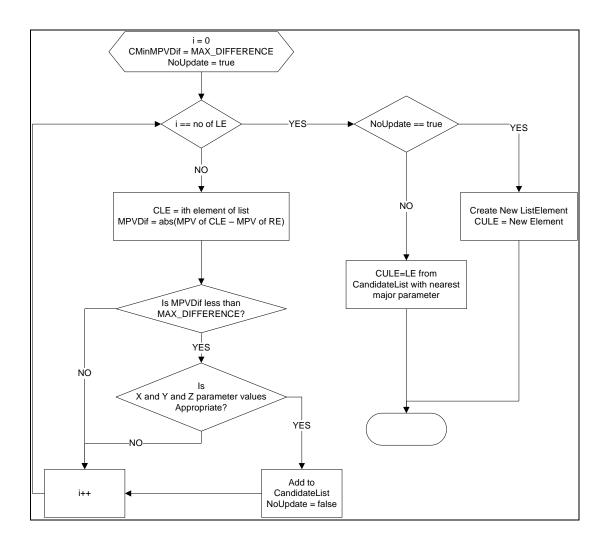

selected as Currently Updating Element (CULE) else a new ListElement is created and it is selected as CULE. After CULE is selected than updating process is made for CULE according to updating algorithm. General flow of the List Management Algorithm is shown in Figure 3.4.

Figure 3.4 Flow Chart of the List Management Algorithm

#### Update Decision Algorithm:

Currently updating ListElement (CULE) is chosen according to result of the update decision algorithm. If result is UPDATE for a ListElement then it is

selected as CULE else a new ListElement is created and becomes CULE.

To decide CULE, newly parameters of received element are compared one by one with the parameters of ListElements that are currently involved in the list.

**Major Parameter Comparison:** Firstly major parameter values are compared. If the absolute value of the difference of the comparing elements major parameter values is less than MAX\_DIFFERENCE then algorithm continues with specific parameter comparison. Else then next element from list is selected as comparing element.

**Specific Parameter Comparison:** MostInterceptionPercentage are computed for specific parameters of ListElement and ReceivedElement as following:

- Saying that currently comparing ListElement specific parameter minimum and maximum values are minValueLE and maxValueLE respectively and similiarly minimum and maximum values of newly received element parameters are minValueRE and maxValueRE.

- Interception is computed as following for different cases:

- Interception = 0

if maxValueLE ≤ minValueRE or maxValueRE ≤ minValueLE

- Interception = maxValueRE minValueRE

if minValueLE ≤ minValueRE and maxValueRE ≤ maxValueLE

- Interception = maxValueLE minValueLE

if minValueRE ≤ minValueLE and maxValueLE ≤ maxValueRE

- Interception = maxValueLE minValueRE

if minValueLE ≤ minValueRE and maxValueLE ≤ maxValueRE

- Interception = maxValueRE minValueLE

if minValueRE  $\leq$  minValueLE and maxValueRE $\leq$  maxValueLE

Maximum Interception Percentage = 100 \* maximum of Interception/(maxValueLE - minValueLE) and Interception/(maxValueRE minValueRE)

If Maximum Interception Percentage values for all three parameters are greater than MIN\_INTERCEPTION\_PERCENTAGE then ListElement is selected as CULE. Else then next element from list is selected as comparing element.

Beside this X, Y and Z parameter comparison algorithm, also some other algorithms may be possible with different methods. Some methods may be use parameter history list. Thus process time for the method is changed with the selected MAX\_HISTORY\_LENGTH constant. Since main focus of this thesis is not related with the selected methods, in test program this part of algorithm is replaced with a TimeKiller function that uses the CPU for a given time named as killtime. Tests are made for different killtime values to simulate different methods and different MAX\_HISTORY\_LENGTH constant values.

After major parameter and X, Y, Z parameter comparison, if more than one element are decided as CULE candidate then major parameters of these candidates are compared and one that has nearest major parameters value to the RE major parameter value, is selected as CULE.

If all ListElements compared and CULE is not determined yet then new ListElement is created and selected as CULE.

In Figure 3.5 the flow chart of the Update Decision Algorithm is presented.

Figure 3.5: Flow Chart of Update Decision Algorithm

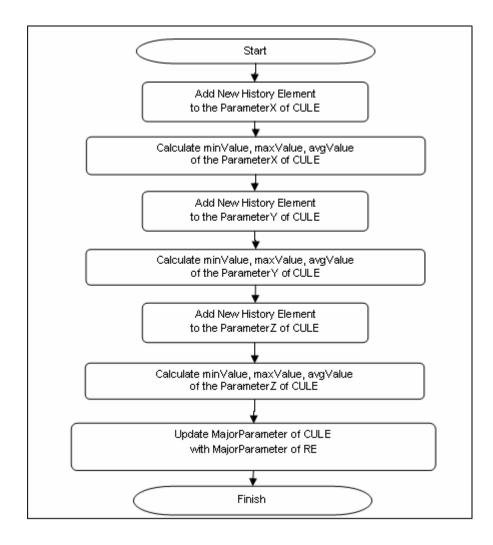

#### **Updating Algorithm:**

CULE major parameter value is set to the Received Element major parameter value. Then minimum, maximum, average values and number of samples values are inserted as a new value history element to the parameter. Then maximum, minimum and average values of parameter are computed as following:

- maxValue = maximum value among the value history elements max values.

- minValue = minimum value among the value history elements max values.

- avgValue = summation of multiplication of average value and number of samples divided by summation of number of samples among the value history elements.

After these update algorithm some other extra analysis on the list can be made. This analysis processing time is changed with the list length or with MAX\_HISTORY\_LENGTH constant. Since main focus of this thesis is not related with these analysis methods, in test program this part of algorithm is replaced with an TimeKiller function that uses the CPU for a given time.

In Figure 3.6 Flow Chart of the Updating Algorithm is demonstrated.

Figure 3.6: Flow Chart of Updating algorithm

## 3.4.2 Design of Parallel Test Software:

Parallel software design for the test project is made by using the pattern language in [1]. According to the pattern language in [1] there are four design phases that must sequentially be passed through by designer. Below, each phase shall be described in succession. In each phase, three different design approaches shall be considered.

In advance, it must be stated that the unit of execution (UE) is the task itself for the purposes of this thesis because the running program will execute on VxWorks OS as a downloadable kernel module.

## 3.4.2.1 Finding Concurrency Phase

According to the pattern language introduced in [1], first step to solve a problem as parallel is finding the concurrency in the problem.

Unfortunately the problem that is tried to solve in this thesis, does not have any parallelism that can be seen obviously. However some parts can be still make parallel.

At first sight, algorithm that is mentioned in 3.4.1 includes two main tasks. First one is update decision task which determines the CULE and second task is updating task that updates the parameters of the CULE with the parameters of the RE.

As for data, two main data are available in this problem, which are current list of LEs and the list of REs.

According the pattern language in [1] there are some forces in finding

concurrency patterns that the software designer must consider. One of these forces is flexibility. Parallel software design must be as flexible as it can be adapted to another hardware which has different architecture, different number of processors and different types of data sharing mechanisms. Another force is efficiency. Parallel software design is efficient if exploited concurrency is greater than work done to make design parallel. Number and size of tasks and data must be adequate to exploit concurrency by to make all PEs busy. Otherwise overhead of design (too much task switching, synchronization, communication etc) may bring about less performance respect to the serial program performance. Another force is simplicity. Design must be simple enough to be handled and complex enough to be run as parallel. However flexibility and efficiency may sometimes bring about some complexity.

Also design must be suitable for the hardware on which software run. Number of PE is an important hardware feature. Design must be made as ideally all PEs be used during runtime. Another important issue that must be considered is the data sharing mechanism on the hardware to make appropriate data decomposition.

Hardware on which test application in this thesis runs is a dual core processor. Thus it has two PEs. Also hardware is used as an SMP system. Therefore data sharing is performed by shared memory mechanism. These hardware features must be considered while parallel software design is being made.

Implementation of the list management algorithm can be made with three different parallel design approaches.

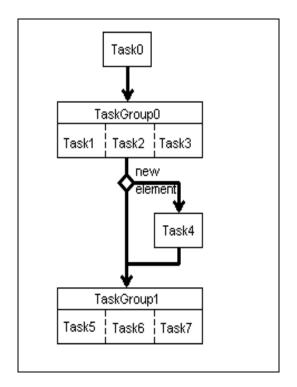

## 3.4.2.1.1 Design Approach 1:

One possible parallel programming design for list updating problem can be made as decompose the update decision task and updating task into small tasks as they process on only one parameter of the list elements. Also unfortunately there must be other tasks that run as sequential. These tasks are major element comparing task and new element creation task.

Tasks: Tasks in this approach are listed below.

- **Task0:** Major parameter comparing task

- This task runs as sequential and it decides whether the major parameters of the RE and CLE are appropriate to update or not.

- Major parameters of the i<sup>th</sup> RE and the k<sup>th</sup> LE are data accessed by this task. These data are read only for this task.

- **Task1:** X parameter comparing task

- This task decides whether the X parameters of the RE and CLE are appropriate to update or not.

- X parameters of the i<sup>th</sup> RE and the k<sup>th</sup> LE are data accessed by this task. These data are read only for this task.

- **Task2:** Y parameter comparing task

- This task decides whether the Y parameters of the RE and CLE are appropriate to update or not.

- Y parameters of the i<sup>th</sup> RE and the k<sup>th</sup> LE are data accessed by this task. These data are read only for this task.

- **Task3:** Z parameter comparing task

- This task decides whether the Z parameters of the RE and CLE are appropriate to update or not.

- Z parameters of the i<sup>th</sup> RE and the k<sup>th</sup> LE are data accessed by this task. These data are read only for this task.

- **Task4:** New list element creating task

- This task runs as sequential and it creates a new list element with default parameters.

- Data for this task is the new list element and it is set as CULE.