# UNCOOLED INFRARED FOCAL PLANE ARRAYS WITH INTEGRATED READOUT CIRCUITRY USING MEMS AND STANDARD CMOS TECHNOLOGIES

# A THESIS SUBMITTED TO THE GRADUATE SCHOOL OF NATURAL AND APPLIED SCIENCES OF THE MIDDLE EAST TECHNICAL UNIVERSITY

$\mathbf{B}\mathbf{Y}$

# SELİM EMİNOĞLU

# IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

#### IN

### THE DEPARTMENT OF ELECTRICAL AND ELECTRONICS ENGINEERING

JULY 2003

Approval of Graduate School of Natural and Applied Sciences

Prof. Dr. Canan ÖZGEN

Director

I certify that this thesis satisfies all the requirements as a thesis for the degree of Doctor of Philosophy.

Prof. Dr. Mübeccel DEMİREKLER

Head of Department

This is to certify that we have read this thesis and that in our opinion it is fully adequate, in scope and quality, as a thesis for the degree of Doctor of Philosophy.

Assoc. Prof. Dr. Tayfun AKIN

Supervisor

Examining Committee Members:

# ABSTRACT

# UNCOOLED INFRARED FOCAL PLANE ARRAYS WITH INTEGRATED READOUT CIRCUITRY USING MEMS AND STANDARD CMOS TECHNOLOGIES

Eminoğlu, Selim Ph.D., Department of Electrical and Electronics Engineering Supervisor: Assoc. Prof. Dr. Tayfun Akın

July 2003, 276 pages

This thesis reports the development of low-cost uncooled microbolometer focal plane arrays (FPAs) together with their integrated readout circuitry for infrared night vision applications. Infrared microbolometer detectors are based on suspended and thermally isolated p<sup>+</sup>-active/n-well diodes fabricated using a standard 0.35  $\mu$ m CMOS process followed by a simple post-CMOS bulk-micromachining process. The post-CMOS process does not require any critical lithography or complicated deposition steps; and therefore, the FPA cost is reduced considerably. The integrated readout circuitry is developed specially for the p<sup>+</sup>-active/n-well diode

microbolometers that provides lower input referred noise voltage than the previously developed microbolometer readout circuits suitable for the diode type microbolometers. Two FPAs with  $64 \times 64$  and  $128 \times 128$  array formats have been implemented together with their low-noise integrated readout circuitry. These FPAs are first of their kinds where such large format uncooled infrared FPAs are designed and fabricated using a standard CMOS process.

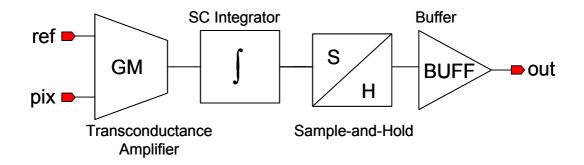

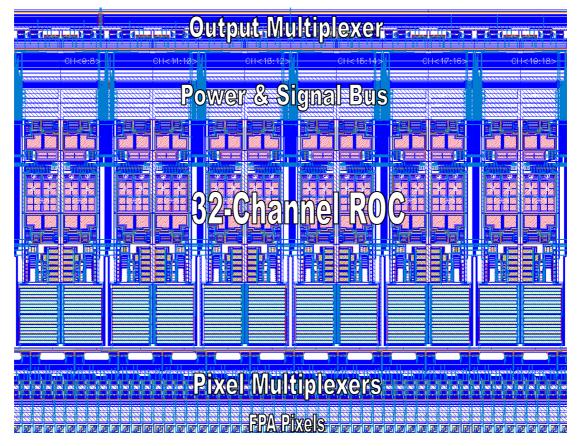

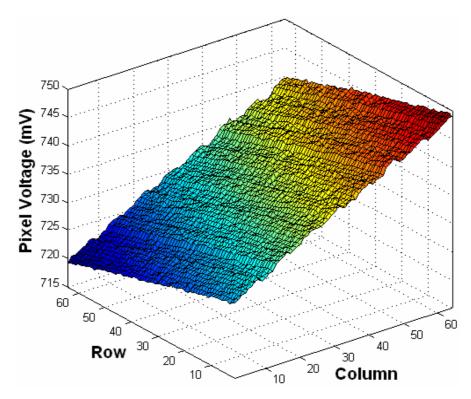

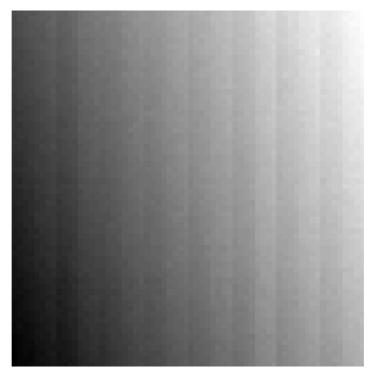

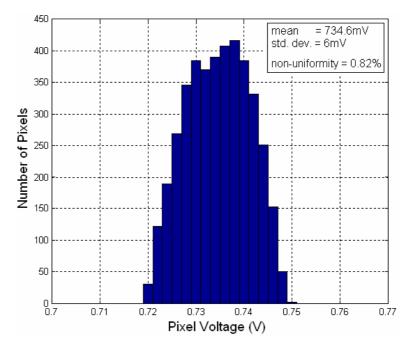

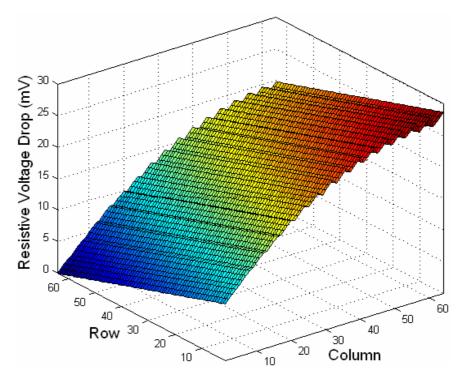

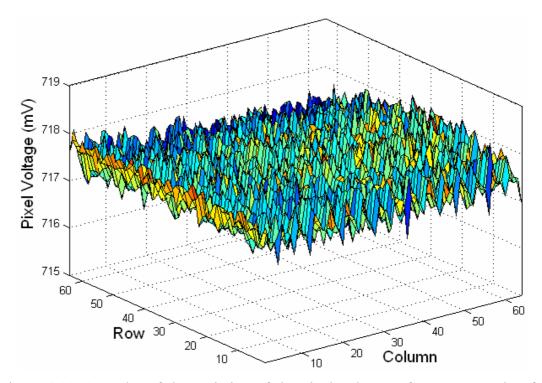

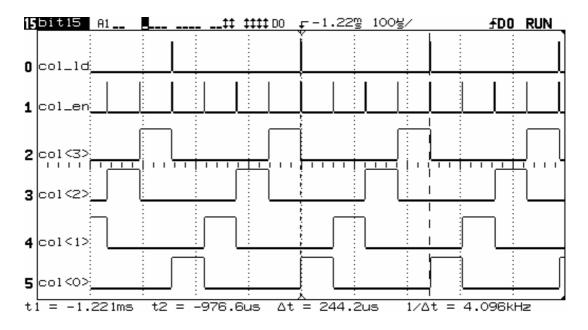

The fabricated detectors have a temperature coefficient of -2 mV/K, a thermal conductance value of  $1.55 \times 10^{-7}$  W/K, and a thermal time constant value of 36 ms, providing a measured DC responsivity  $(\Re)$  of 4970 V/W under continuous bias. The measured detector noise is 0.69  $\mu$ V in 8 kHz bandwidth, resulting a measured detectivity (D<sup>\*</sup>) of  $9.7 \times 10^8$  cm $\sqrt{\text{Hz/W}}$ . The 64 × 64 FPA chip has 4096 pixels scanned by an integrated 16-channel parallel readout circuit composed of low-noise differential transconductance amplifiers, switched capacitor integrators, and sample-and-hold circuits. It measures  $4.1 \text{ mm} \times 5.4 \text{ mm}$ , dissipates 25 mW power, and provides an estimated NETD value of 0.8 K at 30 frames/sec (fps) for an f/1 optics. The measured uncorrected voltage non-uniformity for the  $64 \times 64$  array after the CMOS fabrication is 0.8 %, which is reduced further down to 0.2 % for the  $128 \times 128$  array using an improved FPA structure that can compensate for the fixed pattern noise due to the FPA routing. The  $128 \times 128$  FPA chip has 16384 microbolometer pixels scanned by a 32-channel parallel readout circuitry. The  $128\times128$  FPA measures 6.6 mm  $\times$  7.9 mm, includes a PTAT temperature sensor and a vacuum sensor, dissipates 25 mW power, and provides an estimated NETD value of 1 K at 30 fps for an f/1 optics. These NETD values can be decreased below 350 mK with further optimization of the readout circuit and post-CMOS etching steps. Hence, the proposed method is very cost-effective to fabricate large format focal plane arrays for very low-cost infrared imaging applications.

Keywords: Uncooled infrared detectors, microbolometers, low-cost microbolometer detectors, uncooled infrared focal plane arrays, readout circuits for microbolometers.

# MEMS VE STANDART CMOS TEKNOLOJİLERİ İLE ENTEGRE OKUMA DEVRELİ SOĞUTMASIZ KIZILÖTESİ ODAK DÜZLEM MATRİSLERİ

Eminoğlu, Selim Doktora., Elektrik ve Elektronik Mühendisliği Bölümü Tez Yöneticisi: Doç. Dr. Tayfun Akın

Temmuz 2003, 276 sayfa

Bu tezde kızıl ötesi gece görüş uygulamaları için MEMS ve standart CMOS teknolojileri kullanılarak düşük maliyetli, okuma devreleri ile entegre edilmiş soğutmasız kızıl ötesi dedektör odak düzlem matrisleri (ODMler) anlatılmaktadır. Geliştirilen kızıl ötesi mikrobolometre dedektörleri, 0.35 µm CMOS üretim süreci ve sonrasında basit bir gövde aşındırma işlemi kullanılarak üretilen, gövdeden ısıl olarak izole edilmiş p<sup>+</sup>-aktif/n-kuyu diyot yapılarına dayanmaktadır. CMOS üretim sonrasında yapılan işlemler ne kritik bir pozlama ne de karmaşık bir malzeme serim işlemi içermektedir; bu nedenle, odak düzlem matrisinin maliyeti oldukça düşürülmüştür. Entegre okuma devresi özel olarak p<sup>+</sup>-aktif/n-kuyu diyot tipi mikrobolometreler için geliştirilmiş olup, daha önceden geliştirilen diyot tipi

mikrobolometrelere uygun okuma devrelerinden daha düşük giriş gürültüsüne sahiptir. Düşük gürültülü entegre okuma devreleri içeren 64 × 64 ve 128 × 128 dizin formatlı iki adet odak düzlem matrisi üretilmiştir. Üretilen bu odak düzlem matrisleri bu boyutlarda CMOS teknolojisinde üretilmiş olan ilk odak düzlem matrisleri olma özelliğine sahiptirler.

Üretilen dedektörlerin sıcaklık sabitleri -2 mV/K, ısıl iletileri  $1.55 \times 10^{-7}$  W/K, ısıl zaman sabitleri 36 ms'dir ve ölçülmüş kızılötesi DC cevaplılıkları sürekli kutuplama altında 4970 V/W'dır. Ölçülen dedektör gürültüsü 8 kHz elektriksel band aralığında 0.69  $\mu$ V'dur ve 9.7 × 10<sup>8</sup> cm $\sqrt{Hz/W'}$ lık bir dedektivite değerine karşılık gelmektedir. 64 × 64 odak düzlem matrisindeki 4096 adet piksel, düşük gürültülü fark-geçiş-ileti yükselticisi, anahtarlamalı kapasitör entegratörü ve örnekle-ve-tut devreleri içeren 16 kanallı paralel bir okuma devresi tarafından taranmaktadır. Üretilen 64  $\times$  64 odak düzlem matrisinin boyutu 4.1 mm  $\times$  5.4 mm, güç tüketimi 25 mW olup, 30 fps tarama hızında f/1 optik ile 0.8 K'lik bir gürültüye eş sıcaklık farkı (GESF) sağlaması beklenmektedir. CMOS üretim sonunda  $64 \times 64$  odak düzlem matrisinin ölçülmüş esdeğersizlik değeri % 0.8'dir ve bu değer  $128 \times 128$ odak düzlem matrisinde geliştirilmiş odak düzlem yapısı sayesinde % 0.2'ye kadar indirilmiştir.  $128 \times 128$  odak düzlem matrisindeki 16384 adet piksel 32 kanallı bir okuma devresi tarafından okunmaktadır. 128 × 128 odak düzlem matrisinin boyutu 6.6 mm × 7.9 mm, güç tüketimi 25 mW olup, 30 fps hızında f/1 optik ile 1 K GESF değeri sağlaması beklenmektedir. Okuma devrelerinin ve CMOS sonrası asındırma işlemlerinin optimizasyonu ile verilen GESF değerlerinin 350 mK'in altına indirilmesi mümkündür. Yukarıda belirtilen nedenlerden dolayı öne sürülen bu yeni yöntem, düşük maliyetli kızıl ötesi görüntüleme uygulamaları için büyük dizin yapılarının düşük maliyet ile üretimini mümkün kılmaktadır.

Anahtar Kelimeler: Soğutmasız kızıl ötesi dedektörler, mikrobolometreler, düşük maliyetli mikrobolometre dedektörleri, soğutmasız kızılötesi odak düzlem matrisleri, mikrobolometreler için okuma devreleri.

To My Parents

# ACKNOWLEDGEMENTS

I would like to express my appreciation and thanks to my thesis advisor Assoc. Prof. Dr. Tayfun Akın for his valuable guidance, support, and help throughout my graduate studies and the development of this thesis.

I would also like to thank Assoc. Prof. Dr. Cengiz Beşikci and Prof. Dr. Abdullah Atalar for their comments and suggestions throughout the development of this thesis work. I would also like to thank Prof. Dr. Murat Aşkar for giving me the first research opportunity in the field of integrated circuit design, which formed the very basis of this thesis work.

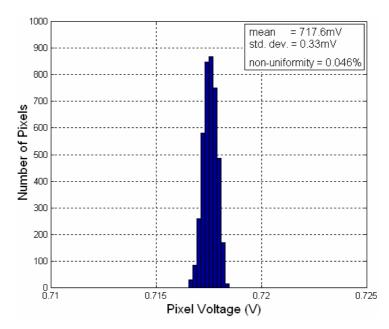

I would like to thank Prof. Dr. Ekmel Özbay and Murat Güre from Bilkent University for providing access to their dry etching equipments during the post processing of the CMOS fabricated chips. I would also like to thank Hacer Selamoğlu and Ümid Tümkaya from ASELSAN Inc. for the fabrication of the printed circuit boards used for the chip testing. I am also grateful to İhsan Özsoy, Zeki Topçu, Yılmaz Ünal, and Cumhur Ergenekon from ASELSAN Inc. for their valuable suggestions, help, and equipment support during the electro-optical tests of the fabricated infrared detectors.

I would like to thank Dr. Deniz Sabuncuoğlu Tezcan for her valuable suggestions and discussions during the design of the detector arrays and detector tests. I am also thankful to Mahmud Yusuf Tanrıkulu for his efforts for the post-processing of the fabricated detectors and arrays as well as for his help in the electro-optical tests. I would also like to thank Orhan Akar for his valuable suggestions during detector design and for his extra ordinary efforts to keep the laboratory infrastructure working throughout this thesis research. I would also like to thank Mustafa Özuysal and Murat Tepegöz for their contributions in the software development of the data acquisition system, and Fatih Say for his helps in the preparations of printed circuit boards using in-house fabrication facilities. I would like to thank Haluk Külah and Fatih Koçer for their friendship and hospitality during my conference visits to the United States. I would also like to thank to all the research group members, staff and friends whose names are not listed above for providing a very pleasant and friendly working environment.

Last but not least, I would like to thank to my parents Ayla and Muhittin Eminoğlu for their continuous support and encouragement through all my life.

This research work is supported by the Research and Development Department of the Ministry of Defense (MSB ArGe) and partially supported by the ASELSAN Inc.

# **TABLE OF CONTENTS**

| ABSTR  | RACT                                             | iii  |

|--------|--------------------------------------------------|------|

| ÖZ     |                                                  | v    |

| DEDIC  | ATION                                            | vii  |

| ACKN   | OWLEDGEMENTS                                     | viii |

| TABLE  | E OF CONTENTS                                    | X    |

| LIST O | F TABLES                                         | xiv  |

| LIST O | FFIGURES                                         | xv   |

| СНАРТ  | ΓER                                              |      |

| 1.     | INTRODUCTION                                     | 1    |

|        | 1.1 Infrared Spectrum                            | 2    |

|        | 1.2 Types of Infrared Detectors                  | 5    |

|        | 1.3 Thermal (Uncooled) Infrared Detectors        | 6    |

|        | 1.3.1 History of Thermal Detectors               | 9    |

|        | 1.4 Types of Thermal Infrared Detectors          | 10   |

|        | 1.4.1 Resistive Microbolometers                  | 11   |

|        | 1.4.2 Pyroelectric and Ferroelectric Detectors   | 14   |

|        | 1.4.3 Thermoelectric Detectors                   |      |

|        | 1.4.4 Diode Type Microbolometers                 |      |

|        | 1.5 Low-cost Uncooled Infrared Detectors at METU | 19   |

|        | 1.6 Research Objectives and Thesis Organization  | 22   |

| 2.     | FIGURE OF MERITS FOR THERMAL DETECTORS           |      |

|        | 2.1 Responsivity                                 |      |

|        | 2.2 Noise Equivalent Power (NEP)                 | 29   |

|    | 2.3 Noise Equivalent Temperature Difference (NETD)  | 30  |

|----|-----------------------------------------------------|-----|

|    | 2.4 Detectivity (D <sup>*</sup> )                   | 32  |

|    | 2.5 Fundamental Limits                              | 33  |

|    | 2.5.1 Background (Photon) Noise Limit               | 34  |

|    | 2.5.2 Temperature Fluctuation Noise Limit           | 35  |

|    | 2.6 Conclusions                                     | 38  |

| 3. | N-WELL DIODE TYPE MICROBOLOMETER DETECTOR           | 39  |

|    | 3.1 Pixel Structure                                 | 40  |

|    | 3.2 Pixel Optimization and Performance Analysis     | 42  |

|    | 3.2.1 Optimum Pixel Size                            | 42  |

|    | 3.2.2 Temperature Sensitivity                       | 46  |

|    | 3.2.3 Electrical Noise                              | 49  |

|    | 3.2.4 Optimum Pixel Bias                            | 51  |

|    | 3.3 Self-Heating                                    | 53  |

|    | 3.4 Conclusions                                     | 54  |

| 4. | TEST RESULTS OF THE SINGLE PIXEL DETECTORS          | 56  |

|    | 4.1 Post-CMOS Fabrication                           | 57  |

|    | 4.2 Temperature Sensitivity Measurement             | 58  |

|    | 4.3 I-V Measurements                                | 60  |

|    | 4.4 Infrared Responsivity Measurement               | 63  |

|    | 4.5 Spectral Absorption Measurement                 | 66  |

|    | 4.6 Noise Measurement                               | 69  |

|    | 4.7 Conclusions                                     | 77  |

| 5. | READOUT CIRCUITS FOR UNCOOLED INFRARED              |     |

|    | DETECTOR ARRAYS                                     | 79  |

|    | 5.1 Biasing Circuits for the Uncooled Detectors     | 80  |

|    | 5.2 Self-Heating Compensation                       | 85  |

|    | 5.3 Preamplifiers for the Resistive Microbolometers | 86  |

|    | 5.3.1 BCDI Preamplifier Circuit                     | 87  |

|    | 5.3.2 CTIA Preamplifier                             | 93  |

|    | 5.3.3 WBDA Preamplifier                             | 99  |

|    | 5.3.4 CCBDI Preamplifier                            | 100 |

|    | 5.4 | Prea   | mplifiers for the Diode Type Microbolometers            | 106 |

|----|-----|--------|---------------------------------------------------------|-----|

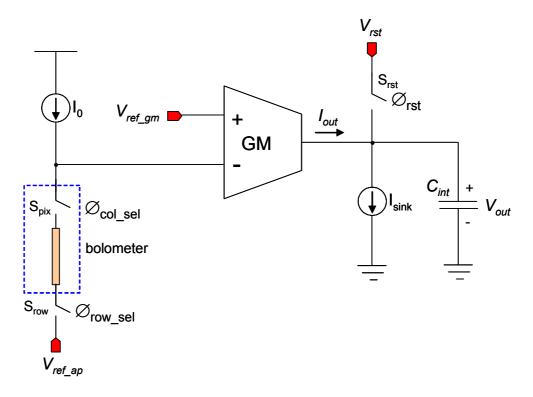

|    | 5.  | 4.1    | GMI Preamplifier                                        | 107 |

|    | 5.4 | 4.2    | DBI-CTIA Preamplifier                                   | 111 |

|    | 5.5 | Rea    | dout Architecture for the Uncooled Detector Arrays      | 113 |

|    | 5.6 | Unit   | formity Correction                                      | 116 |

|    | 5.7 | Sum    | mary and Conclusions                                    | 117 |

| 6. | THE | E 64 > | × 64 UNCOOLED INFRARED FPA                              | 121 |

|    | 6.1 | Arra   | ay Structure                                            | 122 |

|    | 6.2 | Effe   | ect of the FPA Routing Resistance on the Infrared Image | 125 |

|    | 6.3 | Refe   | erence Detector Array                                   | 127 |

|    | 6.4 | Rea    | dout Architecture of the 64 × 64 FPA Chip               | 128 |

|    | 6.5 | Ana    | log Channel Readout Circuit                             | 129 |

|    | 6.  | 5.1    | Low-Noise Preamplifier                                  | 130 |

|    | 6.  | 5.2    | Switched-Capacitor Integrator (SCI)                     | 146 |

|    | 6.  | 5.3    | Opamp                                                   | 155 |

|    | 6.  | 5.4    | Correlated Double Sampling (CDS) Circuit                | 164 |

|    | 6.  | 5.5    | Sample-and-Hold (S/H) Amplifier                         | 167 |

|    | 6.  | 5.6    | Analog Multiplexers and Etch Transistors                | 170 |

|    | 6.6 | Digi   | ital Scanning Circuitry                                 | 173 |

|    | 6.  | 6.1    | Digital Timing Circuit                                  | 174 |

|    | 6.  | 6.2    | Shift Registers (VSR, HSR, and OSR)                     | 175 |

|    | 6.7 | Lay    | out Integration of Modules                              | 182 |

|    | 6.8 | Sum    | mary and Conclusions                                    | 188 |

| 7. | THE | E 128  | × 128 UNCOOLED INFRARED FPA                             | 189 |

|    | 7.1 | FPA    | Architecture                                            | 191 |

|    | 7.2 | Imp    | roved Array Structure                                   | 192 |

|    | 7.3 | Ana    | log Readout Circuitry                                   | 198 |

|    | 7.  | 3.1    | Improved Differential Transconductance Amplifier        | 199 |

|    | 7.  | 3.2    | Improved Switched Capacitor Integrator (SCI)            | 202 |

|    | 7.  | 3.3    | Improved Self-Heating Compensation                      | 204 |

|    | 7.4 | Digi   | ital Scanning Circuitry                                 | 205 |

|    | 7.5 | Inte   | gration of Modules                                      | 206 |

|       | 7.6 On-chip Temperature and Vacuum Sensors           | 208 |

|-------|------------------------------------------------------|-----|

|       | 7.6.1 Temperature Sensors                            | 209 |

|       | 7.6.2 Vacuum Sensors                                 | 211 |

|       | 7.7 Floor Plan and Chip Layout                       | 212 |

|       | 7.8 Summary and Conclusions                          | 215 |

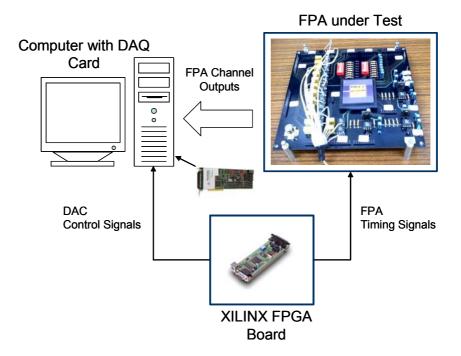

| 8.    | TEST RESULTS OF THE FABRICATED FPAS                  | 216 |

|       | 8.1 Post-CMOS Fabrication Results                    | 217 |

|       | 8.2 Test Results of the $64 \times 64$ FPA           |     |

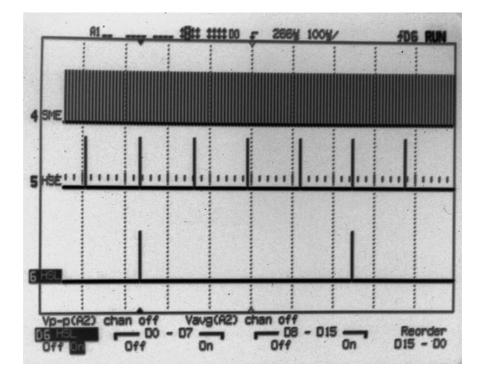

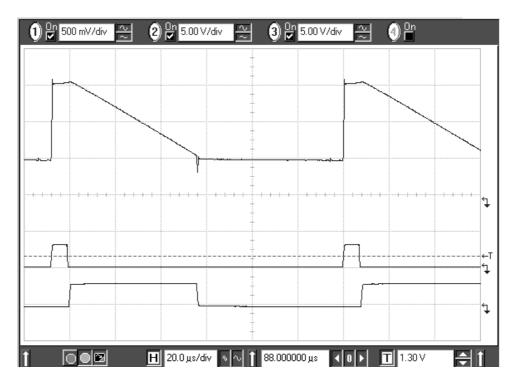

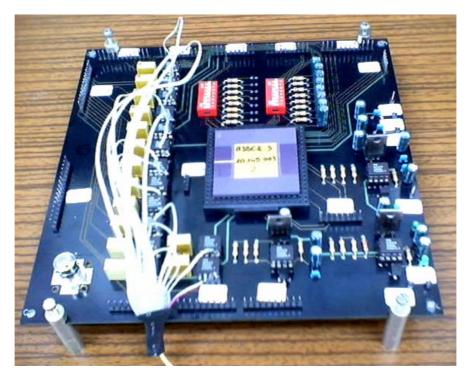

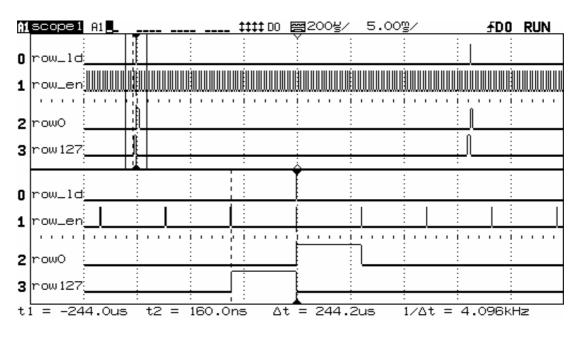

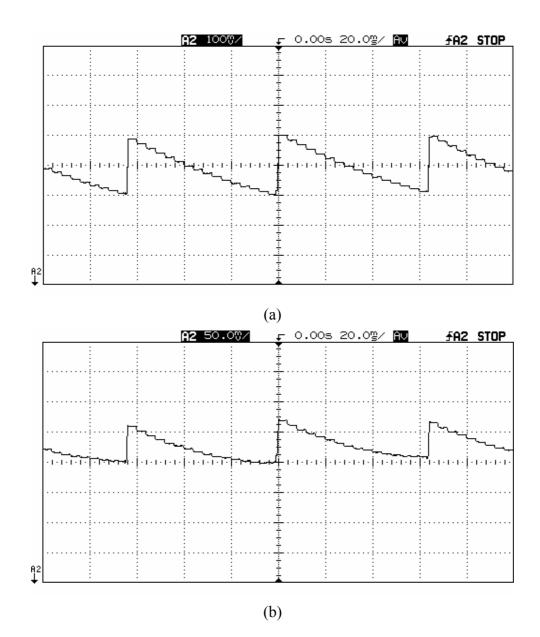

|       | 8.2.1 Test Results of the Digital Scanning Circuitry | 220 |

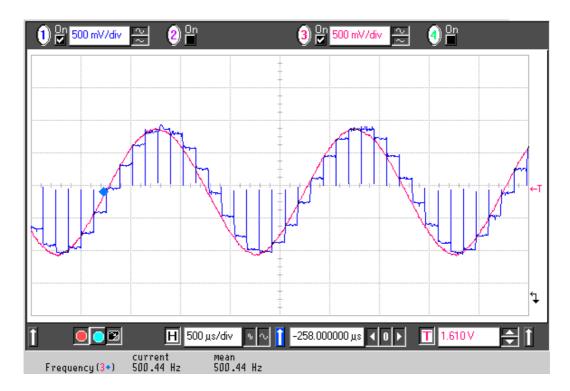

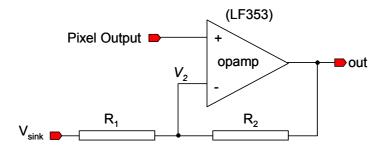

|       | 8.2.2 Test Results for the Analog Test Channel       | 224 |

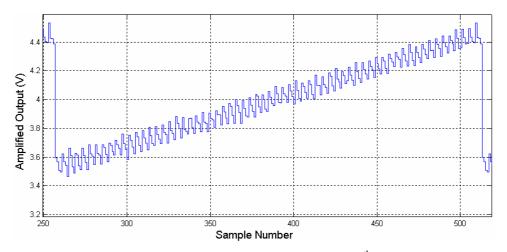

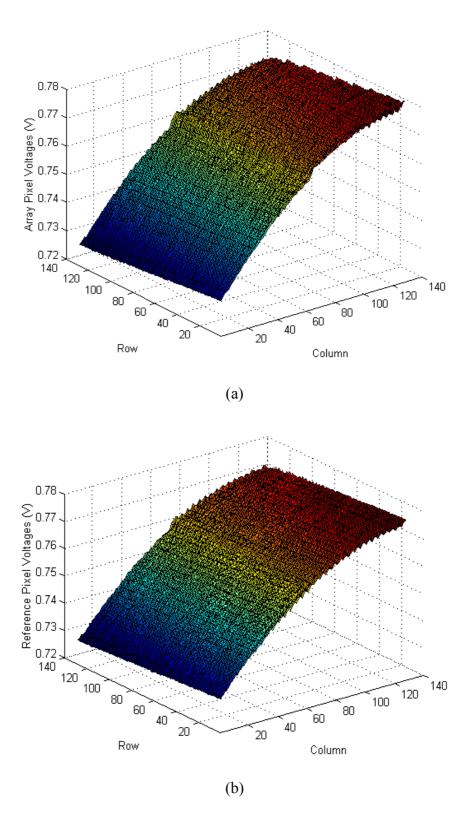

|       | 8.2.3 Uniformity Tests                               |     |

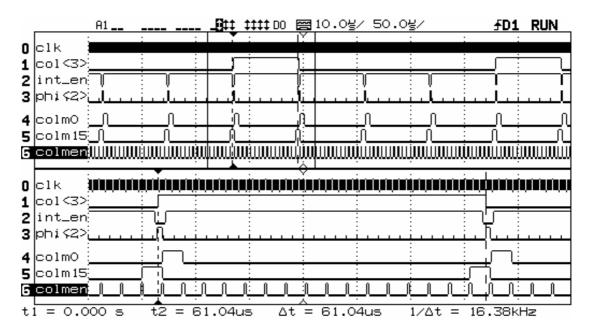

|       | 8.3 Test Results of the $128 \times 128$ FPA         | 240 |

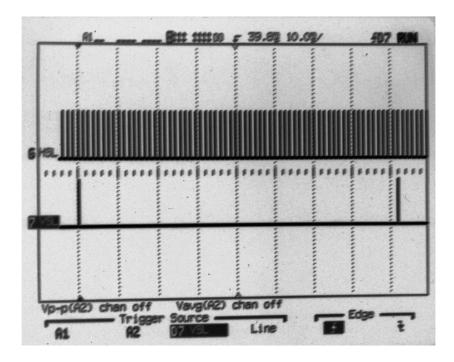

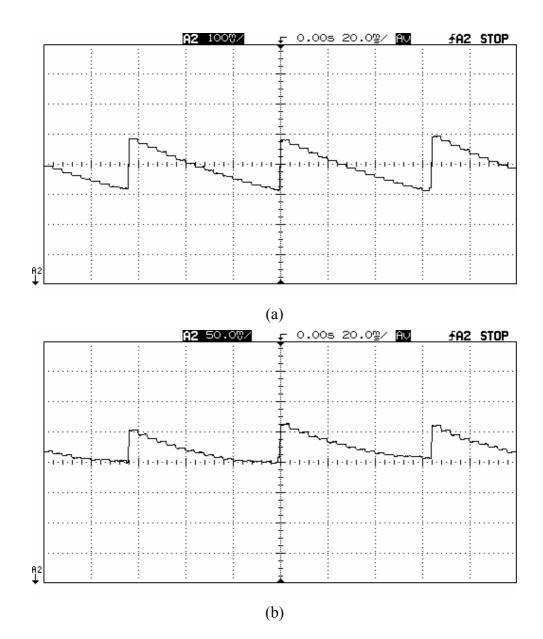

|       | 8.3.1 Test Results of the Digital Scanning Circuit   | 241 |

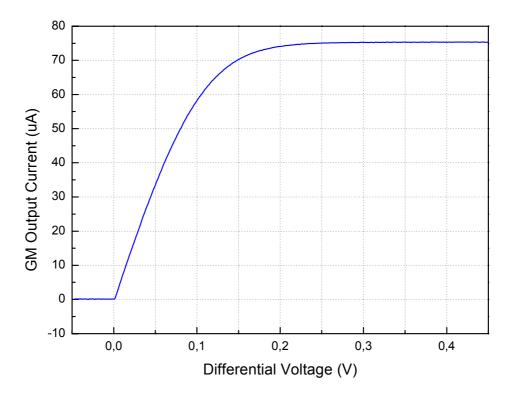

|       | 8.3.2 Test Results of the Analog Circuits            | 243 |

|       | 8.3.3 FPA Uniformity Test Result                     |     |

|       | 8.4 Effect of Post-CMOS Processing on FPA Uniformity | 255 |

|       | 8.5 Expected Yield for Wafer Level Fabrication       | 256 |

|       | 8.6 Conclusions                                      | 258 |

| 9.    | CONCLUSIONS AND FUTURE WORK                          | 259 |

| REFER | RENCES                                               |     |

| VITA  |                                                      |     |

# LIST OF TABLES

| TAB | LE                                                                                                                                                          |     |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.1 | Material [53] and process [54] properties used in the determination of the optimum pixel size for the diode type microbolometer detector                    | 43  |

| 4.1 | Comparison of resistive and diode type n-well microbolometer detectors                                                                                      | 78  |

| 6.1 | Device geometries for the circuit given in Figure 6.6                                                                                                       | 133 |

| 6.2 | Device geometries for the offset current sink circuitry                                                                                                     | 149 |

| 6.3 | Gain adjustment of the SCI and corresponding dynamic ranges of the readout circuit for a 2.8 V output swing                                                 | 152 |

| 6.4 | Transistor device dimensions used in the opamp circuit                                                                                                      | 156 |

| 6.5 | Simulated electrical parameters of the transistors involved in the low frequency open loop gain expression of the opamp circuit                             | 159 |

| 6.6 | Simulated parameter summary for the opamp circuit.                                                                                                          | 163 |

| 6.7 | Capacitor and output voltages at different clock phases in the CDS circuit                                                                                  | 166 |

| 6.8 | Capacitor and output voltages of the S/H circuit at different clock phases                                                                                  | 169 |

| 8.1 | Comparison of the expected yield and cost of the p <sup>+</sup> -active/n-well FPAs developed at METU with different uncooled arrays in the literature [23] | 257 |

| 9.1 | Performance parameter summary for the CMOS fabricated FPAs                                                                                                  | 264 |

# **LIST OF FIGURES**

# FIGURE

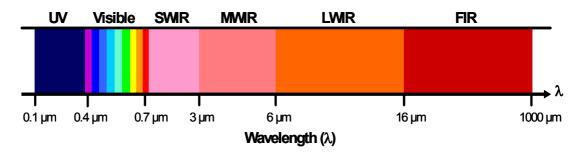

| 1.1 Complete electromagnetic spectrum of light with important spectral regions [1].                                                                                                                                                                                   | 3  |

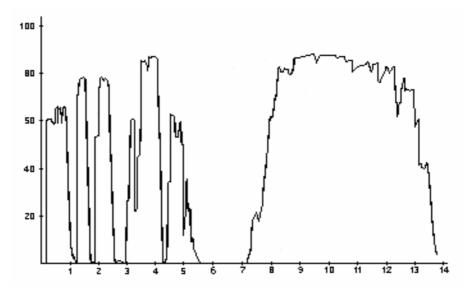

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 Atmospheric transmittance over 2 km at sea level [2]                                                                                                                                                                                                              | 3  |

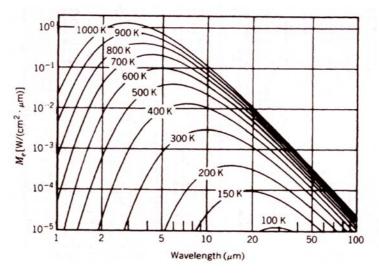

| 1.3 Variation of the blackbody spectral exitance with wavelength for different blackbody temperatures from 100 K to 1000 K [4].                                                                                                                                       | 4  |

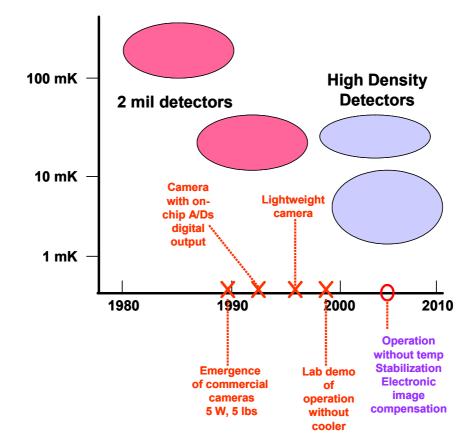

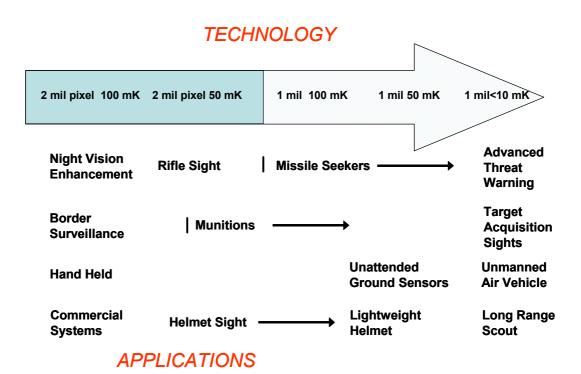

| 1.4 Technological development of uncooled infrared FPAs [12].                                                                                                                                                                                                         | 8  |

| 1.5 System application roadmap for the uncooled infrared FPAs [12]                                                                                                                                                                                                    | 8  |

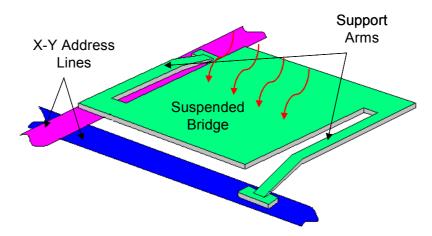

| 1.6 Simplified perspective view of a microbolometer structure obtained using surface micromachining techniques [11].                                                                                                                                                  | 11 |

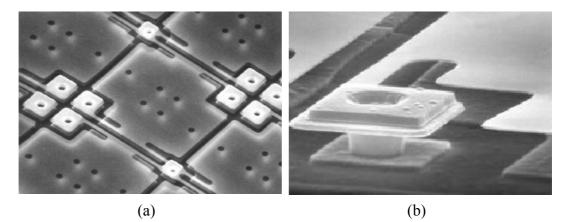

| 1.7 SEM photographs of the a-Si surface micromachined microbolometer detectors: (a) top view and (b) zoomed view of the pixel support arm structure [25].                                                                                                             | 12 |

| 1.8 Simple half-bridge circuit used to measure microbolometer resistance.                                                                                                                                                                                             | 13 |

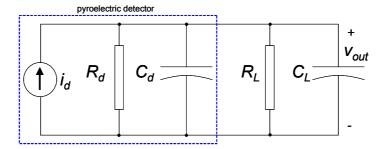

| 1.9 Electrical model of the pyroelectric uncooled detector and its load [36]                                                                                                                                                                                          | 14 |

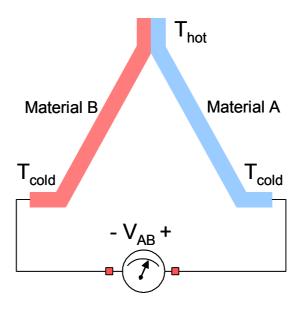

| 1.10 Schematic of a thermocouple.                                                                                                                                                                                                                                     | 16 |

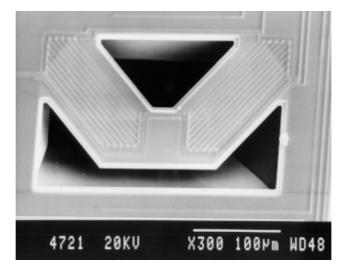

| 1.11 SEM photograph of a semiconductor thermopile structure implemented using 20 n-poly/p <sup>+</sup> active thermocouples in a standard n-well CMOS process developed at METU [50]. The structure measures 325 $\mu$ m × 180 $\mu$ m in a 1.2 $\mu$ m CMOS process. | 17 |

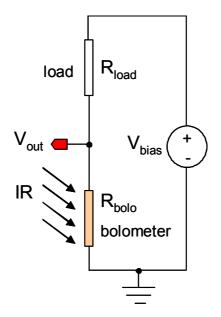

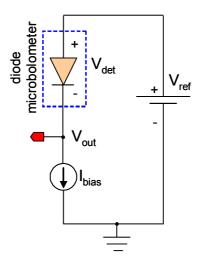

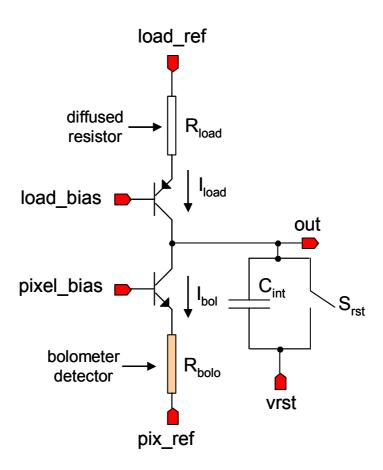

| 1.12 Simple readout circuit used for the diode type microbolometers.                                                                                                                                                                                                  | 18 |

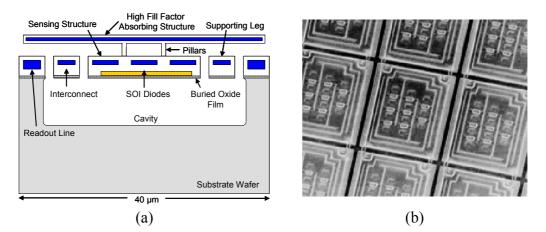

| <ul><li>1.13 SOI diode microbolometer: (a) schematic of the detector cross section and (b) SEM photograph of the fabricated SOI diode array pixels [28]</li></ul>                                                                                                     | 19 |

| 1.14 SEM photograph of the fabricated and post processed $16 \times 16$ n-well microbolometer array [36-38].                                                                                                                                                                                                                                                                                                 | .20 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

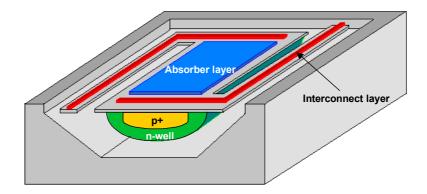

| 1.15 Perspective view of the p <sup>+</sup> -active/n-well diode microbolometer that can be obtained in a standard n-well CMOS process [39].                                                                                                                                                                                                                                                                 | .21 |

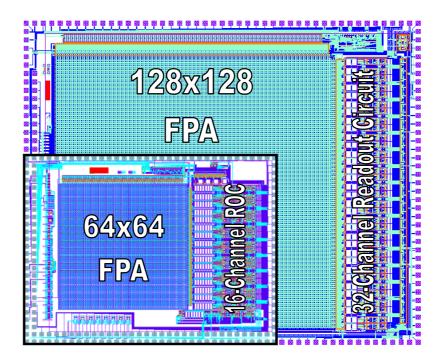

| 1.16 Layout of the fabricated uncooled infrared imager chips with on-chip readout circuitry. The 64 × 64 FPA chip has 16-channel parallel readout circuitry, and it measures 4.1 mm × 5.4 mm in a 0.35 $\mu$ m CMOS process. The 128 × 128 FPA has 32-channel parallel readout circuitry, and it measures 6.6 mm × 7.9 mm in the same process [42].                                                          | .22 |

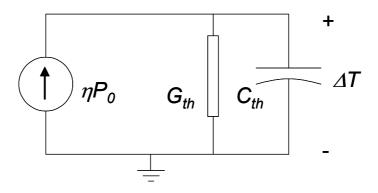

| 2.1 Thermal equivalent circuit of the microbolometer detector                                                                                                                                                                                                                                                                                                                                                | .27 |

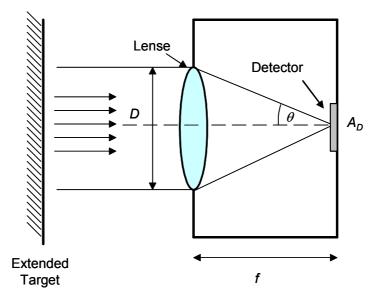

| 2.2 Simplified optical setup used in thermal detection [14]                                                                                                                                                                                                                                                                                                                                                  | .30 |

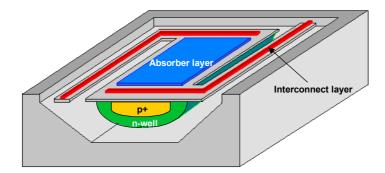

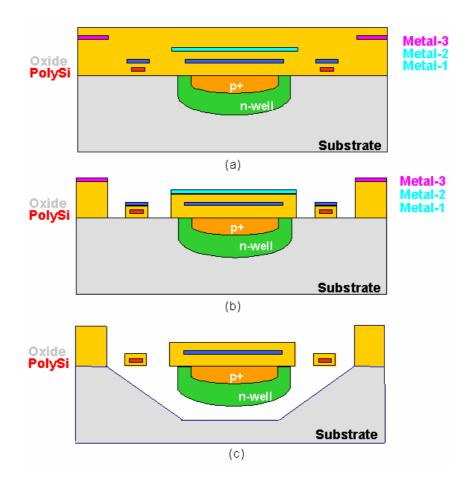

| 3.1 Perspective view of the n-well diode microbolometer that can be obtained in a standard n-well CMOS process [39-42]                                                                                                                                                                                                                                                                                       | .40 |

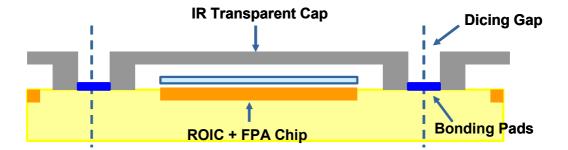

| 3.2 The post-CMOS fabrication steps and the cross-section of the diode pixel structure (a) after CMOS process, (b) after dry etch, and (c) anisotropic silicon etch [39-42, 51].                                                                                                                                                                                                                             | .41 |

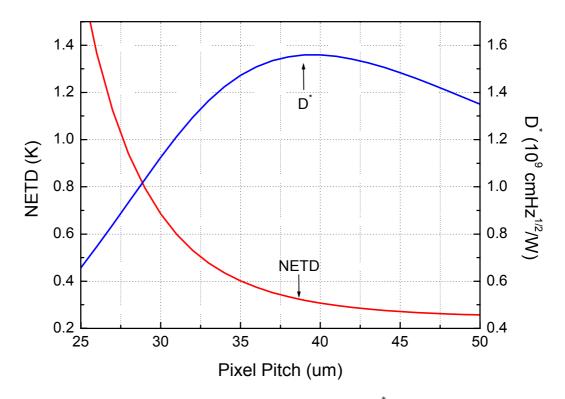

| 3.3 Simulated variation of the NETD and D <sup>*</sup> values with pixel pitch including the required routing in a possible array [39].                                                                                                                                                                                                                                                                      | .44 |

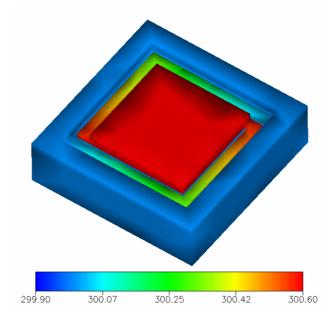

| 3.4 Thermal simulation result obtained using CoventorWare simulation program.                                                                                                                                                                                                                                                                                                                                | .45 |

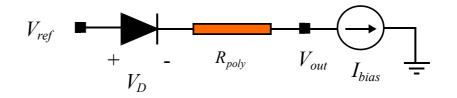

| 3.5 Model of the p <sup>+</sup> -active/n-well diode pixel used in analyzing the temperature coefficient of the pixel voltage when biased at a constant current.                                                                                                                                                                                                                                             | .46 |

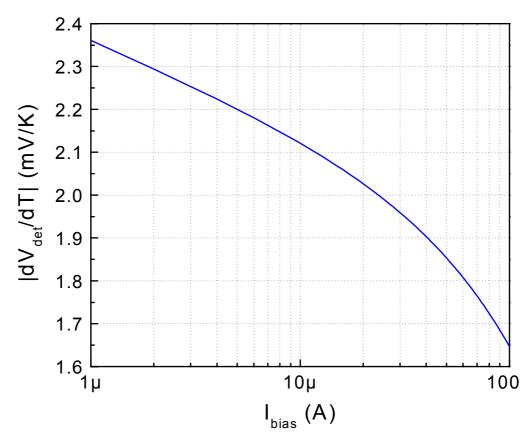

| 3.6 Simulated variation in the magnitude of detector voltage temperature sensitivity $( dV_{det}/dT )$ with pixel bias current $(I_{bias})$ . The magnitude of temperature sensitivity decreases from 2.35 mV/K to 1.65 mV/K when the bias current is increased from 1 $\mu$ A to 100 $\mu$ A.                                                                                                               | .48 |

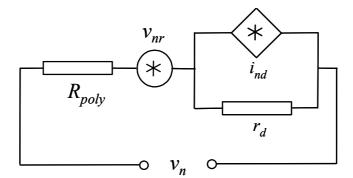

| 3.7 Electrical noise model of the pixel used in the performance analysis [39]                                                                                                                                                                                                                                                                                                                                | .49 |

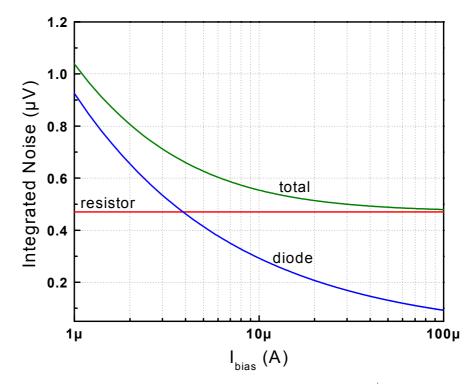

| 3.8 Simulated variation of noise components for the p <sup>+</sup> -active /n-well diode microbolometer for 4 kHz bandwidth at different bias levels. Noise contribution of the interconnect resistor and p <sup>+</sup> -active/n-well diode are also plotted separately [39].                                                                                                                              | .51 |

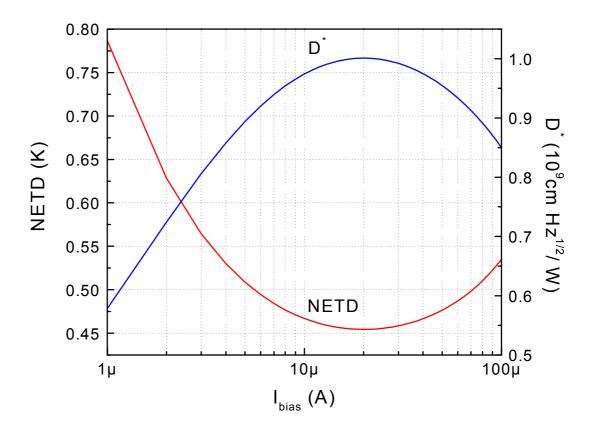

| 3.9 Simulated variation of the NETD and $D^*$ values of the p <sup>+</sup> -active/n-well diode type microbolometer for different bias levels ( $I_{bias}$ ) for 4 kHz bandwidth. Optimum performance is achieved at 20 $\mu$ A with NETD and $D^*$ values of 470 mK and $9.7 \times 10^8$ cm $\sqrt{Hz}/W$ , respectively. In this simulation the detector parameters are taken from the actual measurement |     |

| results of the fabricated 40 $\mu$ m × 40 $\mu$ m detectors, which will be given in Chapter IV.                                                                                                                                                                                                                                                                                                                             | 52 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

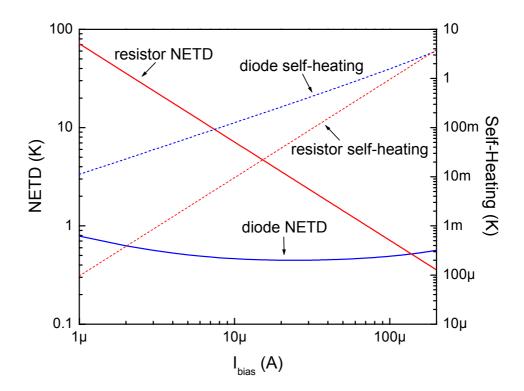

| 3.10 Simulated variation of self-heating and NETD of n-well resistive and p <sup>+</sup> -active/n-well diode type microbolometers [40].                                                                                                                                                                                                                                                                                    | 53 |

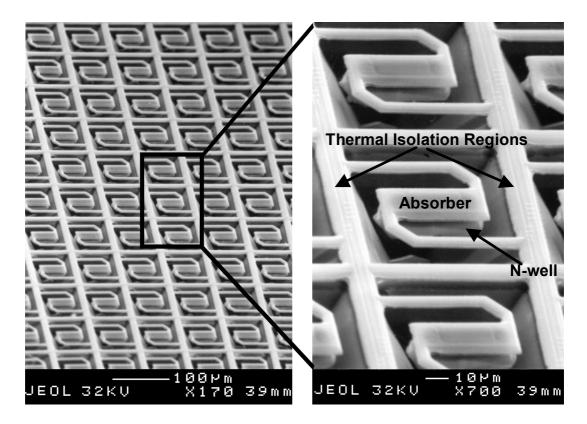

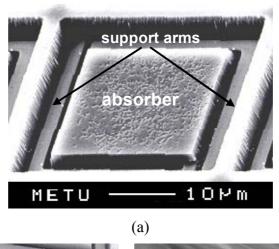

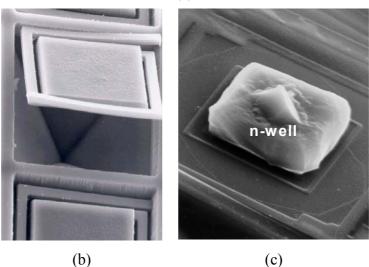

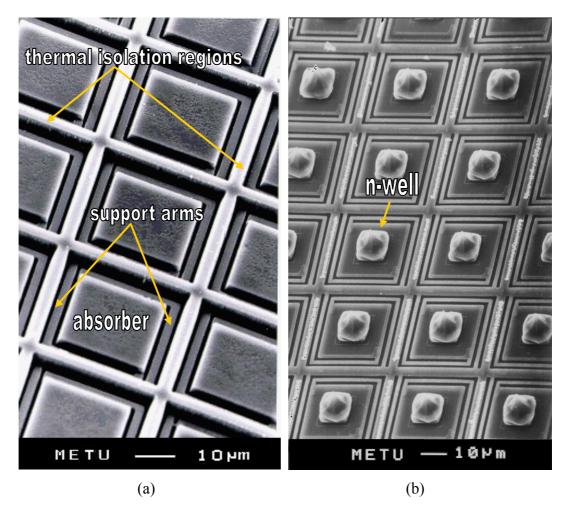

| 4.1 SEM photographs of the post-processed single pixel $p^+$ -active/n-well diode microbolometer using a dry-etch step followed by an electro-chemical etch stop in TMAH solution: (a) top view measuring 40 $\mu$ m × 40 $\mu$ m with a fill-factor of 44 % [43], (b) etched v-groove underneath the pixel, and (c) suspended n-well structure obtained by removing the pixel from the substrate using a sticky-tape [51]. | 57 |

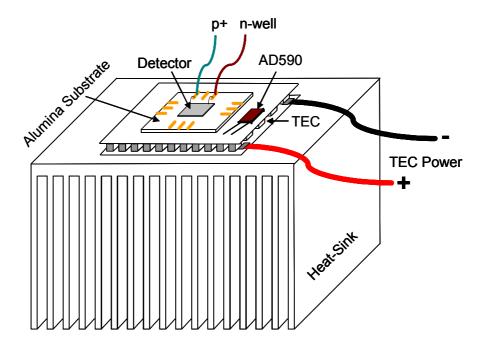

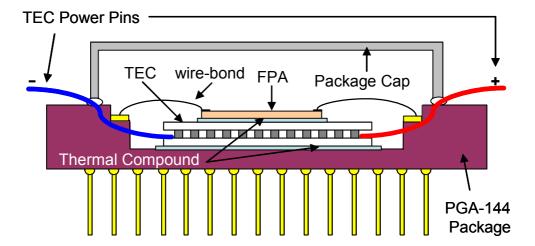

| 4.2 Temperature sensitivity measurement setup using a thermo-electric cooler (TEC) together with a heat-sink and a temperature sensor (AD590)                                                                                                                                                                                                                                                                               | 58 |

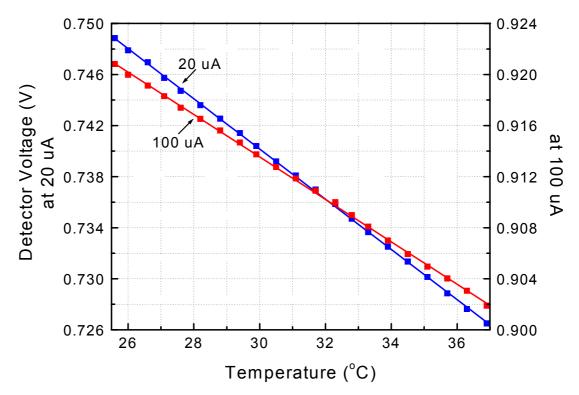

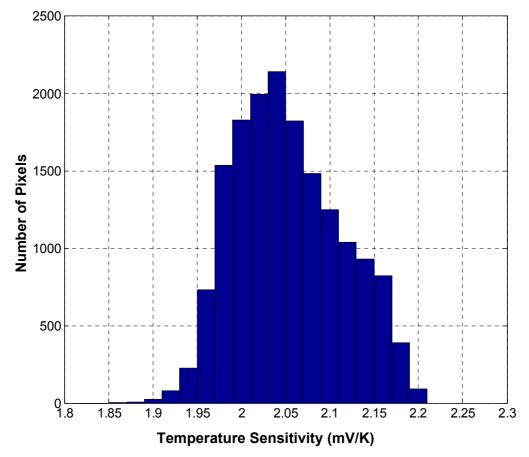

| 4.3 Measured variation of detector voltage with temperature at different detector bias levels. The detector temperature sensitivity is measured as -2 mV/K at 20 $\mu$ A, and sensitivity decreases in magnitude to -1.7 mV/K at 100 $\mu$ A, which is in accordance with the simulation results given in Chapter III [39].                                                                                                 | 59 |

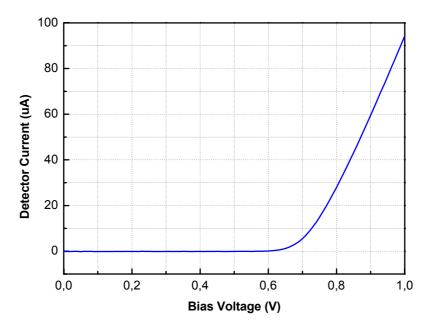

| 4.4 Measured I-V characteristics of the suspended diode type detector operated at room temperature (298 K) and under room pressure level (1 atm). For the sake of simplicity, the data points are not shown, since the bias voltage is applied in small steps of 10 mV [42].                                                                                                                                                | 60 |

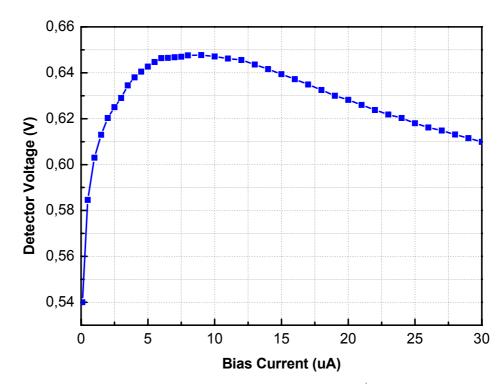

| 4.5 Measured I-V characteristic of the suspended p <sup>+</sup> /n-well active diode type<br>microbolometer detector at 50 mTorr vacuum level biased by a variable<br>current source [42].                                                                                                                                                                                                                                  | 62 |

| 4.6 Test setup used for the infrared responsivity measurement                                                                                                                                                                                                                                                                                                                                                               | 64 |

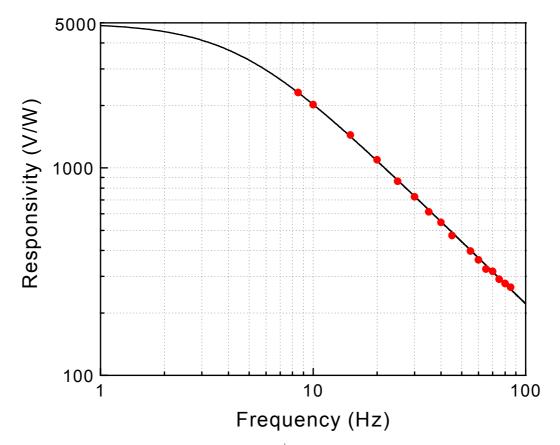

| 4.7 Measured responsivity of the p <sup>+</sup> /n-well active diode type microbolometer detector with respect to infrared modulation frequency from 8.5 Hz to 85 Hz at 80 mTorr vacuum level. The measurement data fits into a single-pole frequency response, and the DC responsivity and the thermal time constant values of the detector are extracted as 4970 V/W and 36 ms, respectively [40, 41].                    | 65 |

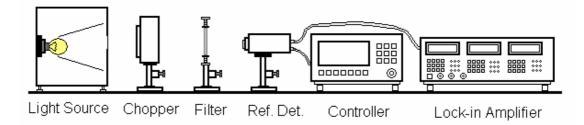

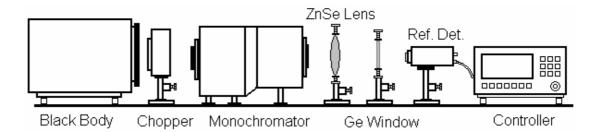

| 4.8 The spectral absorption test setup including a black body, a light chopper, a monochromator, a Zinc Selenide (ZnSe) lens for focusing, a Germanium (Ge) optical filter, and reference detector or p <sup>+</sup> -active/n-well diode type microbolometer detector for testing, and the control unit of the reference detector or a lock-in amplifier.                                                                  | 67 |

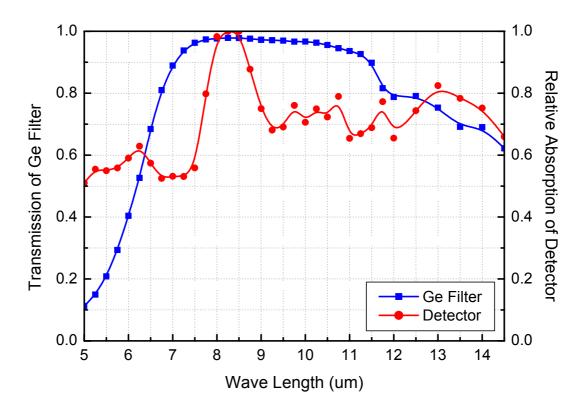

| 4.9 Measured optical transmission of the Ge optical filter and relative spectral absorption of the p <sup>+</sup> -active/n-well diode type microbolometer detector recorded in the 5 $\mu$ m - 14.5 $\mu$ m spectral window.                                                                                                                                                                                               | 68 |

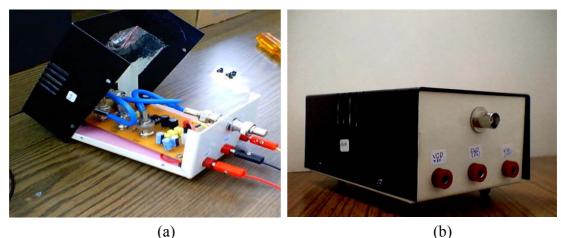

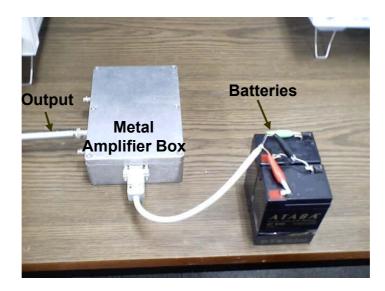

| 4.10 Prepared preamplifier circuit board (a) placed in a metal box (b) to minimize any possible electromagnetic interference.                                                                                                                                                                                             | 69 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

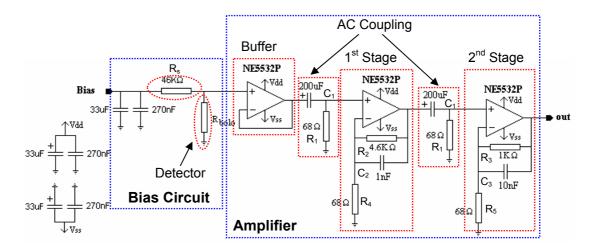

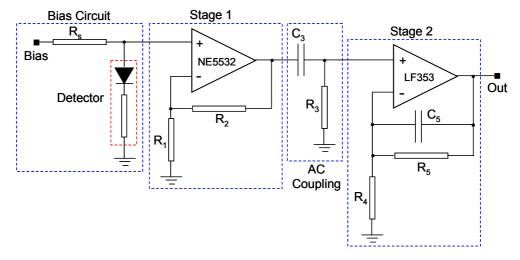

| 4.11 Schematic of the implemented low-noise preamplifier circuit together with the detector bias circuit designed to be used both for the resistive and diode type n-well microbolometers.                                                                                                                                | 70 |

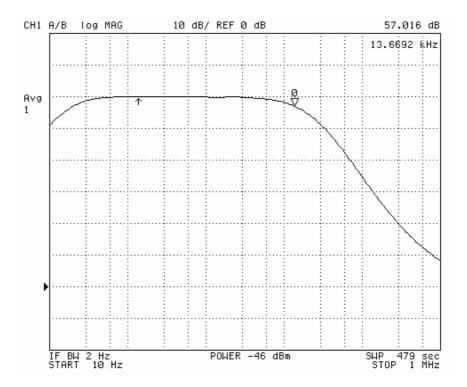

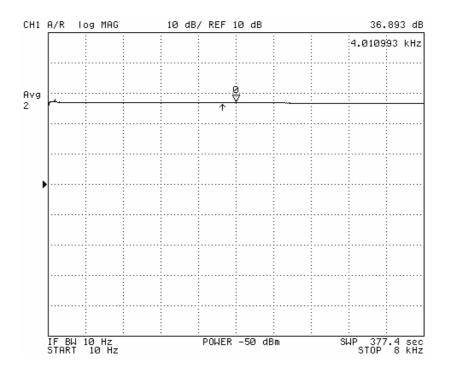

| 4.12 Measured frequency response of the designed preamplifier obtained using HP 4395A. The amplifier has 3 dB points at 10 Hz and 13.7 kHz with a mid-band gain of 60 dB gain                                                                                                                                             | 72 |

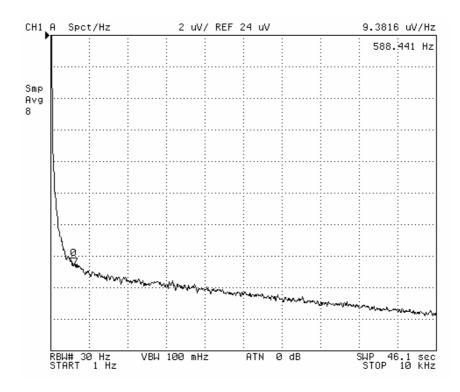

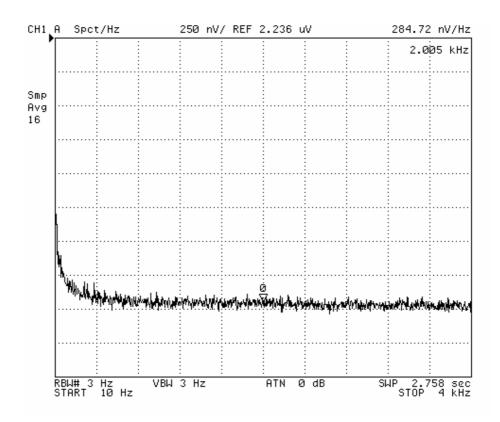

| 4.13 Measured noise spectral density of the preamplifier output when the detector is replaced with a 50 $\Omega$ resistor.                                                                                                                                                                                                | 72 |

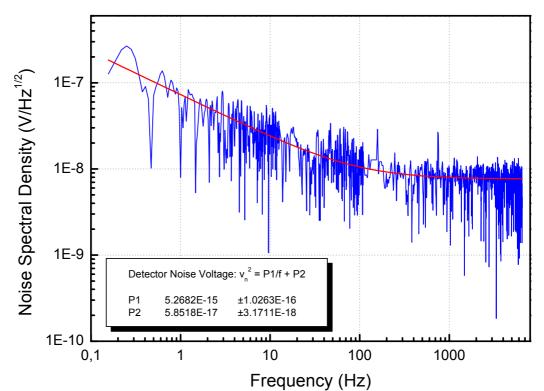

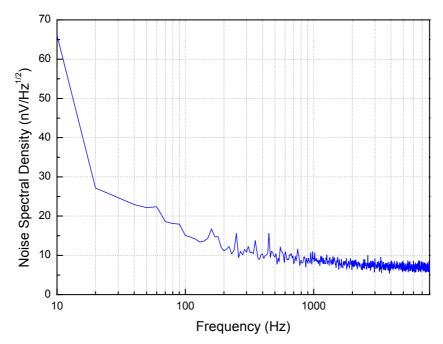

| 4.14 Measured noise spectral density of the p <sup>+</sup> -active/n-well diode type microbolometer detector from 0.1 Hz to 4 kHz at 17 $\mu$ A bias level. Total rms noise voltage from 0.1 Hz to 4 kHz is measured as 0.51 $\mu$ V with a corner frequency of 4.4 Hz.                                                   | 73 |

| 4.15 Schematic of the new low-noise preamplifier circuit composed of a bias circuit and two gain stages.                                                                                                                                                                                                                  | 74 |

| 4.16 Amplifier placed in a metal box for electromagnetic shielding. To achieve low noise, amplifier is powered with 6 V batteries. Bias for the detector is applied using a 1.5 V battery placed inside the box together with the detector to prevent any external interference.                                          | 75 |

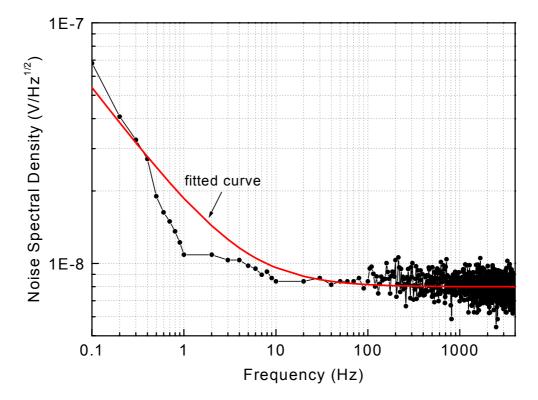

| 4.17 Measured noise spectral density of the diode type microbolometers measured from 0.15 Hz to 6.5 kHz at 17 $\mu$ A bias level. Total rms noise voltage is found as 0.69 $\mu$ V with a corner frequency of 90 Hz.                                                                                                      | 76 |

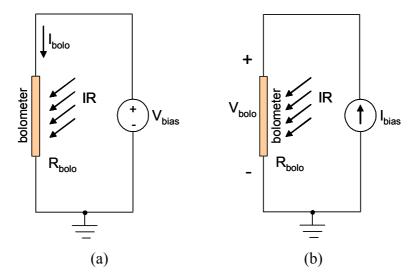

| 5.1 Two basic methods to measure the resistance value of the resistive microbolometer detectors: (a) constant voltage bias-current reading and (b) constant current bias-voltage reading methods.                                                                                                                         | 81 |

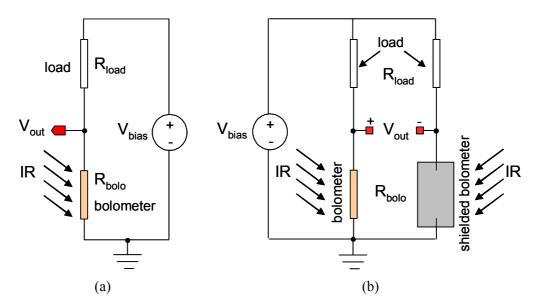

| 5.2 Bridge circuits for the resistive microbolometers: (a) half bridge and (b) full bridge circuits, where $R_{bolo}$ and $R_{load}$ are the resistance of the microbolometer detector and the resistive load, respectively.                                                                                              | 82 |

| 5.3 Schematic of the BCDI preamplifier circuit used for a 320 × 240 resistive microbolometer detector array [61].                                                                                                                                                                                                         | 87 |

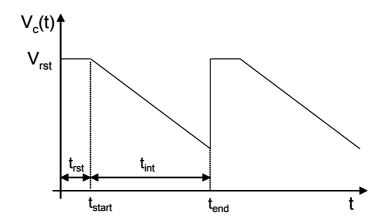

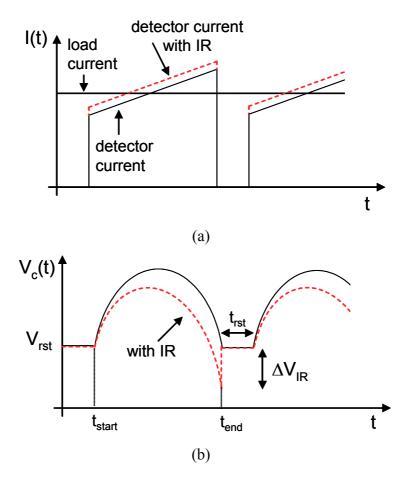

| 5.4 Variation of integration capacitor voltage $(V_c(t))$ in time neglecting self-heating effect. One plate of the integration capacitor is at a reference potential $(V_{rst})$ , and the capacitor is periodically reset for a fixed reset duration of time $(t_{rst})$ before an integration period $(t_{int})$ starts | 89 |

| 5.5 Operation of the BCDI circuit with respect to time including the effect of self-heating and absorbed infrared radiation: (a) variation of bolometer current and (b) integration capacitance voltage [61]                                                                                                              | 91 |

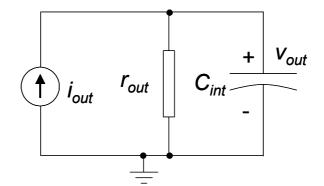

| 5.6 Small signal model of the of the output stage                                                                                                                                                                                                                                       | 92  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

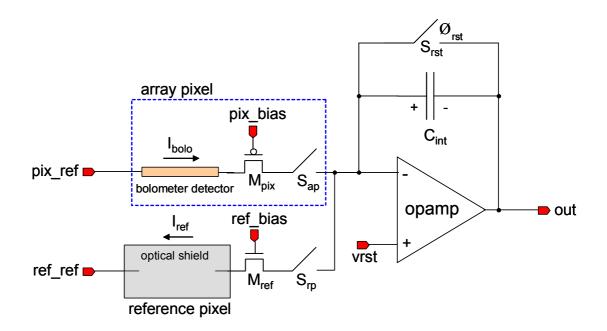

| 5.7 Simplified schematic of a preamplifier circuit called capacitive transimpedance amplifier (CTIA), which is commonly used in the readout circuits of the resistive uncooled detector arrays [25].                                                                                    | 94  |

| 5.8 Noise sources in the CTIA circuit with direct injection biasing circuits composed of a MOS transistor, detector resistance, and an opamp integrator circuit.                                                                                                                        | 96  |

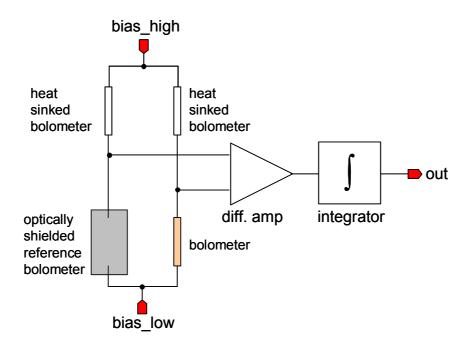

| 5.9 Schematic of the Wheatstone type differential readout circuit used in a modern 640 × 480 uncooled microbolometer FPA [21].                                                                                                                                                          | 99  |

| 5.10 Simplified schematic of the preamplifier using a constant current bias circuit with a differential transconductance amplifier [58]                                                                                                                                                 | 101 |

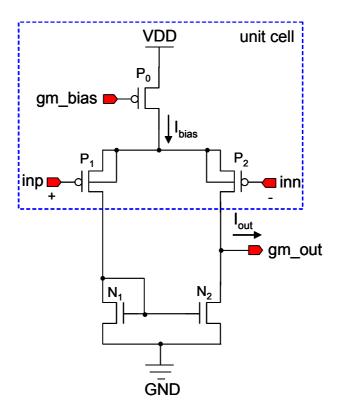

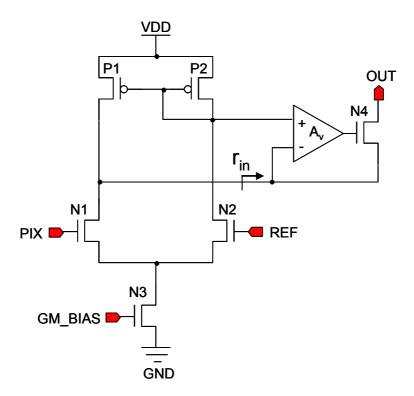

| 5.11 Schematic of the differential transconductance amplifier used in the constant current preamplifier circuit [58].                                                                                                                                                                   | 102 |

| 5.12 Schematic of the improved differential transconductance amplifier used in the CCBDI preamplifier structure [58].                                                                                                                                                                   | 103 |

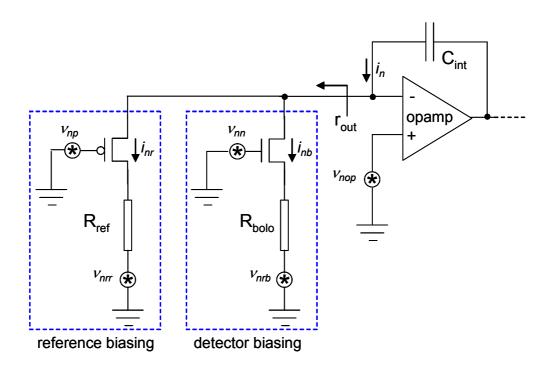

| 5.13 Noise model of the CCBDI amplifier circuit.                                                                                                                                                                                                                                        | 103 |

| <ul><li>5.14 Schematic view of the preamplifier used in the 320 × 240 SOI diode FPA [28]. This preamplifier structure is called gate modulation integration (GMI) circuit.</li></ul>                                                                                                    | 107 |

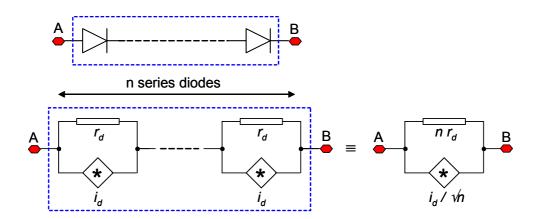

| 5.15 Noise model of the series diodes                                                                                                                                                                                                                                                   | 108 |

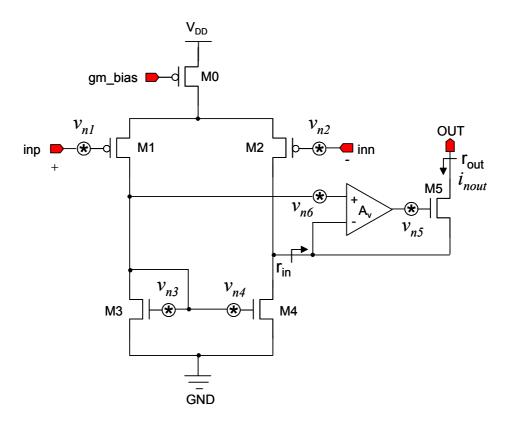

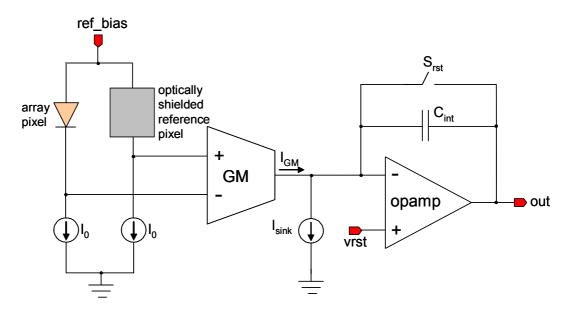

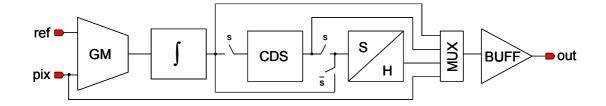

| 5.16 Simplified schematic of the preamplifier used in the 64 × 64 and 128 × 128 n-well diode type FPAs [41-42]. This preamplifier is the combination of the CCBDI and CTIA structures, and it is called differential buffered injection-capacitance transimpedance amplifier (DBI-CTIA) | 112 |

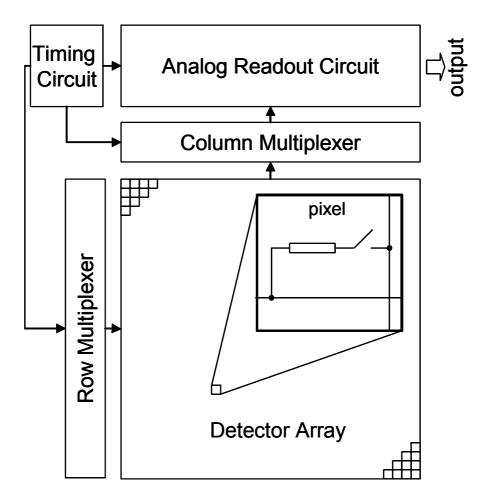

| 5.17 Block diagram of the readout circuit used for most of the uncooled infrared detector arrays.                                                                                                                                                                                       | 114 |

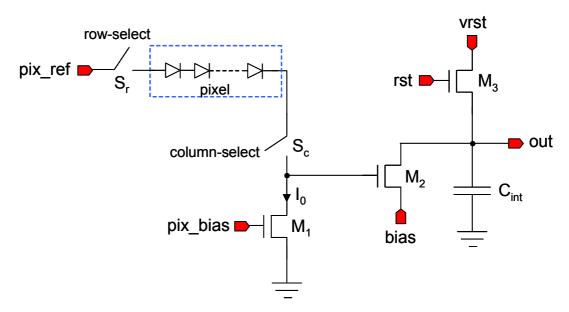

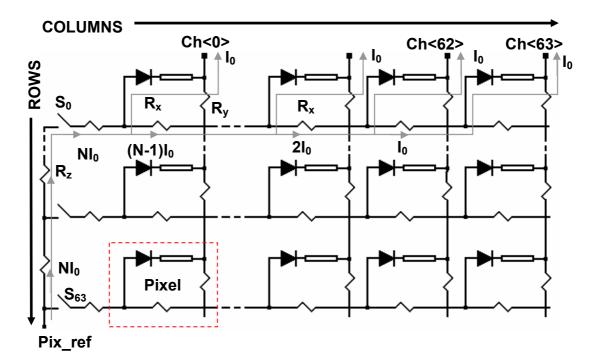

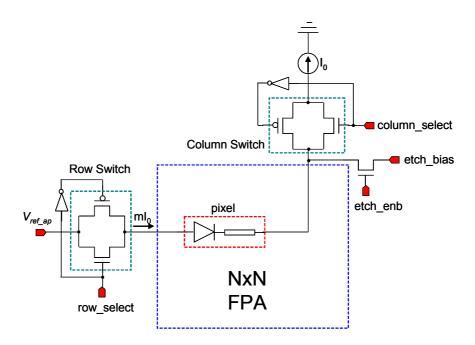

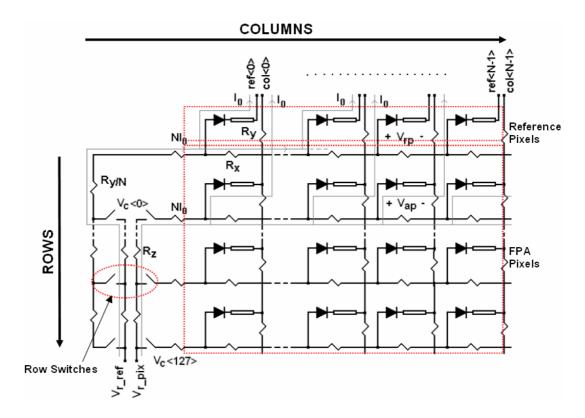

| 6.1 Simplified schematics of the $64 \times 64$ FPA.                                                                                                                                                                                                                                    | 122 |

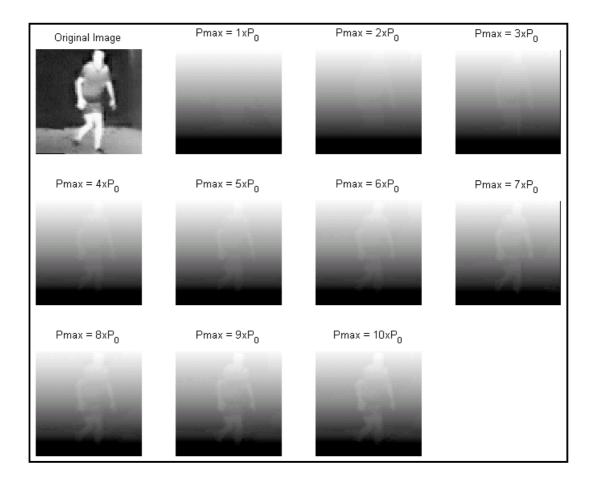

| 6.2 Simulated effect of FPA routing resistance on the infrared image                                                                                                                                                                                                                    | 125 |

| 6.3 Layout of the reference detector array with its biasing circuitry, which measures 680 $\mu$ m × 300 $\mu$ m in a 3-metal 2-poly 0.35 $\mu$ m CMOS process                                                                                                                           | 127 |

| 6.4 Readout architecture of the $64 \times 64$ FPA                                                                                                                                                                                                                                      | 128 |

| 6.5 Block diagram of the analog channel readout circuit in the $64 \times 64$ FPA                                                                                                                                                                                                       | 130 |

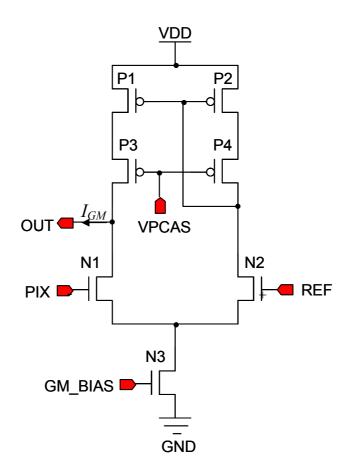

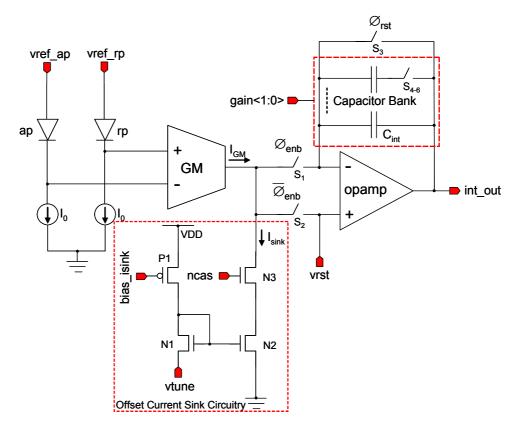

| 6.6  | Schematic of the low-noise differential transconductance amplifier used in the $64 \times 64$ FPA chip                                                                                                                                                                                                                                                                                                                         |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

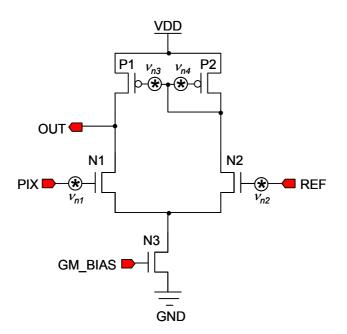

| 6.7  | Simplified schematic of the differential transconductance amplifier with important noise sources                                                                                                                                                                                                                                                                                                                               |

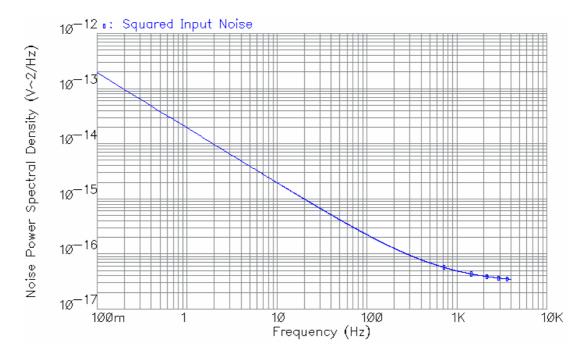

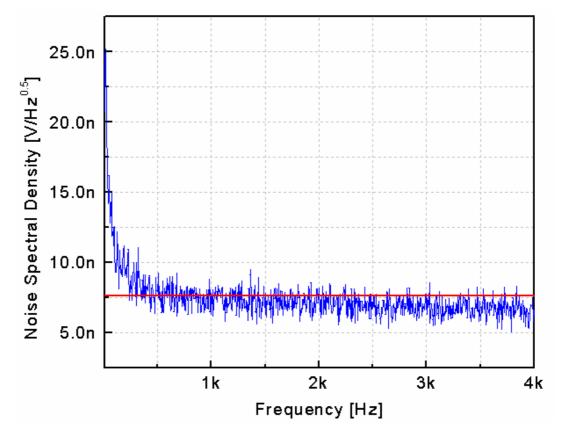

| 6.8  | Simulated input referred noise power spectral density of the differential transconductance amplifier from 100 mHz to 4 kHz. Total rms noise voltage is extracted as $0.57 \ \mu V$ in 4 kHz bandwidth                                                                                                                                                                                                                          |

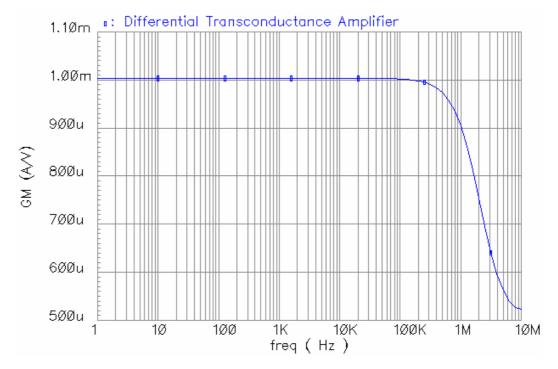

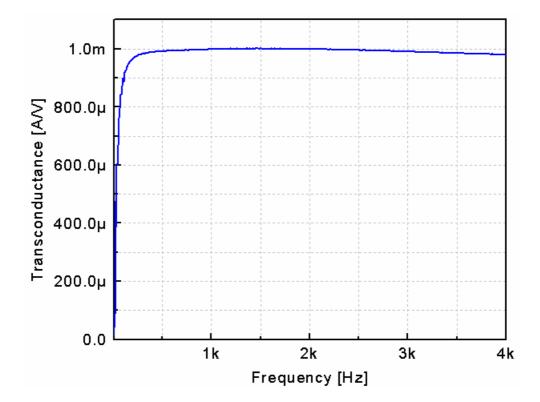

| 6.9  | Simulated transconductance value of the differential transconductance amplifier designed for the $64 \times 64$ FPA. The simulated transconductance value is 1004 $\mu$ A/V with a 3 dB corner frequency of 2.45 MHz well above the 4 kHz bandwidth of the $64 \times 64$ FPA.                                                                                                                                                 |

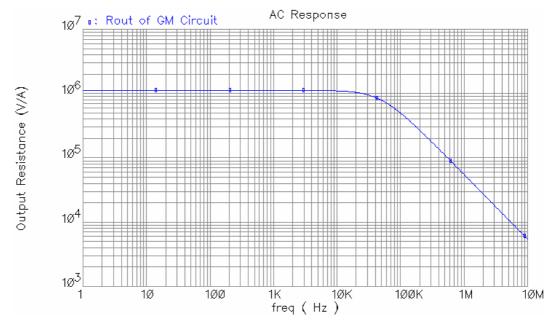

| 6.10 | Simulated small signal output resistance of the differential transconductance amplifier. Output resistance is larger than 1 M $\Omega$ for frequencies less than 20 kHz                                                                                                                                                                                                                                                        |

| 6.11 | Simulated variation of transconductance value with operating temperature. The result is obtained using AC analysis at different temperatures from 0 $^{\circ}$ C to 50 $^{\circ}$ C. The temperature sensitivity of the transconductance value is extracted as -4.6 $\mu$ A/V/K, which corresponds to a temperature coefficient of 0.46 %/K.                                                                                   |

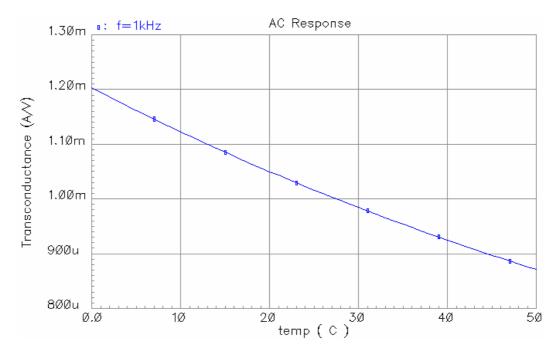

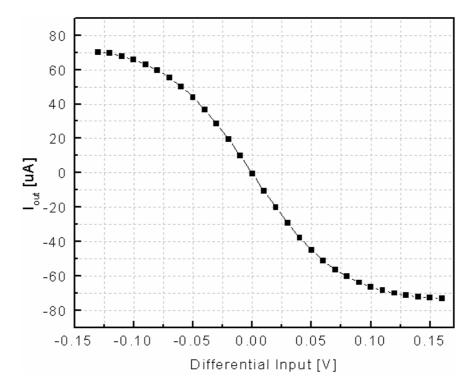

| 6.12 | 2 DC simulation result of the output current ( $I_{GM}$ ) with respect to differential input voltage ( $V_{rp}$ - $V_{ap}$ )                                                                                                                                                                                                                                                                                                   |

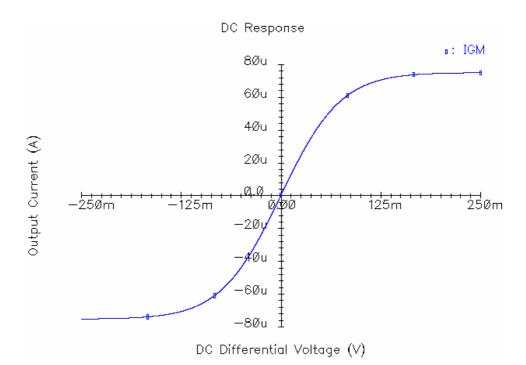

| 6.13 | Simulated variation of the offset current of the differential transconductance amplifier with respect to operating temperature from 0 °C to 50 °C. Differential voltage is set to 0 V, and offset at room temperature (27 °C) is about 530 nA.                                                                                                                                                                                 |

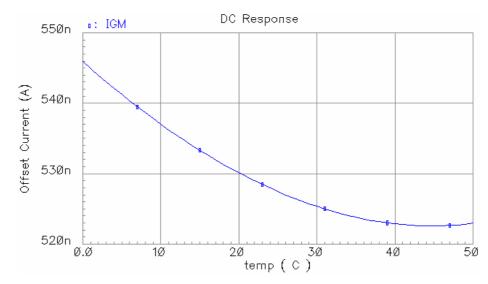

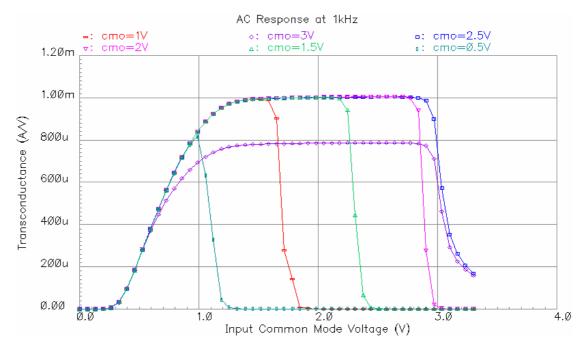

| 6.14 | Simulated variation of the transconductance value with respect to input<br>common mode voltage swept for different output common mode voltage<br>values. This data is obtained by performing AC analysis at 1 kHz for<br>different input and output DC voltage levels. Input common mode is swept<br>rail-to-rail, while output common mode voltage is simulated at discrete<br>points from 0.5 V to 3.0 V in six linear steps |

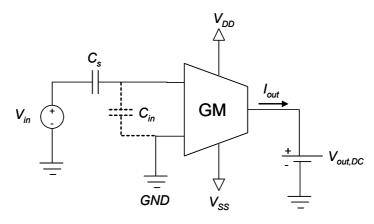

| 6.15 | Simulated circuit schematic used to determine the input capacitance $(C_{in})$ of the GM circuit                                                                                                                                                                                                                                                                                                                               |

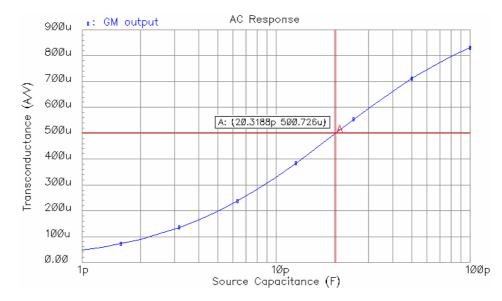

| 6.16 | Simulated variation of overall transconductance with varying source capacitance. The value of $C_s$ at which the gain drops to half of the original value is equal to the value of the input capacitance value ( $C_{in}$ ). The input capacitance for a single input is determined as 20.3 pF                                                                                                                                 |

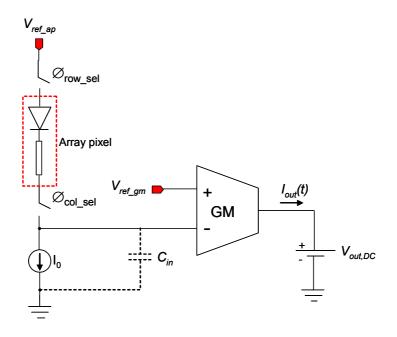

| <ul><li>6.17 Simplified schematic of the input stage showing the pixel select circuitry with the row and column select switches, the constant current source, and the GM circuit.</li></ul>                                                                                                                                                                                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

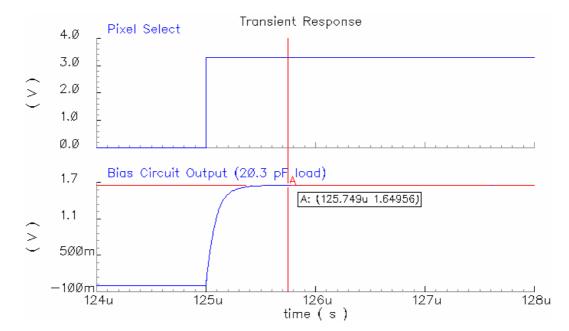

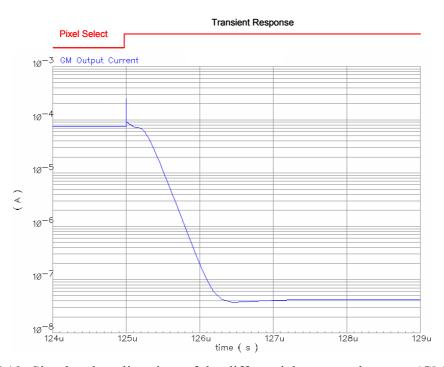

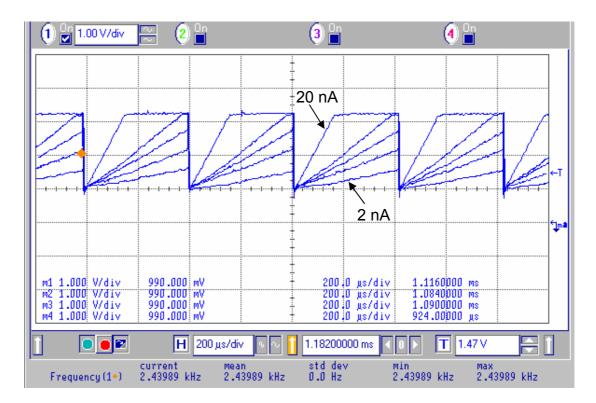

| 6.18 Simulated transient response of the bias and pixel select circuitry when driving a 20.3 pF load equivalent to that of the input capacitance of the GM circuit. The time required for the transient to decay is recorded as 0.75 μs142                                                                                                                                                                             |

| 6.19 Simulated settling time of the differential transconductance (GM) output current upon an applied pixel select pulse (at t=125 μs), and output reaches its steady state value within 2 μs                                                                                                                                                                                                                          |

| 6.20 Layout of the input differential pair used in the low-noise differential transconductance amplifier in the $64 \times 64$ FPA. The transistors have <i>W/L</i> values of 4250 $\mu$ m / 3.5 $\mu$ m implemented using 35 identical gates laid out in an interdigitated manner for improved matching purposes [72]. It measures 155 $\mu$ m × 387 $\mu$ m in a 3-metal 2-poly 0.35 $\mu$ m CMOS process145         |

| 6.21 Layout of the load and bias transistors of the differential transconductance amplifier used in the 64 $\times$ 64 FPA. It also includes the offset removal circuitry together with integration enable switches. For matching purposes transistor pairs are laid out symmetrically in an interdigitated manner. The layout measures 140 $\mu$ m $\times$ 158 $\mu$ m in a 3-metal 2-poly 0.35 $\mu$ m CMOS process |

| 6.22 Simplified block diagram of the switched capacitor integrator (SCI) circuit together with the offset current sink circuitry, differential transconductance amplifier, and detector bias circuit                                                                                                                                                                                                                   |

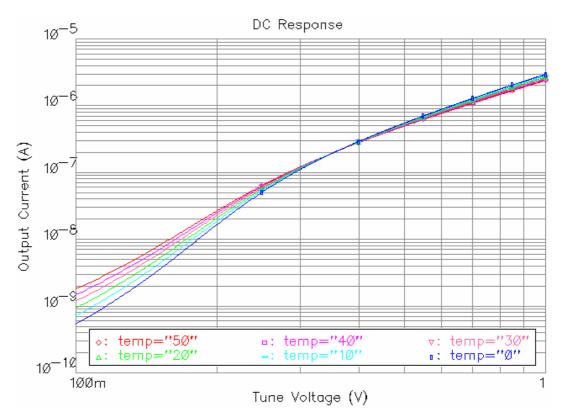

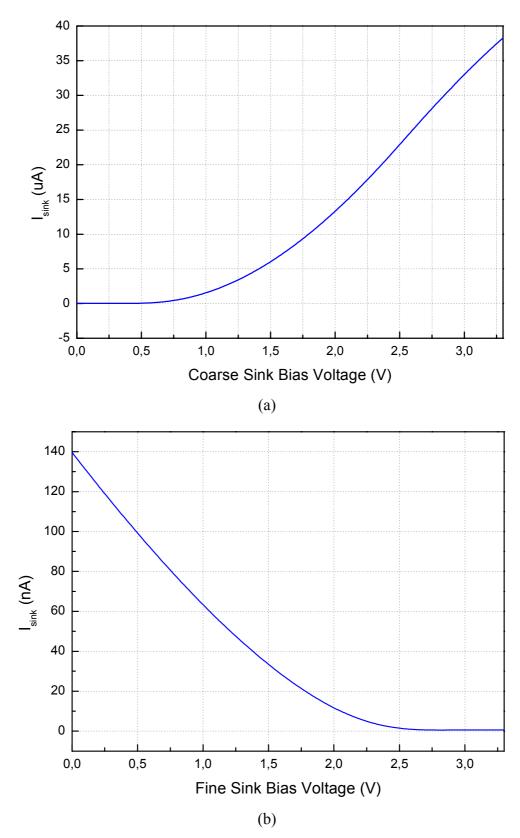

| 6.23 Simulated variation of the output current of the offset current sink circuitry with respect to the tune voltage ( $V_{tune}$ ) at different operating temperatures ranging from 0 °C to 50 °C. The circuit is designed to cancel the offset current values as low as 1 nA                                                                                                                                         |

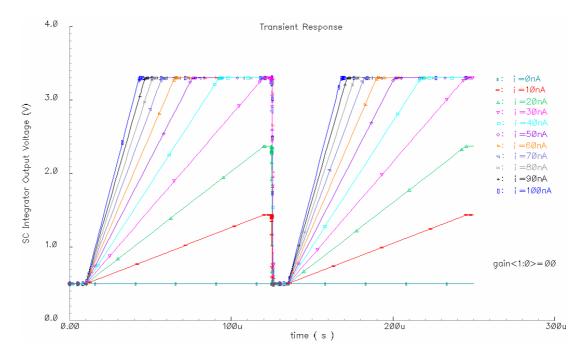

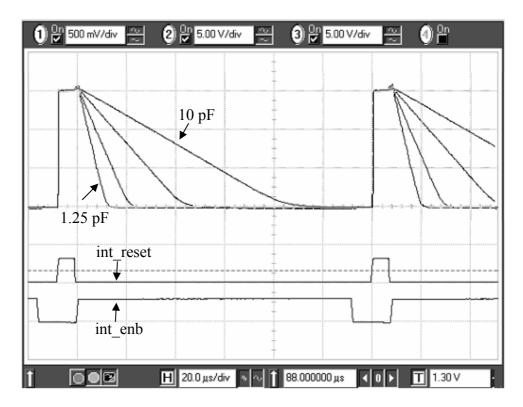

| 6.24 Transient simulation result of the SCI at different input current levels ranging from 0 nA to 100 nA. Integration gain is set to its maximum value by selecting long integration (110 $\mu$ s) and the minimum integration capacitance (1.25 pF when <i>gain</i> <1:0> = 00)                                                                                                                                      |

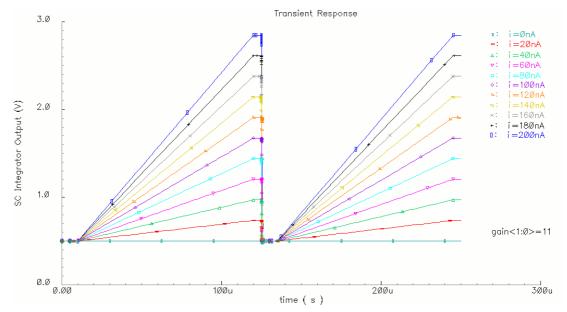

| 6.25 Transient simulation result of the SCI at different input current levels ranging from 0 nA to 200 nA. Integration capacitance is set to its maximum value (10 pF when $gain < 1:0 > = 11$ ), and long integration is used                                                                                                                                                                                         |

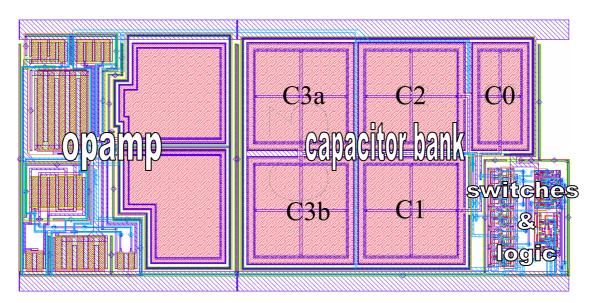

| <ul><li>6.26 Layout of the variable gain switched capacitor integrator circuit. It is composed of an opamp, a capacitor bank, switches, and digital circuitry for gain control.</li></ul>                                                                                                                                                                                                                              |

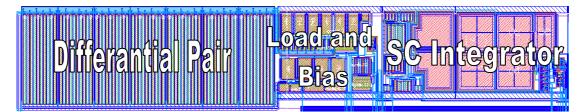

| 6.27 Layout of the input stage of the channel readout circuit. It is composed of the differential pair of the GM stage, the load and bias transistors of the GM stage placed in the middle together with the offset removal circuitry, and the variable gain switched capacitor integrator circuit                                                                                                                            | 54 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

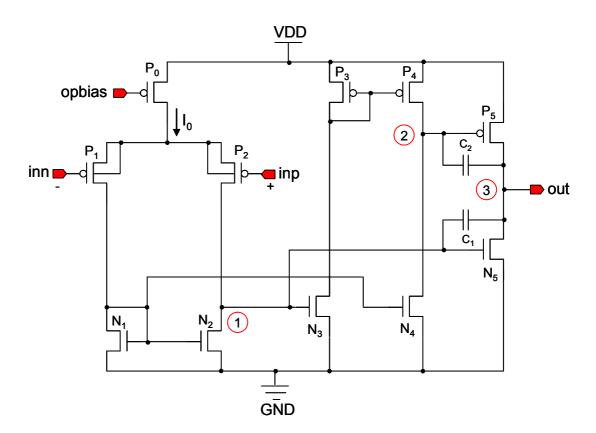

| 6.28 Schematic of the opamp used in various places in the FPA readout [73]15                                                                                                                                                                                                                                                                                                                                                  | 55 |

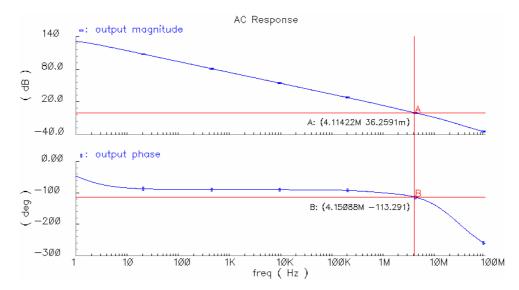

| 6.29 Simulated gain and phase plot of the compensated opamp. Low frequency open loop gain of the opamp when driving a 1 pF load is recorded as 131 dB with a unity gain frequency of 4.1 MHz with a phase margin of 67 °. Markers show the data points where the gain is about unity (0 dB)15                                                                                                                                 | 59 |

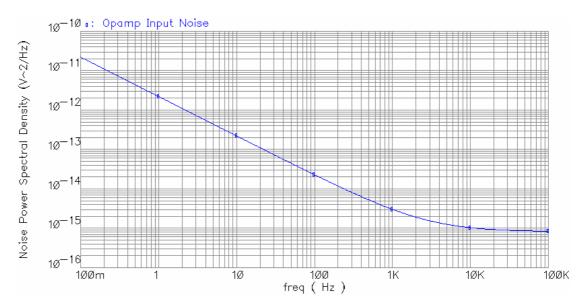

| 6.30 Simulated opamp input noise power spectral density from 0.1 Hz to 100 kHz. Total rms noise in 4 kHz bandwidth is simulated as 5.16 $\mu$ V, which has an average noise spectral density of 81 nV/ $\sqrt{Hz}$ . For 8 kHz bandwidth, total integrated noise is found as 5.6 $\mu$ V with a density of 63 nV/ $\sqrt{Hz}$ . For wide bandwidth applications noise spectral density becomes less than 30 nV/ $\sqrt{Hz}$ . | 62 |

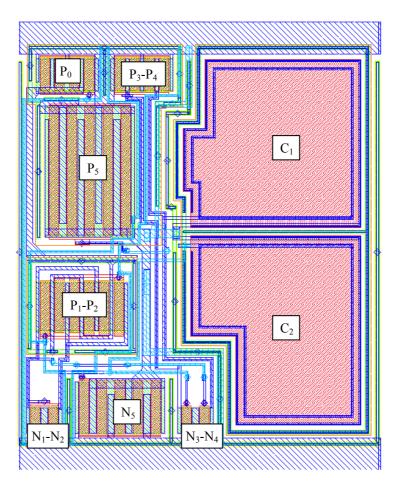

| 6.31 Layout of the designed opamp. It measures 140 μm × 113 μm in a 3-metal 2-poly 0.35 μm CMOS process                                                                                                                                                                                                                                                                                                                       | 64 |

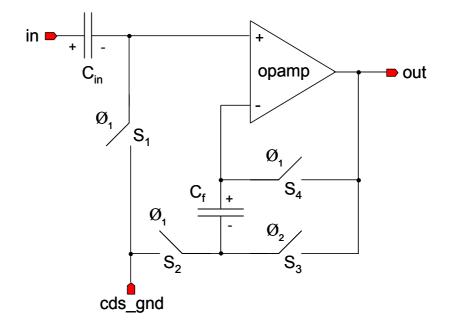

| 6.32 Simplified schematic view of the switched capacitor correlated double sampling (CDS) circuit used in the 64 × 64 FPA readout circuit                                                                                                                                                                                                                                                                                     | 65 |

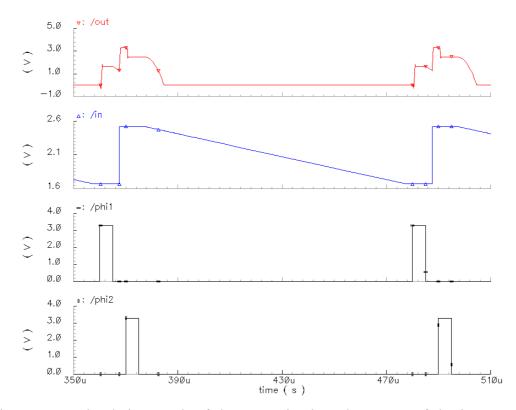

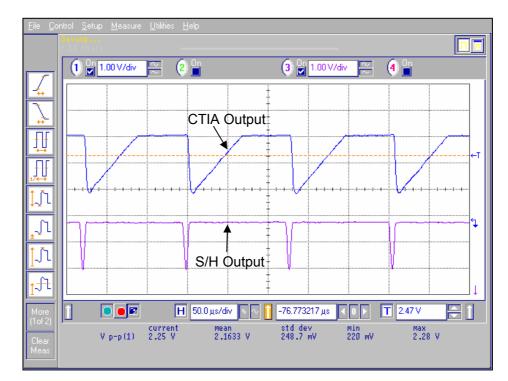

| 6.33 Simulation result of the CDS circuit. The output of the integrator is connected to the input of the CDS circuit. The circuit is capable to cancel the offset at the input and at the integrator output.                                                                                                                                                                                                                  | 66 |

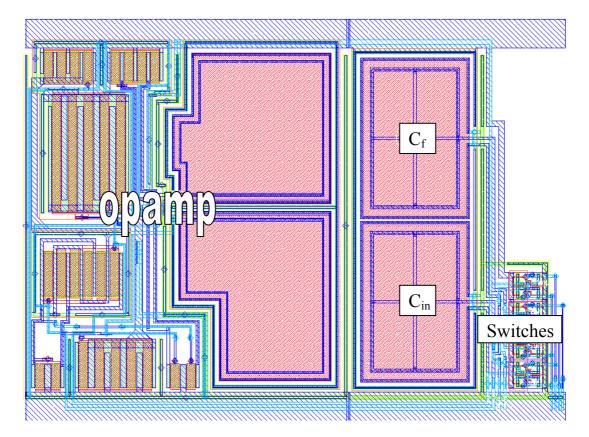

| 6.34 Layout of the CDS circuit. It is composed of an opamp, two sampling capacitors ( $C_{in}$ and $C_f$ ), and four analog CMOS switches with dummy transistors. The layout measures 140 $\mu$ m × 190 $\mu$ m in a 3-metal 2-poly 0.35 $\mu$ m CMOS process.                                                                                                                                                                | 67 |

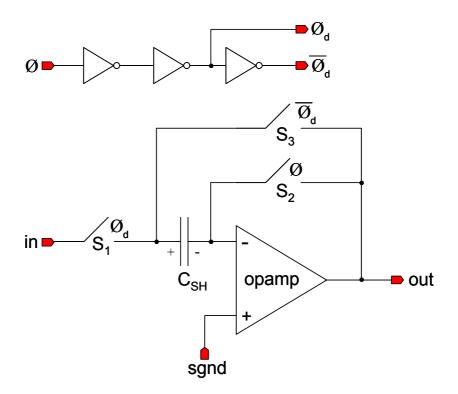

| 6.35 Simplified schematic of the switched capacitor sample-and-hold (S/H) circuit with offset cancellation feature used in the 64 × 64 FPA readout circuit [63]. The CMOS switches are controlled by three different timing signals ( $\emptyset$ , $\emptyset_d$ , and its complement $\overline{\Phi}_d$ ), which are generated from a single clock signal by a simple inverter circuit.                                    | 68 |

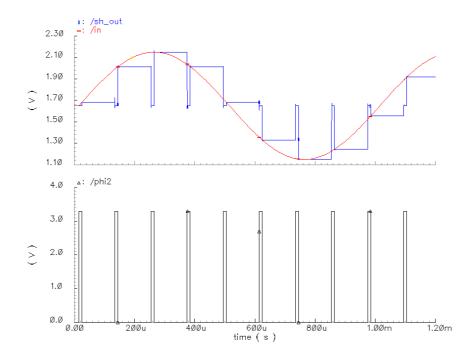

| 6.36 Simulation result of the S/H amplifier. The input ( <i>in</i> ) is a 1 V peak-to-peak sine wave at 1 kHz with DC value of 1.65 V. The circuit samples the input signal and holds it at the output at the positive and negative edges of the applied clock signal ( $\emptyset = phi2$ ), respectively                                                                                                                    | 69 |

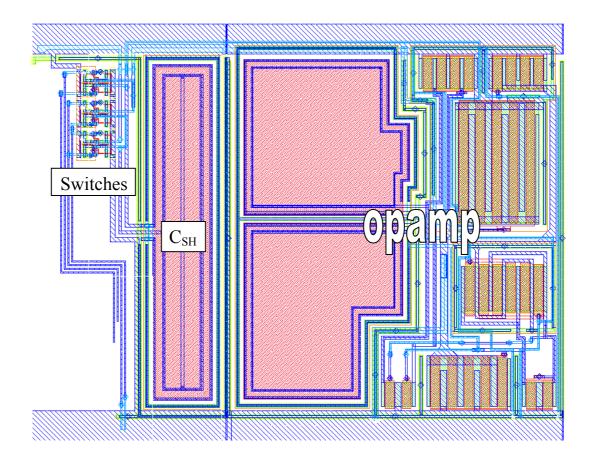

| 6.37 shows the layout of the S/H circuit. It is composed of an opamp, a sampling capacitor ( $C_{SH}$ ), and three analog CMOS switches with dummy transistors. The layout measures 140 $\mu$ m × 170 $\mu$ m in a 3-metal 2-poly 0.35 $\mu$ m CMOS process. The layout has been flipped vertically in order to                                                                                                               |    |

|      | utilize the unused area on top of the CDS switches when the two blocks are placed next to each other.                                                                                                                                                                                                                                                                 | .170 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 6.38 | Layout of the S/H circuit. It is composed of an opamp, a sampling capacitor (CSH), and three analog CMOS switches with dummy transistors. The layout measures 140 $\mu$ m × 170 $\mu$ m in a 3-metal 2-poly 0.35 $\mu$ m CMOS process.                                                                                                                                | .170 |

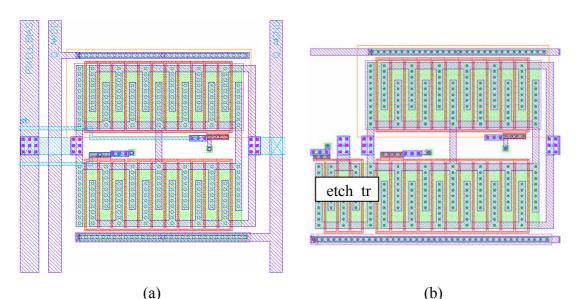

| 6.39 | Layout of the analog CMOS switches used in the (a) row and (b) column multiplexer circuitry. Column select switches have also an additional n-cannel transistor used to bias the n-wells of the array pixels during electro-chemical etching. The designed $W/L$ ratio of the p-channel and n-channel transistors in the analog switches is $120 \mu m / 0.3 \mu m$ . | .171 |

| 6.40 | Simplified schematic of the FPA addressing circuit together with the etch transistors. During etching the <i>etch_enb</i> signal is high, and all the cathodes (n-well connections) of the array pixels are shorted to a common bias potential ( <i>etch_bias</i> ) that prevents etching of the n-well.                                                              | .172 |

| 6.41 | Block diagram of the $64 \times 64$ FPA readout circuit including the array pixels, row and column multiplexers, the 16-channel parallel analog readout circuit, and the output multiplexer, which all are controlled by the digital circuit.                                                                                                                         | .173 |

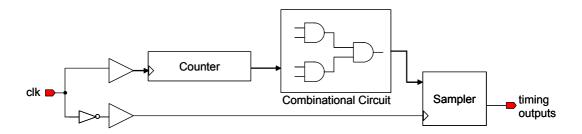

| 6.42 | Block diagram of the digital timing circuit composed of a synchronous counter, a combinational circuit that generates the required timing signals using the counter outputs, and a sampling circuit which is operating at the negative clock edge.                                                                                                                    | .174 |

| 6.43 | Internal register content of the 15-bit counter                                                                                                                                                                                                                                                                                                                       | .175 |

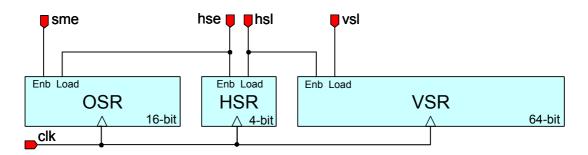

| 6.44 | Block diagram of the shift registers of OSR, HSR, and VSR together with their common control signals of <i>sme</i> , <i>hse</i> , <i>hsl</i> , and <i>vls</i> . The <i>hse</i> and <i>hsl</i> signals for the HSR are in common with the OSR's load ( <i>Load</i> ) signal and VSR's ( <i>Enb</i> ) enable signal, respectively.                                      | .177 |

| 6.45 | Verilog-XL simulation result showing the generation of the <i>hsl</i> and <i>vsl</i> pulses.                                                                                                                                                                                                                                                                          | .178 |

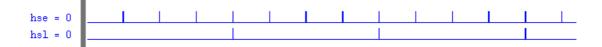

| 6.46 | Verilog-XL simulation result showing the generation of the <i>hse</i> and <i>hsl</i> signals. The frequency of <i>hsl</i> is $1/4^{th}$ of the frequency of <i>hse</i>                                                                                                                                                                                                | .179 |

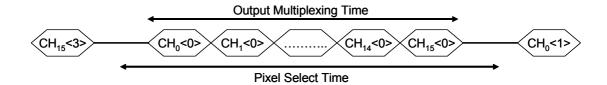

| 6.47 | Timing diagram of the serial output multiplexer. Within a pixel select time, S/H outputs of 16 channels are multiplexed to the serial output.                                                                                                                                                                                                                         | .179 |

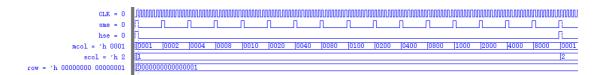

| 6.48 | Verilog-XL simulation result showing the generation of timing signals for the OSR. <i>CLK</i> is the system clock, <i>sme</i> is the enable signal and <i>hse</i> is the load signals for this register. <i>Mcol</i> is the content of the OSR, <i>scol</i> is the content of the 4-bit HSR, and row is the content of the VSR.                                       | .180 |

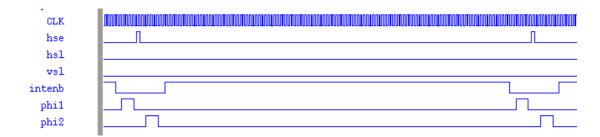

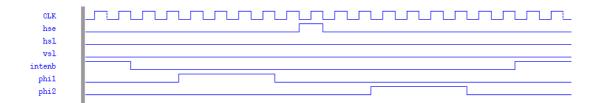

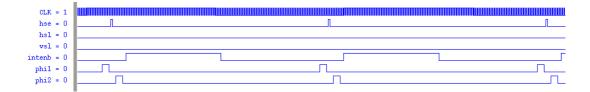

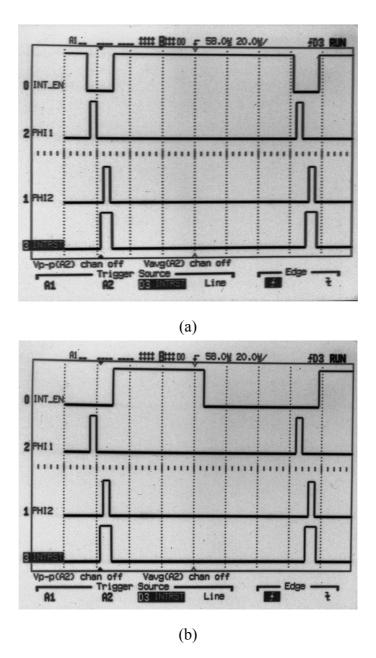

| 6.49 Verilog-XL simulation result showing the generation of the <i>intenb</i> , <i>phi1</i> , and <i>phi2</i> with respect to pixel select control signals such as <i>hse</i> , <i>hsl</i> , and <i>vsl</i> .                                                                                                                                                                                                                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.50 Zoomed simulation view showing the generation of timing signals for analog circuits                                                                                                                                                                                                                                                                                                                                                                             |

| <ul><li>6.51 Verilog-XL simulation result showing generation of the <i>intenb</i> signal when<br/>the integration time is reduced. The <i>intenb</i> pulse is reduced from 112<br/>clock cycles to 56 clock cycles. 56 clock cycles</li></ul>                                                                                                                                                                                                                        |

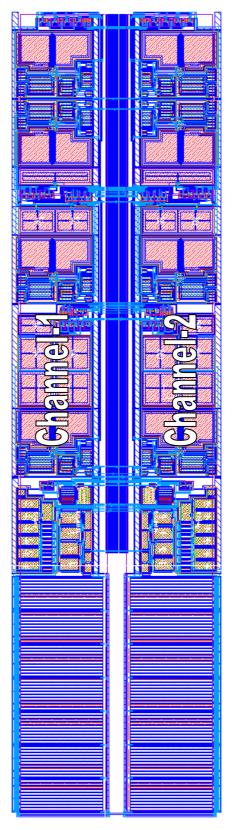

| <ul> <li>6.52 Combined layout of the two identical readout channels (<i>Channel-1</i> and <i>Channel-2</i>). The layout measures 340 μm × 1320 μm in a 3-metal 2-poly 0.35 μm CMOS process.</li> </ul>                                                                                                                                                                                                                                                               |

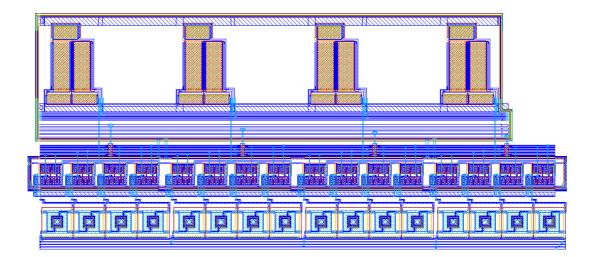

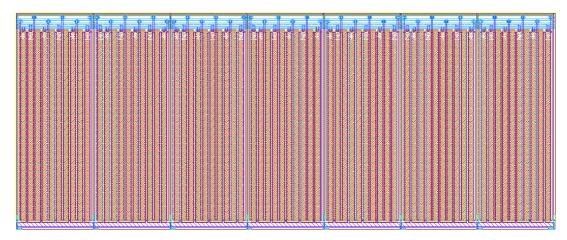

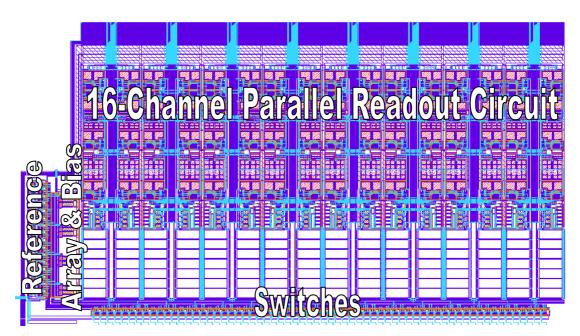

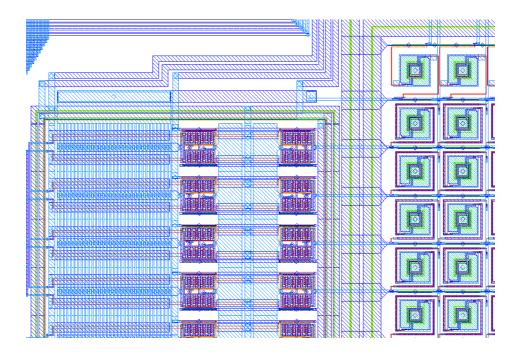

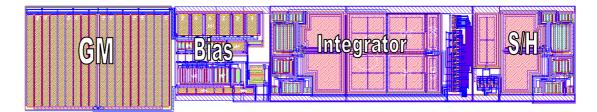

| 6.53 Layout of the complete 16-channel analog readout circuit. It is composed of 16 identical readout channels, a reference array and its bias circuit, and analog multiplexer switches for column selection. The layout measures $3025 \ \mu m \times 1700 \ \mu m$ in a 3-metal 2-poly 0.35 $\ \mu m$ CMOS process                                                                                                                                                 |

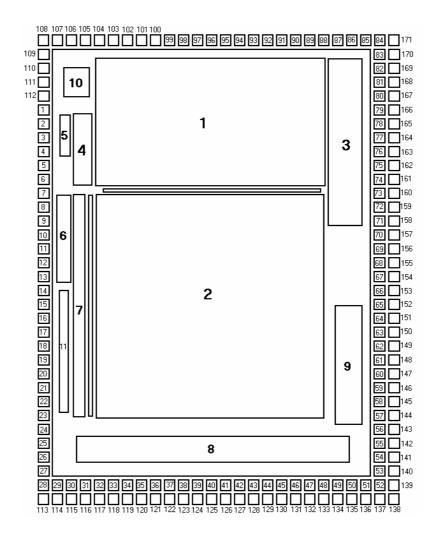

| <ul> <li>6.54 Floor plan and pad frame of the 64 × 64 microbolometer FPA. There are basically 11 structures in the FPA: 1) 16-channel readout circuit, 2) 64 × 64 FPA, 3) analog test circuits, 4) reference array and its bias circuit, 5) analog serial output multiplexer, 6) scanning control circuit, 7) vertical shift register, 8) test pixels, 9) thermal test structures, 10) etch monitor openings, 11) surface profile measurement structures.</li> </ul> |

| 6.55 Layout of the 64 $\times$ 64 infrared imager chip. It measures 4095 $\mu m \times 5375 \ \mu m \ (22 mm^2)$ in a 3-metal 2-poly 0.35 $\mu m \ CMOS \ process.$ 187                                                                                                                                                                                                                                                                                              |

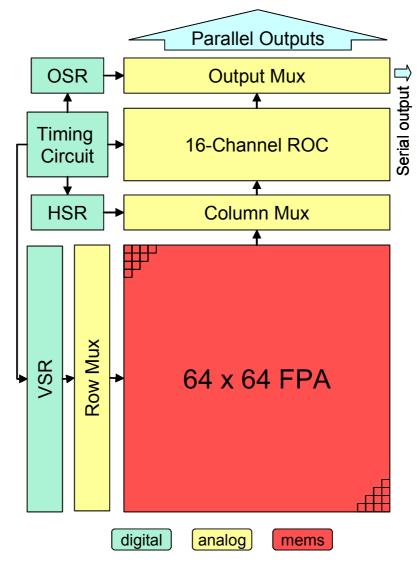

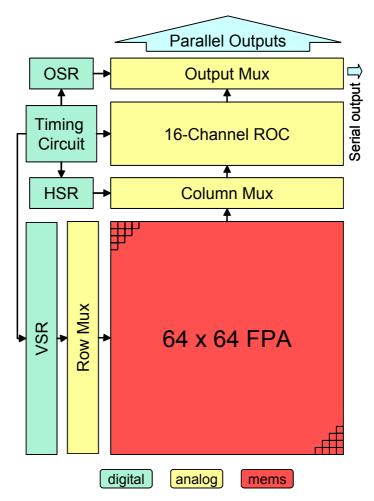

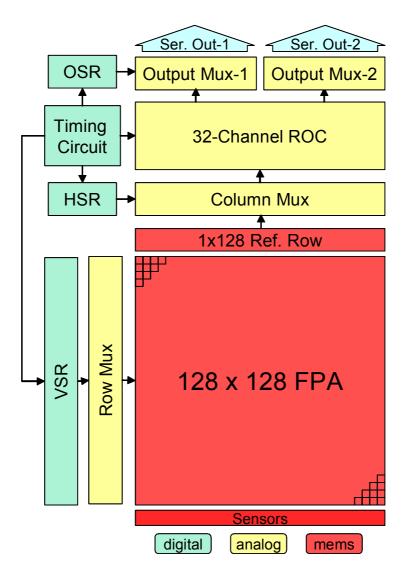

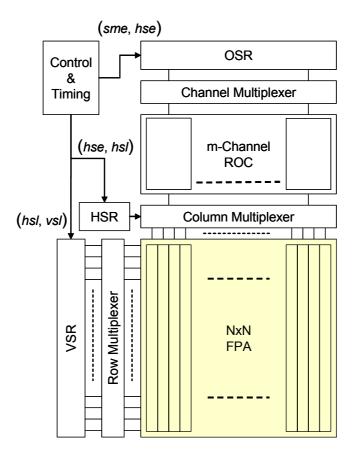

| 7.1 Block diagram of the $128 \times 128$ uncooled infrared imager chip                                                                                                                                                                                                                                                                                                                                                                                              |

| 7.2 Simplified schematics of the 128 × 128 array with the improved array structure [42]                                                                                                                                                                                                                                                                                                                                                                              |

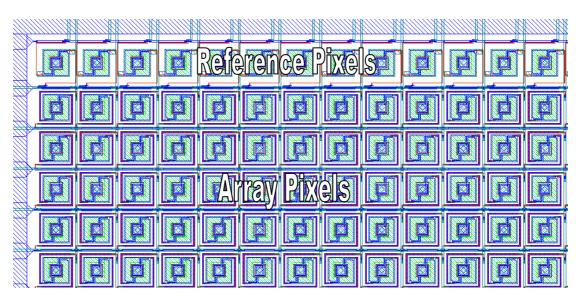

| 7.3 Zoomed layout of the $136 \times 136$ array pixels with reference pixels placed in<br>a $1 \times 136$ format above the array pixels                                                                                                                                                                                                                                                                                                                             |

| 7.4 Zoomed layout of the dummy routing structures used to compensate for the vertical voltage drops in the FPA                                                                                                                                                                                                                                                                                                                                                       |

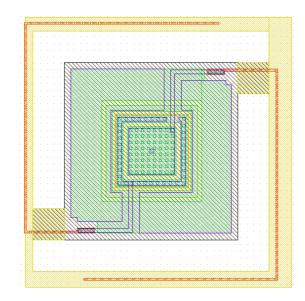

| 7.5 Layout of the reference pixel. The reference pixel is thermally shorted to the substrate with wide metal-oxide layer to increase the thermal conductance value. A polysilicon interconnect placed on the substrate is used to match the electrical resistance of the pixel to that of the array pixel197                                                                                                                                                         |

| <ul> <li>7.6 Block diagram of the analog readout circuitry used in the parallel readout channels in the 128 × 128 FPA.</li> </ul>                                                                                                                                                                                                                                                                                                                                    |

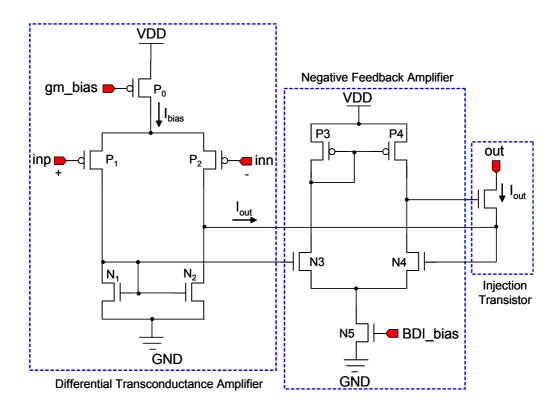

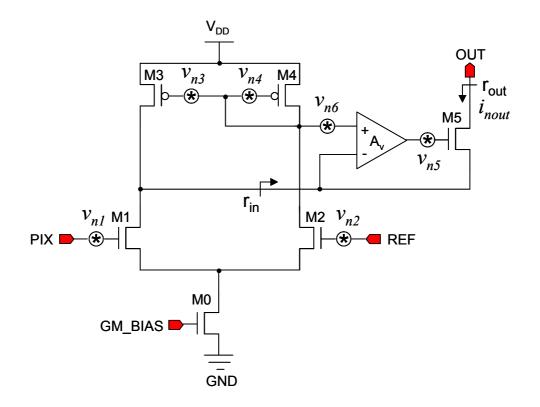

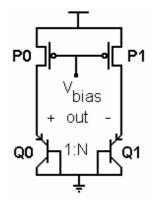

| 7.7 Schematic of the improved differential transconductance amplifier used in the readout circuitry of the $128 \times 128$ FPA. Matching and offset reduction is achieved with the help of a negative feedback structure [58].                                                                                                                                                                                   | .199 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 7.8 Noise model of the improved differential transconductance amplifier                                                                                                                                                                                                                                                                                                                                           | .201 |

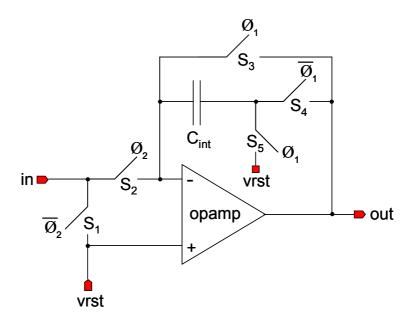

| 7.9 Schematic of the improved SCI circuit used in the readout circuitry of the $128 \times 128$ FPA. The offset and low frequency correlated noise of the opamp are cancelled by resetting and sampling the residual offset voltage prior to the actual integration operation [76]. The gain of the integrator can be adjusted by varying the integration capacitance ( $C_{int}$ ).                              | .203 |

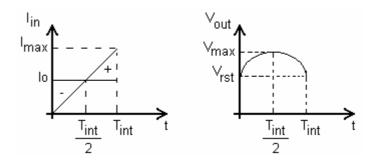

| 7.10 Cancellation of self-heating by using current sink method [61]. $I_{in}(t)$ is the output current of the differential transconductance amplifier, which changes to the self-heating effect, reaching a maximum value of $I_{max}$ . $I_o$ is the average of $I_{in}(t)$ over the integration period of $T_{int}$ . $V_{out}(t)$ is the output voltage of the SCI circuit with a reset voltage of $V_{rst}$ . | .205 |

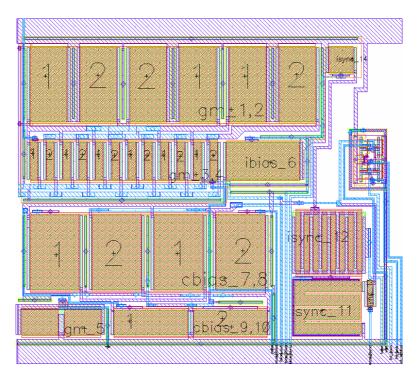

| 7.11 Layout of the analog channel readout circuitry. It measures 155 μm × 820 μm in a 3-metal 2-poly 0.35 μm CMOS process.                                                                                                                                                                                                                                                                                        | .206 |

| 7.12 Zoomed layout view of the 32-channel readout circuit, where only 12 of the readout channels are shown                                                                                                                                                                                                                                                                                                        | .208 |

| 7.13 Complete layout of the 32-channel analog readout circuit.                                                                                                                                                                                                                                                                                                                                                    | .208 |

| 7.14 Schematic of a simple temperature sensor based on diode connected vertical bipolar transistors available in CMOS [63, 78].                                                                                                                                                                                                                                                                                   | .209 |

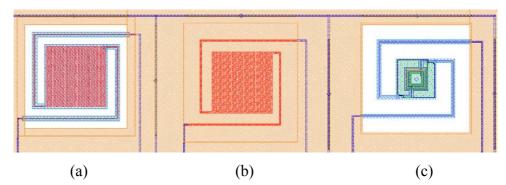

| 7.15 Layout of two PTAT sensors. The upper one uses diode type reference pixels, while the lower one uses bipolar transistors with integrated current sources.                                                                                                                                                                                                                                                    | .211 |

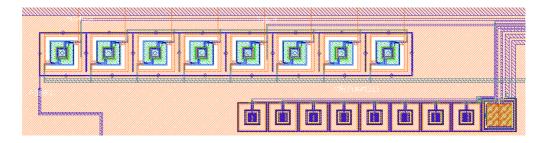

| 7.16 Layout view resistive and diode type vacuum sensors. Resistive vacuum sensor has a bridge circuit constructed with (a) a variable and (b) reference vacuum sensors using polysilicon resistors. (c) Diode type vacuum sensor is implemented using a suspended n-well diode thermally shorted to the substrate using metal interconnects.                                                                     |      |

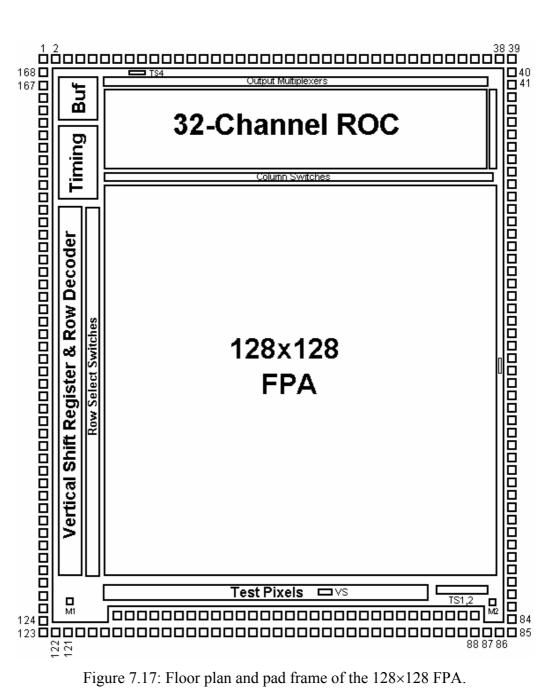

| 7.17 Floor plan and pad frame of the 128×128 FPA                                                                                                                                                                                                                                                                                                                                                                  | .213 |

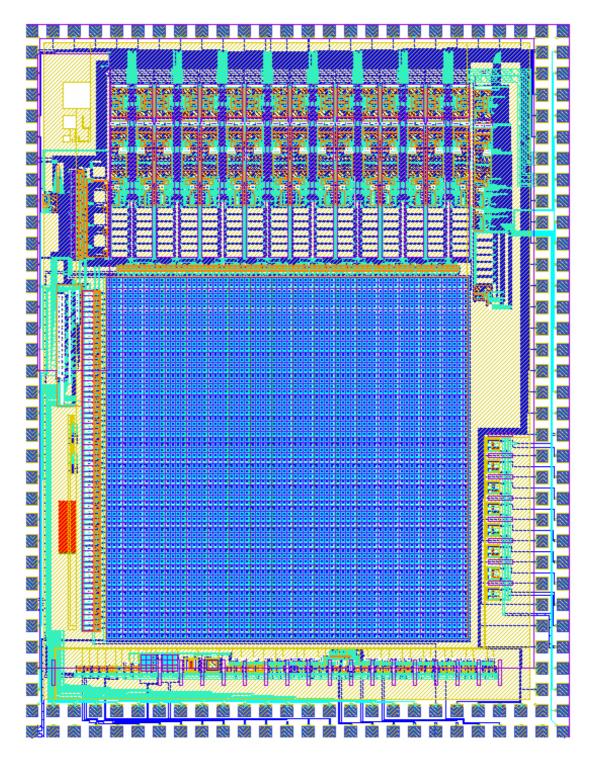

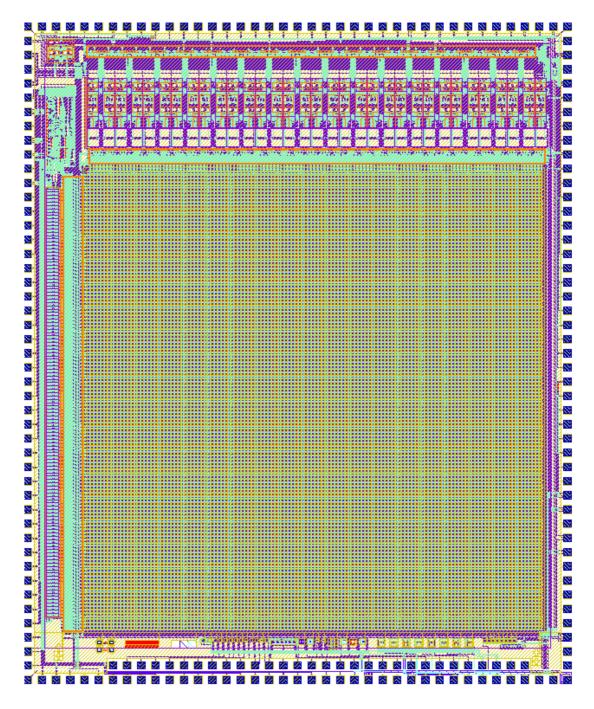

| 7.18 Layout view of the 128 $\times$ 128 imager chip. It measures 6555 $\mu m \times 7915 \ \mu m \ (52 \ mm^2)$ in a 0.35 $\mu m \ 3M2P \ CMOS \ process.$                                                                                                                                                                                                                                                       | .214 |

| 8.1 SEM photographs of the fabricated detector array pixels after post-CMOS processing: (a) top view and (b) bottom view after removing pixels from the substrate using a sticky-tape [41, 42].                                                                                                                                                                                                                   | .217 |

|                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

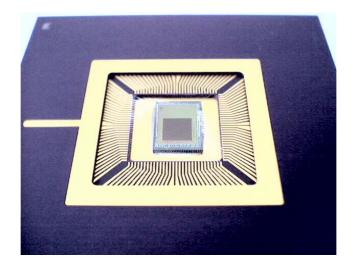

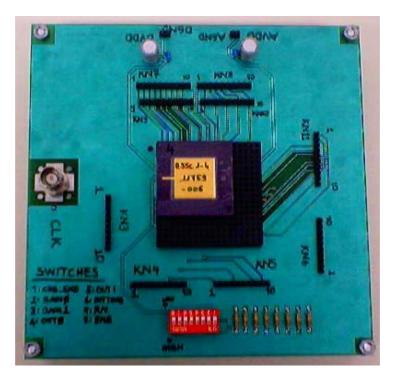

| 8.2 CMOS fabricated $64 \times 64$ FPA placed in a 120-pin pin grid array (PGA-120) package, which is used for the electrical tests of the $64 \times 64$ FPA.                                                                                                                                                                                                                                                        | 19 |