### DESIGN AND DIGITAL IMPLEMENTATION OF THYRISTOR CONTROLLED REACTOR CONTROL

### A THESIS SUBMITTED TO THE GRADUATE SCHOOL OF NATURAL AND APPLIED SCIENCES OF MIDDLE EAST TECHNICAL UNIVERSITY

BY

MURAT GENÇ

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE IN ELECTRICAL AND ELECTRONICS ENGINEERING

DECEMBER 2007

Approval of the thesis:

### DESIGN AND DIGITAL IMPLEMENTATION OF THYRISTOR CONTROLLED REACTOR CONTROL

submitted by **MURAT GENÇ** in partial fulfillment of the requirements for the degree of **Master of Science in Electrical and Electronics Engineering Department, Middle East Technical University** by,

Prof. Dr. Canan Özgen Dean, Graduate School of **Natural and Applied Sciences**

Prof. Dr. İsmet Erkmen — Head of Department, **Electrical and Electronics Engineering**

Prof. Dr. Muammer Ermiş Supervisor, **Electrical and Electronics Engineering Dept.**, **METU**

### **Examining Committee Members:**

Prof. Dr. Kemal Leblebicioğlu Electrical and Electronics Engineering Dept., METU

Prof. Dr. Muammer Ermiş Electrical and Electronics Engineering Dept., METU

Prof. Dr. H. Bülent Ertan Electrical and Electronics Engineering Dept., METU

Prof. Dr. Işık Çadırcı Electrical and Electronics Engineering Dept., Hacettepe Univ.

Dr. Özgül Salor Chief Expert Researcher, TÜBİTAK-UZAY

Date: 14.12.2007

I hereby declare that all information in this document has been obtained and presented in accordance with academic rules and ethical conduct. I also declare that, as required by these rules and conduct, I have fully cited and referenced all material and results that are not original to this work.

Name, Last name : Murat Genç

Signature :

#### ABSTRACT

# DESIGN AND DIGITAL IMPLEMENTATION OF THYRISTOR CONTROLLED REACTOR CONTROL

Genç, Murat M.S., Department of Electrical and Electronics Engineering Supervisor : Prof. Dr. Muammer Ermiş

December 2007, 116 pages

In this research work, the control system of 16 MVAr, 13.8 kV TCR will be designed and digitally implemented. A Real-Time Control System (NI CompactRIO<sup>TM</sup> Reconfigurable I/O) and a Digital Platform (NI LabVIEW<sup>TM</sup> G-code) are used in the digital implementation of TCR control system. The digital control system is composed of reactive power calculation, firing angle determination and triggering pulse generation blocks. The performance of control system will be tested in the field. The simulation results will also be compared with test data.

Keywords: Reactive Power Compensation, Thyristor Controlled Reactor (TCR), Real-Time controller, LabVIEW, CompactRIO.

# ÖZ

# TRİSTÖR KONTROLLÜ REAKTÖR KONTROLÜ TASARIMI VE SAYISAL GERÇEKLEŞTİRMESİ

Genç, Murat Yüksek Lisans, Elektrik ve Elektronik Mühendisliği Bölümü Tez Yöneticisi : Prof. Dr. Muammer Ermiş

Aralık 2007, 116 sayfa

Bu araştırma çalışmasında, 16 MVAr, 13,8 kV TKR'nin kontrol sistemi tasarlanacak ve sayısal olarak gerçekleştirilecektir. TKR Kontrol sisteminin sayısal gerçekleştirilmesinde Gerçek Zamanlı Kontrol Sistemi (NI CompactRIO Reconfigurable I/O) ve Sayısal Platform (NI LabVIEW G-code) kullanılacaktır. Kontrol sistemi reaktif güç hesabı, ateşleme açısı belirlemesi ve tetikleme sinyali üretimi bloklarını içermektedir. Kontrol sisteminin performansı sahada test edilecektir. Ayrıca, benzetim sonuçları test verisi ile karşılaştırılacaktır.

Anahtar Kelimeler: Reaktif Güç Kompanzasyonu, Tristör Kontrollü Reaktör (TKR), Gerçek zamanlı kontrollör, LabVIEW, CompactRIO.

to my grandmother Ayşe

### ACKNOWLEDGMENTS

I would like to express my deepest gratitude to his supervisor Prof. Dr. Muammer Ermiş for his guidance, advices and criticism throughout this research.

I also would like to thank K. Nadir Köse for his suggestions and contributions to this research but also his continuous confidence in me. His encouragement in the project and field works is the main reason for the success of the study.

I would like to thank Adnan Açık, Burhan Gültekin and Cem Özgür Gerçek for their contributions and support in the study.

Special thanks to Serhan Buhan and Burak Boyrazoğlu, mobile power quality measurement team members of National Power Quality Project of Turkey (Project No: 105G129), in obtaining the electrical characteristics and power quality of ladle furnaces and performance of SVC by field measurements.

This industrial system developed within the scope of this research work is a part of the turn-key project (Project No: 7050503) carried out by TÜBİTAK-UZAY for ERDEMİR Iron & Steel Inc. I would like to acknowledge TÜBİTAK-UZAY for allowing this research work.

I also would like to acknowledge the technical assistance of ERDEMIR Energy Generation and Distribution unit staff for their technical guidance and support.

# TABLE OF CONTENTS

| ABSTRACT          | iv   |

|-------------------|------|

| ÖZ                | v    |

| ACKNOWLEDGEMENTS  | vii  |

| TABLE OF CONTENTS | vii  |

| LIST OF FIGURES   | х    |

| LIST OF TABLES    | xiii |

### CHAPTER

| 1. | INTRODU   | JCTION                                         | .1  |

|----|-----------|------------------------------------------------|-----|

|    | 1.1. OVE  | RVIEW                                          | .1  |

|    | 1.2. SCOF | PE OF THE STUDY                                | .3  |

| 2. | TCR BAS   | ED SVC                                         | .5  |

|    | 2.1. GENI | ERAL                                           | .5  |

|    | 2.2. STAT | TIC VAr COMPENSATOR                            | .6  |

|    | 2.3. THYI | RISTOR CONTROLLED REACTOR                      | .8  |

|    | 2.4. LADI | LE FURNACE                                     | .13 |

|    | 2.5. HAR  | MONIC FILTERING                                | .17 |

|    | 2.6. SVC  | DESIGN PROCEDURE                               | .23 |

| 3. | STRUCT    | URE OF PROTOTYPE SVC SYSTEM                    | .36 |

|    | 3.1. POW  | ER SYSTEM                                      | .36 |

|    | 3.2. CON  | TROL STAGE                                     | .43 |

|    | 3.2.1.    | SVC control                                    | .43 |

|    | 3.2.2.    | Analog Circuitry                               | .51 |

|    | 3.2.3.    | Real-Time Computing                            | .53 |

|    | 3.2.4.    | LabVIEW and NI CompactRIO Real-Time Controller | .54 |

|    | 3.2.5.    | Supplementary Elements                         | .61 |

|    |           |                                                |     |

| 4.       | SIMULATION WORK                           | 64 |

|----------|-------------------------------------------|----|

|          | 4.1. SIMULATION PLATFORM                  | 64 |

|          | 4.2. STEP RESPONSE                        | 67 |

|          | 4.3. SVC RESPONSE AGAINST LOAD VARIATIONS | 75 |

|          | 4.4. LOAD BALANCING                       | 77 |

|          | 4.5. ADAPTIVE CONTROL                     | 79 |

|          | 4.6. SUMMARY OF SIMULATION WORK RESULTS   | 84 |

| 5.       | FIELD RESULTS                             | 85 |

|          | 5.1. FEEDBACK CONTROL                     |    |

|          | 5.2. FEEDFORWARD CONTROL                  | 87 |

|          | 5.3. HYBRID CONTROL                       |    |

|          | 5.4. SUMMARY                              | 92 |

| 6.       | CONCLUSION                                | 93 |

|          | 6.1. CONCLUSION                           | 93 |

| FERE     | NCES                                      | 96 |

| PEND     | IX – A                                    |    |

| VIEW     | / code                                    | 99 |

| ctive l  | Power Measurement                         | 10 |

| itial I/ | O                                         | 10 |

| 96 |

|----|

| 9  |

### APP

| LabVIEW code               | 99  |

|----------------------------|-----|

| Reactive Power Measurement | 100 |

| Digitial I/O               | 101 |

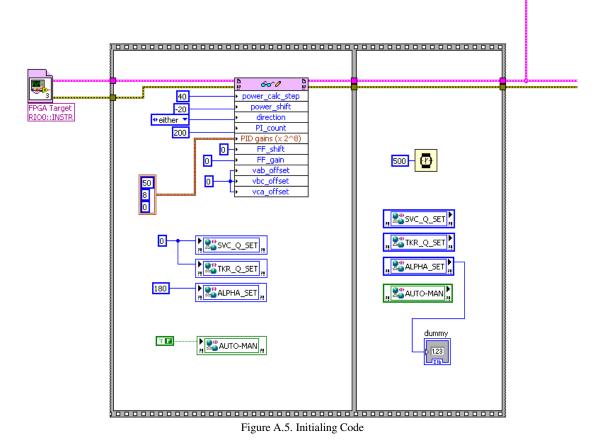

| Initializing               | 102 |

| FPGA Control               |     |

| Communication              | 104 |

# APPENDIX – B

| CompactRIO Data Sheet105 |

|--------------------------|

|--------------------------|

# APPENDIX – C

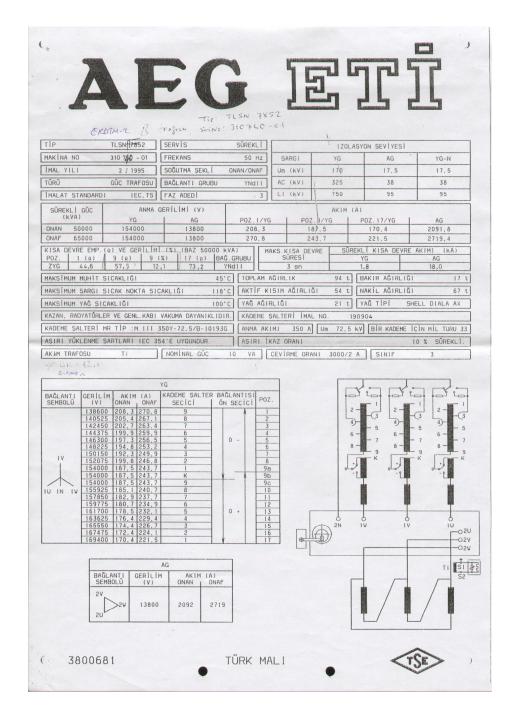

| Power transformer | datasheet | <br> | 115 |

|-------------------|-----------|------|-----|

|                   |           |      |     |

| APPENDIX – D | ) | 11 | 6 |

|--------------|---|----|---|

|--------------|---|----|---|

## LIST OF FIGURES

### FIGURE

| 2.1 Power triangle                                                         | 6  |

|----------------------------------------------------------------------------|----|

| 2.2 Basic scheme of SVC                                                    | 7  |

| 2.3 SVC compensation capability according to the capacitor and inducto     | or |

| reactive powers                                                            | 8  |

| 2.4 Thyristor Controlled Reactor                                           | 9  |

| 2.5 TCR voltage and current waveforms                                      | 9  |

| 2.6 TCR harmonic currents flow                                             | 11 |

| 2.7 TCR current values according to conduction angle                       | 12 |

| 2.8 TCR harmonic current values according to conduction angle              | 12 |

| 2.9 Ladle furnace                                                          | 13 |

| 2.10 Active (red) and Reactive (blue) powers of ladle furnace for one      |    |

| heating process                                                            | 14 |

| 2.11 Active (red) and Reactive (blue) powers of ladle furnace for one      |    |

| heating process (zoomed)                                                   | 15 |

| 2.12 Voltage and current waveforms of an electric arc                      | 15 |

| 2.13 Nonlinear Voltage-Current characteristic of electric arc              | 16 |

| 2.14 Harmonics of an electric arc furnace at refining stage                | 16 |

| 2.15 Passive filter connection to a power system                           | 18 |

| 2.16 Damped passive filter connection to a power system                    | 19 |

| 2.17 Frequency-impedance characteristics of filter                         | 20 |

| 2.18 Frequency-impedance characteristics of the damped filter              | 21 |

| 2.19 One phase of 13.8 kV/14.2 MVAr C-type 2 <sup>nd</sup> Harmonic Filter | 22 |

| 2.20 Filter characteristic of the C-type filter                            | 23 |

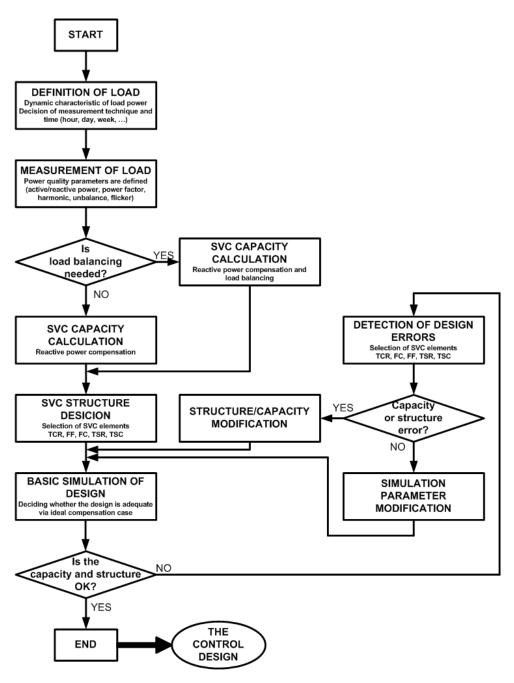

| 2.21. Power Stage design                                                   | 25 |

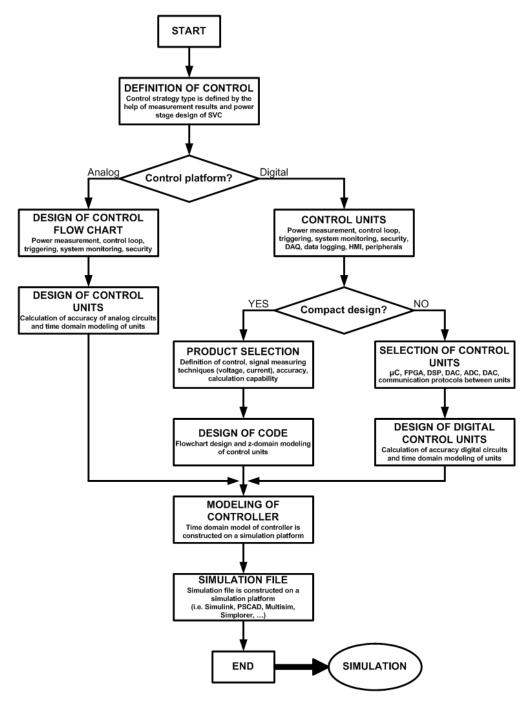

| 2.22. Controller design                             | 28 |

|-----------------------------------------------------|----|

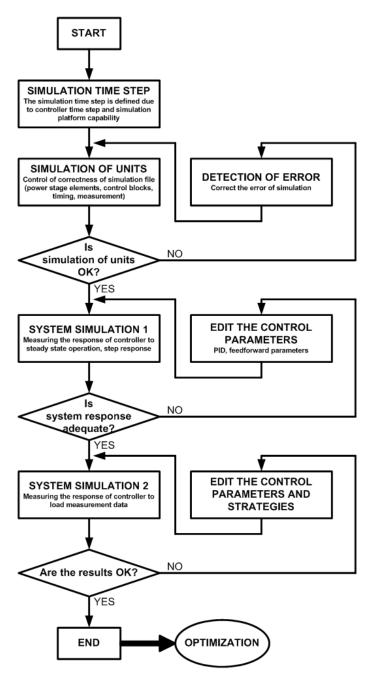

| 2.23. Simulation                                    | 31 |

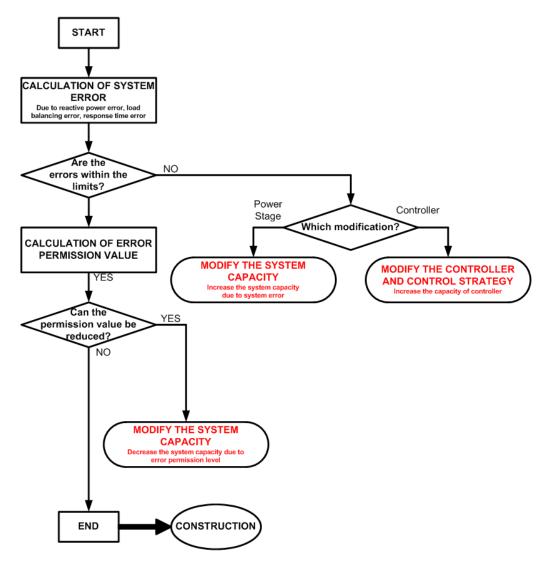

| 2.24. Optimization                                  | 33 |

| 2.25. Construction                                  | 35 |

| 3.1 Connection diagram of power system of SVC       | 38 |

| 3.2 Power stage of SVC system                       | 39 |

| 3.3 Views of power system elements of SVC (outside) | 40 |

| 3.4 View of power system elements of SVC (inside)   | 41 |

| 3.5 Thyristor stack                                 | 41 |

| 3.6 General view of indoor stage                    | 42 |

| 3.7 Control system enclosures                       | 42 |

| 3.8 Control diagram of SVC                          | 44 |

| 3.9 Control stage of SVC                            | 45 |

| 3.10 Voltage phasors for a 3¢ system                | 46 |

| 3.11 Analog circuitry                               | 51 |

| 3.12 Inside of CD4046BE PLL                         | 53 |

| 3.13. Real-Time system operation                    | 53 |

| 3.14. Real-Time system failure                      | 54 |

| 3.15 NI cRIO mounted inside the control enclosure   | 56 |

| 3.16. Reactive power calculation loop for phase B   | 57 |

| 3.17. Control loop                                  | 58 |

| 3.18. Discrete PID component of LabVIEW FPGA        | 58 |

| 3.19. Detection of ZC and PC signals                | 61 |

| 3.20. The pulse train generation                    | 61 |

| 3.21. Inside of control enclosure                   | 62 |

| 4.1 PSCAD Simulation file of SVC System             | 66 |

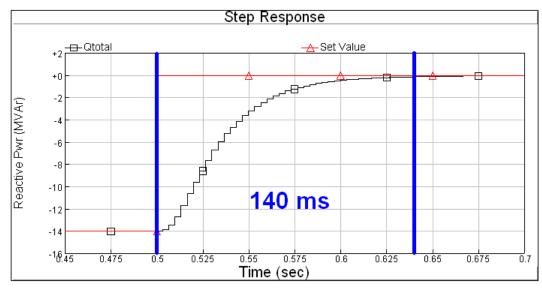

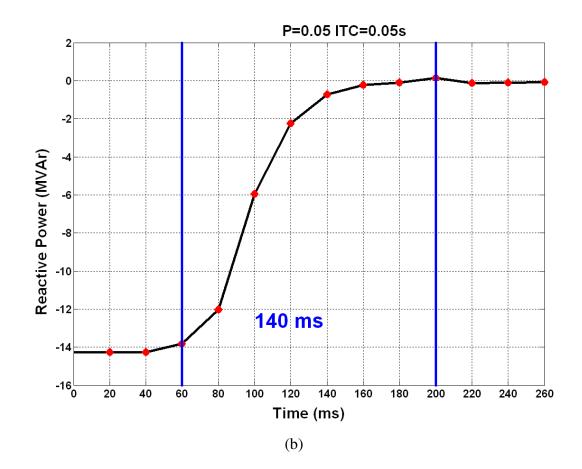

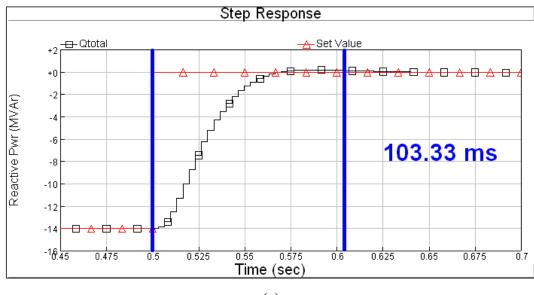

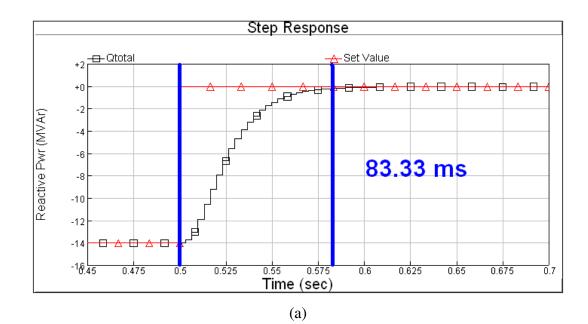

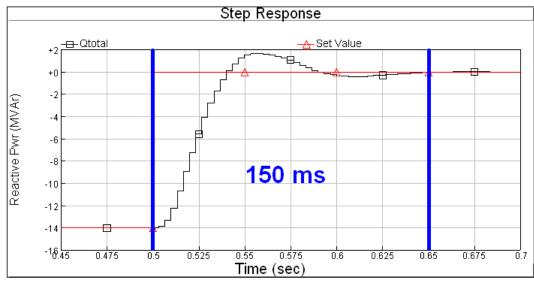

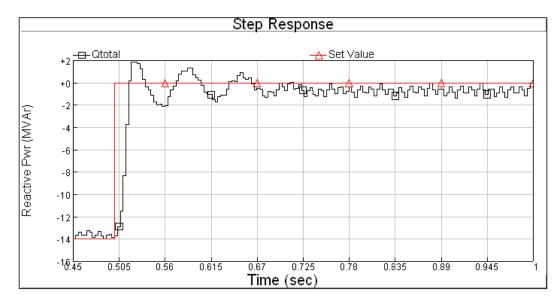

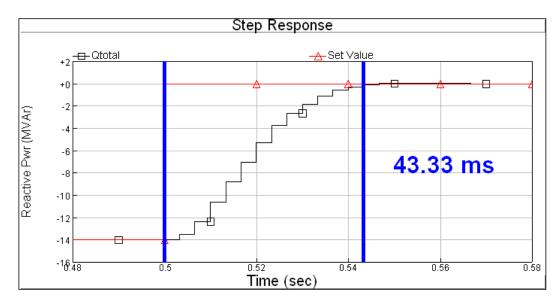

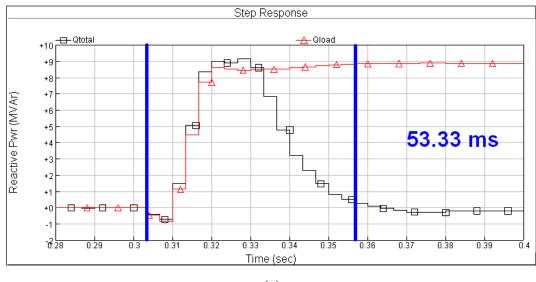

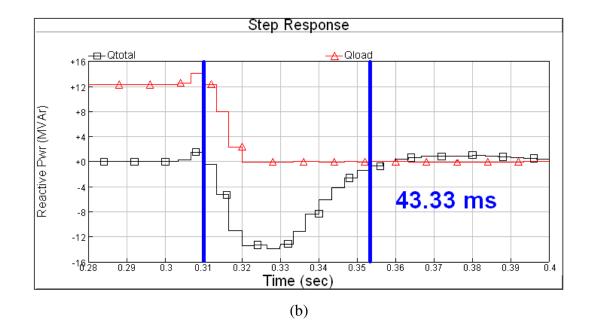

| 4.2 P=0.05, ITC=0.05 sec                            | 68 |

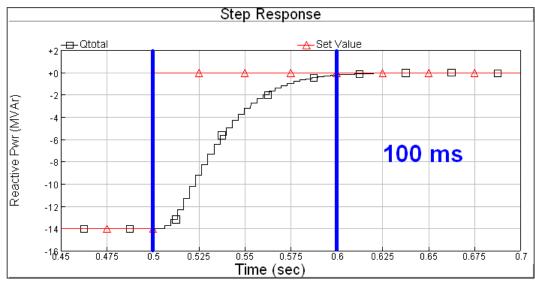

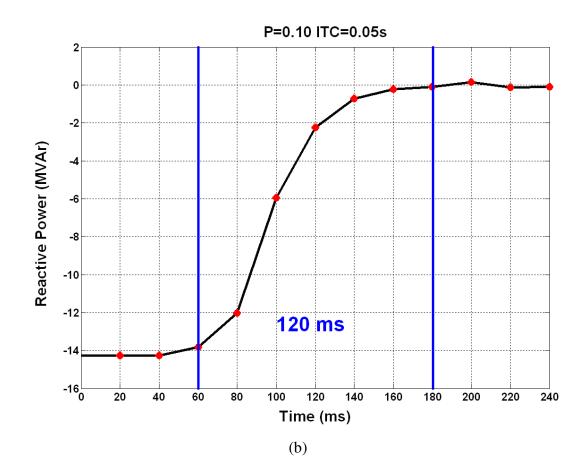

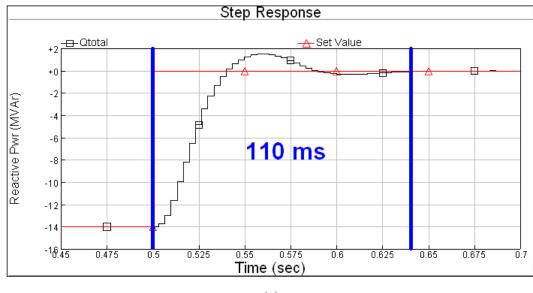

| 4.3. P=0.1, ITC=0.05 sec                            | 69 |

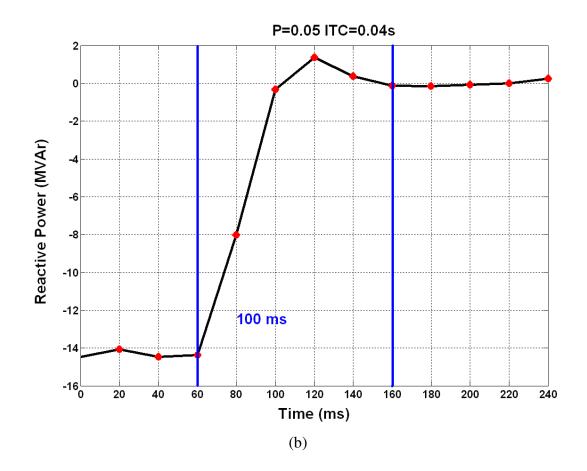

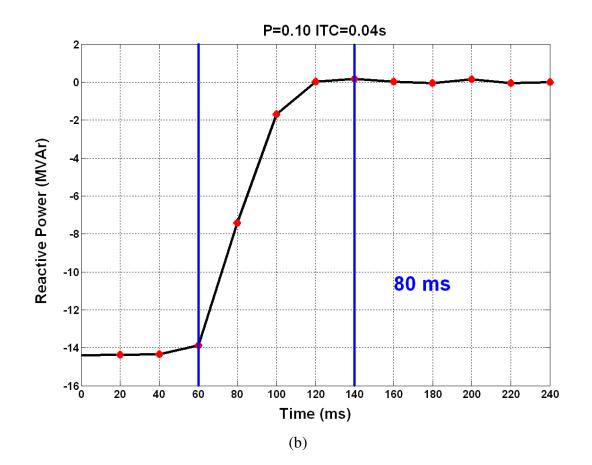

| 4.4. P=0.05, ITC=0.04 sec                           | 70 |

| 4.5. P=0.1, ITC=0.04 sec                            | 71 |

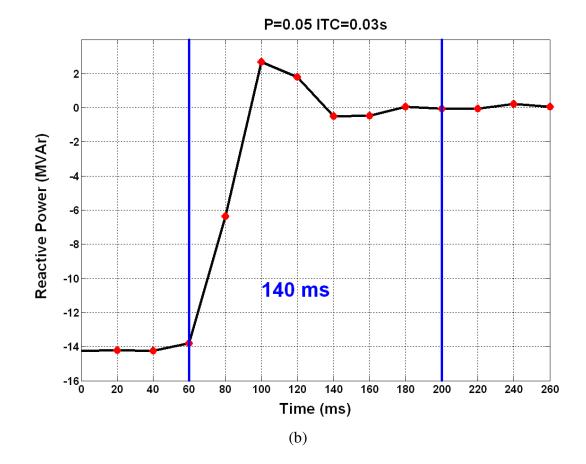

| 4.6. P=0.5, ITC=0.03 sec                            | 72 |

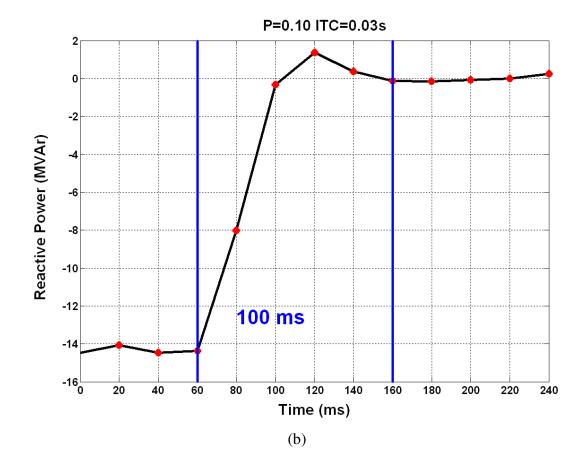

| 4.7. P=0.1, ITC=0.03 sec                            | 73 |

| 4.8. P=0.2, ITC=0.01 sec. unstable                  | 74 |

| xi                                                  |    |

| 4.9. P=0.17, ITC=0.028 sec                                            | 4 |

|-----------------------------------------------------------------------|---|

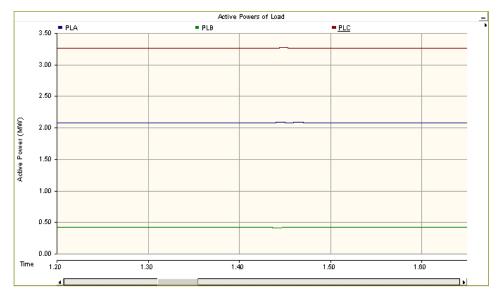

| 4.10. The response of SVC to load for FB7                             | 5 |

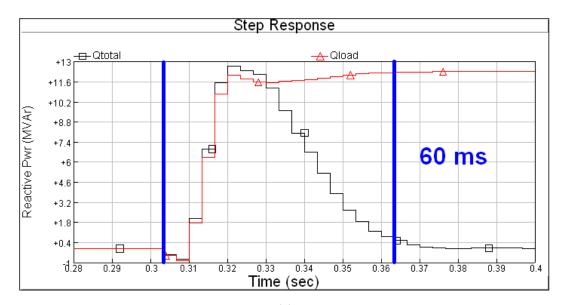

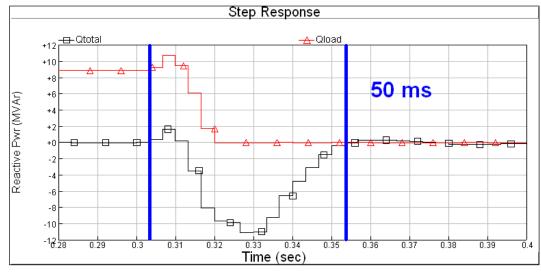

| 4.11. The response of SVC to load for FB+FF70                         | 6 |

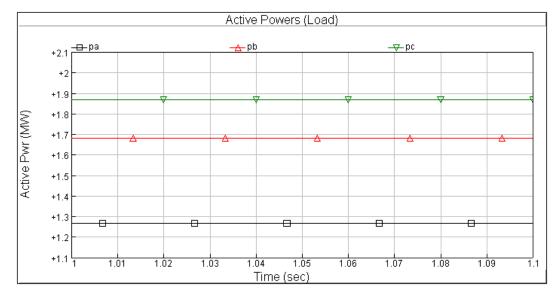

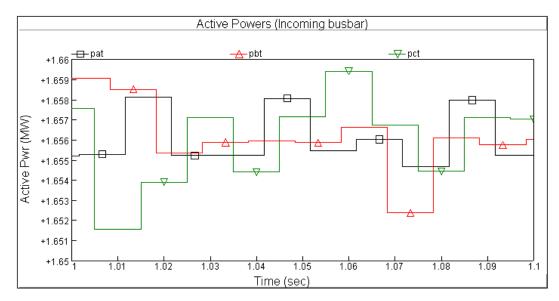

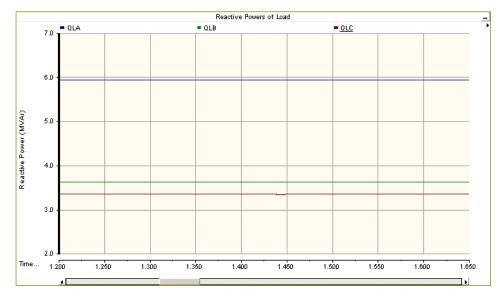

| 4.12. Unbalanced load's active powers (MW)7                           | 7 |

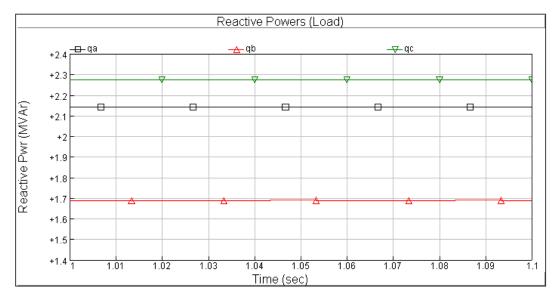

| 4.13. Unbalanced load's reactive powers (MVAr)78                      | 8 |

| 4.14. Balanced incoming busbar active powers                          | 8 |

| 4.15. Compensated incoming busbar active powers                       | 9 |

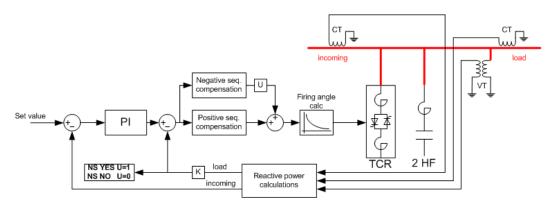

| 4.16. Adaptive control                                                | 0 |

| 4.17. Active powers of the unbalanced load                            | 1 |

| 4.18. Reactive powers of the unbalanced load                          | 1 |

| 4.19. Reactive powers of the unbalanced load                          | 2 |

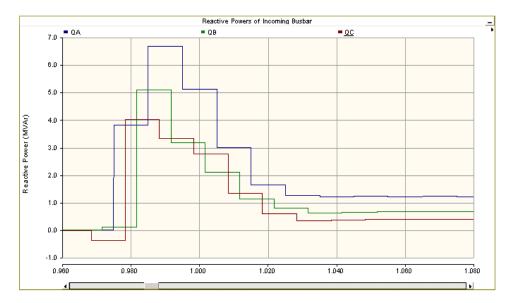

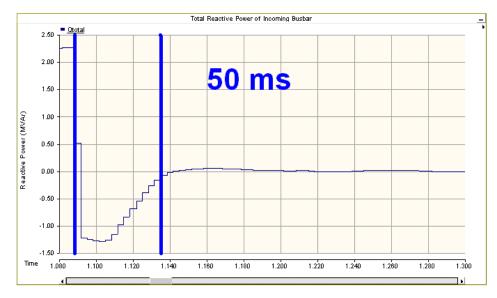

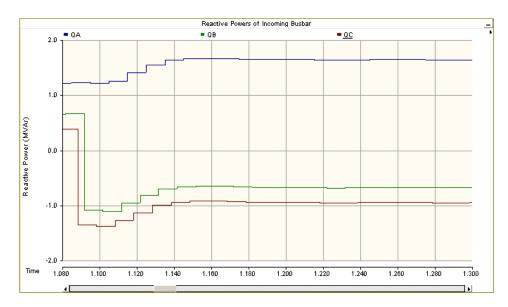

| 4.20. Total reactive power of incoming busbar for adaptive control8   | 3 |

| 4.21. Phase reactive powers of incoming busbar for adaptive control82 | 3 |

| 5.1 Feedback control                                                  | 5 |

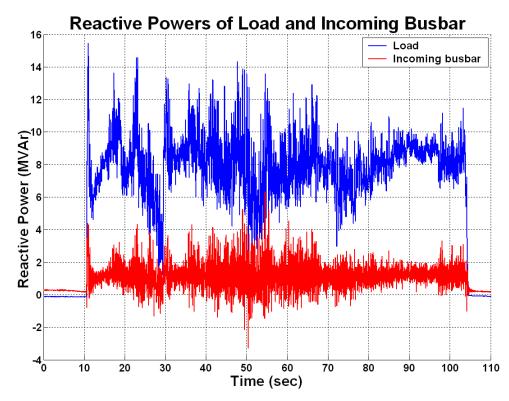

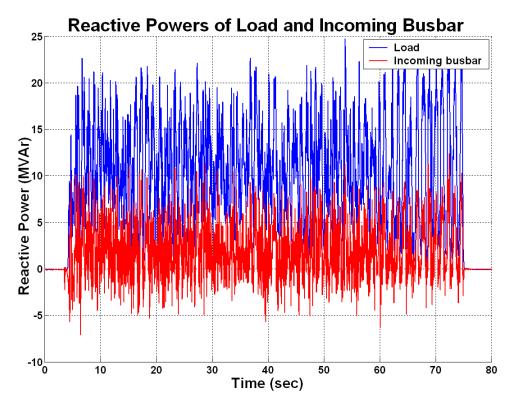

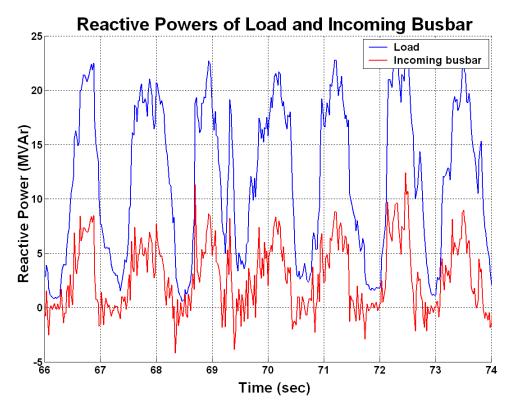

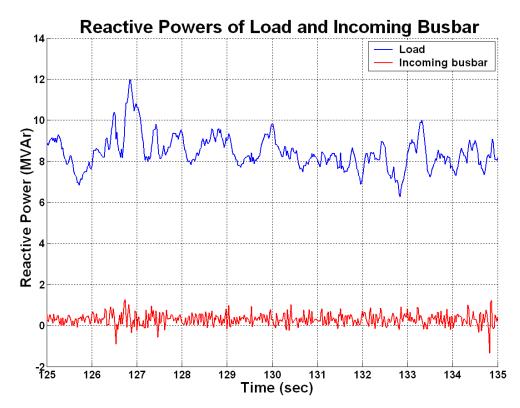

| 5.2 Reactive powers for feedback control                              | 6 |

| 5.3 Reactive powers for feedback control (zoomed)                     | 6 |

| 5.4 Feedforward control                                               | 7 |

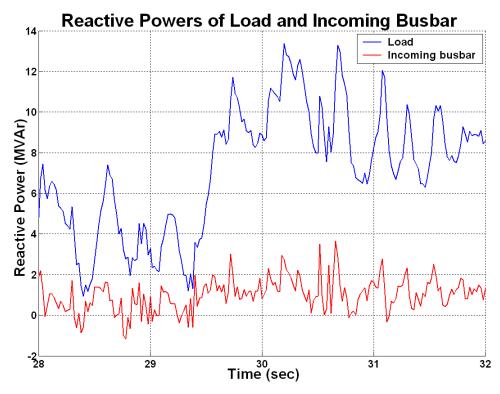

| 5.5 Reactive powers for feedforward control                           | 8 |

| 5.6 Reactive powers for feedforward control (zoomed)                  | 8 |

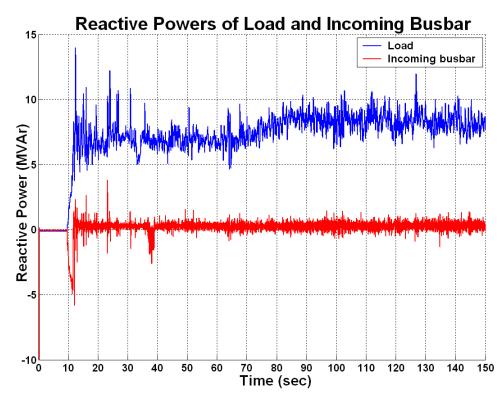

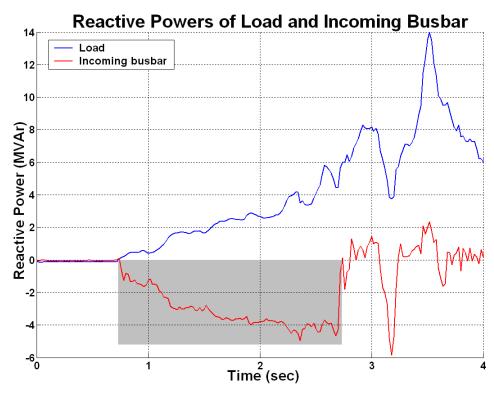

| 5.7. Hybrid (FB+FF) control                                           | 9 |

| 5.8. Reactive powers for hybrid control                               | 0 |

| 5.9. Reactive powers for hybrid control (zoomed)9                     | 0 |

| 5.10. Malfunction of SVC (shaded area)9                               | 1 |

# LIST OF TABLES

## TABLE

| 2.1 Maximum harmonic ratios of TCR current | 10 |

|--------------------------------------------|----|

| 2.2. Advantages of Digital Controller      | 27 |

| 2.3. Disadvantages of Digital Control      | 27 |

### **CHAPTER 1**

### **INTRODUCTION**

#### **1.1 OVERVIEW**

With the advance in modern industrial plants, consuming electrical energy, significant problems arise. These are;

- Reactive power consumption of industrial loads from the supply

- Harmonic currents injected by the loads to the supply

- Unbalanced loading of the supply because of unbalance operation of some industrial loads

- Light flicker arising from voltage fluctuations

- Further power quality problems arise from nonlinear industrial loads such as electric arc furnaces, ladle furnaces, rolling mils, excavating machines, transportation systems, etc.

These problems are solved by the use of FACTS to a great extent these are ranging from TCR based SVC to STATCOM [1] [2] [3][4][5][6][7].

This research work deals with the design and implementation of a real-time digital controller for TCR based SVC systems.

TCR based SVCs should follow the rapidly changing reactive power demand of loads closely. In general, since rapidly changing loads are also unbalanced loads, each SVC phase must be controlled separately [1] [8][9].

For the accurate and redundant operation of SVC, digital implementation is selected for the controller of SVC. Noise immunity, accuracy of arithmetic operations, ability for modularity structure, and improved sensitivity to parameter variations in digital electronics made the choice of digital option for implementation of TCR controller more advantageous as compared to the analog counter part.

Further than this, the digital controller provides more flexibility. Modification in the field and development is easier because the implementation is markedly based on software. Most of the modifications are done by changing the code installed into the digital components as ICs, compact devices. Moreover, due to the ability of complex arithmetic calculations of digital implementation, performance of the controller is increased as compared to the analog controller.

Since, digital electronics do not require calibration and maintenance as much as analog electronics, changing the application does not require major changes in hardware but only minor modifications in software.

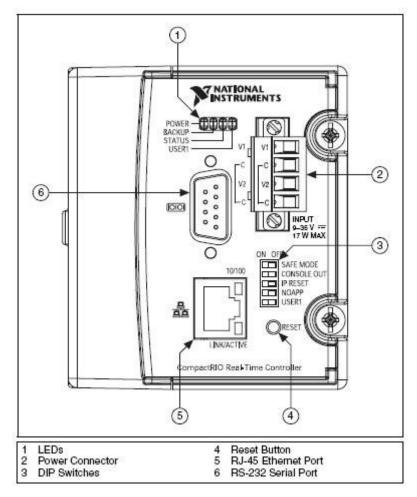

For the implementation platform NI cRIO 9004 Real-Time Controller and NI cRIO 9104 Reconfigurable Embedded Chassis are used for the TCR controller. More information about NI cRIO is available in Appendix (A). The software of the controller is built on NI LabVIEW program compatible with NI cRIO RT controller. The software is available in Appendix (B).

The implemented controller has been tested on the reactive power compensation system of ladle furnace of Ereğli Iron & Steel Works. PI based feedback, feedforward, hybrid and adaptive control strategies have been tried out theoretically and experimentally.

#### **1.2 SCOPE OF THE STUDY**

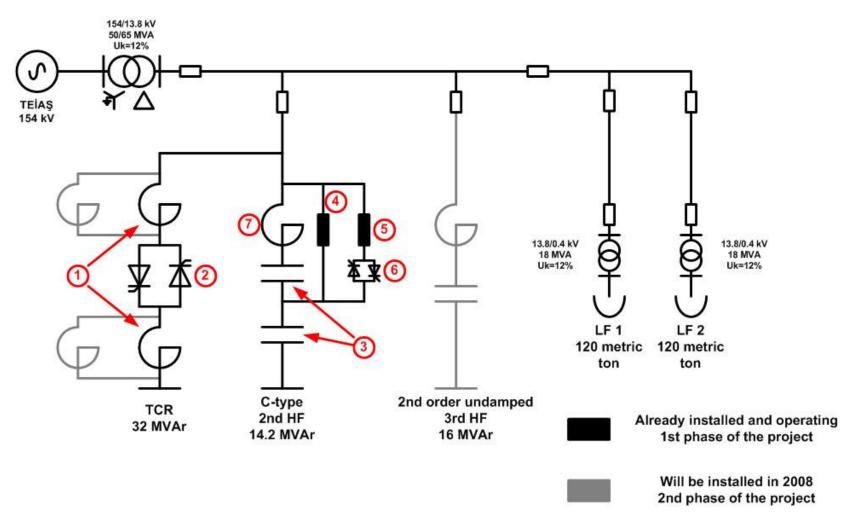

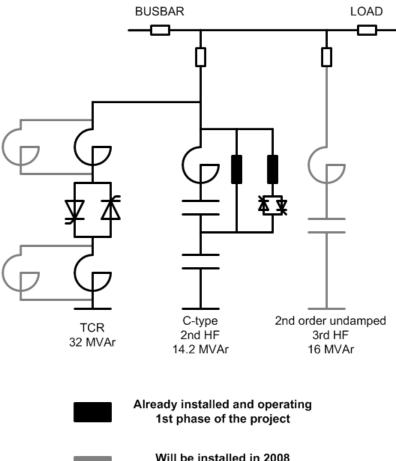

In this study, the control system of TCR has been designed and digitally implemented on NI CompactRIO Real-Time controller platform. This controller is used in the TCR type compensation system of ERDEMİR Iron and Steel Co., Turkey. The compensation system includes 32 MVAr TCR, 14.2 MVAr C-type 2<sup>nd</sup> harmonic filter and 16 MVAr 2<sup>nd</sup> order 3<sup>rd</sup> harmonic filter and it is connected to the low voltage side of 154/13.8 kV transformer at TEİAŞ switchyard within the ERDEMİR campus. This system is designed to compensate the reactive power of ladle furnaces of the factory.

The control system is tested in the field with different type of control algorithms feedback (PI), feedforward (FF), hybrid (PI+FF) and adaptive control. The results are discussed according to the resultant reactive power measurements acquired by the field measurements carried out by DAQ systems.

The outline of the thesis is as follows;

In Chapter 2, description and operating principles of TCR based SVC is described. After explaining the basic definitions of SVC and TCR, operation principles and reactive power control by TCR are described. The ladle furnace, its operation and its electrical characteristic are also described in this chapter. Passive filtering method for harmonic filtering is described and the damping factor is examined. Lastly, SVC design procedure is explained to have the optimum system.

In Chapter 3, power system of the SVC is described. The connections of the elements to the power system are explained. The control of TCR based SVC is examined and the control algorithm of an SVC is explained mathematically for positive and negative sequence compensation. The structure of control stage and closed loop control diagram are given. The parts of electronic TCR controller are identified and their functions and operating principles are explained. Also the real-time controller's codes are explained.

In Chapter 4, the simulations of the SVC system are carried out. For feedback control, the effects of PI parameters are examined and the optimum parameter values are obtained by trial and error method. The contribution of feedforward loop to the response time of the system is examined. An adaptive control method is simulated and its operation is explained.

In Chapter 5, the field measurement results are given. The resultant incoming busbar reactive powers for different control strategies are examined and the results are compared with the theoretical ones given in Chapter 4.

In Chapter 6, general conclusions are given.

#### CHAPTER 2

### TCR BASED SVC

### **2.1 GENERAL**

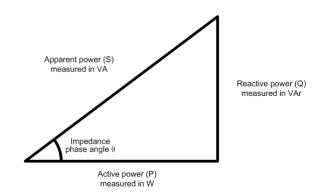

In an AC electrical system, *active power* (P) is the power consumed by the resistive loads in an electrical circuit. *Reactive power* (Q) is the power generated in an AC circuit because of the expansion and the collapse of magnetic (inductive) and electrostatic (capacitive) fields. Reactive power is expressed in Volt-Amperes-reactive (VAr) (Figure 2.1). These are given in Equations 2.4-2.6 for purely sinusoidal voltages and currents. In a single phase AC circuit;

$$V = \frac{\hat{V}}{\sqrt{2}}\cos(\omega t)$$

2.1

$$I = \frac{\hat{I}}{\sqrt{2}}\cos(\omega t + \theta)$$

2.2

$$\omega = 2\pi f \qquad 2.3$$

$$P = V_{rms} I_{rms} \cos(\theta)$$

2.4

$$Q = V_{rms} I_{rms} \sin(\theta)$$

2.5

$$S = \sqrt{P^2 + Q^2}$$

2.6

$$pf = \frac{P}{S}$$

2.7

Unlike active power, reactive power is not a useful power. Reactive energy is stored by inductors since they expand and collapse their magnetic fields in an attempt to keep their current constant and it is also stored by capacitors since they charge and discharge in an attempt to keep their voltage constant. Circuit inductance and capacitance consume and give back the reactive energy. The power delivered to the inductance is stored in the magnetic field when the field is expanding and it is returned to the source when the field collapses. The power delivered to the capacitance is stored in the electrostatic field when the capacitor is charging and returned to the source when the capacitor discharges. The active power, which is the power consumed is consumed over one cycle, is thus zero for inductive and capacitive elements.

Figure 2.1. Power triangle

#### 2.2 STATIC VAr COMPENSATOR

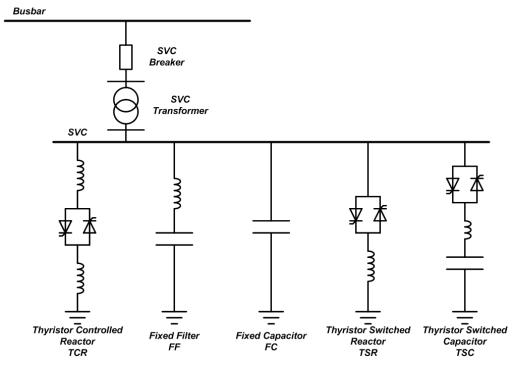

Static VAr compensator (SVC) is a fast acting reactive power compensator device connected to a high or medium voltage power network to supply the required reactive power by electrical loads. It contains some of the compensation devices such as TCR, thyristor switched capacitor (TSC), thyristor switched reactor (TSR), fixed capacitor (FC), fixed filter (FF) as illustrated in Figure 2.2.

Figure 2.2. Basic scheme of SVC

The SVC is an automated impedance matching device. It measures the reactive power of the power system and calculates the required reactive power for compensation. The required reactive power is generated by phase angle modulation of thyristor switches. Since the reactive power adjustment is made by thyristor switches and there is no mechanical switching action, it is called *static*.

An SVC can continuously supply reactive power to the bus to which it is connected. Whenever the load power varies, SVC responds quickly, and continues to operate with a new reactive power value.

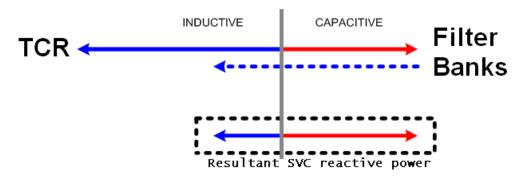

TCR based SVC is the most common topology used in SVC type compensators. The main idea is to compensate the load with capacitors and make the total reactive power capacitive. The TCR is controlled to compensate the capacitive reactive power. TCR type SVC has a compensation capacity between the power of capacitors for capacitive reactive power and the reactive power difference between reactors and capacitors for inductive reactive power. Figure 2.3 shows the compensation limits for a TCR based SVC.

Figure 2.3. SVC compensation capability according to the capacitor and inductor reactive powers

Because of the resonance and inrush problem between the line impedance and capacitance, generally capacitors are not to be connected to the bus directly. Instead of direct connection, a small tuning or detuning reactor is used to eliminate the inrush currents of the capacitor, and by the resonance frequency between the reactor and capacitor, the load harmonic at this frequency can be eliminated. Two problems, inrush and harmonic filtering, are solved by reactor addition.

#### 2.3 THYRISTOR CONTROLLED REACTOR

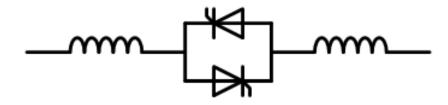

*Thyristor controlled reactor (TCR)* is a dynamic passive element whose admittance is controlled by a thyristor stack connected in anti-parallel form and it conducts on half cycles of the power supply voltage period. The circuit diagram of each phase of a TCR is shown in Figure 2.4.

Figure 2.4. Thyristor Controlled Reactor

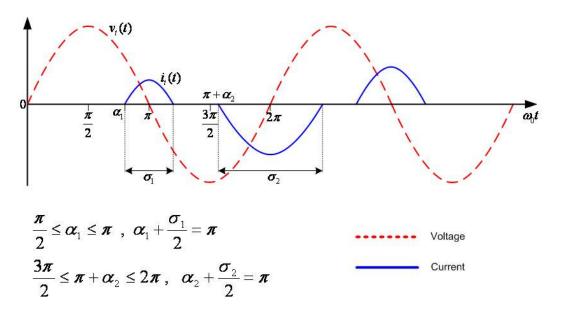

Figure 2.5. TCR voltage and current waveforms

The admittance of reactor depends on the triggering angle of the thyristors. Each thyristors is triggered into conduction in the second quadrant of its anode-cathode voltage signal (Figure 2.5).

The current on the reactor is controlled by changing the firing angle of the thyristors ( $\alpha$ ). The fundamental component of the TCR current depends on the firing angle which makes the impedance of the reactor controllable. The ability to control the impedance of the reactor makes TCR a controllable inductive load which is suitable for reactive power compensation.

The relation between firing angle and TCR current is acquired by solving the following equation 2.8 for the fundamental component which gives equation 2.10.

$$I_{TCR} = \begin{cases} \frac{\sqrt{2}V}{X_L} (\cos(\alpha) - \cos(\omega t)), & \alpha < \omega t < \alpha + \sigma \\ 0, & \alpha + \sigma < \omega t < \alpha + \pi \end{cases}$$

(2.8)

$$\sigma = \frac{\pi - \alpha}{2} \tag{2.9}$$

$$I_{TCR,n} = \frac{4}{\pi} \frac{V}{X_L} \left[ \frac{\sin(n+1)\alpha}{2(n+1)} + \frac{\sin(n-1)\alpha}{2(n-1)} - \cos\alpha \frac{\sin(n\alpha)}{n} \right]$$

(2.10)

$n = 3, 5, 7, ...$

$$I_{TCR,1} = \frac{\sigma - \sin(\sigma)}{\pi \times X_L} V_{rms} \quad A_{rms}$$

(2.11)

$$B_{L}(\sigma) = \frac{\sigma - \sin(\sigma)}{\pi} \times \frac{1}{X_{L}}$$

(2.12)

Since the current of TCR is non-sinusoidal, there occurs harmonics in the power system to which TCR is connected. The harmonic values are shown in Table 2.1.

| Harmonic | Ratio to the fundamental (%) |

|----------|------------------------------|

| 1        | 100                          |

| 3        | (13,78)                      |

| 5        | 5,05                         |

| 7        | 2,59                         |

| 9        | (1,57)                       |

| 11       | 1,05                         |

| 13       | 0,75                         |

| 15       | (0,57)                       |

| 17       | 0,44                         |

| 19       | 0,35                         |

| 21       | (0,29)                       |

| 23       | 0,24                         |

| 25       | 0,20                         |

Table 2.1 Maximum harmonic current ratios of TCR current

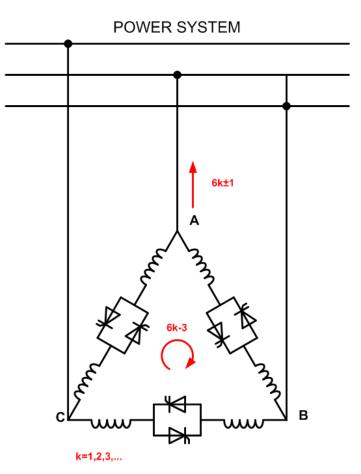

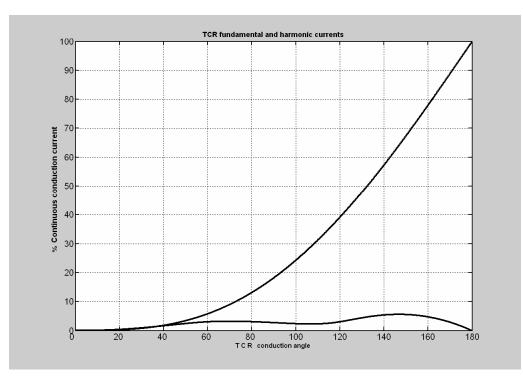

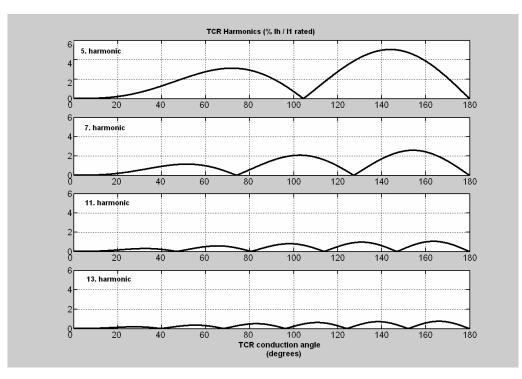

If the firing angle is same for positive and negative half-cycles of voltage signal then the current has odd symmetry and there is no harmonics with even index number. From Equation 2.10, the 3<sup>rd</sup> harmonic and the other harmonics with index number odd multiplies of 3 are in zero sequence and if TCR branches are connected in delta form, these harmonics do not flow through the power system and they circulate among TCR branches. When TCR branches are connected in  $\Delta$ form, only harmonics with index number  $6k\pm 1$  (k=1,2,3,...) will flow through the system (Figure 2.6, 2.7, 2.8).

Figure 2.6. TCR harmonic currents flow

Figure 2.7. TCR current values according to conduction angle

Figure 2.8. TCR harmonic current values according to conduction angle

#### **2.4 LADLE FURNACE**

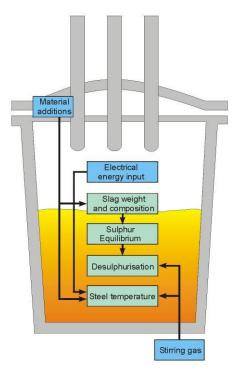

The *steelmaking* is one of the process steps in steel production in which the impurities such as carbon and sulfur are removed from steel and some materials are added such as manganese, nickel, chromium to produce the steel with required characteristics. This operation is done via *ladle furnace* by adjusting the temperature of molten iron ore (Figure 2.9).

Temperature adjusting (heating) of the material is the main function of ladle furnace (LF). There is a power transformer that converts high voltage low- current electric power into low voltage high current electric arc in order to heat the molten steel in the LF.

Figure 2.9. Ladle Furnace

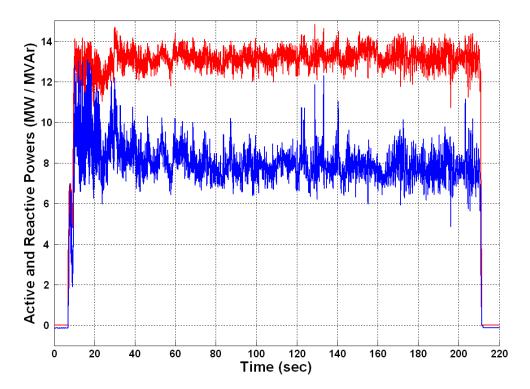

The electrodes at the low voltage side of the LF are connected to the phases of the power system respectively. When the heating treatment process starts, the electrodes come close to the slag at the top of the molten material and an electric arc occurs between the electrode pairs crossing through the slag surface. The current between the electrodes and the slag heats the molten material in the LF. By this way, the electric energy is transformed into thermal energy and the heat of the material is increased to the desired processing temperature (Figure 2.10, 2.11).

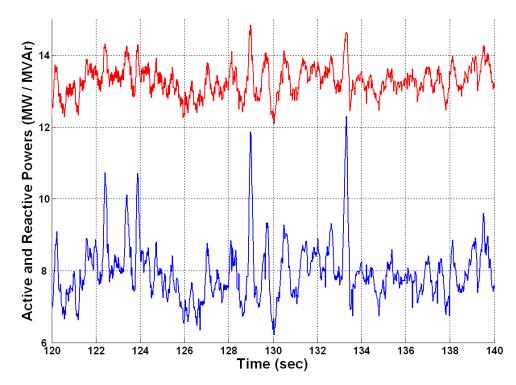

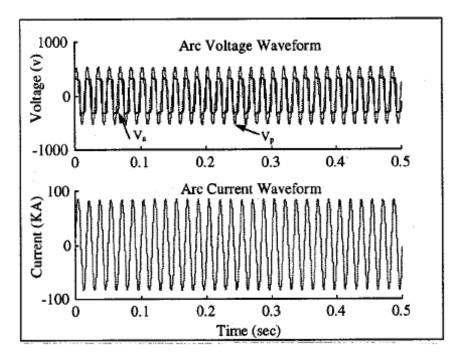

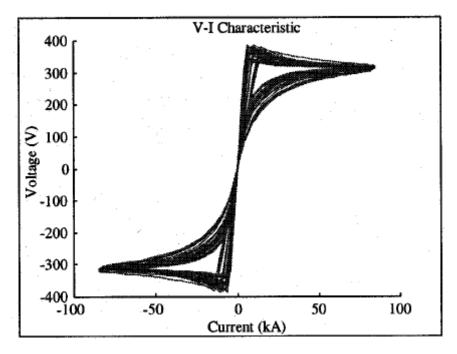

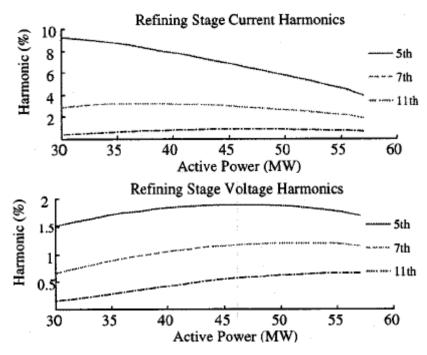

Since the ladle furnace generates electric arc and the arc has a nonlinear V-I characteristics (Figure 2.12, 2.13, 2.14) it generates inductive reactive power and harmonics at the power system. The power factor and harmonic content of power system exceed the standard permissible values. The reactive power and harmonic currents of the LF make it the second worst electric load after the arc furnace. In fact, ladle furnace electrical model is the same as the arc furnace electrical model at the refining stage of arc furnace operation.

Figure 2.10. Active (red) and Reactive (blue) powers of ladle furnace for one heating process

Figure 2.11. Active (red) and Reactive (blue) powers of ladle furnace for one heating process (zoomed)

Figure 2.12. Voltage and current waveforms of an electric arc

Figure 2.13. Nonlinear Voltage-Current characteristic of electric arc

Figure 2.14. Harmonics of an electric arc furnace at refining stage

#### **2.5 HARMONIC FILTERING**

With the development of electric technologies, modern power systems require power quality more than before. The efficiency of transmission and distribution systems is proportional to the power quality of the loads connected to the system. When the power quality increases, the infrastructure capacity can be used more efficiently that makes the investment costs lower. The economic point of view and customer satisfaction are the main reasons imposing power quality.

In a DC system, the system has only two parameters as bus voltage and line resistance; however, an AC system has bus voltage, frequency, voltage harmonic content and line impedance as power source. The effect of a load to an AC system is more complex than a DC system. When an electrical load is linear -that can be modeled by resistor, capacitor, inductor or dependent sources- then the load current is proportional to bus voltage in magnitude and phase. For a pure sine voltage signal, a linear load draws pure sine current at the same frequency. On the other hand, for a nonlinear load, the drawn current has harmonics which cause voltage harmonics at the bus voltage. Another load or customer connected to the same bus with the nonlinear load is affected by the harmonics in a bad manner.

In a power system, harmonics bring about overheating of electric devices (motors, transformers, etc.), resonance problems between the inductive and the capacitive parts (i.e. transmission line and shunt capacitors) and malfunctioning of the electronic devices which are designed and manufactured to be supplied at voltage with fundamental frequency and high currents in neutral conductors. A simple solution for these problems is to increase the electrical ratings of the devices and more lasting devices due to disturbances.

However, this solution is not economical from engineering perspective. More material, more cost and bulky designs are not appropriate when the optimum solution is considered. Instead of protection against harmonics at the load side, eliminating the harmonics is more feasible and reasonable. There are two types of harmonic filtering methods. The first one is connecting a passive filter that has a high impedance at fundamental frequency and low impedance at the harmonic frequency that is chosen to be eliminated. The second way is to use a DC/AC converter topology connected to the power system that inserts inverse of the harmonic current to eliminate.

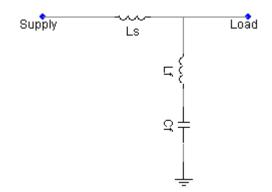

In a TCR type SVC, passive filters are commonly used. An LC resonant circuit (Figuree 2.15) tuned to any harmonic frequency supplies capacitive reactive power at fundamental frequency and filters out the harmonic current that it is tuned. Adding a reactor in series with the capacitor makes it a harmonic filter and reduces the transient current component at the switching instant.

Figure 2.15. Passive filter connection to a power system

For a passive filter connected to a power system, the impedance from the supply side is a capacitance at the fundamental frequency and if the supply side has no voltage harmonics, there are no current harmonics from the supply side through the load side. From the load side, the impedance of the bus is  $L_s ||(L_f+C_f)|$  which results in theoretically zero Ohm impedance at  $L_f$  and  $C_f$  resonance frequency. So, when the load generates harmonic near this resonance frequency, then this harmonic component will flow through the filter instead of the line.

Even if passive filters can be a better solution for harmonic elimination, there are resonance problems for harmonic currents. When the circuit topology is investigated for the load side, it is easy to see that there is a parallel resonance circuit in  $L_s||(L_f+C_f)$  form which has a resonance frequency at  $(L_f+L_s||C_f)$ . This parallel resonance circuit acts like an open circuit. If there is a current harmonic near this frequency, the voltage harmonic on the filter with this frequency will be amplified and more than the load harmonic current would flow both through the system and the filter.

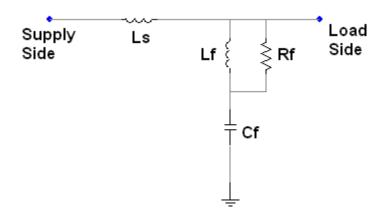

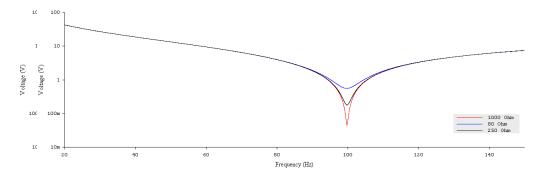

To eliminate this resonance problem, a resistance can be used at the filter side to make the impedance at parallel resonance frequency a real value instead of infinity. The damping resistor (Figure 2.16) eliminates the resonant problem, protects the filter capacitors against overvoltage and the new topology, and also filters other harmonics at higher frequencies to some extent.

Figure 2.16. Damped passive filter connection to a power system

For a 100 kVAr 5th harmonic filter at 1 kV bus with 5 uH line impedance, when the tuned frequency is 95% of the harmonic frequency, then the frequencyimpedance characteristic of the filter and the impedance seen from the load side are as shown in Figure 2.17.

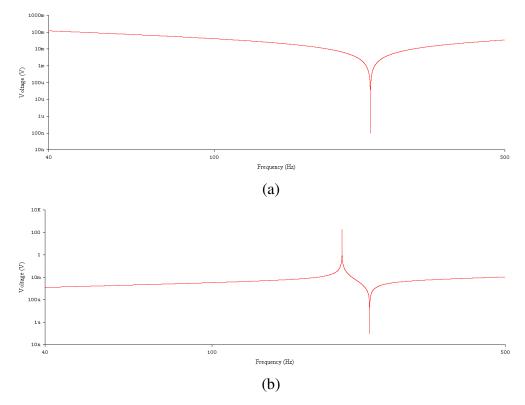

Figure 2.17. Frequency-impedance characteristics of filter (a) LC branch impedance (b) Impedance seen from the load side

When the impedance graphs are investigated, the filter has zero impedance near 238 Hz, and from the load side, the supply impedance is infinity near 204 Hz. If the load has any 4th harmonic, then this harmonic will be amplified. Because of this problem, 4th harmonic of the load may exceed the limit value specified in the associated standard.

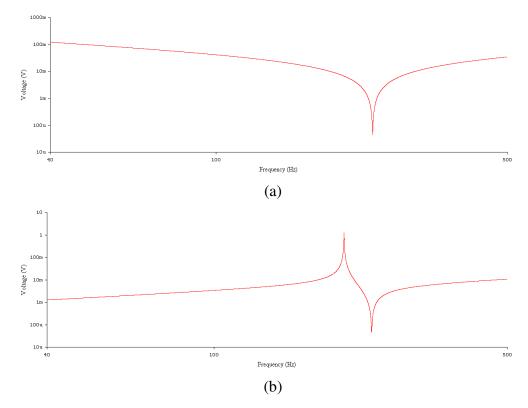

When a resistor is connected in parallel with the filter reactor, then the filter impedance and supply impedance change. The resultant impedances are not zero and infinity. The resultant frequency- impedance characteristics are shown in Figure 2.18.

Figure 2.18. Frequency-impedance characteristics of the damped filter (a) LC branch impedance (b) Impedance seen from the load side

The new impedance characteristics show that the resistor makes the frequency response of the filter smoother and the resonance problems are solved. Furthermore, the higher frequency harmonics are filtered with the new topology. The resistance value is calculated due to the optimization of filtering characteristic and active loss cost of the filter.

Another solution for parallel resonance problem for passive filters is to add another passive filter tuned to the previous harmonic frequency. If the load does not have dominant harmonic at this frequency, the second passive filter filters out the amplified harmonic and prevents it from penetrating into the through the power system.

Light flicker stands for the fluctuations at the fundamental component of the power system voltage between 8-100 Hz where the human eye is disturbed. The main reason of flicker is powerful loads changing rapidly. When the reactive

power of the load changes rapidly in large amounts, then the voltage drop on the transmission line becomes considerable. As a result of this voltage drop, the voltage value at the load bus decreases. If the reactive power of the load fluctuates, then the bus voltage fluctuates. The main reason of flicker is rapidly changing loads such as arc furnaces, ladle furnaces, welding machines, etc.

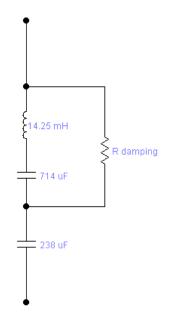

However, when there is a passive filter at the SVC stage, the harmonic component of fluctuating load current at the flicker frequency may be amplified because of the parallel resonance. For instance, when a  $2^{nd}$  harmonic filter is used, the parallel resonance frequency of the filter and line impedance may occur at 90 Hz neighborhood. A dirty load -like arc furnace or ladle furnace- generates interharmonic at this frequency neighborhood, the harmonic problem becomes more complicated. The second harmonic filter which is designed to filter the harmonics at 100 Hz neighborhood amplifies the interharmonics near this neighborhood. To avoid this problem, the harmonic filter is used in damped form which means that the damping resistor of the filter is small enough to filter a large frequency band but when the resistor gets smaller, filtering capability at the tuned frequency is reduced. The effect of damping resistor to filtering characteristic of a C-type second harmonic filter is shown in figure 2.19 and 2.20.

Figure 2.19. One phase of 13.8 kV/14.2 MVAr C-type 2<sup>nd</sup> Harmonic Filter

Figure 2.20. Filter characteristic of the C-type filter

#### 2.6 SVC DESIGN PROCEDURE

An SVC system is designed and constructed in 5 steps. These parts are power stage design, controller design, simulation, optimization and construction. The main idea of the procedure is to find the optimum point between power capacity + controller performance and financial cost + installation cost of system. For an SVC system, the producer and the customer negotiate and agree upon capacity, cost, and installation and operation type. After the agreement the producer should find the optimum design to have positive profit and the desired operation performance.

The power capacity of the SVC is defined by the field measurements of the load aimed to be compensated. Before the measurements, the load characteristic is defined by the help of customer. The power characteristic, operation duty cycle, load changes, etc. are to be defined and measurement technique and its duration are to be defined. At this stage, the previous information available in literature and guidance of the customer are very important to obtain the exact load characteristics.

After characterization of load, the measurement technique (full-cycle, 1 second average, 3 second average, energy meter, ...) and measurement time period (hour, day, week, ...) are defined. If the load cannot be characterized, then the most accurate measurement technique and the longest measurement time should be chosen. Since the power stage units are custom designed for the load, voltage and

environment parameters, and then the design error at this stage should be minimum for safe operation of SVC.

After the measurements, power quality parameters of the load such as active and reactive powers, power factor, harmonics, unbalance and flicker are to be calculated. The next step is the decision of load balancing. Since SVC can balance the unbalanced active power of load, the power capacity of SVC can be chosen for both reactive power compensation and load balancing.

If the load balancing option is chosen then the design of SVC power capacity should be done for compensator's delta branch impedances. By the help of Steinmetz equations the maximum inductive and capacitive powers for delta branches of SVC are calculated. Only if the reactive power compensation option is selected, then the capacitive and inductive power capacity of SVC can be chosen by using the maximum reactive power of the load as reference.

After capacity calculation, the structure of SVC is defined. By the help of load's power characteristic the SVC elements are chosen for compensation. All or some of TCR, FF, FC, TSC and TSR can be selected as SVC components to have the minimum cost and adequate performance. After structure design, the basic simulation of the system is done. At this stage, the correctness of capacity and structure design is controlled. For example, by the load's power characteristic the designer selects TSC as a component and load balancing option for operation type. At the basic simulation step, if he founds that the compensator cannot balance the active load when TSC is out of operation; as mentioned before, at this stage the design should be carried out with high attention to have zero error since modifying the power stage is very expensive after installation.

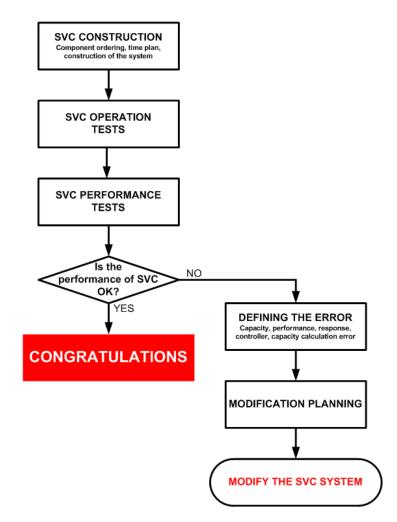

After basic simulation; if the results are not adequate for performance, then the error should be defined. If the error comes from capacity or structure stage, then the component parameters are modified due to the error. The other error source is simulation error that can be corrected by editing the simulation parameters. The flowchart of power stage design is shown in Figure 2.21.

Figure 2.21. Power Stage design

Power stage design is followed by the controller design of the SVC. The reference data for the controller are measurement data, performance goals, predefined controller budget, signal measurement techniques (voltage/current transformers, capacitive divider, lems, etc.), human machine interface (HMI), system monitoring.

Controller design procedure starts with control technique (PI, PID, feedforward) selection step. The dynamic characteristic of load power and performance goal is the main guides for control technique selection. If the rate of change of load's power is high and the reactive power error limits are small, then the response time of the controller must be small enough to meet the desired performance. The control technique can be selected by the guidance of literature and experience of previous applications.

For an electronic controller, the most important decision is choosing the implementation platform of the controller. If the control technique requires fast and complex calculations and controller budget is large enough, then digital platforms should be chosen. In opposition, if the control technique is simple (basic PID controller) and controller budget is limited, and then analog platform should be chosen. For selection of analog or digital controller, the following criteria are the guide for the designer. The advantages and disadvantages of digital implementation are listed in Table 2.2 and 2.3. When it is considered that analog electronics is the native solution, the following rules make the designer switch to digital electronics or not. The design procedure for the control is shown in Figure 2.22.

# Advantages of Digital Control

- System upgrade in the field is easier than that of solution.

- Arithmetic calculations are more flexible and accurate.

- The data processing is noise free. Once the data is transferred into digital platform (0s and 1s), the data have noise immunity.

- Suitable for modular design and implementation.

- Digital devices have more reliability. MTBF parameter is very large for digital than it that of the case.

- Communications between other elements and data logging is easier.

- Changing the structure controller does not require an alternation in the hardware.

- Digital systems provide improved sensitivity to parameter variations.

# Table 2.2. Advantages of Digital Controller

# Disadvantages of Digital Control

- Limited cycles due to the finite wordlength of the digital processor or ADCs and DACs.

- Platform has limited capability. After reaching the maximum capacity, another digital device is required for expansion.

- Production costs are higher for digital systems. There is a trade off between cost and performance and this should be taken into account at hardware decision stage before system design.

- Reduced signal resolution due to the finite wordlength of the digital processor.

## Table 2.3. Disadvantages of Digital Control

For analog controller, the first step is designing the flow chart of control and analog circuit design of the flow chart components. These steps can be done by designing an analog mainboard as base for the controller and analog PCBs for control elements (power measurement, triggering, etc.). In an ideal system, accuracy of analog circuits is 100%, but when the parameter characteristic of components for temperature changes is considered with an analog circuitry, calculation errors can be much higher than it is expected. This handicap should be taken into account and analog controller type should be chosen with considering the operation area of the SVC. If there is harsh environment, the PCBs should be well protected by coolers, heaters, air filters, which means more maintenance and small *mean time between failures* (MTBF) and more malfunctioning.

Figure 2.22. Controller design

When digital control is selected, the first step is choosing the digital platform for the controller. In digital electronics world, an electronic system can be designed and built by implementing each flowchart element by ICs and additionally a compact platform can be used with integrated embedded control, ICs, sensors, peripherals. The advantage of compact platforms is reducing the design and implementation job to software level that the designer only works on software. For discrete design with ICs, each part should be designed separately and the communications between parts should also be implemented. In opposition, with discrete designs each variable transmitted between parts can be monitored and custom designs can be done. For a compact platform, all of the operations take place inside the box and there is no possibility to intervene in the system for modification. The design engineer is restricted by the abilities of the product and if there is an upgrade need in the future a new or additional platform will be needed.

Using a compact platform makes the job easier but the ability of the system is restricted and expansion is stepwise. When there is a need for extra control job in discrete analog/digital design, adding a new PCB solves the problem. For compact platform case; if the used capacity is near 100%, new additions require an additional platform or a new platform with more capability.

After selecting the controller type, the preparation of simulation stage starts. The designed controller's units are mathematically modeled for simulations. The simulation platform is selected due to the accuracy required. If it is needed, a powerful simulation platform (high speed CPU, large RAM, etc.) is built. Then the simulation file is constructed on the simulation platform.

For the controller design stage, the important rule is that the designer can modify the controller and control strategy whenever he wants before controller implementation. Once the implementation gets started, then any modification means extra time, cost and effort. The critical point is the decision of the structure of the controller. If the deadline of the SVC construction limits research and development studies a basic and previously implemented control technique and controller platform are more suitable to reduce the risks. If the practice is a research and development job, a powerful compact controller platform makes the job easier by eliminating the electronics studies such as PCB design, implementation, and noise immunity.

After the controller design stage, the system is fully designed for simulation stage. The simulation file is run on the simulation platform selected in the previous stage. The first step is selecting the *simulation time step* for the accuracy of the results. The simulation time step should be small enough for measuring and calculation accuracy for analog case and it should be smaller than the operation time step of the controller for digital case.

The next step for simulation stage is testing the constructed blocks of simulation file. The SVC units and control units are tested basically to guarantee right operation of simulation. Currents, voltages, active/reactive powers, delay times of SVC units are tested for ideal cases. The response times, measurement and calculation accuracy, right operation, correctness of algorithms of control units are controlled by using constant values and basic signals like sine, square, triangle, sawtooth waves. Running the simulation to take constant power from TCR connected to an ideal source can be an example for this step. Morover, the simulation time step value is verified for accurate operation of simulations at this step.

If the simulation of units is completed successfully, then the whole system simulation of the complete system takes place. In the simulation stage the designer builds the controller structure. The design procedure is shown in Figure 2.23.

Figure 2.23. Simulation

In the first step of system simulation, the control parameters are defined. These parameters can be found by trial and error method or by solving the system transfer function. The method depends on the accuracy goal of the system.

If the desired system response is found, then the second system simulation takes place. At this step the measured data are integrated to the simulation to obtain the response of the design to the load to be compensated. At this step the important point is modeling the load by using the measured data. When the field data is simulated with the designed SVC in parallel the resultant voltage drop, harmonic content and loading of transmission and distribution elements will be improved. The effect of these improvements to the load should also be modeled in the simulations to have more accurate results. Instead of the conventional modeling techniques like component based modeling, more accurate techniques like adaptive back-propagation, improved composite load modeling may be used [15].

At the second system simulation step the response of the system is optimized to have the minimum errors as a result. The optimization is done by changing the control parameters and control strategy. If the results show that the control strategy should be improved and if the controller design is not capable for this improvement, the controller should be changed in the next step of design. Furthermore, the basic simulation step results in the phase of power stage design are verified at the second simulation step.

The following stage is the optimization of the system design (Figure 2.24). Up to this stage, the system is designed for full compensation in ideal by selecting the capacity and performance for the worst case of load and zero error in ideal. When the result is considered in engineering philosophy, the goal should not be the case nearest to ideal. Optimum solution is to have the best solution with the lowest price. In optimization stage the system's parameters are modified due to the system error result of simulation stage. If the results are not within the error limits, then the designer has two choices. The first one is modifying the power capacity of the system by increasing the capacity by the redundant error value. This option is the expensive one but gives the designer the chance to be more flexible while choosing new parameters and structure for the power stage in the next design loop iteration. The second option is modifying the controller of the system. From the simulation results, if it is seen that a better control technique (adding a second control loop or adaptive control) decreases the error under the limit values, then the designer can select this step. Besides selecting one of the modification options, both of them can be selected for optimization iteration. At this step, the choice and modification strategy can be selected by the guidance of literature and previous experience.

When the prices of increasing the capacities of power stage and controller are compared, modifying the controller at this step is more reasonable. By this way, the designer may found an optimum point with smaller price.

Figure 2.24. Optimization

If the resultant error values are within the limits, then the next step is calculating the *error permission value* of the design. *Error permission value* is the difference

between the predefined error limits and the resultant error values. If the ratio of error permission value is comparable to ratio of error level, then the design is modified to decrease the error permission value. To do this decrement, the system capacity is reduced. When the price of power stage capacity cost is compared with the controller cost, reducing the expensive one, power capacity, is more reasonable. In the next optimization stage of iteration loop, the designer could decrease the controller capacity to reduce the cost of the system. The key point of this modification is reducing only one type of parameter. When the both capacity of power stage and controller capacity are reduced; then in the next iteration loop the result may diverge such that the simulation results are above the limits. This step is a controlled experiment and the optimization is done for power stage only.

If the error permission value is near 0, then the design procedure finishes and implementation and construction stages start. The optimization of the design is based on optimizing the power stage firstly and the controller secondly. The reason of designing the controller parallel with the power stage instead of sequential independent design procedures is to start with an closer point to the optimum case. When the design procedure finishes, the designer may optimize the controller again to reduce the controller's budget content in the project.

After the design procedure, the construction procedure takes place (Figure 2.25). The components of the SVC system are ordered, the time plan for the project is defined and the implementation and construction of the system is started. After the installation of the system, the SVC is tested in the field. The tests consists isolation tests of power stage components, operation tests of components (controller, voltage/current transformers, thyristors, etc.) and control parameter tests for no load, full load, step responses of the system. The test procedure is defined by the conditions and characteristics of the components and depends on the system design.

The next step is occupied by the performance tests, which means running the SVC system with load connected. If the results of the performance tests are within the

limits as planned in the design steps, then the job is done and the designer deserves a greeting.

Figure 2.25. Construction

If the performance tests' results do not meet the planned values, then the source of the error is defined. A modification plan is done and the required changes are applied to the system and the test procedure is run again.

## **CHAPTER 3**

### STRUCTURE OF PROTOTYPE SVC SYSTEM

## **3.1 POWER SYSTEM**

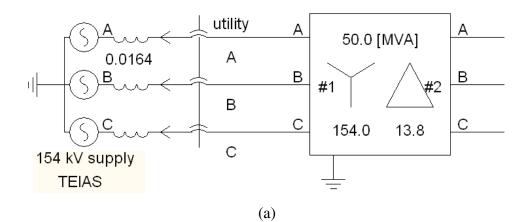

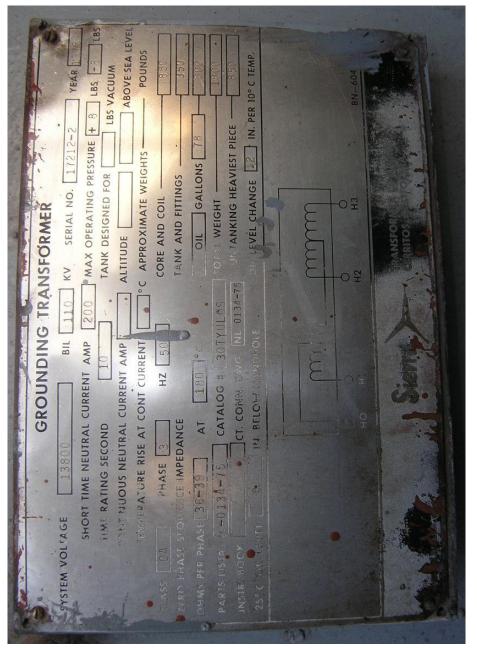

The power system to which the SVC is connected is the secondary side of 154/13.8 kV power transformer that supplies power to the two ladle furnaces of ERDEMİR Iron & Steel Factories Co. The transformer is wye connected at the primary side and delta connected at the secondary side; it is located at the TEİAŞ switchyard within the factory campus. Power is delivered to the factory by a 154 kV overhead line with a SCMVA 4500 MVA (Figure 3.1). The earth connection is maintained via a grounding transformer. There is no ground connection other than this one which means no zero sequence at the 13.8 kV bus.

The SVC system is connected to the secondary of the transformer and the ladle furnaces are connected through power cables with a length about 1 km. The ladle furnaces have step-down transformers with 13.8/0.4 kV voltage ratio shown in Figure 3.1. These step-down transformers are energized by circuit breakers at each heating process and this operation causes high inrush currents with a markedly  $2^{nd}$  harmonic current content.

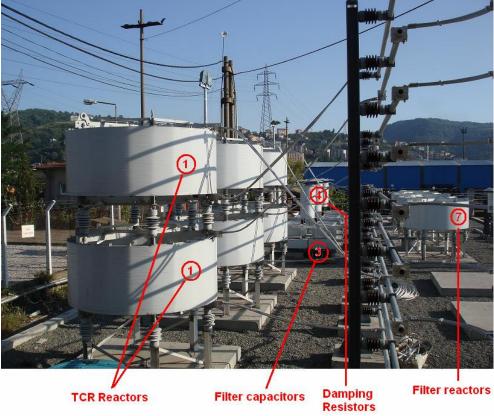

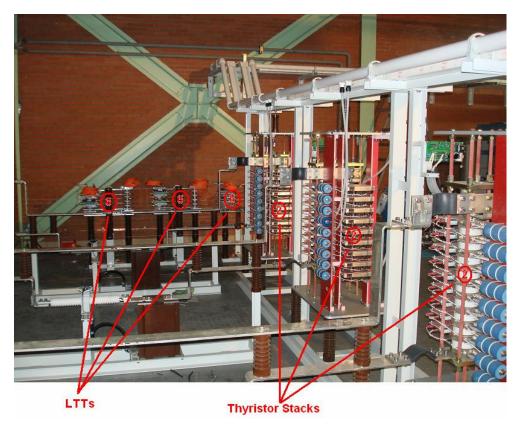

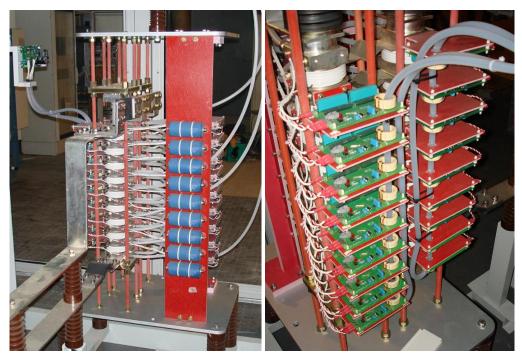

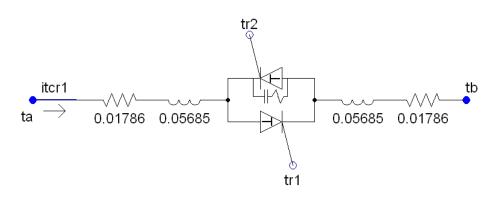

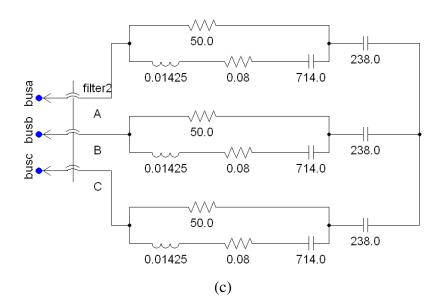

The power stage of the SVC has 3 reactor pairs with 16 MVAr connected in delta form and a C-type 2<sup>nd</sup> harmonic filter with 14.2 MVAr connected in wye connection without grounding (Figure 3.2 and 3.3). Three thyristor stacks with 9

thyristors in series are connected between the reactors for control of reactive power (Figure 3.3 - 3.6)

When the ladle furnace's step down transformer is energized, there occurs an inrush current which has a high amount of  $2^{nd}$  harmonic current. The amount of the  $2^{nd}$  harmonic current of inrush current is harmful for the filter capacitors. To eliminate the risk of failure, the damping status of  $2^{nd}$  harmonic filter is controlled by controlled resistors connected in parallel with damping resistors. These controllable resistors are taken into operation with LTTs when the current of any damping resistor passes predefined threshold level [24] (Figure 3.4).

Figure 3.1. Connection diagram of power system of SVC

38

Will be installed in 2008 2nd phase of the project

Figure 3.2. Power stage of SVC system

**TCR Reactors**

**Filter capacitors**

Figure 3.3. Views of power system elements of SVC (outside)

Figure 3.4. View of power system elements of SVC (inside)

Figure 3.5 Thyristor stack

Figure 3.6 General view of indoor stage

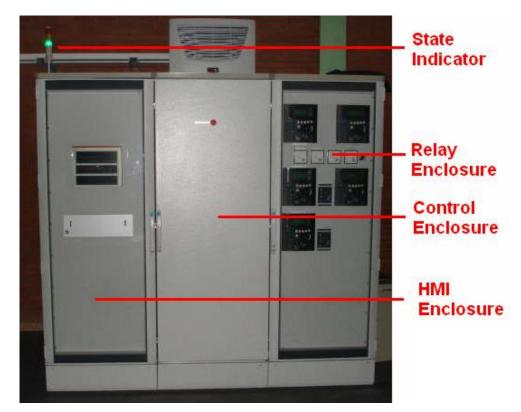

Figure 3.7 Control system enclosures

#### **3.2 CONTROL STAGE**

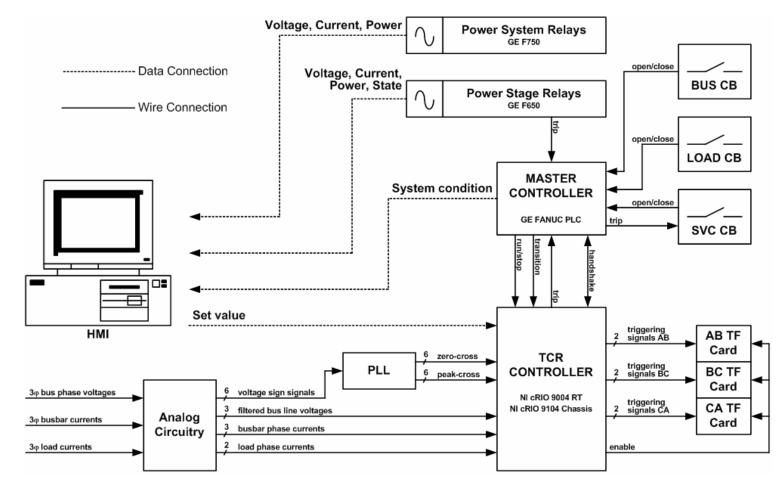

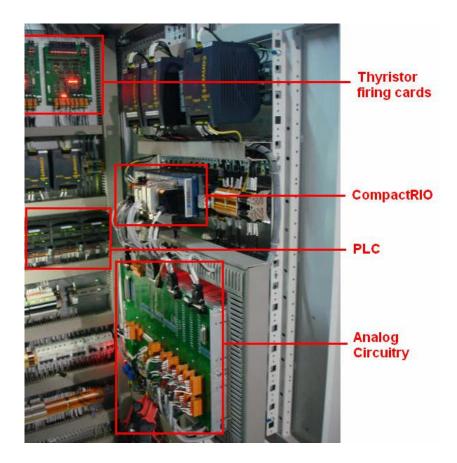

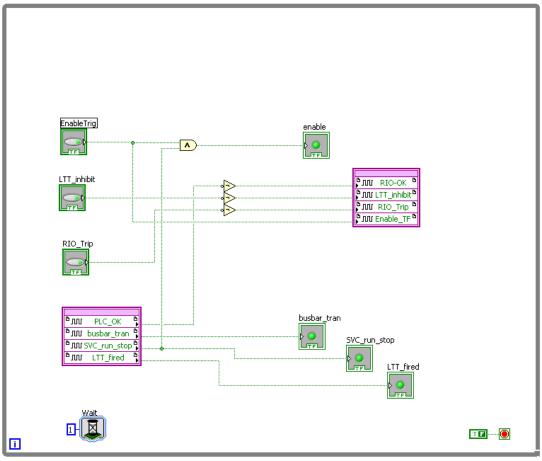

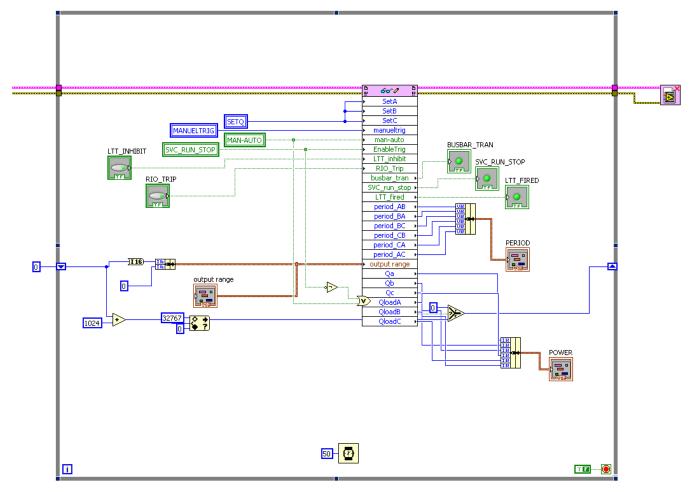

The control stage contains two main and three supplementary parts. The main parts are analog circuitry and NI CompactRIO Real-Time Controller. The supplementary parts are GE Fanuc PLC, GE F650 Bay controllers and PC based HMI.

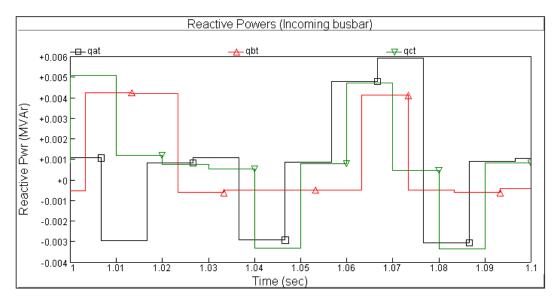

### 3.2.1 SVC Control

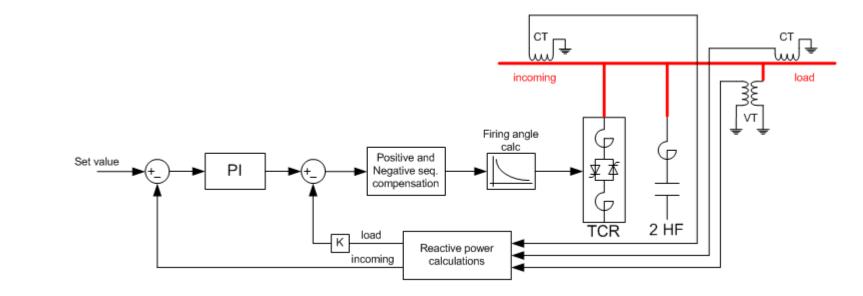

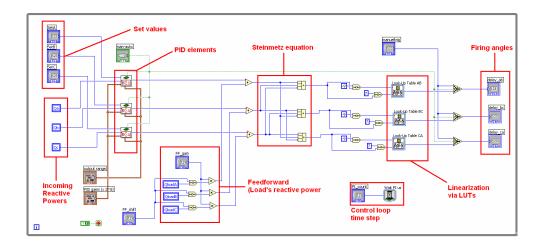

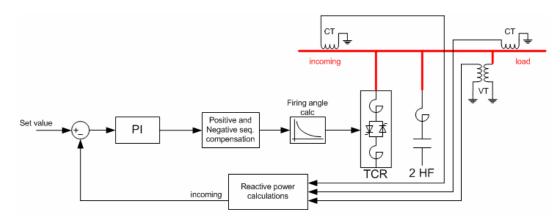

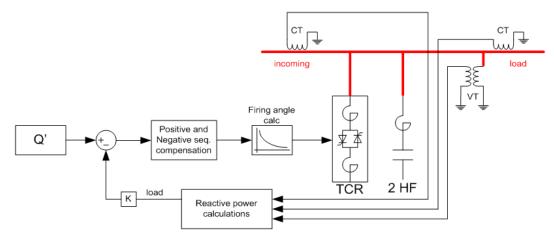

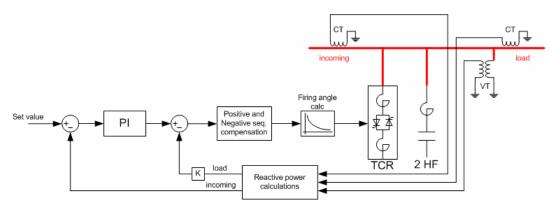

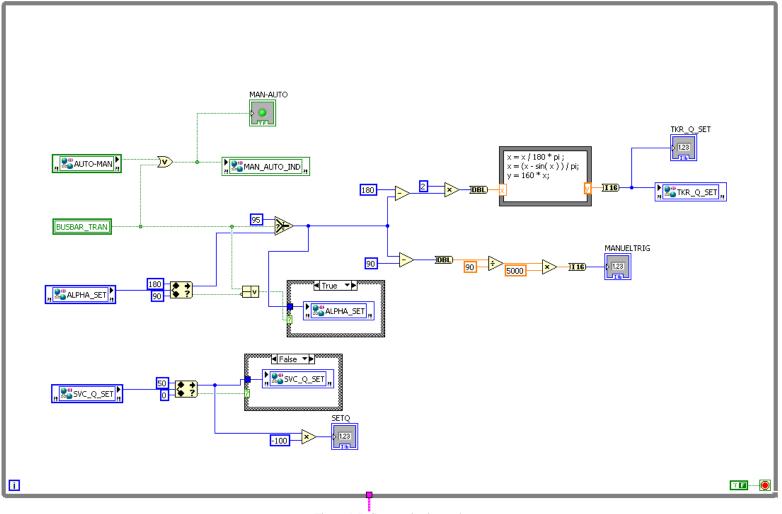

The control of the SVC is a closed loop PI with a feedforward gain. The job of the control loop is calculating the firing angles of thyristors. The calculation is done with incoming and load reactive powers. SVC compensates the reactive power of incoming bus to the set value and balance the active power of the load at each phase at incoming bus. SVC is given the compensation job for both positive and negative sequences.

In the control scheme shown in Figure 3.3, the PI regulator calculates the required inductive reactive power for the system for compensation at each phase. The feedforward part makes the response of closed loop controller faster and improves the system stability. The basic control of SVC is calculating the load reactive power and with the known reactive power of capacitive filters firing the thyristors of TCR branches such that the incoming reactive powers are zero. This type of control, feedforward control, is inherently stable and fast. The PI element makes the incoming reactive powers accurate and eliminates the errors due to voltage changes, firing errors, measurement errors etc. For rapidly changing loads such as ladle furnaces, feedforward part makes the control robust and decreases reactive power error. This decrement makes the bus voltage oscillations [15] [18].

The control diagram and control system structure are shown in Figures 3.8 and 3.9.

Figure 3.8. Control diagram of SVC

Figure 3.9. Control stage of SVC

The weights of its and feedforward controllers depend on reactive power measurement accuracy and speed, load variations, utility voltage fluctuations. If the load's current harmonic content has a big THD, then load reactive power measurement is not accurate to make the controller feedforward dominant. Since the incoming currents are total of load, TCR and harmonic filters then the THD of incoming busbar currents are decreased when compared to the load currents. If the power measurement is not capable of filtering current signals rapidly, then instead of using feedforward dominant control technique, it is more reasonable to use a feedback dominant control technique.

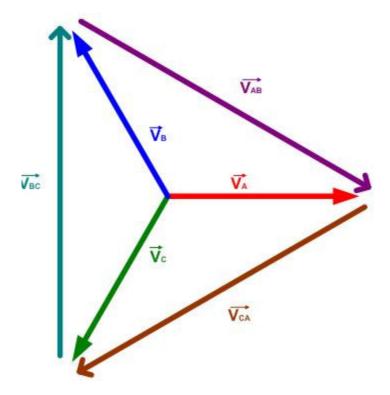

For reactive power calculation, the definition is that at each phase the phase current and phase voltage signal at 90° lagging are multiplied and the mean of this calculation for one period gives reactive power. For a 1 $\phi$  voltage signal, the power calculation is done by delaying the voltage signal 90° (5 ms for 50 Hz power system). In a 3 $\phi$  voltage signal instead of the delayed voltage signal, the other two phases' line-to-line voltage signal may be used.

Figure 3.10. Voltage phasors for a 3¢ system

The phase voltage phasors shown in Figure 3.10 are expressed in Equations 3.1 and 3.2.

$$V_{A} = V \angle 0^{\circ}$$

$$V_{B} = V \angle -120^{\circ}$$

$$V_{C} = V \angle -240^{\circ}$$

$$V_{AB} = V_{A} - V_{B} = \sqrt{3}V \angle -330^{\circ}$$

$$V_{BC} = V_{B} - V_{C} = \sqrt{3}V \angle -90^{\circ}$$

$$V_{CA} = V_{C} - V_{A} = \sqrt{3}V \angle -210^{\circ}$$

(3.2)

Instead of generating delayed signals, it is easier to use line-to-line voltages for reactive power calculation. In this case, the results are  $\sqrt{3}$  times the reactive powers.

$$Q_{A} = \frac{1}{T} \int_{0}^{T} V_{A} \cos(\omega t - 90^{\circ}) \times I_{A} \cos(\omega t - \beta) dt$$

$$Q_{A} = \frac{1}{\sqrt{3}} \frac{1}{T} \int_{0}^{T} V_{BC} \cos(\omega t) \times I_{A} \cos(\omega t - \beta) dt$$

(3.3)

For line-to-line voltage calculation, the magnitudes of voltages are assumed the same for each line-to-line and the phases are assumed 120° far from the previous one. It means that there is no negative and zero sequence components for the supply voltage signals. Since SVC is connected without neutral and it has no capability to compensate the zero sequence component of the load, then only the line-to-line voltages are read by the controller.

If the load current has a negative sequence component, the voltage at the load bus has also a negative sequence component. When the SVC starts to the compensation of load, the incoming currents become balanced and the voltage drop on the line impedance becomes balanced. At the steady state operation, the bus voltages have no negative sequence component. For this part of operation, line impedance has an important effect on load balancing. When the line impedance is large, load balancing operation takes more time which means longer settling time.

For reactive power compensation and load balancing, SVC compensates both negative and positive sequence currents of the load. The positive sequence compensation is done by injecting the inverse of one third of total reactive power to each phase.

Negative sequence compensation is the load balancing operation. For a  $3\phi$  balanced voltage system without neutral connection, when the reactive power of all phases are zero, then the load and SVC total is seen as three equal resistances connected to the bus. The main idea of compensation with load balancing is modeling the load as a delta connected circuit and controlling the SVC to eliminate the negative sequence and reactive components of the load currents.

$$V_{a} = V$$

$$V_{b} = V \times h^{2}$$

$$V_{c} = V \times h$$

$$h = e^{j2\pi/3} = -1/2 + j\sqrt{3}/2$$

(3.4)

The phase voltages are defined as shown in equation 3.7 and the line-to-line voltages becomes as follows.

$$V_{ab} = V_a - V_b = (1 - h^2) V$$

$$V_{bc} = V_b - V_c = (h^2 - h) V$$

$$V_{ca} = V_c - V_a = (h - 1) V$$

(3.5)

Assuming that the load is delta connected then the delta branch currents of the load becomes;

$$I_{ab} = Y_{1}^{ab} x V_{ab} = Y_{1}^{ab} x (1 - h^{2}) V$$

$$I_{bc} = Y_{1}^{bc} x V_{bc} = Y_{1}^{bc} x (h^{2} - h) V$$

$$I_{ca} = Y_{1}^{ca} x V_{ca} = Y_{1}^{ca} x (h - 1) V$$

$$48$$

(3.6)

From the delta branch currents, the phase currents can be acquired

$$I_{a} = I_{ab} - I_{ca} = (Y_{1}^{ab} x (1 - h^{2}) - Y_{1}^{ca} x (h - 1)) V$$

$$I_{b} = I_{bc} - I_{ab} = (Y_{1}^{bc} x (h^{2} - h) - Y_{1}^{ab} x (1 - h^{2})) V$$

$$I_{c} = I_{ca} - I_{bc} = (Y_{1}^{ca} x (h - 1) - Y_{1}^{bc} x (h^{2} - h)) V$$

(3.7)

Instead of calculating the phase impedances from phase currents, using symmetrical components of the currents makes the solution easier since one of the goals is eliminating the negative sequence currents (one of the symmetrical components). Then the symmetrical components of the line currents become as follows. To make the transformation orthogonal,  $1/\sqrt{3}$  is used instead of 1/3.

$$I_{0} = (I_{a} + I_{b} + I_{c}) / \sqrt{3} = 0$$

$$I_{1} = (I_{a} + h \times I_{b} + h^{2} \times I_{c}) / \sqrt{3} = (Y_{1}^{ab} + Y_{1}^{bc} + Y_{1}^{ca}) V\sqrt{3}$$

$$I_{2} = (I_{a} + h^{2} \times I_{b} + h \times I_{c}) / \sqrt{3}$$

$$= - (h^{2} \times Y_{1}^{ab} + h \times Y_{1}^{bc} + Y_{1}^{ca}) V\sqrt{3}$$

(3.8)

With analogy the compensator currents will be

$$I_{0\gamma} = 0$$

$$I_{1\gamma} = j (B_{\gamma}^{ab} + B_{\gamma}^{bc} + B_{\gamma}^{ca}) V\sqrt{3}$$

$$I_{2\gamma} = -j (h^2 x B_{\gamma}^{ab} + h x B_{\gamma}^{ba} + B_{\gamma}^{ca}) V\sqrt{3}$$

(3.9)

For negative sequence compensation the equation (3.10) and for reactive power compensation in positive sequence equation (3.11) should be satisfied.

$$I_{21} + I_{2\gamma} = 0 \tag{3.10}$$

$$Im (I_{11}) + Im (I_{1\gamma}) = 0$$

(3.11)

Using equations 3.10 and 3.11 with 3.9, the delta branch impedances of compensator become as follows

$$B_{\gamma}^{ab} = -1/(3\sqrt{3}V) (Im (I_{11}) + Im (I_{21}) - \sqrt{3} Re (I_{21}))$$

$$B_{\gamma}^{bc} = -1/(3\sqrt{3}V) (Im (I_{11}) - 2 Im (I_{21}))$$

(3.12)

$$B_{\gamma}^{ca} = -1/(3\sqrt{3}V) (Im (I_{11}) + Im (I_{21}) + \sqrt{3} Re (I_{21}))$$

Converting the symmetrical component impedances in equation (3.9) to delta branch impedances, the result becomes as

$$\begin{split} B_{\gamma}^{\ ab} &= -1/(3V) \ ( + Im \ (I_{al}) + Im \ (hI_{bl}) - Im \ (h^{2}I_{cl}) \ ) \\ B_{\gamma}^{\ bc} &= -1/(3V) \ ( - Im \ (I_{al}) + Im \ (hI_{bl}) + Im \ (h^{2}I_{cl}) \ ) \\ B_{\gamma}^{\ ca} &= -1/(3V) \ ( + Im \ (I_{al}) - Im \ (hI_{bl}) + Im \ (h^{2}I_{cl}) \ ) \end{split}$$

(3.13)

By this formula, the branch impedances of SVC can be calculated due to wye impedances of load. For AB branch

$$\begin{split} B_{\gamma}^{\ ab} &= -1/3 \ ( + \ Im \ ( \ I_{al} / \ V) + \ Im \ ( \ hI_{bl} / \ V) - \ Im \ ( \ h^{2}I_{cl} / \ V) \ ) \\ B_{\gamma}^{\ ab} &= -1/3 \ ( + \ Im \ ( \ I_{al} / \ V_{a} \ ) + \ Im \ ( \ I_{bl} / \ V_{b} \ ) - \ Im \ ( \ I_{cl} / \ V_{c} ) \ ) \\ B_{\gamma}^{\ ab} &= -1/3 \ ( + \ Im \ ( \ Y_{l}^{\ a} \ ) + \ Im \ ( \ Y_{l}^{\ b} \ ) - \ Im \ ( \ Y_{l}^{\ c} \ ) \ ) \\ B_{\gamma}^{\ ab} &= -1/3 \ ( + \ Im \ ( \ Y_{l}^{\ a} \ ) + \ Im \ ( \ Y_{l}^{\ b} \ ) - \ Im \ ( \ Y_{l}^{\ c} \ ) \ ) \\ B_{\gamma}^{\ ab} &= -1/3 \ ( + \ B_{l}^{\ a} + \ B_{l}^{\ b} - \ B_{l}^{\ c} \ ) \end{split}$$

When both sides are multiplied by  $V^2$  then the equation becomes for AB branch as follows

$$V^{2} B_{\gamma}^{ab} = -1/3 ( + B_{l}^{a} + B_{l}^{b} - B_{l}^{c} ) V^{2}$$

$$(\sqrt{3}V)^{2} B_{\gamma}^{ab} = - ( + V^{2} B_{l}^{a} + V^{2} B_{l}^{b} - V^{2} B_{l}^{c} )$$

$$V_{l-l}^{2} B_{\gamma}^{ab} = - ( + V^{2} B_{l}^{a} + V^{2} B_{l}^{b} - V^{2} B_{l}^{c} )$$

$$Q_{\gamma}^{ab} = - ( Q_{l}^{a} + Q_{l}^{b} - Q_{l}^{c} )$$

(3.15)

$$Q_{\gamma}^{\ ab} = -(+Q_{l}^{\ a} + Q_{l}^{\ b} - Q_{l}^{\ c})$$

$$Q_{\gamma}^{\ bc} = -(-Q_{l}^{\ a} + Q_{l}^{\ b} + Q_{l}^{\ c})$$

$$Q_{\gamma}^{\ ca} = -(+Q_{l}^{\ a} - Q_{l}^{\ b} + Q_{l}^{\ c})$$

(3.16)

### 3.2.2 Analog Circuitry

The power system data acquired by voltage and current transformers are converted to electronic signals by an analog circuitry (Figure 3.11). The signals for reactive power calculation and thyristor firing are built at this part. The electric signals from voltage and current transformers are converted to small voltage signals via lems.

Figure 3.11. Analog circuitry

Since the SVC system can compensate the reactive power at the fundamental frequency, then the reactive power calculation for compensation should include only the fundamental components of the voltage and current signals. For this purpose, the voltage signals are filtered by a bandpass filter tuned to fundamental frequency, 50 Hz. Reactive power calculations are done by multiplying voltage and current signals. Since the integral of two signals at different frequencies and in product form is zero over one cycle, then filtering only voltage signals is enough to calculate the reactive power at fundamental frequency. Reactive power calculation with fundamental components of voltage and current signals gives the same result

with reactive power calculation with the filtered voltage and the unfiltered current signals.

$$V = \sum_{n} V_n \cos(n\omega t + \alpha_n)$$

(3.17)

$$I = \sum_{n} I_{n} \cos(n\omega t + \beta_{n})$$

(3.18)

$$\frac{1}{T} \int (V \times I) dt = \frac{1}{T} \int (V_1 \times I) dt = \frac{1}{T} \int (V_1 \times I_1) dt$$

(3.19)

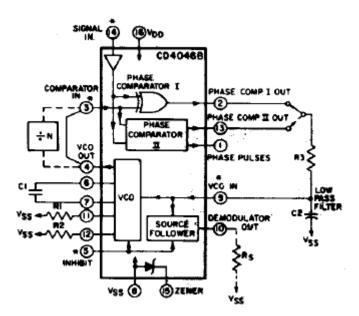

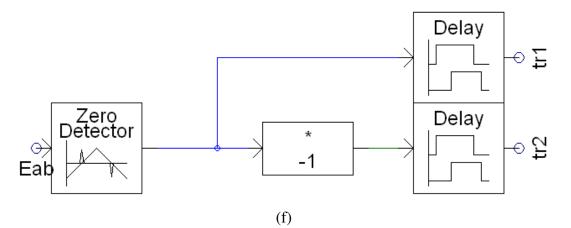

Thyristors of TCR are phase controlled and the phase reference is acquired by the zero-crosses of line voltages. To avoid multiple zero-crosses, filtered voltage signals are used for the phase reference. To avoid misfiring which cause flow of DC current, the thyristors should be triggered after the peaks of voltage signals. The peaks of voltage signals are detected by a PLL circuit. The input of the PLL circuit is a square wave generated by voltage signals, and output is the sign of voltage signals. The filtered voltage signals are compared to ground by a comparator and the output of the comparator is used as voltage sign signal. The peak of line voltage is the middle of the sign signal that is the second most significant bit of PLL counter. Using PLL guarantees that firing pulses to the thyristor stacks are always after the voltage peak and the risk of DC firing vanishes. Here, the important criterion for the PLL stage is the response time of the circuitry to the frequency changes at the bus voltage. When there is a frequency change, the PLL should settle down rapidly and generate the new peak signals at new position. The PI controller inside the PLL should not oscillate in a large scale. Since the triggering reference is the output of PLL, then the firing angle of TCR oscillates and the reactive power generated by the TCR also oscillates due to PLL PI oscillations. The PI parameter setting of PLL is carried out assuming that the bus frequency changes are 0.1 Hz for a cycle. Since the PLL input square wave is generated from the filtered voltage signal, the minor changes occurring the transients are eliminated and only the major frequency changes of utility frequency are effective. For PLL stage, CD4046BE (Figure 3.12) is used and the error of the peak signal is set to 5 us.

Figure 3.12. Inside of CD4046BE PLL

## 3.2.3 Real-Time Computing

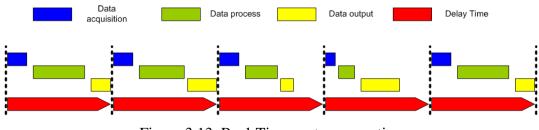

The term *real-time* refers to an application that receives information and the corresponding output is immediately responded without any delay. In real-time world, input information and output response are synchronous with no time period.

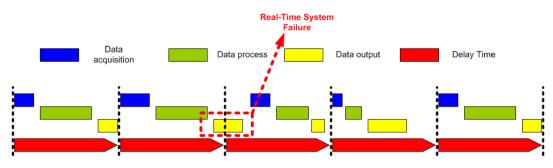

In a *real-time system*, the deadlines between inputs and outputs are predefined and the execution time between the input event and the system response is always constant (Figure 3.13). By contrast, a non-real-time system has no deadlines for outputs and even if its responses to input events are very fast [10][11][12][13][14].

Figure 3.13. Real-Time system operation

In electrical manner, fully analog electronic systems are real-time systems. The time delay between any input and its corresponding output is always constant. In ideal case there is no delay and in practical case the delays due to internal impedances of ICs are constant. A dedicated digital electronic system is also a real-time system. For example, a flip-flop circuit triggered with a clock signal and changing its state at each clock pulse is a real-time system. The output state of the flip-flop is defined by the present state and the input signal. Computer based real-time systems are the result of the developments of microcomputer ( $\mu$ C) technologies. For a  $\mu$ C based real-time system, the  $\mu$ C program has deadlines for the responses to the input events.

In a real-time system correctness of operation depends not only upon the right outputs but also upon the time delays. If the corresponding output is not responded for an input event before deadline, it is called as a *real-time system failure* (Figure 3.14).

Figure 3.14. Real-Time system failure

#### 3.2.4 LabVIEW and NI CompactRIO Real-Time Controller

LabVIEW (abbr. of Laboratory Virtual Instrumentation Engineering Workbench) is a virtual programming language (VPL) of National Instruments (NI). LabVIEW development environment provides data acquisition, instrument control, industrial control and measurement, and embedded design abilities to user. It is available on various platforms such as Windows, UNIX, Linux and Mac OS.

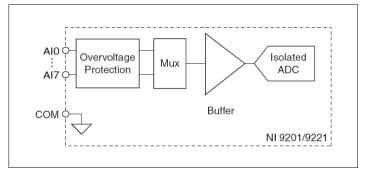

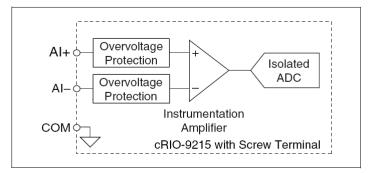

The NI CompactRIO (Reconfigurable I/O) programmable automation controller (PAC) is a reconfigurable control and acquisition system that includes a real-time processor and a reconfigurable chassis with FPGA connected analog and digital I/O modules. NI cRIO RT Controller 9004 has 195 MHz processor, 64 MB DRAM and 512 MB CompactFlash. NI cRIO 9104 Reconfigurable Embedded Chassis has 3 MGate Xilinx FPGA chip (XC2V3000-4FG676I) and 8 reconfigurable slots.

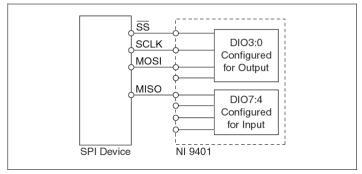

The main part of SVC control stage is NI CompactRIO controller (Figure 3.15). Reactive power calculations, PI controller and firing pulse generation take place inside the chassis FPGA of cRIO. The chassis structure is configured for the requirements of reactive power calculation and firing pulses. There are also digital I/Os for system control.

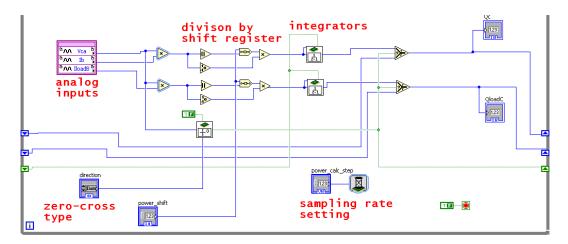

The reactive power calculations are made by using the equation 3.3. The current and voltage signals are sampled periodically in 16 bit form with a sampling rate 25 kHz simultaneously, and for each phase reactive power is calculated by its using current and the other phases by line-to-line voltage signal. At each sampling, the current and voltage signals are multiplied. The analog input channels have noise. Moreover, the integrator has 32 bit register and the sum of 500 data at each cycle may overflow this register. To eliminate the noise of input signals and the risk of overflow, the result of the multiplication is divided with a constant. The division is done by a shift register which is faster than the standard divider element and occupies less memory in the FPGA.

The result of division is put in to an integrator. This operation is the integral part of Equation 3.3. The output of this integrator is sampled at each zero cross of voltage signal and later in the next sampling step, the integrator is reset. In the next step, the multiplication result is taken as initial value to the integrator not to lose the sampled data.

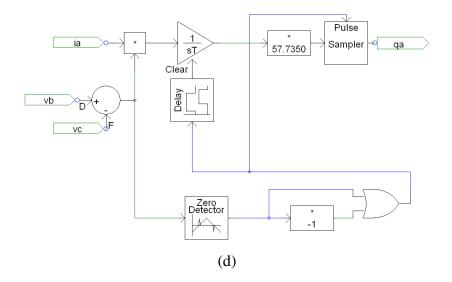

Figure 3.15. NI cRIO mounted inside the control enclosure

The following code part of LabVIEW FPGA calculates the reactive power of phase A for incoming and load busses. The sampled signal data are multiplied by a 32 bit multiplier. The zero cross detector generates a TRUE signal if the voltage crosses 0 V to sample the integrator data and reset the integrator in the next step. The signal is delayed for a sampling step time, 40 us. When a zero cross occurs for voltage signal, the integral output is written to a local variable. If the zero-cross type is selected "either", then the calculations are done for every half cycle; if the direction is selected "minus-plus" or "plus-minus", then the calculations are done for full cycle.

For the reactive power formula in Equation 3.3, the 1/T constant is ignored in calculation operation because of the sampling rate. If the sampling rate is low and the number of sampled data at each cycle is small, then the right way to measure the reactive power is to synchronize the sampling frequency to line frequency, which means constant sampling at each cycle. If the sampling frequency is high enough, the output of integral gets nearer to (50 Hz / Line frequency) x Actual Reactive Power. For a constant sampling rate, the variations in reactive power calculation vary only with line frequency changes. Since the line frequency varies in a narrow range and the rate of change of line frequency is small, then eliminating 1/T part of Equation 3.3 changes the calculated reactive power in a small range which can be corrected by the PI controller easily.

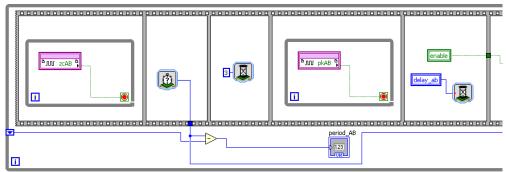

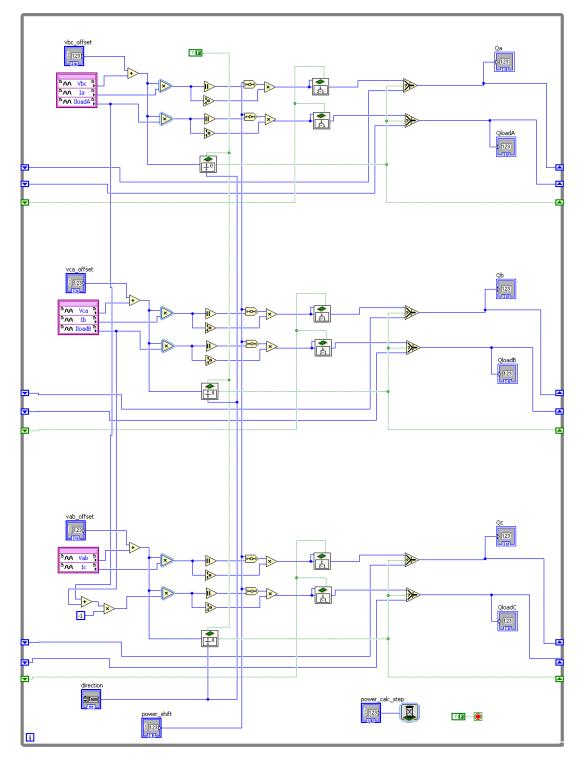

The code shown for reactive power calculation (Figure 3.16) for incoming and load bus at phase B. For the other phases, the code is the same with other analog channels.

Figure 3.16. Reactive power calculation loop for phase B

The reactive power calculation loop is an infinite loop. It samples the analog inputs continuously and calculates the reactive power of the input signals.

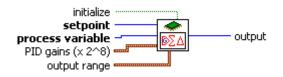

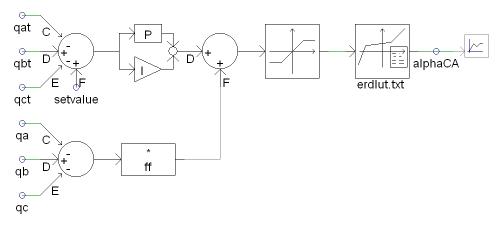

The second part of the code is PI loop that takes the set values and the calculated values of reactive power as input and runs 3 parallel PI controllers one for each phase. The feedforward part takes place at the output of PI component and the reactive power of the load is multiplied with a constant between 0 and 1 and it is subtracted from PI output.

Figure 3.17. Control loop