## X – BAND 7 BIT MMIC PHASE SHIFTER DESIGN

# A THESIS SUBMITTED TO THE GRADUATE SCHOOL OF NATURAL AND APPLIED SCIENCES OF MIDDLE EAST TECHNICAL UNIVERSITY

BY

# ERDİNÇ ERÇİL

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS

FOR

THE DEGREE OF MASTER OF SCIENCE

IN

ELECTRICAL AND ELECTRONICS ENGINEERING

SEPTEMBER 2006

| Approval of the Graduate Sc                           | hool of Natural and  | Applied Sciences                        |

|-------------------------------------------------------|----------------------|-----------------------------------------|

|                                                       |                      |                                         |

|                                                       |                      | Prof. Dr. Canan ÖZGEN                   |

|                                                       |                      | Director                                |

| I certify that this thesis sati<br>Master of Science. | sfies all the requir | ements as a thesis for the degree o     |

|                                                       |                      | Prof. Dr. İsmet ERKMEN                  |

|                                                       |                      | Head of Department                      |

|                                                       |                      | Assoc. Prof. Şimşek DEMİR<br>Supervisor |

| Examining Committee Mem                               |                      | Supervisor                              |

| Lamining Committee Wein                               | bers                 | Supervisor                              |

| Prof. Dr. Canan TOKER                                 | bers<br>(METU, EE)   | Supervisor                              |

| ·                                                     | (METU, EE)           | Supervisor                              |

| Prof. Dr. Canan TOKER                                 | (METU, EE)           |                                         |

| Prof. Dr. Canan TOKER  Assoc. Prof. Şimşek DEMİR      | (METU, EE)           |                                         |

I hereby declare that all information in this document has been obtained and presented in accordance with academic rules and ethical conduct. I also declare that, as required by these rules and conduct, I have fully cited and referenced all material and results that are not original to this work.

Erdinç ERÇİL

#### **ABSTRACT**

# X – BAND 7 BIT MMIC PHASE SHIFTER DESIGN

# ERÇİL, Erdinç

M.S., Department of Electrical and Electronics Engineering Supervisor: Assoc. Prof. Dr. Şimşek DEMİR

# September 2006, 130 pages

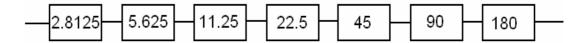

Modern phased array radars require large numbers of electronically controlled phase shifters to steer their beams to the desired direction. The amount of beam steering error depends on the phase resolution of the phase shifters as well as the performance of other parts of the antenna system. The size of the phase shifter in such systems is most of the time needed to be small, which necessitates the MMIC implementation. In the context of this thesis, an X band 7 bit MMIC phase shifter of 2.8125 degree phase resolution, including its layout, is designed using the design kit of OMMIC® Foundry. All bits of the phase shifter are designed to have low return loss so as to minimize the performance degradation due to loading effects upon cascading. Also some structures studied using the design kit of WIN® Foundry are presented. Both designs were performed using ADS®. For the optimum cascading of 7 bits, a MATLAB code was written and used.

Keywords: Digital phase shifter, MMIC, MMIC foundry, pHEMT.

## X – BANT 7 BİT MMIC FAZ KAYDIRICI TASARIMI

# ERÇİL, Erdinç Yüksek Lisans, Elektrik Elektronik Mühendisliği Bölümü Tez Yöneticisi: Doç. Dr. Şimşek DEMİR

# Eylül 2006, 130 sayfa

Modern faz dizili anten radarlarında hüzmenin istenen tarafa yönlendirilmesi için çok miktarda elektronik denetimli faz kaydırıcıya gereksinim duyulmaktadır. Bu sistemlerde huzme açısı hatası sistemin diğer elemanlarının performansına olduğu kadar, kullanılan faz kaydırıcıların faz çözünürlüğüne de bağlıdır. Söz konusu sistemlerde kullanılacak faz kaydırıcı boyutlarının küçüklüğü MMIC teknolojisini gerektirmektedir. Bu tez kapsamında OMMIC Firmasının ADS için hazırladığı tasarım kiti kullanılarak X bantta çalışan 7 bit sayısal bir faz kaydırıcı serimi ile beraber tasarlanmıştır. Tüm bitlerin tasarımında, art arda bağlanma sonucu ortaya çıkacak yükleme etkilerini azaltmak amacıyla, her iki porttan geriye dönüş kayıplarının iyi olmasına özen gösterilmiştir Ayrıca WIN Firmasının tasarım kiti ile tasarlanan bazı yapılar da sunulmaktadır. Her iki tasarım da ADS® programında yapılan benzetimler ile gerçekleştirilmiştir. Bitlerin performans açısından en uygun dizilimini tespit etme amacıyla bir MATLAB programı yazılmış ve kullanılmıştır.

Anahtar kelimeler: Sayısal faz kaydırıcı, MMIC, MMIC Firması, pHEMT.

To my beloved family

## **ACKNOWLEDGEMENTS**

I would like to express my sincere appreciation to my supervisor, Assoc. Prof. Şimşek Demir for his support, valuable recommendations and friendly encouragement.

I also wish to present my special thanks to Mehmet Erim İnal and Eralp Atmaca. Their experience and insights enlightened me throughout this work. Also, my thanks go to ASELSAN A.Ş. for all facilities provided.

I would like to acknowledge my gratitude to my friends and colleagues Can Barış Top, Nizam Ayyıldız, Burak Alişan, Bülent Alıcıoğlu and Necip Şahan and my flatmate Ali Haydar Akçay for their morale support and trust.

Finally, I feel grateful to my family, for their patience and understanding.

# **TABLE OF CONTENTS**

| ABSTR   | ACT                               | iv    |

|---------|-----------------------------------|-------|

| ÖZ      |                                   | v     |

| ACKNO   | OWLEDGEMENTS                      | vii   |

| TABLE   | OF CONTENTS                       | viii  |

| LIST O  | F FIGURES                         | xii   |

| LIST O  | F TABLES                          | xviii |

| LIST O  | F ABBREVIATIONS                   | xx    |

| СНАРТ   | TERS                              |       |

| 1. INTR | ODUCTION                          | 1     |

| 2. A CL | OSE LOOK AT PHASE SHIFTERS        | 6     |

| 2.1.    | General Considerations            | 6     |

| 2.1.1.  | Definition of Phase Shifter       | 6     |

| 2.1.2.  | Phase Shifter and Time Shifter    | 8     |

| 2.1.3.  | Phase Shifter Applications        | 8     |

| 2.1.4.  | Phase Shifter Classification      | 9     |

| 2.2.    | Integrated Circuit Phase Shifters | 11    |

| 2.2.1.  | Hybrid IC (MIC)                   | 12    |

| 2.2.2.  | MMIC                              | 12    |

| 2.2.3.  | RF MEMS                           | 12    |

| 2.2.4.  | BST (Barium Strontium Titanate)   | 13    |

| 2.3.    | Digital Phase Shifters            | 13    |

| 2.3.1.   | The Bit Concept                              | 15 |

|----------|----------------------------------------------|----|

| 2.3.2.   | The Number of Bits in a Phase Shifter        | 16 |

| 2.3.3.   | Digital Phase Shifter Requirements           | 17 |

| 2.3.3.1. | Phase Flatness                               | 17 |

| 2.3.3.2. | Number of Bits                               | 18 |

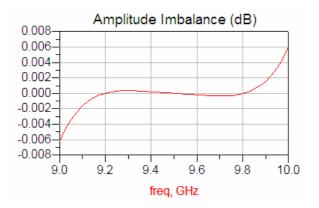

| 2.3.3.3. | Amplitude Imbalance                          | 18 |

| 2.3.3.4. | Insertion Loss                               | 18 |

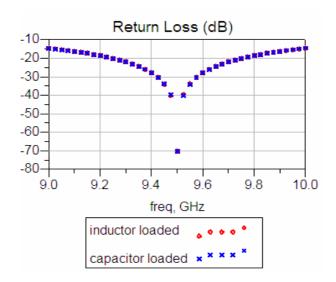

| 2.3.3.5. | Return Loss                                  | 19 |

| 2.3.3.6. | Switching Speed                              | 19 |

| 2.3.3.7. | Driver Voltages                              | 19 |

| 2.3.3.8. | Bandwidth                                    | 20 |

| 2.3.3.9. | Power Handling                               | 20 |

| 2.3.3.10 | . Size                                       | 20 |

| 3. DESIG | GN OF MMIC PHASE SHIFTERS                    | 21 |

| 3.1.     | Common Phase Shifter Topologies              | 21 |

| 3.1.1.   | Switched Line Phase Shifters                 | 21 |

| 3.1.1.1. | Sample Design                                | 22 |

| 3.1.2.   | High Pass - Low Pass Type Phase Shifters     | 23 |

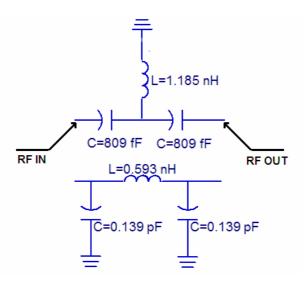

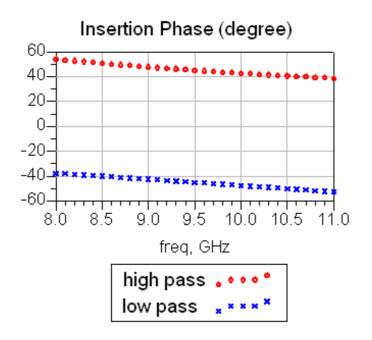

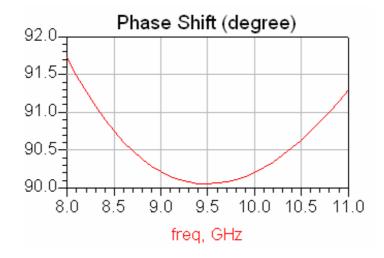

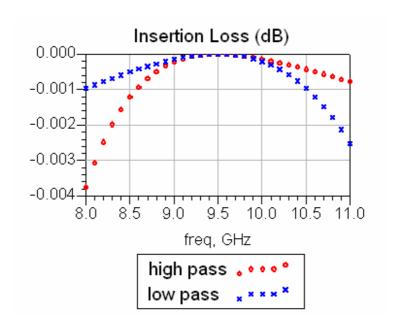

| 3.1.2.1. | Sample Design                                | 29 |

| 3.1.3.   | Loaded Line Phase Shifters                   | 32 |

| 3.1.3.1. | Sample Design                                | 33 |

| 3.1.4.   | Reflection Type Phase Shifters               | 35 |

| 3.1.4.1. | Sample Design                                | 36 |

| 3.2.     | The role of GaAs FETs in MMIC phase shifters | 39 |

| 3.2.1.   | GaAs FET Switching Mechanism                 | 40 |

| 3.2.2.   | Comparison of MESFET and HEMT                        | 42 |

|----------|------------------------------------------------------|----|

| 3.3.     | Working in Cooperation with A MMIC Foundry           | 43 |

| 3.3.1.   | Models                                               | 46 |

| 3.3.2.   | Measurements                                         | 46 |

| 3.3.3.   | Limitations                                          | 47 |

| 3.3.4.   | Layout Concepts                                      | 47 |

| 4. STUE  | DIES WITH WIN FOUNDRY                                | 49 |

| 4.1.     | Switch Process of WIN Foundry                        | 49 |

| 4.2.     | Design of a 90 Degree Bit                            | 50 |

| 4.2.1.   | Design of an SPDT with WIN Components                | 50 |

| 4.2.2.   | Combining the SPDTs with filters                     | 52 |

| 4.3.     | Design of the 180 Degree Bit                         | 56 |

| 4.4.     | Layout Phase                                         | 59 |

| 5. STUE  | DIES WITH OMMIC FOUNDRY DESIGN KIT                   | 60 |

| 5.1.     | Usage of OMMIC FET as a Switch                       | 61 |

| 5.1.1.   | Design of an SPDT with OMMIC Components              | 65 |

| 5.1.2.   | SPDTs used for the 90° and 180° bit                  | 71 |

| 5.2.     | Design of a Seven Bits of the Phase Shifter          | 73 |

| 5.2.1.   | Topologies Used in Design of the 7 Bit Phase Shifter | 74 |

| 5.2.2.   | Design of the Bits                                   | 75 |

| 5.2.2.1. | Design of the 2.8125 degree bit                      | 75 |

| 5.2.2.2. | Design of the 5.625 degree Bit                       | 78 |

| 5.2.2.3. | Design of the 11.25° Bit                             | 79 |

| 5.2.2.4. | Design of the 22.5° Bit                              | 81 |

| 5.2.2.5. | Design of the 90° bit                                | 88 |

| 5.2.2.6. | Design of the 180° bit                      | 91  |

|----------|---------------------------------------------|-----|

| 6. INTE  | GRATING THE BITS OF THE PHASE SHIFTER       | 94  |

| 6.1.     | Integration 1                               | 95  |

| 6.2.     | Integration 2                               | 98  |

| 6.3.     | A MATLAB Program for Integration of Bits    | 101 |

| 6.3.1.   | Results of the Batch Simulation             | 102 |

| 6.3.2.   | ADS Results for Sub-optimum Arrangements    | 109 |

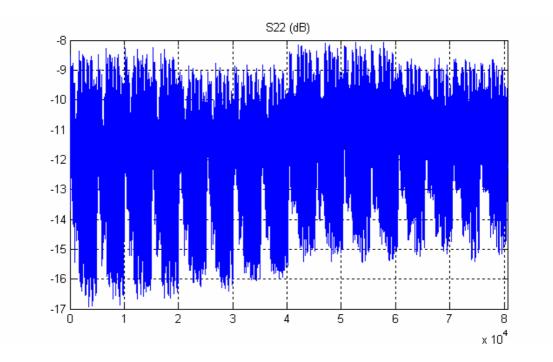

| 6.3.3.   | Arrangement 1: Minimum Peak Phase Error     | 109 |

| 6.3.3.1. | Arrangement 2: Minimum Rms Phase Error      | 112 |

| 6.3.3.2. | Arrangement 3: Minimum Amplitude Imbalance  | 115 |

| 6.3.3.3. | Arrangement 4: Minimum S11+S22              | 118 |

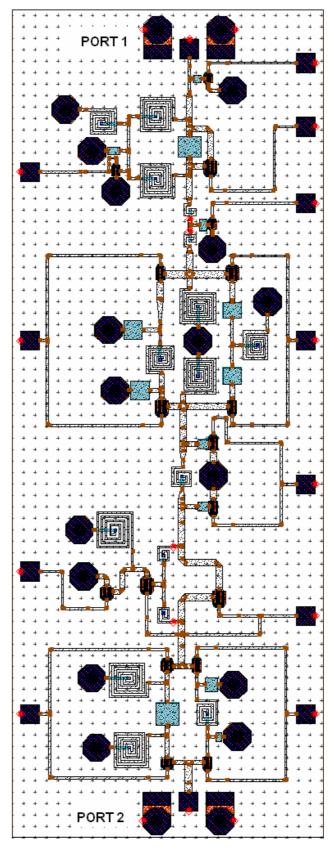

| 6.4.     | Layout of the Minimum Rms Error Arrangement | 120 |

| 7. CONC  | CLUSIONS                                    | 123 |

| REFERE   | ENCES                                       | 126 |

# LIST OF FIGURES

| Figure 2.1 General digital phase shifter structure                                       | 14      |

|------------------------------------------------------------------------------------------|---------|

| Figure 2.2 The basic phase shifter structure                                             | 15      |

| Figure 2.3 The method of virtually increasing the phase shift resolution in a p          | hased   |

| array antenna                                                                            | 17      |

| Figure 3.1 Topology of the switched line phase shifter                                   | 21      |

| Figure 3.2 Differential phase shift of the ideal switched line phase shifter             | 22      |

| Figure 3.3 TEE type LP/HP phase shifter                                                  | 23      |

| Figure 3.4 PI type LP/HP phase shifter                                                   | 24      |

| Figure 3.5 Series impedance Z                                                            | 24      |

| Figure 3.6 Shunt admittance Y                                                            | 25      |

| Figure 3.7 Generic TEE type network                                                      | 25      |

| Figure 3.8 The insertion loss comparison of the two T type networks                      | 26      |

| Figure 3.9 TEE to PI conversion                                                          | 28      |

| Figure 3.10 Circuit Diagram for the 90° phase shifter with ideal SPDT switcher           | es and  |

| passive elements.                                                                        | 29      |

| Figure 3.11 Insertion phases of the two filters used in the ideal 90° HP/LP              | phase   |

| shifter                                                                                  | 30      |

| Figure 3.12 Differential phase shift of the ideal 90° HP/LP phase shifter                | 30      |

| Figure 3.13 Insertion Losses of the two states of the ideal 90° HP/LPphase shift         | ter. 31 |

| Figure 3.14 Amplitude imbalance between the two states of the ideal 90° H                | HP/LP   |

| phase shifter                                                                            | 31      |

| Figure 3.15 Return losses of the two states of the ideal 90° HP/LP phase shifter         | · 32    |

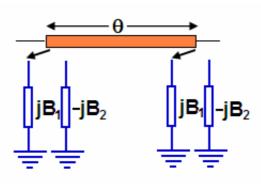

| Figure 3.16 Topology of the loaded line phase shifter                                    | 33      |

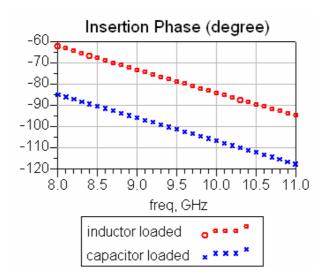

| Figure 3.17 Insertion phases at two states of the ideal loaded line phase shifter.       | 34      |

| Figure 3.18 Differential Phase Shift of the ideal loaded line phase shifter,             | 34      |

| <b>Figure 3.19</b> Insertion losses in two states of the ideal loaded line phase shifter | 34      |

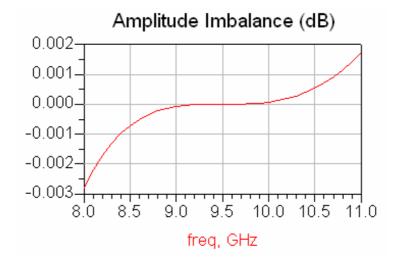

| Figure 3.20 Amplitude imbalance between the two states of the ideal loaded line                      |

|------------------------------------------------------------------------------------------------------|

| phase shifter                                                                                        |

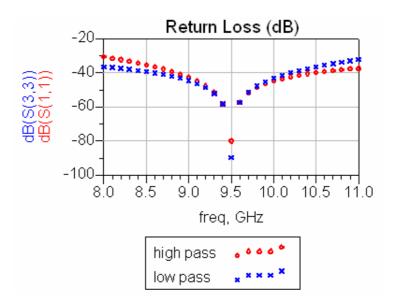

| Figure 3.21 Return losses of the two states of the ideal loaded line phase shifter 35                |

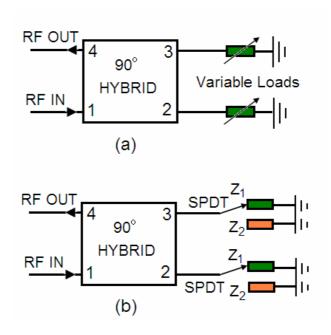

| Figure 3.22 Reflection type phase shifter with 90 degree hybrid: (a) analog                          |

| implementation (b) digital implementation                                                            |

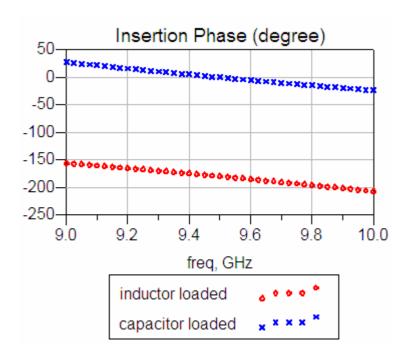

| Figure 3.23 Insertion phases in the two states of the ideal reflective phase shifter 37              |

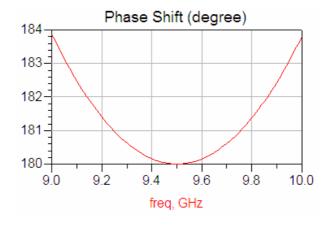

| Figure 3.24 Differential phase shift of the ideal reflection type $180^{\circ}$ phase shifter . $37$ |

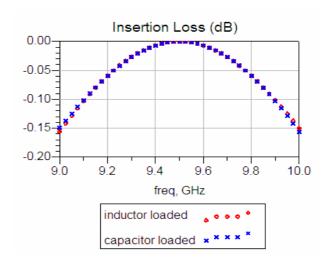

| Figure 3.25 Insertion losses in two states of the ideal reflection type 180° phase                   |

| shifter                                                                                              |

| Figure 3.26 Amplitude imbalance between the two states of the ideal reflection type                  |

| 180° phase shifter                                                                                   |

| Figure 3.27 Return losses of in two states of the ideal reflection type 180° phase                   |

| shifter                                                                                              |

| <b>Figure 3.28</b> PIN diode in SPST configuration                                                   |

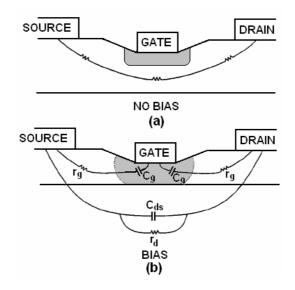

| Figure 3.29 Linear operating regions of a FET Switch[34]                                             |

| Figure 3.30 Cross section of FET switch with resistive and capacitive regions: (a)                   |

| ON state (b) OFF state [34]41                                                                        |

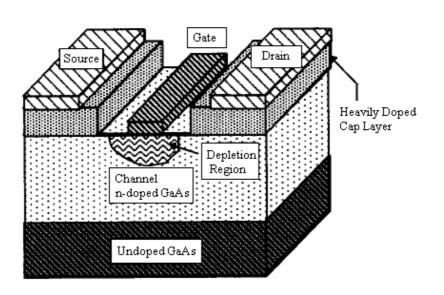

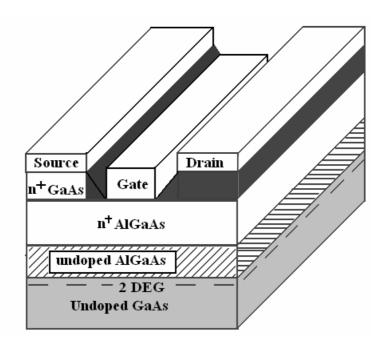

| Figure 3.31 Cross section of MESFET [34]                                                             |

| Figure 3.32 Cross section of AlGaAs/GaAs HEMT [34]                                                   |

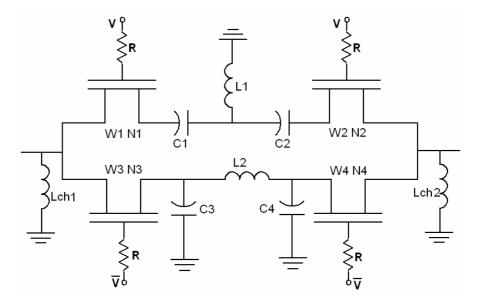

| Figure 4.1 Schematic of the SPDT switch designed with WIN foundry's 0.5 um                           |

| switch pHEMT process 51                                                                              |

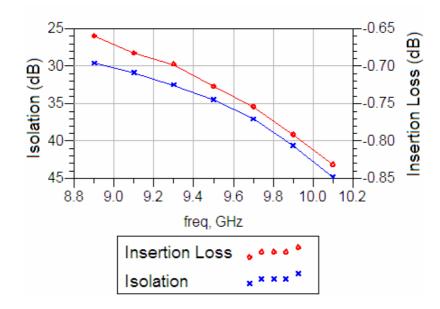

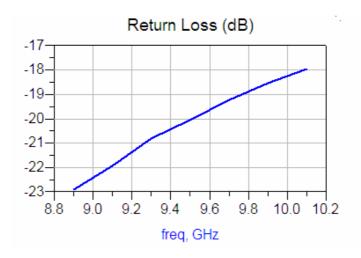

| Figure 4.2 Isolation and the insertion loss of the SPDT designed with WIN                            |

| components 52                                                                                        |

| Figure 4.3 Input return loss of the SPDT designed with WIN components                                |

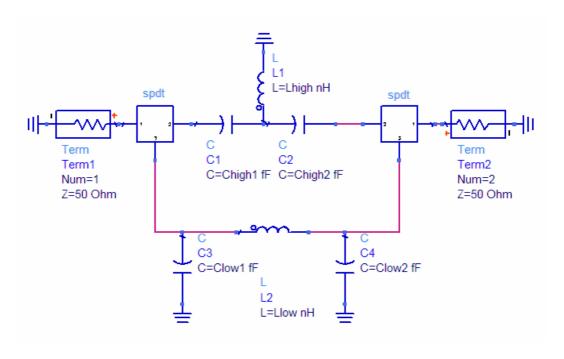

| Figure 4.4 SPDT switch designed with design kit of WIN Foundry's 0.5 um switch                       |

| pHEMT process                                                                                        |

| <b>Figure 4.5</b> The legend to be referred for the bit-performance graphs                           |

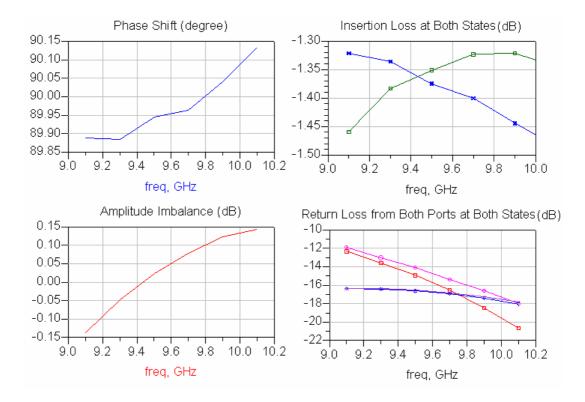

| Figure 4.6 Overall performance of the 90 degree bit designed with ideal filter                       |

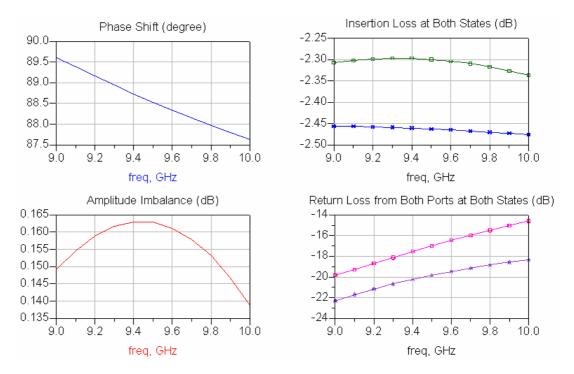

| elements but practical SPDT. 54                                                                      |

| Figure 4.7 Performance of the 90 degree bit upon replacement of ideal components                     |

| with more realistic ones: Capacitors with models and inductors with measurements.                    |

| 56                                                                                                   |

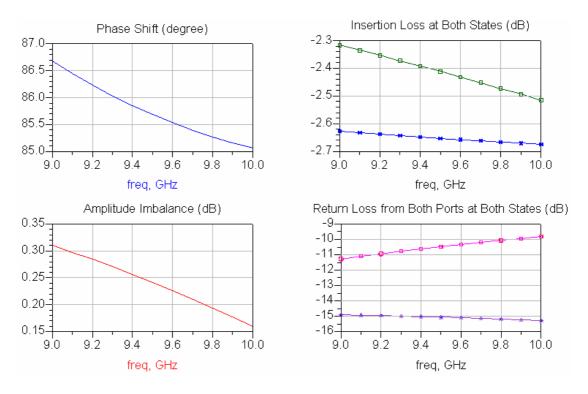

| Figure 4.8 Overall performance of the 180 degree bit designed with ideal filter                  |

|--------------------------------------------------------------------------------------------------|

| elements but practical SPDT                                                                      |

| Figure 4.9 Performance of the 180 degree bit upon replacement of ideal components                |

| with more realistic ones: Capacitors with models and inductors with measurements                 |

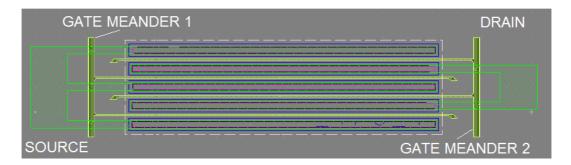

| Figure 4.10 Layout of a 4x125µm Single Gate Transistor in the 0.5 um InGaAs                      |

| Switch pHEMT process of WIN Foundry. 59                                                          |

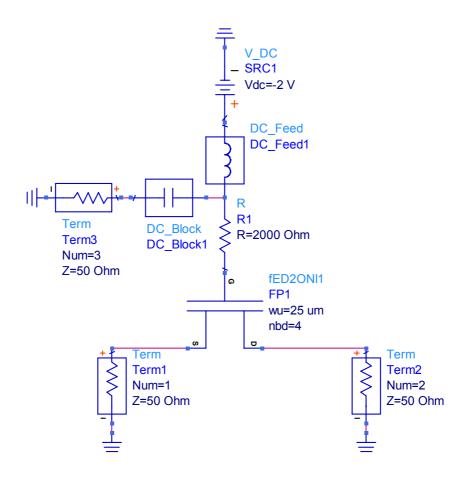

| <b>Figure 5.1</b> Setup for measuring isolation between gate and the drain terminals 62          |

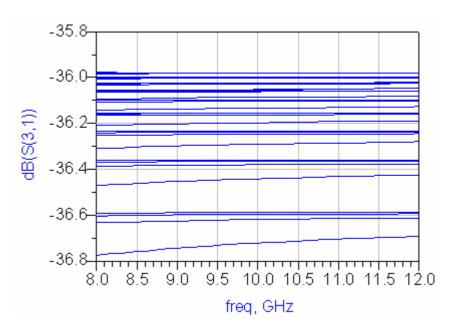

| Figure 5.2 Result of swept simulation with $Rg = 3000 \Omega$ (Isolation between gate and drain) |

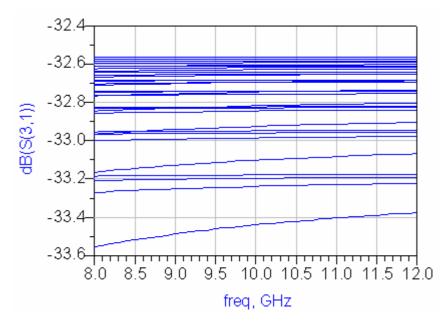

| Figure 5.3 Result of swept simulation with $Rg=2000\Omega$ (Isolation between gate and           |

| drain)                                                                                           |

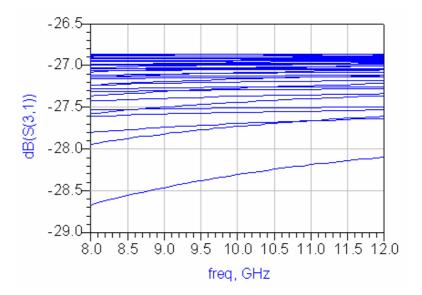

| Figure 5.4 Results of swept simulation with Rg=1000 $\Omega$ (Isolation between gate and         |

| drain)                                                                                           |

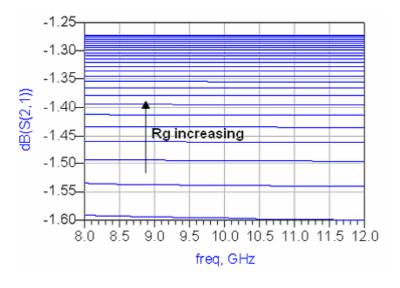

| Figure 5.5 Effect of Rg on the insertion loss of the transistor in the ON state 64               |

| Figure 5.6 Effect of Rg on the isolation of the transistor in the OFF state (Isolation           |

| between source and drain)                                                                        |

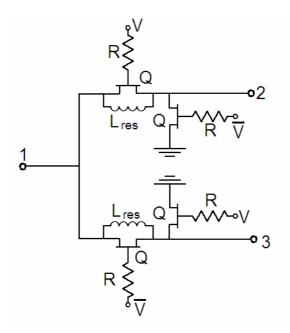

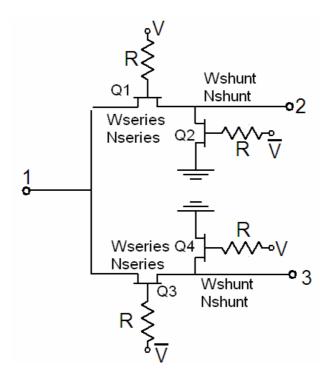

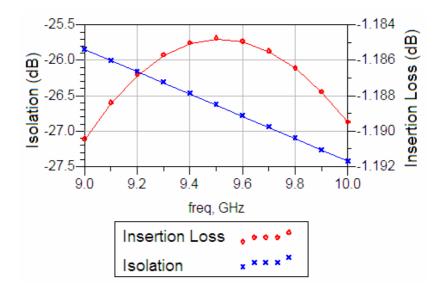

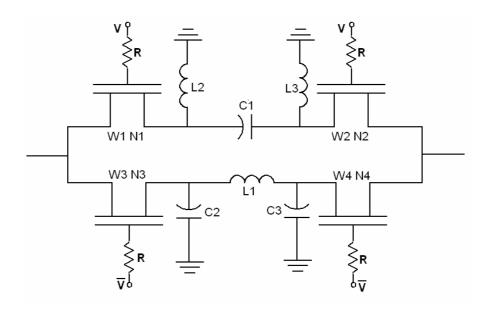

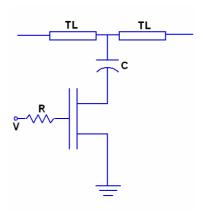

| Figure 5.7 Series – Shunt SPDT structure                                                         |

| <b>Figure 5.8</b> Series – Shunt SPDT with resonating inductor                                   |

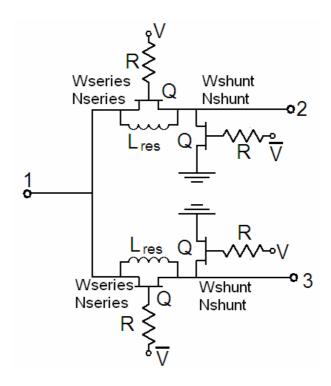

| Figure 5.9 Isolation and insertion loss of the SPDT designed with OMMIC                          |

| components                                                                                       |

| Figure 5.10 Input return loss of the SPDT designed with OMMIC components 69                      |

| <b>Figure 5.11</b> The legend to be referred for the bit-performance graphs                      |

| Figure 5.12 Performance of 90 degree bit where SPDT does have a resonating                       |

| inductor                                                                                         |

| Figure 5.13 Performance of 90 degree bit where SPDT does not have a resonating                   |

| inductor                                                                                         |

| <b>Figure 5.14</b> Topology used for the 90° bit                                                 |

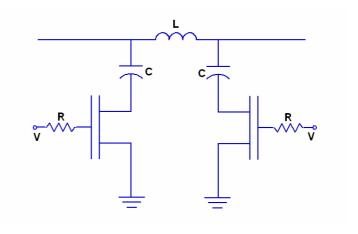

| <b>Figure 5.15</b> Topology used for the 180° bit                                                |

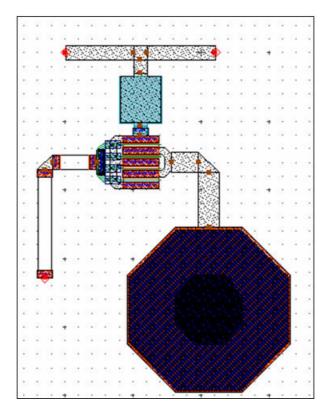

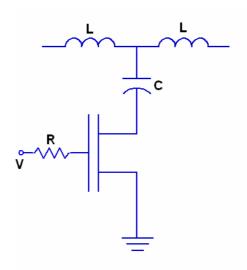

| <b>Figure 5.16</b> Structure for the 2.8125 degree bit                                           |

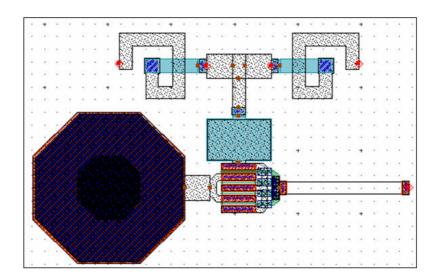

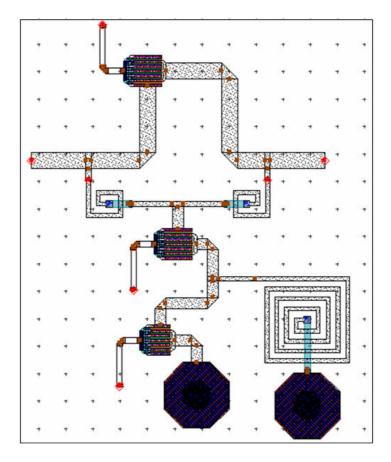

| <b>Figure 5.17</b> Layout of the 2.8125° bit                                                     |

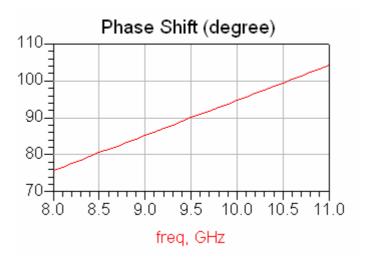

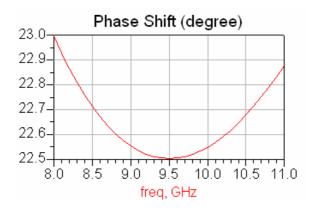

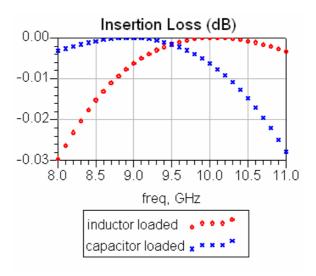

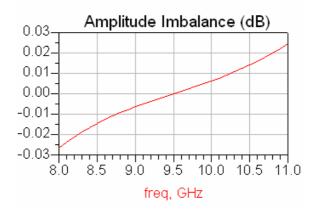

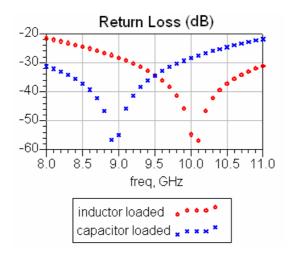

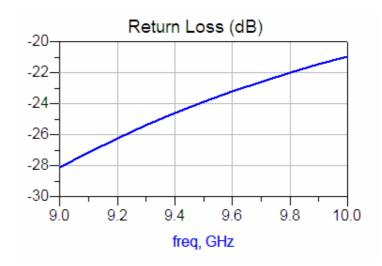

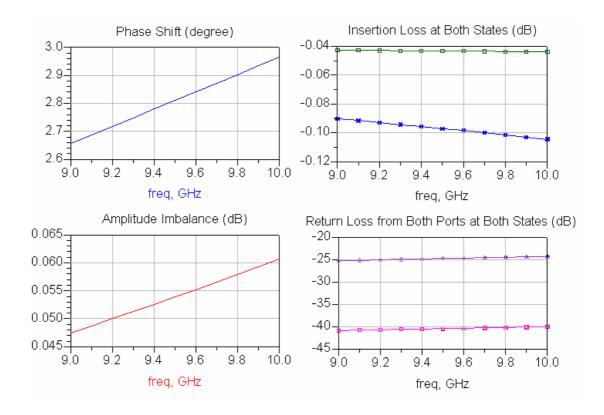

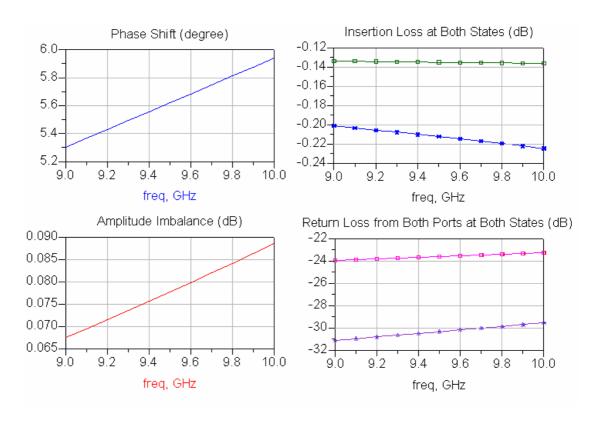

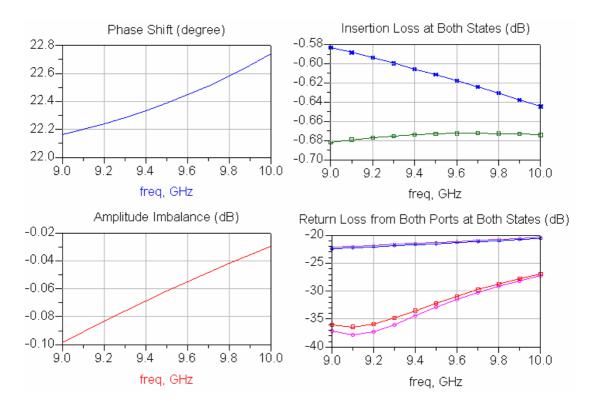

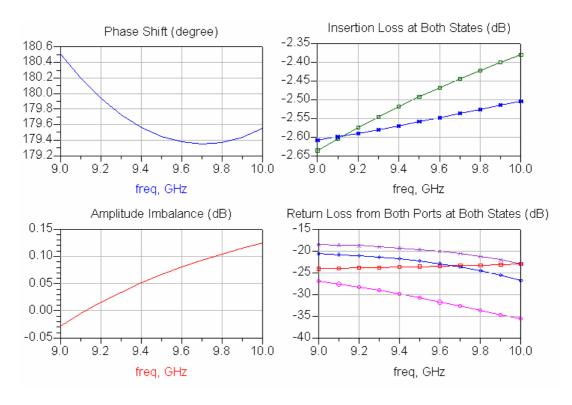

| Figure 5.18 Final performance of the 2.8125° bit                                                 |

| Figure 5.19 Structure for the 5.625 degree bit                                    | 78        |

|-----------------------------------------------------------------------------------|-----------|

| Figure 5.20 Layout of the 5.625° bit                                              | 78        |

| Figure 5.21 Final performance of the 5.625° bit                                   | 79        |

| Figure 5.22 Structure for the 11.25° bit                                          | 80        |

| Figure 5.23 Layout of the 11.25° bit                                              | 80        |

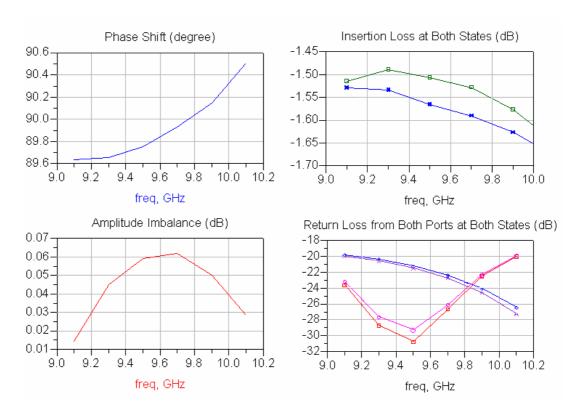

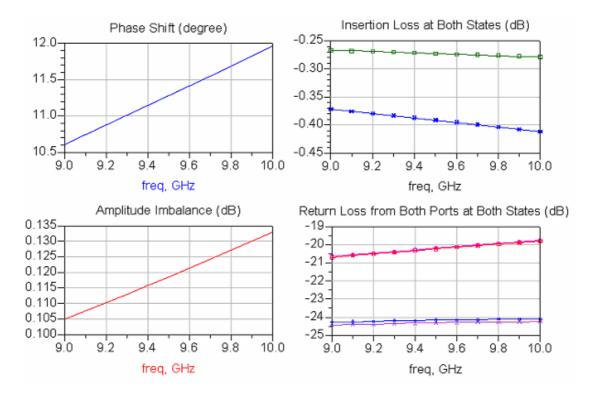

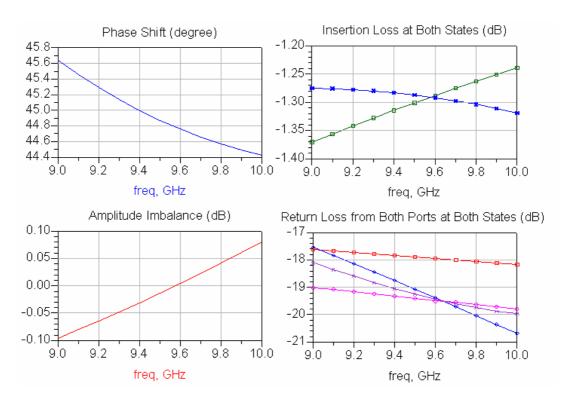

| <b>Figure 5.24</b> Final performance of the 11.25° bit                            | 81        |

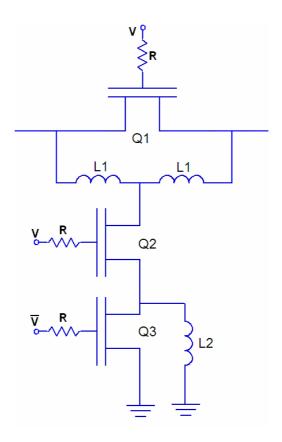

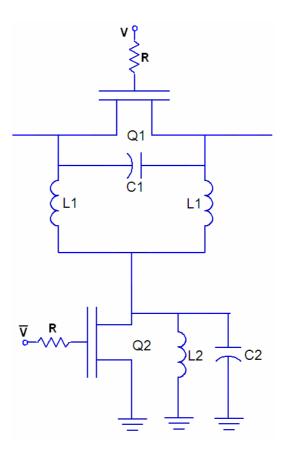

| <b>Figure 5.25</b> Structure utilized for the realization of 22.5° bit [15], [17] | 82        |

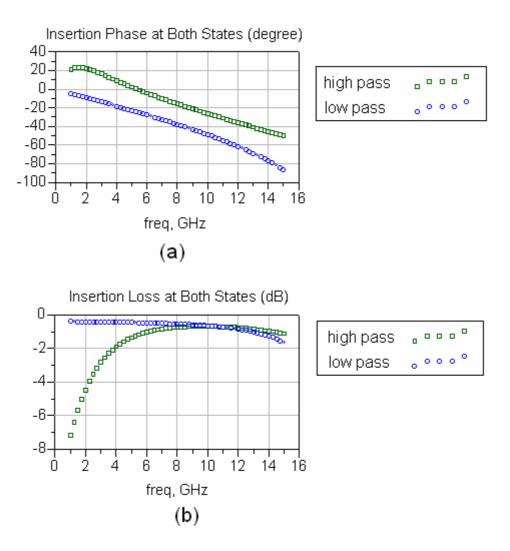

| Figure 5.26 (a) Insertion phases and (b) insertion losses corresponding to l      | nigh pass |

| and low pass states of the 22.5° bit in 1-15 GHz band                             | 83        |

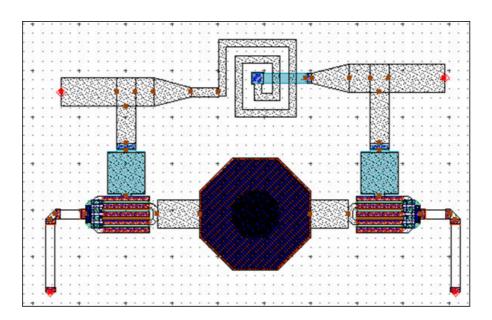

| <b>Figure 5.27</b> Layout of the 22.5° bit                                        | 84        |

| <b>Figure 5.28</b> Final performance of the 22.5° bit                             | 85        |

| <b>Figure 5.29</b> Structure utilized for the realization of 45° bit [reference]  | 86        |

| Figure 5.30 Layout of the 45° bit                                                 | 87        |

| Figure 5.31 Performance of the 45° bit                                            | 88        |

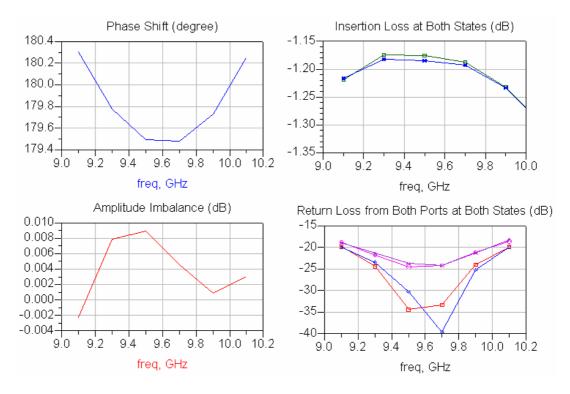

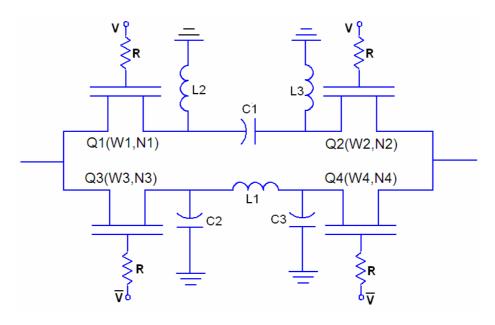

| <b>Figure 5.32</b> HP/LP topology used for realization of the 90° bit             | 89        |

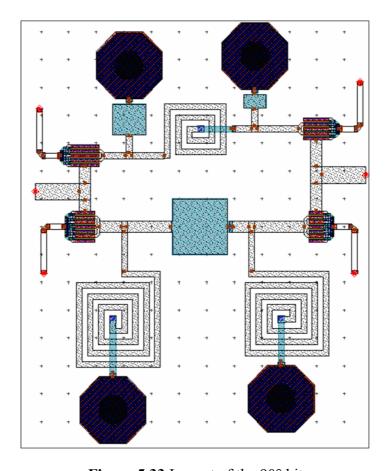

| <b>Figure 5.33</b> Layout of the 90° bit                                          | 89        |

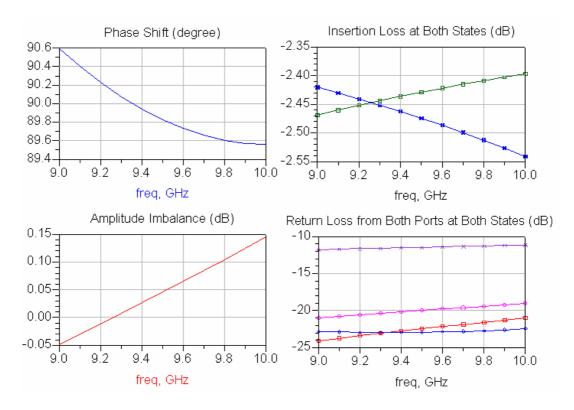

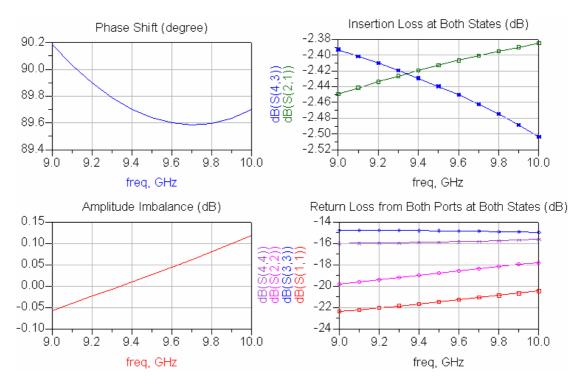

| <b>Figure 5.34</b> Performance of the 90° bit                                     | 90        |

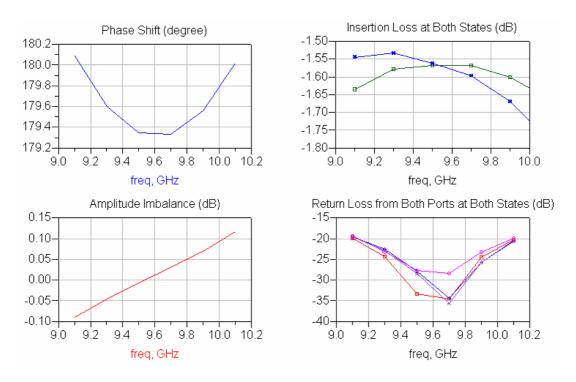

| <b>Figure 5.35</b> HP/LP topology used for realization of the 180° bit            | 91        |

| Figure 5.36 Layout of the 180° bit                                                | 92        |

| Figure 5.37 Performance of the 180° bit                                           | 93        |

| Figure 6.1 The sequence of the bits                                               | 95        |

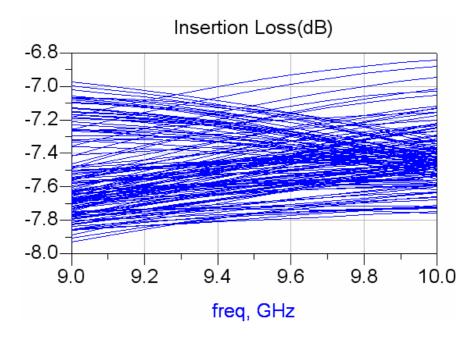

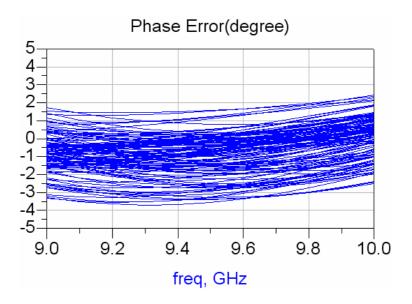

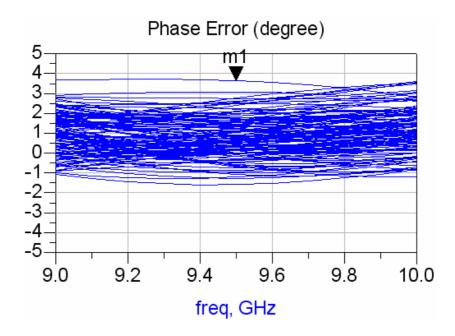

| <b>Figure 6.2</b> The phase error of the phase shifter at all 128 states          | 95        |

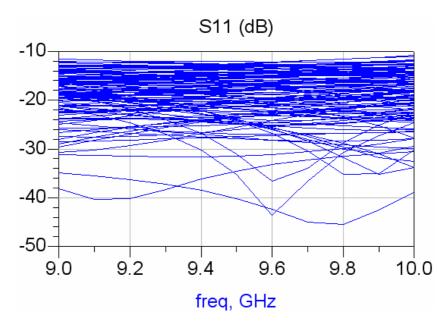

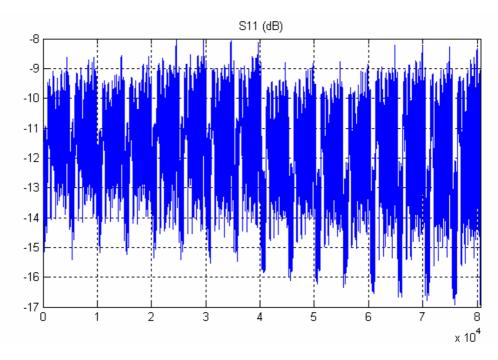

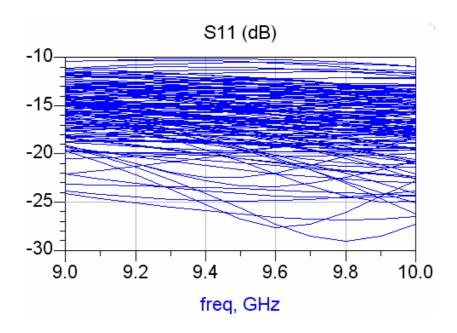

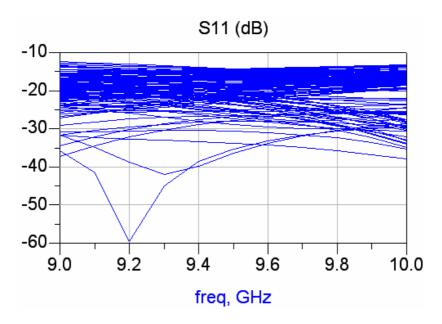

| Figure 6.3 The return loss from the first port of the phase shifter at all 128 st | tates 96  |

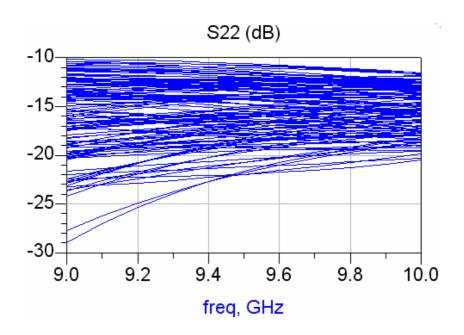

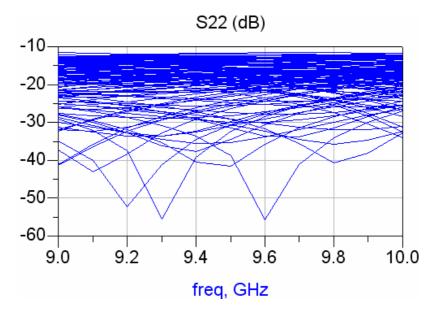

| Figure 6.4 The return loss from the second port of the phase shifter at all 1     | 28 states |

|                                                                                   | 96        |

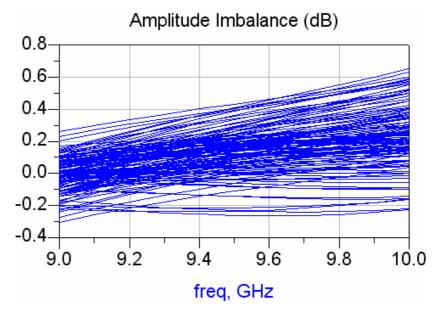

| Figure 6.5 The amplitude variation of the phase shifter referenced to the         | e lowest  |

| phase state                                                                       | 97        |

| <b>Figure 6.6</b> The insertion loss of the phase shifter at all 128 states       | 97        |

| <b>Figure 6.7</b> Performance of the modified 90° bit                             | 98        |

| <b>Figure 6.8</b> The phase shifter schematic with modified 90° bit               | 98        |

| <b>Figure 6.9</b> The phase error of the phase shifter with the modified 90° bit  | 99        |

| Figure 6.10 The return loss from the first port of the phase shifter with the modified                        |

|---------------------------------------------------------------------------------------------------------------|

| 90° bit                                                                                                       |

| Figure 6.11 The return loss from the second port of the phase shifter with the                                |

| modified 90° bit                                                                                              |

| <b>Figure 6.12</b> The amplitude variation of the phase shifter with the modified 90° bit                     |

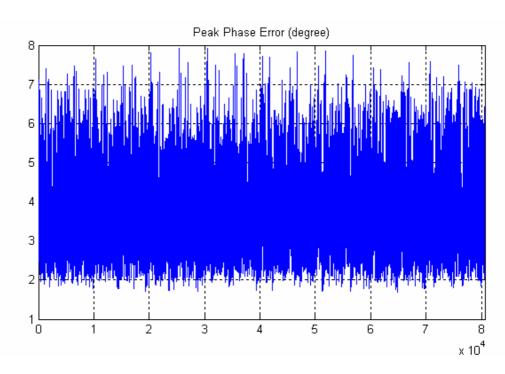

| Figure 6.13 The variation of peak phase error of the phase shifter for all 80640                              |

| different bit arrangements                                                                                    |

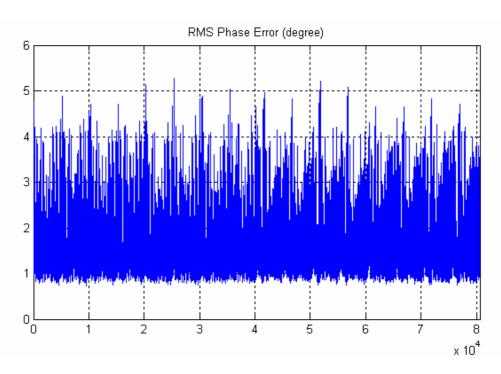

| Figure 6.14 The variation of rms phase error of the phase shifter for all 80640                               |

| different bit arrangements                                                                                    |

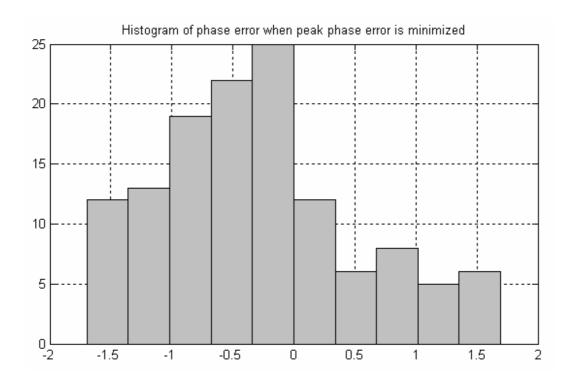

| Figure 6.15 Histogram of phase error when the bits are arranged to minimize peak error                        |

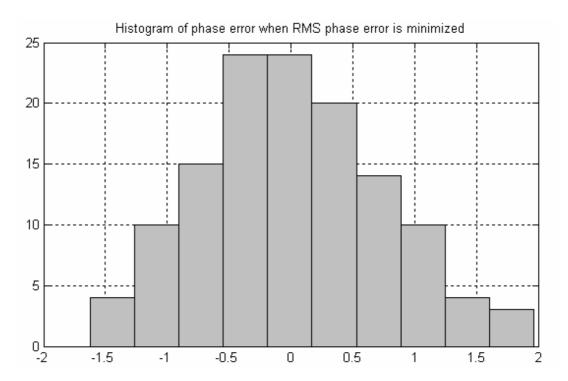

| <b>Figure 6.16</b> Histogram of phase error when the bits are arranged to minimize rms error                  |

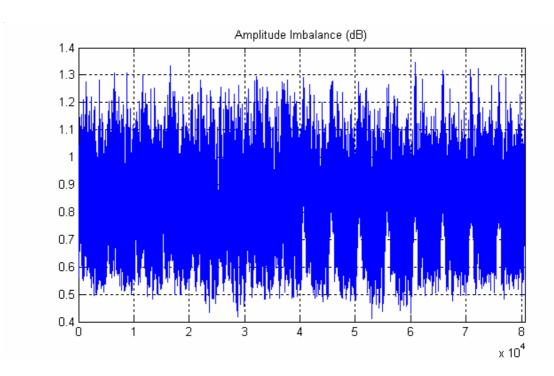

| Figure 6.17 The variation of maximum amplitude imbalance of the phase shifter for                             |

| all 80640 different bit arrangements                                                                          |

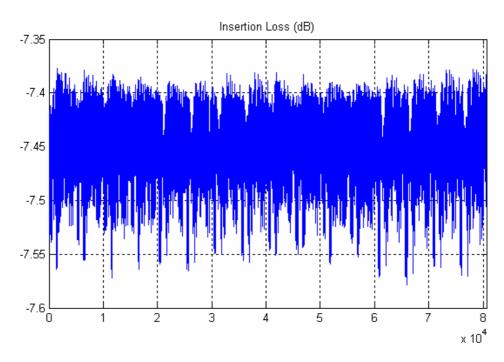

| Figure 6.18 The variation of average loss of the phase shifter for all 80640 different                        |

| bit arrangements. 107                                                                                         |

| <b>Figure 6.19</b> The variation of maximum S11 of the phase shifter for all 80640 different bit arrangements |

| <b>Figure 6.20</b> The variation of maximum S22 of the phase shifter for all 80640                            |

| different bit arrangements                                                                                    |

| <b>Figure 6.21</b> Summary of sub-optimum bit arrangements for the 7 bit phase shifter (f                     |

| stands for flipping w.r.t the layout conventions in Chapter 5)                                                |

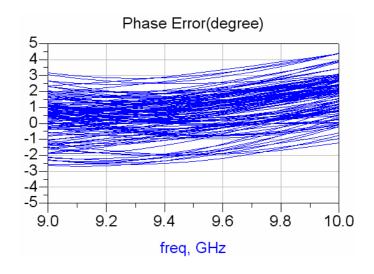

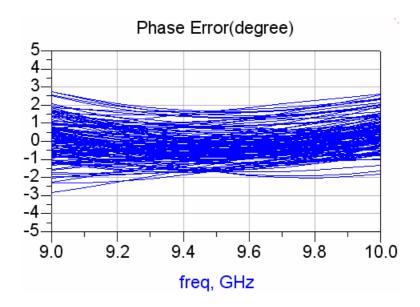

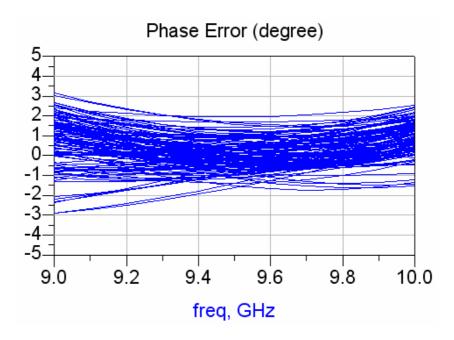

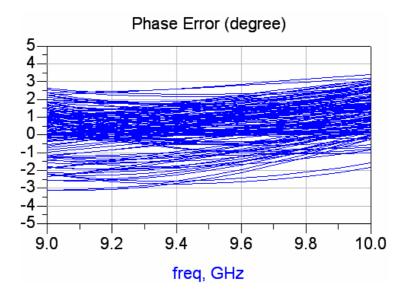

| Figure 6.22 Phase error of the phase shifter when the bits are arranged so as to                              |

| minimize the peak phase error                                                                                 |

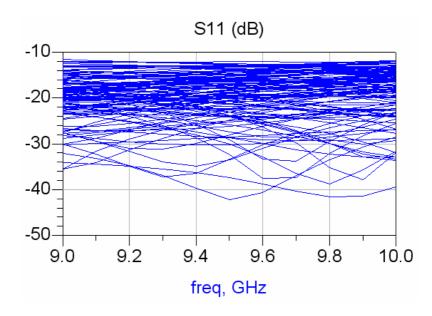

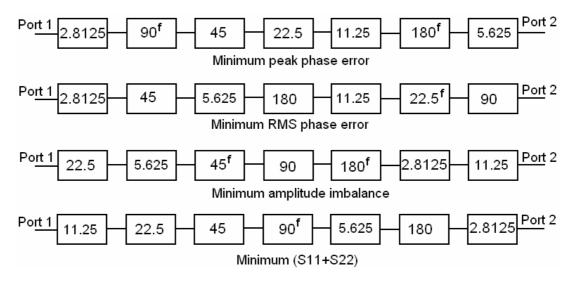

| Figure 6.23 $S_{11}$ of the phase shifter when the bits are arranged so as to minimize the                    |

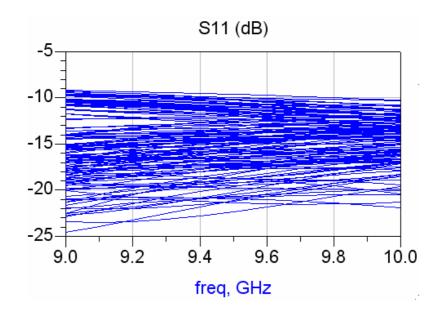

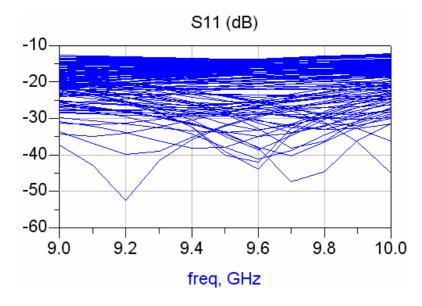

| peak phase error                                                                                              |

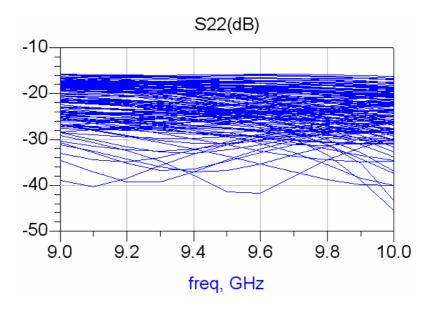

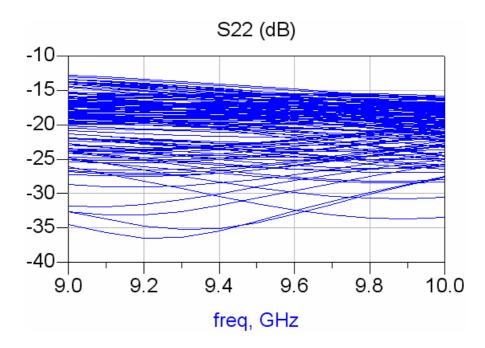

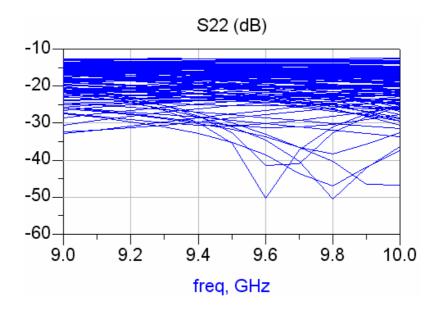

| Figure 6.24 S <sub>22</sub> of the phase shifter when the bits are arranged so as to minimize the             |

| peak phase error                                                                                              |

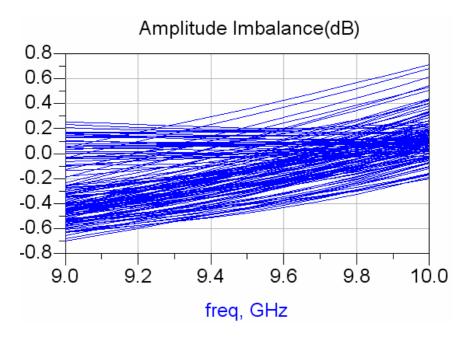

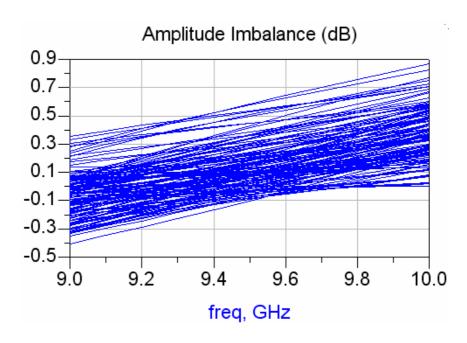

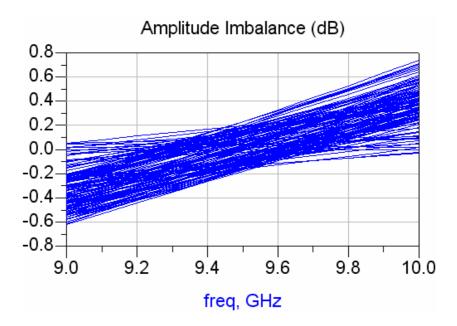

| Figure 6.25 Amplitude imbalance of the phase shifter when the bits are arranged so                            |

| as to minimize the peak phase error                                                                           |

| Figure 6.26 Phase error of the phase shifter when the bits are arranged so as to              |

|-----------------------------------------------------------------------------------------------|

| minimize the rms phase error                                                                  |

| Figure 6.27 $S_{11}$ of the phase shifter when the bits are arranged so as to minimize the    |

| rms phase error                                                                               |

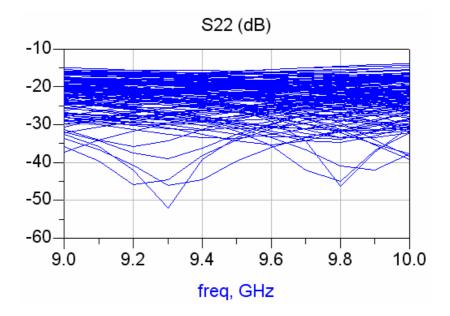

| Figure 6.28 $S_{22}$ of the phase shifter when the bits are arranged so as to minimize the    |

| rms phase error 114                                                                           |

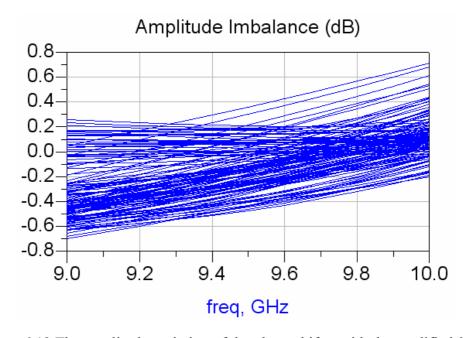

| Figure 6.29 Amplitude imbalance of the phase shifter when the bits are arranged so            |

| as to minimize the rms phase error. 114                                                       |

| Figure 6.30 Phase error of the phase shifter when the bits are arranged so as to              |

| minimize the amplitude imbalance                                                              |

| Figure 6.31 $S_{11}$ of the phase shifter when the bits are arranged so as to minimize the    |

| amplitude imbalance                                                                           |

| Figure 6.32 $S_{22}$ of the phase shifter when the bits are arranged so as to minimize the    |

| amplitude imbalance                                                                           |

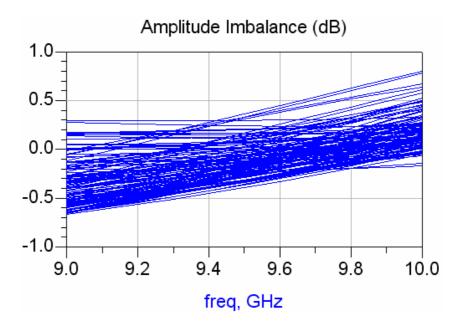

| Figure 6.33 Amplitude imbalance of the phase shifter when the bits are arranged so            |

| as to minimize the amplitude imbalance                                                        |

| Figure 6.34 Phase error of the phase shifter when the bits are arranged so as to              |

| $minimize \ the \ sum \ of \ S_{11} \ and \ S_{22} \ $                                        |

| Figure 6.35 $S_{11}$ of the phase shifter when the bits are arranged so as to minimize the    |

| $sum of S_{11} and S_{22} 		 118$                                                             |

| Figure 6.36 $S_{22}$ of the phase shifter when the bits are arranged so as to minimize the    |

| $sum of S_{11} and S_{22} 		 119$                                                             |

| Figure 6.37 Amplitude imbalance of the phase shifter when the bits are arranged so            |

| as to minimize the sum of $S_{11}$ and $S_{22}$                                               |

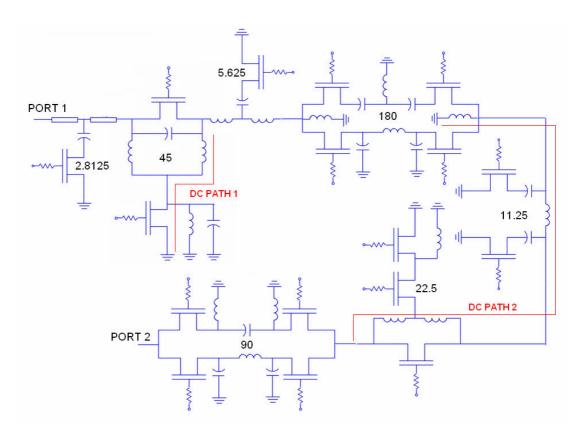

| <b>Figure 6.38</b> Schematic of the 7 bit phase shifter demonstrating critical DC paths . 121 |

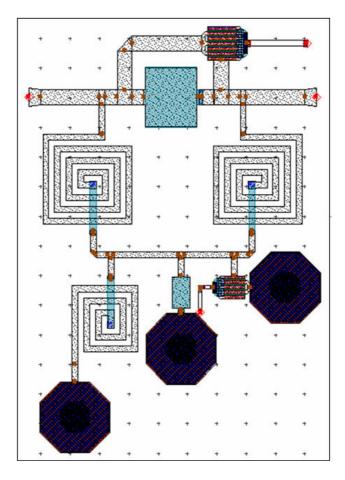

| <b>Figure 6.39</b> Final layout of the phase shifter with minimum rms phase error 122         |

# LIST OF TABLES

| Table 2.1 Nominal insertion phase of a three bit phase shifter at its 8 prog     | gressive |

|----------------------------------------------------------------------------------|----------|

| states                                                                           | 13       |

| Table 3.1 Element values for the PI type low pass and TEE type high pass filt    | ers 29   |

| Table 3.2 Element values required for 180 degree reflective phase shifter        | 37       |

| Table 3.3 List of worldwide MMIC foundries by 2005                               | 44       |

| Table 4.1 Ideal component values in the 90 degree phase bit                      | 53       |

| Table 4.2 Component values of the 90 degree phase shifter bit upon replace       | ment of  |

| ideal elements with S parameters or models and re-optimization                   | 55       |

| Table 4.3 Ideal component values in the 180 degree phase bit                     | 57       |

| Table 4.4 Component values of the 180 degree phase shifter bit upon repla        | acement  |

| and re-optimization                                                              | 58       |

| Table 5.1 The list of gate bias values for each transistor in Figure 5.7 to sele | ct ports |

| 2 or 3                                                                           | 66       |

| Table 5.2 Components used in the SPDT with resonating inductor.                  | 68       |

| Table 5.3 List of components in the final 2.8125° bit                            | 77       |

| Table 5.4 List of components in the final 5.625° bit                             | 79       |

| Table 5.5 List of components in the final 5.625° bit                             | 81       |

| <b>Table 5.6</b> List of components in the final 22.5° bit                       | 84       |

| <b>Table 5.7</b> List of components in the final 44.5° bit                       | 87       |

| <b>Table 5.8</b> List of components in the 90° bit                               | 90       |

| <b>Table 5.9</b> List of components in the 180° bit                              | 92       |

| Table 6.1 The summary of critical performance parameters for every bit           | 95       |

| Table 6.2 Summary of performance when the bit arrangement is such that t         | he peak  |

| phase error is minimum at 9.5 GHz                                                | 112      |

| Table 6.3 Summary of performance when the bit arrangement is such that           | the rms  |

| phase error is minimum at 9.5 GHz                                                | 115      |

| Table 6.4 Summary of performance when the bit arrangement is such that           | that the |

| amplitude imbalance minimum at 9.5 GHz                                           | 117      |

| Table 6.5 Summary of performance when the bit arrangement is such that the | sum of |

|----------------------------------------------------------------------------|--------|

| S <sub>11</sub> and S <sub>22</sub> is minimum at 9.5 GHz                  | 120    |

## LIST OF ABBREVIATIONS

ADS ® :Advanced Design System

AM-PM : Amplitude Modulation - Phase Modulation

BST :Barium Strontium Titanate

CMOS : Complementary MOS

CPW :Coplanar Waveguide

D/A :Digital to Analog

DC :Direct Current

ECM :Electronic Counter Measures

FET :Field Effect Transistor

GaAs :Gallium Arsenide

GSM :Global System for Mobile Communications

HBT :Hetero-junction Bipolar Transistor

HP/LP :High Pass / Low Pass

IC :Integrated Circuit

IL :Insertion Loss

LHTL :Left Handed Transmission Line

LSB :Least Significant Bit

LVDS :Low Voltage Differential Signaling

MESFET : Metal- Semiconductor Field Effect Transistor

MIM :Metal - Insulator - Metal

MMIC : Monolithic Microwave Integrated Circuit

MOSFET : Metal - Oxide - Semiconductor Field Effect Transistor

PCB :Printed Circuit Board

pHEMT :Pseudomorphic High Electron Mobility Transistor

PIN :Positive - Intrinsic - Negative

RF MEMS : Radio Frequency Micro Electro Mechanical System

RHTL :Right Handed Transmission Line

SPST :Single Pole Single Throw

SPDT :Single Pole Double Throw

TTL :Transistor - Transistor Logic

TWTA :Traveling Wave Tube Amplifier

#### **CHAPTER 1**

#### INTRODUCTION

Phase shifters are devices that change the phase of the signals at their output by some means of outside intervention. Most extensive usage area of phase shifters is phased array antennas, where they are most often used together with attenuators so as to obtain the desired complex excitation distribution along the antenna elements. Phased arrays with low sidelobes and low steering errors require digital phase shifters with large number of bits. The number of antenna elements and multi-beam requirements of modern phased array antennas call for small and lightweight phase shifters relying on the MMIC technology. In this study, a seven bit mid X- band MMIC phase shifter to be manufactured by OMMIC foundry of France is designed. Along with the design of this phase shifter, some extra work made with the design kit of another foundry, WIN, is presented.

Digital MMIC phase shifters have been studied extensively in the literature. The studies focus on design while trying to keep the performance of the phase shifter above some specified merit. The domain of studies is generally composed of different topologies and processes. Towards the recent years, the current trend of researchers is to get some MMIC foundry implement the design rather than merely work on theoretical models. Most often, element models or measurements that are obtained from foundries are used in the designs. However, in the early years of MMIC history, the studies used to remain on the theoretical phase. As a matter of fact, while the technology was shifting to MMIC, there was a continuity of circuit topologies that were designed for hybrid circuits.

The first examples of IC phase shifters utilize PIN diodes as switching elements. Work on semiconductor phase shifters using PIN diodes as control elements began in the late 1950's [1]. In the often referred paper [2], along with switched line, loaded line, and reflection types, broadband high pass/low pass filter topologies are

described and evaluated for their performance. Although not specifically meant for MMIC, these topologies have been examined and used very often in MMIC designs. The switching elements are assumed to be diodes and simple analyses on their switching performance was carried out. Equations yielding element values of loaded line and switched three pole HP/LP topologies were derived. It is reported that over almost octave bandwidth  $\pm 2^{\circ}$  error is achieved with these topologies. The bandwidth performance of large bits is postulated to enhance by increasing the order of filter sections.

Another design in [3] with pin diode switching elements used again HP/LP networks as an alternative to distributed type phase shifters (loaded line, hybrid coupled, switched line). Three pin diodes in TEE configuration are utilized and their on and off state models are included in the design. Low loss was achieved together with 20 % bandwidth within which VSWR remains below 1.5 and phase variation remains within 10 % of nominal.

A monolithic integration example with PIN diodes exists in [4]. In this study, the low loss of the circuit is due to the novel topology proposed. Instead of cascading five bits using SPDTs, SP4Ts are used to divert the signal along 4 different phase paths. By this method the signal is subject to less switching elements and thus the insertion loss as low as 3 dB is accomplished.

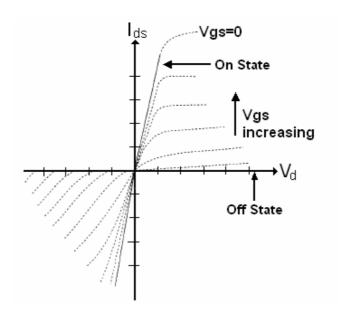

While PIN diodes are possible alternatives as control elements in phase shifters, FET phase shifters were studied widely. [5] - [16] are only a few of the FET phase shifter examples. These studies exhibit a variety of bit numbers, topologies, and performances, but common property of all of them is the utilization of FET switches, be they active or passive; GaAs or SiGe; MESFET, pHEMT, or mHEMT transistors.

One of the hottest points in phase shifter studies is the selection or invention of different circuit topologies. Among these topologies, the reflective hybrid coupler, switched line, loaded line and high pass/low pass filter topologies are designed for digital phase shifters. These topologies all depend on switching between networks of different insertion phases. Due to its lumped implementation, high-pass/low-pass

topology is regarded as a good remedy below X band. For the sake of increasing bandwidth performance, the switching elements are sometimes considered as part of filters in [8], [10], [15], [17], [18], [19] and [21] . [15] is also attention taking for its demonstrating usage of silicon MOSFETs as switching elements rather than classical III-V compound semiconductor FETs.

Apart from above topologies which are all transmission type, varactor loaded hybrid couplers are often utilized as reflection type phase shifters (RTPS). At sufficiently high frequencies where the quarter wavelength lines become feasibly short, usually Lange couplers come into help for wideband requirements. As a matter of fact, distributed type phase shifters are most of the time not preferred at relatively low frequencies (below 10 GHz) due to size and cost considerations. Generally variable reflective loads are required for lossless phase shifting and 3 dB couplers are employed for routing the reflected signal. In [20] the topologies of the 90°, 45°, and 22.5° and 11.25° degree sections utilized interdigitated quadrature couplers terminated with FET switched reflective loads. The problem of too much chip area for hybrid couplers is tried to be circumvented by replacing the coupler with a lumped element equivalent of 3 dB 90 degree coupler in [22] where MESFET varactors are used as variable loads. 0.5 mm² chip area is reported together with 210 degree continuous phase control and 4.9 dB ±0.9 dB insertion loss.

In [23], the lossless phase shifting advantage and intrinsic match property of passive all pass networks are exploited to have octave bandwidth. It is claimed that the bandwidth could be easily increased using more all pass networks in cascade. Measurements of MIC implementation are reported for the 4 bit prototype: 5 dB insertion loss, with less than  $\pm 6^{\circ}$  error for each bit is obtained. Also in [24] and [25] active phase shifters with all pass networks switched by HEMTs and HBTs are proposed and designed.

Some of the recent studies on MMIC phase shifters concentrate on the utilization of metamaterials. Metamaterials are the materials having negative permittivity ( $\epsilon$ ) and/or negative permeability ( $\mu$ ) [26]. The negativeness of these parameters result in the so called "Left Handed Transmission Line" in whose lumped model inductors are

shunt and the capacitors are in series as opposed to the normal "Right Handed Transmission Line". For LHTL, the phase velocity and the group velocity are not codirectional, which is the usual case for a conventional (right-handed) transmission line. This results in negative electrical length. Switching between a LHTL and RHTL of are same amount but opposite sign electrical lengths, ±3 % error in one octave is reported [27].

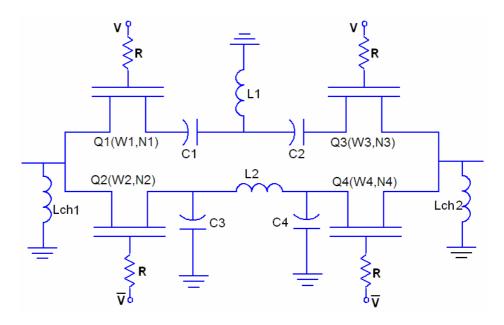

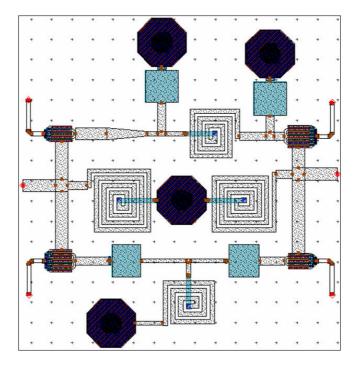

In this thesis, the switching elements are the (pseudomorphic high electron mobility transistor) pHEMTs. The famous high pass – low pass switched filter structures are chosen for the 180 and 90 degree bits of the 7 bit phase shifter. For 45 and 22.5 degree bits, the embedded filter approach devised in [10], [14], [15], and [19] are examined and used. As for the smallest three bits, namely 11.25, 5.625 and 2.8125 degrees the amount of phase shift and the required bandwidth of operation allows usage of low pass/low pass filter switching, where the transistors are again embedded in the design of filters as filter elements. The details of the design will be given in Chapter 5.

In Chapter 2, the concept and general operation principles of phase shifters are introduced. Available technology types for production of phase shifters and applications of phase shifters are also given. Digital phase shifter requirements are also defined and clarified for they matter in the design practice.

Chapter 3 focuses on the preliminaries of designing a MMIC phase shifter. Common phase shifter topologies are presented with theoretical examples in the first part, critical component for a phase shifter, FET switch, is introduced in the second part and MMIC foundry issues are mentioned in the third part of this chapter.

Next, in Chapter 4, some practical work done with the design kit of WIN foundry is exhibited. These include the design of necessary SPDT for switched filter topologies and the 180 and 90 degree bits realized with this SPDT.

The backbone of the study within the context of this thesis is given in Chapter 5 & 6. In Chapter 5 the detailed design of the bits of the 7 bit X band phase shifter with the

OMMIC foundry design kit takes place. Individual design, optimization and performance of each bit and finally the entire phase shifter are given in this chapter. The evaluation of different bit arrangement alternatives for the finalized chip takes place in Chapter 6.

Eventually in Chapter 7, comments on the designed phase shifter are presented and possibilities of enhancing its performance are investigated.

#### **CHAPTER 2**

#### A CLOSE LOOK AT PHASE SHIFTERS

#### 2.1. General Considerations

#### 2.1.1. Definition of Phase Shifter

A phase shifter is a two port device that changes the insertion phase between its ports by some means of intervention. As a matter of fact, any network with modifiable phase characteristic could be regarded as a phase shifter, although it may not be a good one.

An ideal phase shifter only modifies the phase of the injected signal, without disturbing the amplitude. A phase shifter has different scattering matrices corresponding to its different states. The phase shift appears in the insertion phase of the signal, and therefore in the phase of  $S_{21}$  of the phase shifter. This phase shift is called the **differential phase shift**, because it is the difference of the phases of insertion phases of the two states. The terms phase shift and differential phase shift will be used interchangeably throughout this thesis.

The scattering matrices of an ideal phase shifter with a nominal phase shift setting of  $\alpha_2 - \alpha_1$ , before and after commanding the phase shift are the following:

State 1:

$$\begin{bmatrix} b_1 \\ b_2 \end{bmatrix} = \begin{bmatrix} 0 & e^{j\beta_1(\omega)} \\ e^{j\alpha_1(\omega)} & 0 \end{bmatrix} \begin{bmatrix} a_1 \\ a_2 \end{bmatrix}$$

(2-1)

State 2 (Upon commanding the phase shift):

$$\begin{bmatrix} b_1 \\ b_2 \end{bmatrix} = \begin{bmatrix} 0 & e^{j\beta_2(\omega)} \\ e^{j\alpha_2(\omega)} & 0 \end{bmatrix} \begin{bmatrix} a_1 \\ a_2 \end{bmatrix}$$

(2-2)

From the matrices, it is apparent that the phase shift observed in the signal is equal to  $\alpha_2 - \alpha_1$ . The phase shift in the other direction is equal to  $\beta_2 - \beta_1$ , which may or may not be equal to  $\alpha_2 - \alpha_1$ . If they are equal, the phase shifter is said to be reciprocal; and if they are not, the phase shifter is said to be non-reciprocal.

The phase shift,  $\alpha_2 - \alpha_1$ , is not a function of frequency for an ideal phase shifter; that is, it is constant over the entire bandwidth of the phase shifter. It must be noted that, this does not necessitate  $\alpha_1$  and  $\alpha_2$  to be constant individually over that bandwidth.

As seen, the ideal phase shifter does not change the amplitude by definition. Also it is perfectly matched at its two ports.

On the other hand, the S matrices of a non-ideal phase shifter adjusted to shift the phase by  $\alpha_2 - \alpha_1$  are given below:

State 1:

$$\begin{bmatrix} b_1 \\ b_2 \end{bmatrix} = \begin{bmatrix} S_{11}^{-1}(\omega) & |S_{12}^{-1}(\omega)|e^{j\beta_1(\omega)} \\ |S_{21}^{-1}(\omega)|e^{j\alpha_1(\omega)} & S_{22}^{-1}(\omega) \end{bmatrix} \begin{bmatrix} a_1 \\ a_2 \end{bmatrix}$$

(2-3)

State 2:

$$\begin{bmatrix} b_1 \\ b_2 \end{bmatrix} = \begin{bmatrix} S_{11}^2(\omega) & |S_{12}^2(\omega)|e^{j\beta_2(\omega)} \\ |S_{21}^2(\omega)|e^{j\alpha_2(\omega)} & |S_{22}^2(\omega)| \end{bmatrix} \begin{bmatrix} a_1 \\ a_2 \end{bmatrix}$$

(2-4)

Referring to parameters in (2-3) and (2-4), following could be said:

- $\circ$   $|S_{21}^{1}(\omega)|$ ,  $|S_{21}^{2}(\omega)|$ ,  $|S_{12}^{1}(\omega)|$ , and  $|S_{12}^{2}(\omega)|$ . are not necessarily equal and are not equal to one.

- $\circ \quad {S_{11}}^1(\omega), \, {S_{22}}^1(\omega), \, {S_{11}}^2(\omega), \, \text{and} \, \, {S_{22}}^2(\omega) \, \, \text{are not equal to} \, \, 0.$

- o  $\alpha_2(\omega) \alpha_1(\omega)$  might not be exactly equal to the desired phase shift  $\alpha_2 \alpha_1$  at any frequency.

- $\circ$   $\alpha_2(\omega) \alpha_1(\omega)$  and  $\beta_2(\omega) \beta_1(\omega)$  are not constant with frequency.

These facts imply the following about a practical phase shifter:

- o Amplitude imbalance exists between two states of a phase shifter.

- o A finite return loss is suffered by the phase shifter.

- The commanded phase shift and the resultant phase shift may not be exactly equal.

- o Phase shift is not perfectly frequency independent.

#### 2.1.2. Phase Shifter and Time Shifter

A time shifter is a type of phase shifter with linear phase shift characteristic w.r.t frequency. The amount of differential phase shift of the time shifter is proportional to the frequency. This fact results in constant differential group delay; that is, no matter what the frequency of the signal is, the difference of delays between the two states of the time shifter is constant. For this reason, a time shifter is usually called as a true time delay network. A time shifter is not a good phase shifter, considering the definition of ideal phase shifter; but its constant time delay property is the heart of wideband squintless beam steering of a phased array antenna. The reason of this requirement will be explained later in this thesis.

# 2.1.3. Phase Shifter Applications

Phase shifters are the critical elements of electronically scanned array antennas. These antennas are also called phased array antennas, which imply the role of phase shifter in the system. Used together with attenuators, they suffice to determine the distribution of the excitation of the antenna elements and thus the instantaneous pattern of the antenna. They could be used as a part of both the transmit and receive

antennas. Apart from the phased arrays, they are used in both analog and digital phase modulation. As an electronic warfare application, serrodyning or frequency translation is accomplished by continuously varying the phase of the phase shifter and obtaining the desired Doppler profile to deceive the engaged system [30]. Another application area is the power amplifiers, where phase shifting feedback networks are used to compensate for AM-PM distortion and other nonlinearities [29]. Phase shifters are also used in various microwave measurements.

#### 2.1.4. Phase Shifter Classification

Phase shifters can be classified according to their various properties. Most basic classification would be on the basis of adjustability: A phase shifter is either a fixed phase shifter or an adjustable one. It is obvious that an adjustable phase shifter can always be used instead of a fixed one, but cost and design complexity would certainly favor a fixed phase shifter. Fixed phase shifters find their application area in Butler matrices and single channel monopulse converters[28]. Adjustable phase shifters are, on the other hand, one of the most critical elements in a scanned phased array antenna system.

Phase shifters are also divided into two parts according to the type of effort during adjustment: They are either mechanical or electronic. Electronic phase shifters are superior over their mechanical counterparts due to their inertialess phase shifting capability. In mechanical phase shifters, the phase shift is provided via some means of mechanical movement, such as rotating a knob; while it is usually of voltage controlled nature in electronic phase shifters. This difference of nature of phase change mechanisms between two types result in different state-change times as well. Electronic phase shifters are certainly much faster in operation than mechanical ones.

Another classification of phase shifters is according to the reciprocity of these devices. A reciprocal phase shifter could be utilized in both directions, but a non-reciprocal one usually offers haphazard phase and amplitude characteristics in the non-nominal usage direction.

An important category is the type of operation, being analog or digital. Digital phase shifters, as the name implies, have finite number of phase states and can not be operated to provide an arbitrary phase shift. On the other hand, analog phase shifters permit continuous insertion phase variation or in other words analog phase shifters have infinite phase resolution. Digital phase shifters are more compatible with the computerized systems, but an analog phase shifter can always be operated as if it is a digital one with the proper D/A and possibly a voltage leveling interface circuitry. A digital phase shifter has a truth table composed of some bits for reference to its different phase states. For an analog phase shifter, however, there exists some "control voltage to insertion phase transfer curve" used for correctly having the desired phase shift. A digital phase shifter is named after its number of bits, implying its angle resolution, while an analog phase shifter is addressed with its sensitivity. An obvious disadvantage of an analog phase shifter is the susceptibility of the phase shift due to slight variations in the control voltage. A digital phase shifter however, is insensitive to such small variations because the transistors are usually well-pinched off below their pinch-off voltage, keeping their insertion phase almost indifferent to the poorly regulated control voltages.

Hybrid approaches exist in the literature, where most of the phase shift is of digital nature but an analog bit of 11.25° is allocated fine tuning [31].

According to the transmission media employed to implement the phase shifter, a further classification can be done. Phase shifters can be realized in various media such as waveguide, planar transmission line, fin line and dielectric guide [28].

Finally, the technology of fabrication is an important discriminative property of phase shifters. Among these technology types are mainly ferrite, hybrid IC and MMIC. Also in the recent years, although not so mature as the classical IC's, RF MEMS takes its place among IC phase shifters. Ferrite phase shifters are bulky but they dominate over hybrid IC and MMIC in terms of loss and power handling capability. MMIC or in general IC phase shifters are superior to ferrite phase shifters with respect to size, weight and cost. They are incomparably smaller than ferrite phase shifters and once design is fixed, MMIC processes offer low cost phase

shifters in mass production. The logic behind phase shifting mechanisms in ferrite and IC phase shifters are quite different. Phase shifting with ferrites is usually accomplished by the change in magnetic permeability which occurs with application of a magnetic biasing field [32]. On the other hand, analog or digital voltages provide variation of the equivalent circuits represented by semiconductor circuit elements in IC type phase shifters.

In the context of this study, digital MMIC phase shifters are focused on, investigated and designed. Other types of phase shifters are mentioned shortly, wherever they are necessary for the sake of completeness.

# 2.2. Integrated Circuit Phase Shifters

The advent of IC technologies influenced the destiny of phase shifters profoundly as well as all other electronic circuits. Like all other microwave circuits, phase shifters enjoyed the benefits offered by IC approach. The principal advantage of IC phase shifters over waveguide phase shifters is the size of the circuit. Today's two dimensional phased arrays of thousands of elements would be impractical without IC phase shifters. Waveguide phase shifters are still not abandoned completely, they are critical in high power applications. They also have smaller insertion losses, which make them indispensable in certain transmit antenna applications. However, the common trend is to use IC phase shifters wherever possible. The term IC is a general term and could be separated into these parts:

- Hybrid IC (MIC)

- MMIC

- o Silicon

- o Compound Semiconductor (GaAs, InP, SiGe...)

- RF MEMS

- BST (Barium Strontium Titanate)

# **2.2.1.** Hybrid IC (MIC)

Hybrid IC phase shifters are a blend of different technologies, as the name implies. The switching elements are chip diodes or transistors, but together with the passive elements and lines they are in PCB form. With hybrid IC's post-production tuning is possible. Furthermore, failures can usually be easily detected and fixed. However, unit to unit repeatability of hybrid IC's is low and their high frequency performance is poor. On the other hand, the cost of unit area of chip is quite low, which is an advantage of hybrid production in favor of design flexibility.

#### 2.2.2. **MMIC**

The term MMIC stands for Monolithic Microwave Integrated Circuit. All passive and active elements are on the same substrate and thus no soldering is necessary in this technology. Indeed, the sizes of MMICs are so small that soldering is not possible. MMIC approach is suitable for mass production due to nature of the process that yields the chips. For MMICs post-production tuning is impossible and failure diagnosis is extremely difficult. Nevertheless, if the design is successful, the yield of a run is quite satisfactory as compared to hybrid IC's. As for the high frequency behavior, the choice of substrate material matters, although in any case MMIC dominates over hybrid circuits. Thanks to five times higher electron mobility of GaAs w.r.t Silicon, GaAs offers quite larger f<sub>t</sub>'s than Silicon. MMIC phase shifters with III-V compound semiconductor substrates are the most common ones among all types of IC phase shifters.

#### **2.2.3. RF MEMS**

RF MEMS is a newly emerging technology, but due to low-loss switching and fine capacitance variation capability, it is a suitable technology for producing digital and analog phase shifters. RF MEMS is quite cheaper than MMIC and bear similar advantages of MMIC over hybrid approach. The undesired point of RF MEMS is the restriction of switching life time, switching speed, power handling capability, reliability, etc due to various modes of failures including metal failure and dielectric

charging. However, RF MEMS appears to be promising in terms of cost per chip, due to less number of process steps as compared to MMIC production.

# 2.2.4. BST (Barium Strontium Titanate)

BST is also a new technology used for producing phase shifters. BST is a type of ferroelectric material whose dielectric constant changes with value of the electric field applied. With this property, the capacitance per unit length of a microstrip transmission line can be varied. This results in the modification of the phase velocity along the line, which can be exploited to shift the phase by moderate amounts. Also varactors and therefore analog phase shifters can be created with the same idea [29].

# 2.3. Digital Phase Shifters

The insertion phase of digital phase shifters can be switched to quantized levels that are determined in the design stage. As opposed to an analog phase shifter, there is finite number of states of the phase shifter, depending on the number of phase shifter bits. There exists a reference state with a nonzero insertion phase. When measured differentially the other states' phases lead or lag this reference phase by certain angular increments. An n bit phase shifter has insertion phase increments of  $360/2^N$ . To illustrate the operation for a 3 bit phase shifter, **Table 2.1** can be examined:

**Table 2.1** Nominal insertion phase of a three bit phase shifter at its 8 progressive states

| State | Insertion Phase | State | Insertion Phase |

|-------|-----------------|-------|-----------------|

| 000   | φ0              | 100   | φ0 + 180        |

| 001   | $\phi 0 + 45$   | 101   | φ0 + 225        |

| 010   | $\phi 0 + 90$   | 110   | $\phi 0 + 270$  |

| 011   | φ0 +135         | 111   | φ0 + 315        |

Also available from the table is that, all bits are not of the same power of changing the insertion phase. For instance, one could pass from state 000 to state 100 encountering a phase change of 180°. Therefore, bits exist with their significance, that is the most significant bit controls 180° and the least significant bit controls 45°. For any digital phase shifter, the most significant bit always controls 180°, but the least significant bit controls (360/2<sup>N</sup>)° where N stands for the number of phase shifter bits.

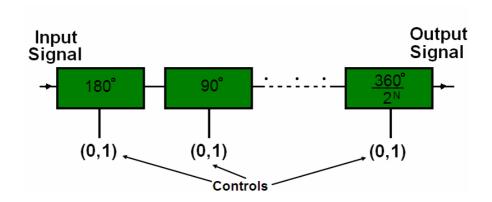

The general structure of an N bit digital phase shifter is presented in Figure 2.1

Figure 2.1 General digital phase shifter structure

From the figure, it is apparent that the phase bits are in cascade form. This structure provides the cumulative nature of the insertion phase, i.e. the signal is subject to the addition of the insertion phases of all blocks. Each block shifts the phase of the signal by the amounts indicated in the figure, thus it is possible to have all phase states by  $(360/2^N)$  o degree steps.

An alternative method would be having the smallest bit as a unit and repeating it in series  $2^N$  times. In that case, the design could be easier, but intolerable insertion loss would probably be suffered due to cascade nature of  $2^N$  networks instead of N networks. Thus the usual approach is to have N bits of binary-increasing weights.

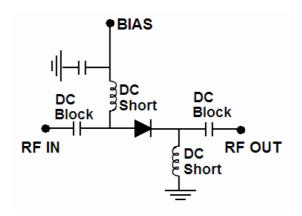

# 2.3.1. The Bit Concept

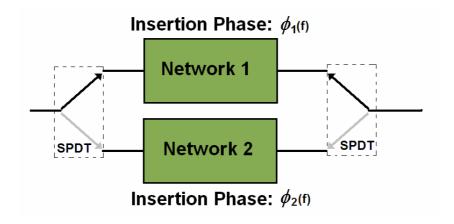

Meant by a "bit" of a digital phase shifter is a circuit that can be operated in two different states with respect to the insertion phase. At one state, the signal "sees" one circuit and at the other state it sees a different one. The phase shift is introduced by the difference of the phase incursions of these two circuits. The change in the circuit topology is provided through some switching devices. For a solid state phase shifter, available switch devices are PIN diodes, FETs mainly. For an RF MEMS type phase shifter, for example, circuit topology is varied by means of MEMS switches. The basic approach in both semiconductor and MEMS technology is to have SPDTs switching between two different networks of different phase responses. Figure 2.2 represents this action. The isolation of SPDTs are often tried to be maximized such that only one network is effectively active at a time. Ideally, one would design two networks with desired phase and amplitude characteristics and there would be no difference in the performance of the phase shifter bit upon insertion of SPDTs as in the figure. However, finite isolation of SPDTs is a practical problem and the aposteriori performance is usually quite different than that of the design made depending on ideal switch assumption. Therefore, noticing that responses in both states are those of two unequally fed parallel networks; the switches usually become a part of the design process.

Figure 2.2 The basic phase shifter structure

### 2.3.2. The Number of Bits in a Phase Shifter

The number of bits of a digital phase shifter determines its phase shift resolution. Phase shift resolution is doubled upon addition of a single bit. The LSB (Least Significant Bit) of a 4 bit phase shifter is 22.5° degrees while that of a 5 bit phase shifter is 11.25°. Nonetheless, it might not be meaningful to have an 8 bit phase shifter (with 1.4° resolution) due to practical facts, i.e. phase variation over frequency. Especially for a wideband phase shifter there is always phase error and usually as the number of bits increases, so does the ratio of phase error to the phase resolution. Therefore it is futile to have very small phase steps (or many bits) unless the phase error is significantly less than the step size.

In a phased array application, the relation between the beam steer angle,  $\theta$ , and the progressive phase shift,  $\delta$ , between antenna elements is given as:

$$\delta = k_0 \sin \theta \tag{2-5}$$

where  $k_0$  is the wavenumber and  $\theta$  is defined as the angle between the array boresight and the beam direction

As the minimum progressive phase shift is equal to the LSB of the phase shifters employed in the array, the resolution of the phase shifter directly determines the steering resolution of the phased array.

However, in a large array, a number of adjacent elements can be considered as a subgroup and be fed equiphase. The next subgroup of elements is again fed equiphase w.r.t. each other but with the smallest possible phase increment w.r.t the previous group. By this method, effective phase resolution is increased by the number of elements in the subgroups.

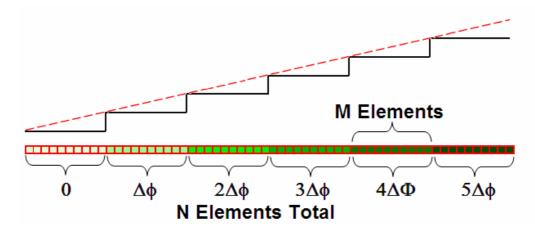

**Figure 2.3** The method of virtually increasing the phase shift resolution in a phased array antenna

Referring to the figure, if  $\Delta \phi$  is the minimum step size of the phase shifters used in the array, the feeding shown approximates the feeding scheme where the minimum step size is  $\Delta \phi/M$  and each antenna element's phases is progressed from the previous element by this much phase. Of course this is only an approximation and the system suffers from grating lobes at smaller scan angles as compared to a system with phase shifters of resolution  $\Delta \phi/M$ .

### 2.3.3. Digital Phase Shifter Requirements

## 2.3.3.1. Phase Flatness

There is always some phase shift error in the nominal bandwidth of a phase shifter. Ideally, a phase shifter would provide constant phase shift over the entire bandwidth, but this is impossible in practice. Usually the designer adjusts the phase shift to be the desired value in the band center and allow some variation around this value. The maximum allowable phase error depends on the application but it is meaningless to have it larger than phase resolution for any phase shifter.

Opposed to this requirement, a switched line phase shifter has inherently linear phase shift characteristics with frequency, because the phase shift depends merely on the difference between the electrical lengths of the two lines. It turns out that a switched

line phase shifter is a time shifter indeed. However this could sometimes be desirable: When operating a phased array over a bandwidth and when the beam is required to remain untilted as the frequency is varied, it is best to have linear phase shift characteristics. With this feature, the progressive phase shift between array elements increases in proportion with the frequency, which provides true time delay. Therefore the signals from all elements are added in phase at the same angle at all frequencies. If, on the contrary, the phase characteristic is flat, the beam is tilted as the frequency changes, which could result in angle errors in detection.

#### 2.3.3.2. Number of Bits

The number of bits of a digital phase shifter determines the phase steps. For a phased array application, this is critical since the minimum progressive phase shift is equal to the minimum phase step of the phase shifter.

### 2.3.3.3. Amplitude Imbalance

An ideal phase shifter does not affect the magnitude while changing the phase of the signal passing through it. However, in practice, from state to state there is some change in the amplitude of the signal. Moreover this change is a function of frequency. This modification of amplitude is undesirable. In communication circuits this phenomena would result in PM/AM conversion. Furthermore, for a phased array with some desired tapering, amplitude imbalance may result in undesired perturbation of the amplitude distribution while steering the beam of the antenna. The sidelobe levels might increase a few dBs unless the amplitude imbalance is low enough or there exists variable attenuators that could correct the amplitude terms. It is best to keep the amplitude imbalance as low as possible to have a phase shifter that can be used at any system, possibly an array with amplitude tapering.

### 2.3.3.4. Insertion Loss

The insertion loss is of course something undesirable, but it could be tolerated if it is not too high. While evaluating the insertion loss of a phase shifter, the number of bits must be taken into account in order not to be too harsh or too tolerant. Usually it is logical to have more insertion loss with more bits, because the bits are in cascaded form. With other properties being the same, a 4 bit phase shifter with 6 dB insertion

loss could be counted more useful than a 3 bit phase shifter with 5.9 dB insertion loss. Furthermore, the bandwidth of the phase shifter is also important. To have a wider bandwidth (in terms of phase flatness for example), more insertion loss could be tolerated.

### **2.3.3.5.** Return Loss

As in almost all microwave circuits, the return loss of a phase shifter is somehow critical. The phase shifter is usually only a part of a more complex system. To be able to operate the phase shifter as desired and also not to disturb peripheral circuits of the phase shifter, the return loss must be as low as possible. The first example that comes into mind is a beam-forming network where the phase shifter is most probably cascaded with an attenuator. If the return loss is not sufficiently low, several perturbations over the attenuator and phase shifter settings might be necessary to finely tune the strip to the desired amplitude and phase setting. This is partly a result of reflections between the phase shifter and the attenuator.

### 2.3.3.6. Switching Speed

The switching speed is a measure of how quick the phase shifter responds to a change in the desired phase setting. Therefore the importance of the switching speed depends on the application. In the most famous application area, the phased array antenna, the switching speed determines the beam steering speed. In the modern electronic warfare age of complex track and search and ECM environment the required beam steering period might be in the order of microseconds. For IC phase shifters the switching speed depends upon the technology and the circuit topology. On the other hand, for ferrite phase shifters, the hysteresis characteristic of the ferrite material is the main factor influencing the switching speed of the device. As for the mechanical phase shifter, though not digital, the rate of phase change is obviously very poor.

## 2.3.3.7. Driver Voltages

Digital phase shifters are operated by means of digital signals controlling the gate bias (for a FET type phase shifter) or the electrode voltage (for a PIN diode phase shifter). It is usually necessary to have a level translation circuit between the gates or electrodes and the digital signals of the control system. For example, negative voltages are required to pinch off a depletion type MESFET, while CMOS; TTL or LVDS voltages might be common to elsewhere in the system. This level translation could be on the chip or, an extra interface could handle this job, freeing the designer of the phase shifter form adding the driving circuitry to the chip.

#### **2.3.3.8.** Bandwidth

Certainly, the bandwidth of a phase shifter is very important, but the bandwidth is defined considering the degradation of some of the above mentioned parameters with frequency such as phase flatness, insertion loss, and amplitude imbalance. The bandwidth of the phase shifter is between the two extreme frequencies where these parameters remain within tolerable limits.

## 2.3.3.9. Power Handling

The power handling requirement of a phase shifter depends on the application. A phase shifter in the transmit array of a satellite antenna may have to operate well with power levels of several hundred watts coming from a TWTA, while a phase shifter on the receive strip of a T/R module is required to operate at a few milliwatts.

### 2.3.3.10. Size

The size is a critical issue in some aspects. First, at the user's side, smaller is almost always favored, because it leads to smaller system and more room remains for something else. Second, at the designer's side; considering an IC phase shifter, smaller chip size results in either less area on the wafer for the same number of chips, or more chips on the same area.

### **CHAPTER 3**

### **DESIGN OF MMIC PHASE SHIFTERS**

# 3.1. Common Phase Shifter Topologies

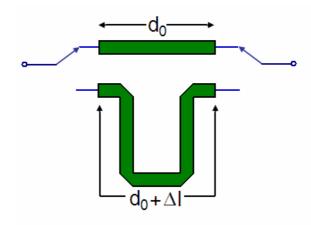

### 3.1.1. Switched Line Phase Shifters

The most basic transmission type phase shifter is the switched line phase shifter. As the name implies, there are two lines of different electrical lengths, which are switched to yield the desired phase shift. The return loss of the switched line phase shifter is determined by the line impedances with the SPDT switches considered ideal. Therefore, selecting the lines matched to the desired characteristic impedance, return loss is taken granted and the design is relaxed. Another relaxing factor having the inherent matching is that the magnitude of the return loss does not change from state to state, thanks to lossless lines. The following figure represents the switched line phase shifter:

Figure 3.1 Topology of the switched line phase shifter

The electrical lengths of the lines are the physical lengths times the propagation constant  $\beta$ :

$$\theta_1 = \beta d_0$$

$$\theta_2 = \beta (d_0 + \Delta l)$$

(3-1)

Switching between the lines results in a differential phase shift proportional to the difference between the lengths of the lines:

$$\Delta \phi = \theta_2 - \theta_1 = \beta \Delta l \tag{3-2}$$

Apparent from the result is that, the phase shift offered by the switched line phase shifter is proportional to the frequency due to the frequency dependence of  $\beta$ .

### 3.1.1.1. Sample Design

Here is the simulation result of an ideal switched line phase shifter designed to shift the phase by  $90^{\circ}$  @ 9.5 GHz:

Figure 3.2 Differential phase shift of the ideal switched line phase shifter

The proportionality of the differential phase shift is readily observed in **Figure 3.2**. As mentioned before, this is due to the constant time delay between the two paths in the phase shifter.

The loss, the amplitude imbalance and the return loss of the ideal switched line phase shifter is not necessary to be presented here because they are perfect. Of course, the design is not this simple when the practical switches and transmission lines are employed.

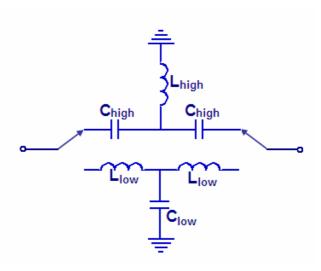

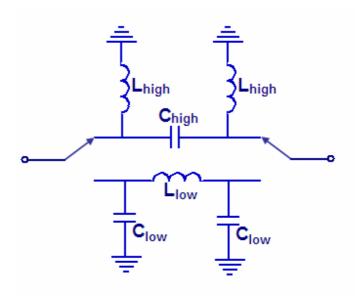

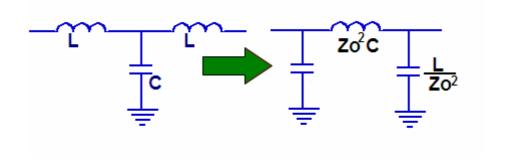

# 3.1.2. High Pass - Low Pass Type Phase Shifters

It is known that a low pass filter with series inductors and shunt capacitors introduces phase delay whereas a high pass filter composed of series capacitors and shunt inductors introduces phase advance. Upon proper selection of the element values in these networks, it is possible to have their insertion phases track each other with almost constant offset within an appreciable band. For a typical phase shifter application, it is also required that the insertion losses of both networks are low and close to each other. Therefore both filters must be operated within their passband and this passband should certainly be common to both filters. The two options, TEE type and PI type HP/LP networks are given in **Figure 3.3** and **Figure 3.4**. In a phase shifter application, there is no drawback in having one filter in TEE configuration and the other in PI configuration.

Figure 3.3 TEE type LP/HP phase shifter

Figure 3.4 PI type LP/HP phase shifter

In order to derive the element values of the filters, S parameters of the filters must first be obtained. It is best to use ABCD to S parameter transformation for the ladder type networks because the ABCD matrix of a cascade connection is simply the product of the individual ABCD matrices of the series and shunt components. The ABCD matrix of a series element with impedance Z seen in **Figure 3.5** is:

$$\begin{bmatrix} A & B \\ C & D \end{bmatrix} = \begin{bmatrix} 1 & Z \\ 0 & 1 \end{bmatrix} \tag{3-3}$$

Figure 3.5 Series impedance Z

Similarly, the ABCD matrix of a shunt admittance Y is given as:

$$\begin{bmatrix} A & B \\ C & D \end{bmatrix} = \begin{bmatrix} 1 & 0 \\ Y & 1 \end{bmatrix} \tag{3-4}$$

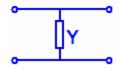

Figure 3.6 Shunt admittance Y

Hence the ABCD matrix of a TEE type network is:

$$\begin{bmatrix} A & B \\ C & D \end{bmatrix} = \begin{bmatrix} 1 & Z \\ 0 & 1 \end{bmatrix} \begin{bmatrix} 1 & 0 \\ Y & 1 \end{bmatrix} \begin{bmatrix} 1 & Z \\ 0 & 1 \end{bmatrix} = \begin{bmatrix} 1 + YZ & 2Z + YZ^2 \\ Y & 1 + YZ \end{bmatrix}$$

(3-5)

Using this expression, the ABCD parameters of the network in **Figure 3.7** is found as in:

$$\begin{bmatrix} A & B \\ C & D \end{bmatrix} = \begin{bmatrix} 1 - BX & 2jX - jBX^2 \\ jB & 1 - BX \end{bmatrix}$$

(3-6)

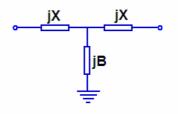

Figure 3.7 Generic TEE type network

The insertion loss of any network (inserted into a Zo  $\Omega$  system) is derived from its ABCD matrix as:

$$S_{21} = \frac{2}{A + B/Zo + CZo + D} \tag{3-7}$$

Applying this transformation for the network in **Figure 3.7**,

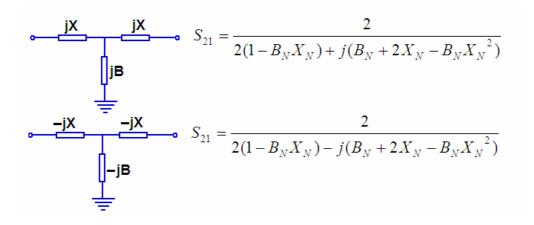

$$S_{21} = \frac{2}{2(1 - B_N X_N) + j(B_N + 2X_N - B_N X_N^2)}$$

$$= \frac{2}{2(1 - BX) + j(BZo + 2X/Zo - BX^2/Zo)}$$

(3-8)

It is readily seen that the magnitude of  $S_{21}$  will remain the same, but the phase of  $S_{21}$  will change sign, if a network with  $-jX_N$  and  $-jB_N$  is considered. This idea is explained in the following figure.

## In Figure 3.8,

$$B_N = BZo$$

$$X_N = X/Zo$$

(3-9)

Figure 3.8 The insertion loss comparison of the two T type networks

The equality of the magnitudes of susceptance and reactance values of the two networks is valid only at a single frequency, which is to be selected as the center frequency of the phase shifter.

The low pass filter is the one with positive reactances and susceptance and the high pass filter is the other network.

The insertion phases of these networks are derived from the  $S_{21}$ 's as:

$$\phi^{high} = \tan^{-1} \left[ \frac{B_N + 2X_N - B_N X_N^2}{2(1 - B_N X_N)} \right]$$

(3-10)

$$\phi^{low} = \tan^{-1} \left[ -\frac{B_N + 2X_N - B_N X_N^2}{2(1 - B_N X_N)} \right] = -\tan^{-1} \left[ \frac{B_N + 2X_N - B_N X_N^2}{2(1 - B_N X_N)} \right]$$

(3-11)

The differential phase shift is found by taking the difference of the insertion phases of the two networks:

$$\phi^{Diff} = \phi^{high} - \phi^{low} = 2 \tan^{-1} \left[ \frac{B_N + 2X_N - B_N X_N^2}{2(1 - B_N X_N)} \right]$$

(3-12)