## AN APPLICATION-AWARE DRAM CONTROLLER

# A THESIS SUBMITTED TO THE GRADUATE SCHOOL OF NATURAL AND APPLIED SCIENCES OF MIDDLE EAST TECHNICAL UNIVERSITY

## BY

## RAMAZAN CİLASIN

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS

FOR

THE DEGREE OF MASTER OF SCIENCE

IN

ELECTRICAL AND ELECTRONICS ENGINEERING

SEPTEMBER 2019

## Approval of the thesis:

## AN APPLICATION-AWARE DRAM CONTROLLER

submitted by RAMAZAN CİLASIN in partial fulfillment of the requirements for the degree of Master of Science in Electrical and Electronics Engineering Department, Middle East Technical University by,

| Prof. Dr. Halil Kalıpçılar<br>Dean, Graduate School of <b>Natural and Applied Sciences</b>           |  |

|------------------------------------------------------------------------------------------------------|--|

| Prof. Dr. İlkay Ulusoy<br>Head of Department, <b>Electrical and Electronics Eng.</b>                 |  |

| Assoc. Prof. Dr. Cüneyt Fehmi Bazlamaçcı<br>Supervisor, <b>Electrical and Electronics Eng., METU</b> |  |

| Examining Committee Members:                                                                         |  |

|                                                                                                      |  |

| Prof. Dr. İlkay Ulusoy<br>Electrical and Electronics Eng. Dept., METU                                |  |

| Assoc. Prof. Dr. Cüneyt Fehmi Bazlamaçcı<br>Electrical and Electronics Eng., METU                    |  |

| Prof. Dr. Gözde Bozdağı Akar<br>Electrical and Electronics Eng. Dept., METU                          |  |

| Prof. Dr. Ece Güran Schmidt<br>Electrical and Electronics Eng. Dept., METU                           |  |

| Assoc. Prof. Dr. Süleyman Tosun<br>Computer Engineering Department, Hacettepe University             |  |

Date: 06.09.2019

| I hereby declare that all information in this document has been obtained and presented in accordance with academic rules and ethical conduct. I also declare that, as required by these rules and conduct, I have fully cited and referenced all material and results that are not original to this work. |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name, Surname: Ramazan Cilasın                                                                                                                                                                                                                                                                            |

| Signature:                                                                                                                                                                                                                                                                                                |

| Signature.                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                           |

| iv                                                                                                                                                                                                                                                                                                        |

#### ABSTRACT

## AN APPLICATION-AWARE DRAM CONTROLLER

Cilasın, Ramazan Master of Science, Electrical and Electronics Engineering Supervisor: Assoc. Prof. Dr. Cüneyt Fehmi Bazlamaçcı

September 2019, 91 pages

Considering that emerging technologies have started to require excessive amount of memory, with quick response times and low power consumption, more efficient memory systems has become a crucial need for almost every system ranging from mobile phones to data centers. However, there exists a gap between CPU and memory speeds and most application execution times depend almost entirely on the speed at which RAM can send data to the CPU. As for the main memory, DDRx DRAM's relatively low-latency, high density and low cost made it the technology choice. DRAM market is a cost-sensitive market and architectural changes in DRAM is not easily welcomed by the manufacturers. On the other hand, DRAM is managed by Memory Controller which provides an interface between requestors and DRAM, and changes to the Memory Controller might have considerable effect on mitigating the problems incurred by slow memory. In this thesis work, DRAM Controllers for general purpose computers are focused on and based on the problem mentioned above the following algorithmic contributions and proposals are made: (i) an application aware memory scheduling algorithm to reduce the main memory interference and to provide fairness (ii) a hybrid page policy to avoid unnecessary activations, (iii) a dynamic command scheduling scheme that is essential for providing flexibility, (iv) a refresh scheduling method to decrease latency and power consumption, (v) an efficient way of using power-down modes to provide balance between latency and power

consumption, (vi) integration of a memory access latency reduction method which is using the intrinsic DRAM characteristics. This thesis work's resultant controller provides a performance benefit of 9.31% on average compared to a recently proposed application aware controller, while serving fairer to applications and consuming lower power at the expense of higher storage cost. Proposed methods are simple to implement and can be used in a modern memory controller.

Keywords: DRAM, Memory controller, Application awareness, Memory scheduling

## UYGULAMA FARKINDA DİNAMİK RASTGELE ERİŞİMLİ BELLEK KONTROLCÜSÜ

Cilasın, Ramazan Yüksek Lisans, Elektrik ve Elektronik Mühendisliği Tez Danışmanı: Doç. Dr. Cüneyt Fehmi Bazlamaçcı

Eylül 2019, 91 sayfa

Gelişmekte olan teknolojilerin hızlı tepki süreleri ve düşük güç tüketimi sağlayan bellek gereksinimleri göz önünde bulundurulduğunda, daha etkili bellek sistemleri, akıllı telefonlardan veri merkezlerine kadar olan bütün sistemlerde çok önemli bir ihtiyaç haline gelmiştir. Fakat işlemci ve bellek hızları arasındaki farkın şiddetli biçimde artmasıyla çoğu uygulamanın yürütme süreleri neredeyse tamamen Rastgele Erişimli Belleklerin işlemcilere veri yollama hızlarına bağlı olacaktır. Ana hafiza olarak, düşük gecikme süresi, yüksek yoğunluğu ve düşük maliyetinden dolayı DDRx DRAM teknolojisi seçilmiştir. DRAM piyasası, maliyete duyarlı bir pazardır ve DRAMdeki değişiklikler üreticiler tarafından kolayca kabullenilmemektedir. Diğer yandan DRAM, istemciler ve DRAM arasında arayüz sağlayan bir bellek kontrolcüsü tarafından yönetilir ve bellek kontrolcüsünde yapılacak değişikliklerin yavaş belleğin sebep olduğu sorunları azaltmada önemli etkileri olabilir. Bu tez çalışmasında genel maksatlı bilgisayarlarda bulunan DRAM kontrolcülerindeki muhtemel iyileştirmelere odaklanılmıştır ve yukarıda bahsedilen probleme yönelik asağıdaki algoritmik katkılar ve öneriler sunulmuştur: (i) ana bellekteki istemci çatışmalarını azaltan ve adil istemci servisi sağlayan bir uygulama farkında bellek zaman çizelgeleyicisi algoritması (ii) ana bellekteki gereksiz etkinleşmeyi engelleyen karma bir bellek sayfası ilkesi (iii) esneklik sağlamak için gerekli olan dinamik bir komut çizelgeleme şeması (iv) gecikme ve güç tüketimin azaltmak için bir yenileme çizelgeleme yöntemi (v) gecikme ve güç tüketimi arasında bir denge sağlamak için güç kapatma modlarının etkili kullanımı (vi) DRAM iç karakteristiklerini kullanan bir bellek erişim gecikme azaltma yönteminin entegrasyonu. Bu tez çalışması sonucunda elde edilen DRAM kontrolcüsü, daha fazla bellek kullanım maliyeti karşılığında, yakın zamanda önerilen bir uygulama farkında DRAM kontrolcüsüne oranla uygulamalara daha adil servis sağlar, daha az güç tüketimi yapar ve ortalamada %9,31 daha iyi performans sergiler. Önerilen yöntemlerin uygulanması kolaydır ve modern bir bellek kontrolcüsünde kullanılabilir.

Anahtar Kelimeler: DRAM, Bellek kontrolcüsü, Uygulama farkındalığı, Bellek zaman çizelgeleyicisi

To Mediha & Özge...

#### **ACKNOWLEDGEMENTS**

I would like to express my deepest gratitude to my advisor Assoc. Prof. Dr Cüneyt Bazlamaçcı for his guidance and endless support in my study. His valuable feedbacks and inspiring ideas in every step of the thesis encouraged me to write it and made this experience an amazingly fruitful one.

I would also wish to express my sincere gratitude to my thesis examining committee members Prof. Dr. İlkay Ulusoy, Prof. Dr. Gözde Bozdağı Akar, Prof. Dr. Ece Güran Schmidt and Assoc. Prof. Dr. Süleyman Tosun for kindly accepting to share their invaluable comments and helpful suggestions with me.

I am grateful to my colleague Mehmet Can Karagöz for his valuable support. He encouraged me all the time and helped me to make the simulation framework run flawlessly. Besides, without his support during the extensive simulations, this thesis would have been impossible to complete.

Last but not least, I would like to thank two very special women in my life, Özge and Mediha. Without the encouragement, endless patience and invaluable support of my one and only love Özge, this work would not have been possible and although no longer with us, my mother Mediha has been the biggest inspiration to me for everything I do and she is the true possessor of my success, may her soul rest in peace.

## TABLE OF CONTENTS

| ABSTRACTv                                |

|------------------------------------------|

| ÖZvii                                    |

| ACKNOWLEDGEMENTS x                       |

| TABLE OF CONTENTSxi                      |

| LIST OF TABLESxv                         |

| LIST OF FIGURESxvi                       |

| LIST OF ABBREVIATIONS xviii              |

| 1. INTRODUCTION                          |

| 1.1. Overview                            |

| 1.2. Outline                             |

| 2. BACKGROUND                            |

| 2.1. Memory System Architecture          |

| 2.2. Main Memory Organization            |

| 2.2.1. DRAM Basics                       |

| 2.2.1.1. DRAM Commands                   |

| 2.2.1.2. An Example Cycle                |

| 2.2.2. DRAM Memory Controller            |

| 2.2.2.1. Address Translation (Mapping)   |

| 2.2.2.2. Transaction Scheduling          |

| 2.2.2.3. Command Generation & Scheduling |

| 2.2.2.4. Refresh Management              |

| 2.2.2.5. Error Management                |

| 3. RELATED WORK                                            | 27               |

|------------------------------------------------------------|------------------|

| 3.1. Scheduling                                            | 27               |

| 3.1.1. TCM (Thread Cluster Memory Scheduling)              | 27               |

| 3.1.2. Thread Fair Memory Request Reordering               | 27               |

| 3.1.3. LAMS (A Latency-Aware Memory Scheduling Policy)     | 28               |

| 3.1.4. Staged Reads                                        | 28               |

| 3.1.5. Rank-Level Parallelism in DRAM                      | 29               |

| 3.1.6. MEDUSA (A Predictable and High-Performance DRAM     | Controller)29    |

| 3.1.7. BLISS (Blacklisting Scheduler)                      | 30               |

| 3.2. Bank/Bandwidth Allocation                             | 30               |

| 3.2.1. BWLOCK (Bandwidth Lock)                             | 30               |

| 3.2.2. PALLOC (DRAM bank-aware memory allocator)           | 31               |

| 3.3. Access Latency                                        | 31               |

| 3.3.1. NUAT (A Non-Uniform Access Time Memory Controlle    | er)31            |

| 3.3.2. ChargeCache                                         | 32               |

| 3.3.3. AL-DRAM (Adaptive-Latency DRAM)                     | 32               |

| 3.4. Refresh                                               | 33               |

| 3.4.1. A Case for Refresh Pausing in DRAM Memory Systems   | 33               |

| 3.4.2. Non-blocking Memory Refresh                         | 33               |

| 3.4.3. DTail (A Flexible Approach to DRAM Refresh Managen  | nent)33          |

| 3.4.4. Elaborate Refresh                                   | 34               |

| 3.4.5. AVATAR (A Variable Retention-Time Aware Refresh) .  | 34               |

| 3.4.6. Improving DRAM Performance by Parallelizing Refresh | es with Accesses |

|                                                            | 34               |

|    | 3.4.7. Refresh Aware Write Recovery Memory Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 35 |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|    | 3.5. Page Policy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 36 |

|    | 3.5.1. RBPP (A Row-based DRAM page policy)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 36 |

|    | 3.5.2. Closed-yet Open DRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 36 |

|    | 3.6. Last-Level Cache and Memory Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 37 |

|    | 3.6.1. Row-Buffer Hit Harvesting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 37 |

|    | 3.6.2. DRAM-Aware Last-Level Cache Writeback                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 37 |

|    | 3.7. Power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 38 |

|    | 3.7.1. A Read-write aware DRAM scheduling for power reduction in multi-control of the scheduling for power reduction in multi-control of the scheduling for power reduction in multi-control of the scheduling for power reduction in multi-control of the scheduling for power reduction in multi-control of the scheduling for power reduction in multi-control of the scheduling for power reduction in multi-control of the scheduling for power reduction in multi-control of the scheduling for power reduction in multi-control of the scheduling for power reduction in multi-control of the scheduling for power reduction in multi-control of the scheduling for power reduction in multi-control of the scheduling for power reduction in multi-control of the scheduling for power reduction in multi-control of the scheduling for power reduction in multi-control of the scheduling for power reduction in multi-control of the scheduling for power reduction in multi-control of the scheduling for power reduction in multi-control of the scheduling for the scheduling for power reduction in the scheduling for the scheduling for the scheduling for the scheduling for power reduction in the scheduling for the scheduling for the scheduling for the scheduling for the scheduling for the scheduling for the scheduling for the scheduling for the scheduling for the scheduling for the scheduling for the scheduling for the scheduling for the scheduling for the scheduling for the scheduling for the scheduling for the scheduling for the scheduling for the scheduling for the scheduling for the scheduling for the scheduling for the scheduling for the scheduling for the scheduling for the scheduling for the scheduling for the scheduling for the scheduling for the scheduling for the scheduling for the scheduling for the scheduling for the scheduling for the scheduling for the scheduling for the scheduling for the scheduling for the scheduling for the scheduling for the scheduling for the scheduling for the scheduling for the scheduling for the scheduling for the | ore  |

|    | systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 38 |

|    | 3.7.2. RAMS (DRAM Rank-Aware Memory Scheduling)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 38 |

| 4. | AN APPLICATION-AWARE DRAM CONTROLLER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 39 |

|    | 4.1. Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 39 |

|    | 4.2. Motivation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 40 |

|    | 4.3. Memory Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 40 |

|    | 4.4. Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 41 |

|    | 4.4.1. Memory Access Intensity Detection (MAID)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 41 |

|    | 4.4.2. Command Scheduling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 45 |

|    | 4.4.3. Page Policy Adaptation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 47 |

|    | 4.4.4. Refresh Scheduling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 49 |

|    | 4.4.5. Access Latency Mitigation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 51 |

|    | 4.4.6. Power-down Mode Usage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 53 |

|    | 4.4.7. Storage Cost                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 55 |

| _  | EVALUATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 57   |

|    | 5.1. Simulation Environment      | 57 |

|----|----------------------------------|----|

| :  | 5.2. Evaluation Workloads        | 58 |

|    | 5.3. Evaluation Metrics          | 60 |

| :  | 5.4. Results                     | 61 |

|    | 5.4.1. MAID                      | 62 |

|    | 5.4.2. Command Scheduling        | 66 |

|    | 5.4.3. Page-Policy               | 69 |

|    | 5.4.4. Access Latency Mitigation | 71 |

|    | 5.4.5. Refresh Scheduling        | 74 |

|    | 5.4.6. Power-down Usage          | 76 |

|    | 5.4.7. Overall Effects           | 80 |

| 6. | CONCLUSION AND FUTURE WORK       | 83 |

| RF | FERENCES                         | 87 |

## LIST OF TABLES

## **TABLES**

| Table 2.1 Important DRAM timing parameters                                    | 16 |

|-------------------------------------------------------------------------------|----|

| Table 2.2 Device density vs Refresh completion time [41]                      | 25 |

| Table 4.1 Current ratings for background power of chips used in [35]          | 54 |

| Table 5.1 Default USIMM configurations used for evaluations                   | 58 |

| Table 5.2 Evaluation Workloads                                                | 59 |

| Table 5.3 Benchmark Combinations                                              | 59 |

| Table 5.4 Window Length Effect on evaluation metrics for MAID only scheduler. | 65 |

| Table 5.5 Effect of other watermark values on evaluation metrics              | 68 |

| Table 5.6 HCRAC table size effect on the evaluation metrics                   | 73 |

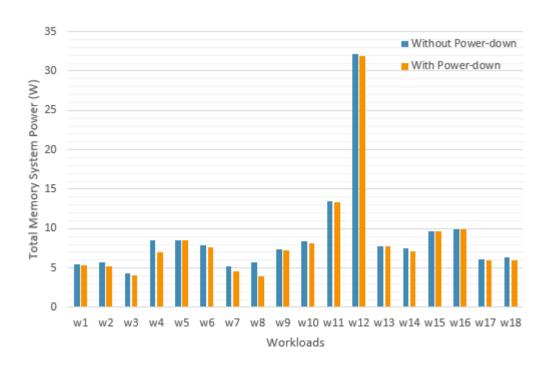

| Table 5.7 Power-down slow and Power-down fast compared with no power-down     | 79 |

## LIST OF FIGURES

## **FIGURES**

| Figure 1.1. Processor vs Memory performance improvement over the years [40]     | )]2    |

|---------------------------------------------------------------------------------|--------|

| Figure 1.2 Refresh effect on energy consumption vs device density [41]          | 3      |

| Figure 1.3 Refresh effect on IPC (Instruction Per Cycle) and average latency vs | device |

| density [41]                                                                    | 4      |

| Figure 2.1 Memory components of general-purpose computers                       | 8      |

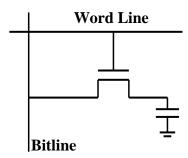

| Figure 2.2 DRAM 1-cell structure                                                | 9      |

| Figure 2.3 Memory arrays forming a single bank                                  | 10     |

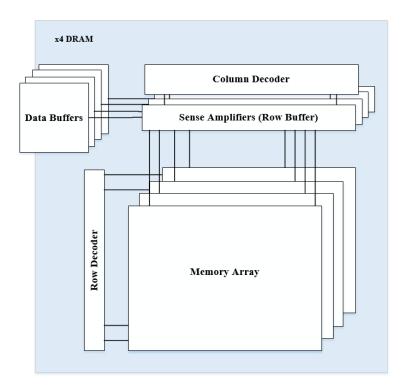

| Figure 2.4 Top-level DRAM structure                                             | 11     |

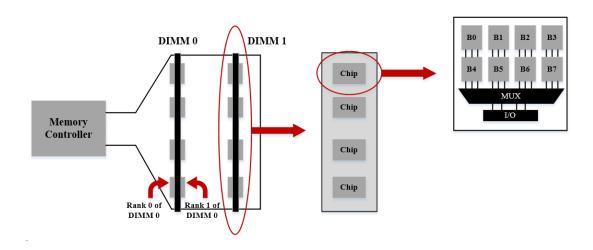

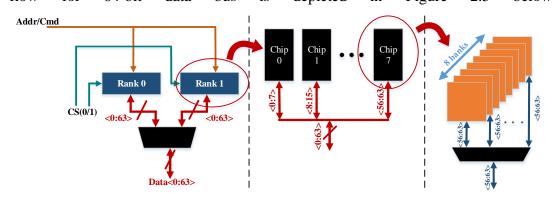

| Figure 2.5 Typical data flow of 64-bit data bus                                 | 11     |

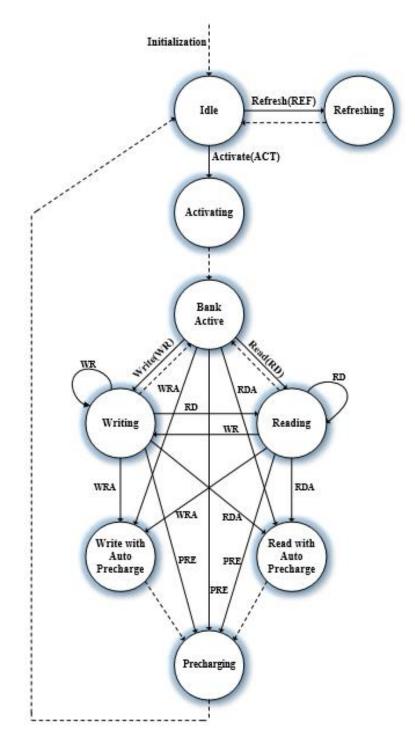

| Figure 2.6 DRAM States and Commands                                             | 13     |

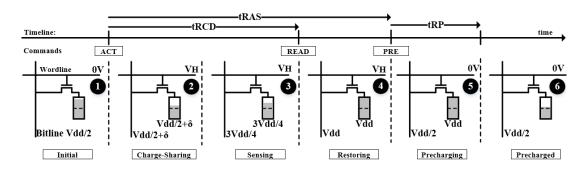

| Figure 2.7 Typical Read cycle with commands, timing parameters & charge sta     | ate17  |

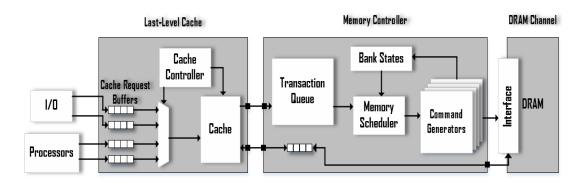

| Figure 2.8 LLC, Memory Controller and DRAM interaction                          | 18     |

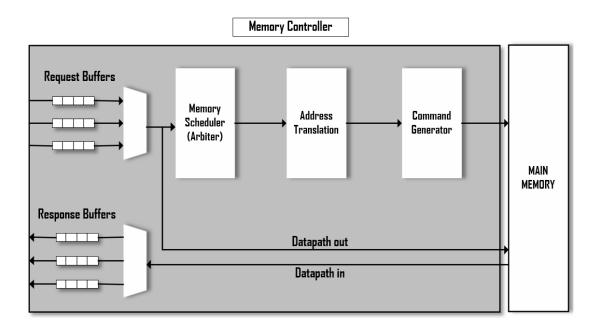

| Figure 2.9 Memory Controller Internal Structure                                 | 19     |

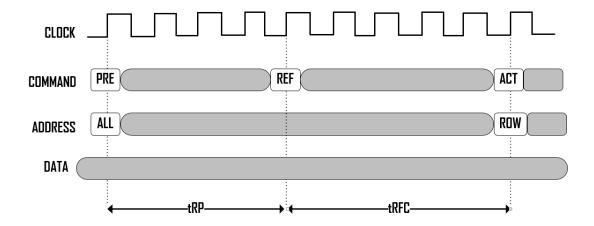

| Figure 2.10 Auto-Refresh example cycle                                          | 24     |

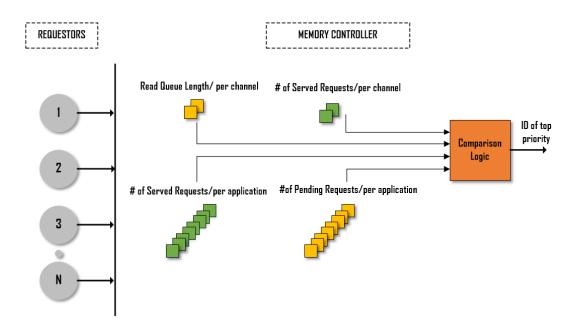

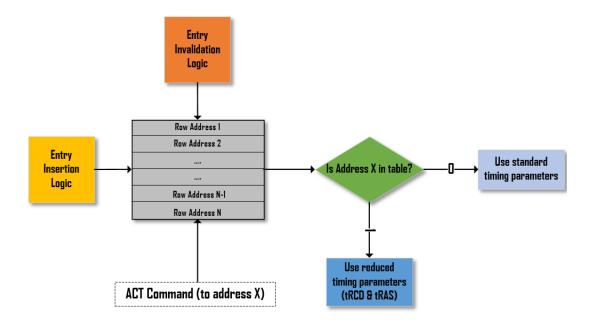

| Figure 4.1 Memory Intensity Detection (MAID) Algorithm Overview                 | 43     |

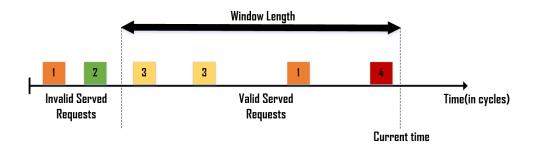

| Figure 4.2 Sliding Window for MAID Algorithm                                    | 44     |

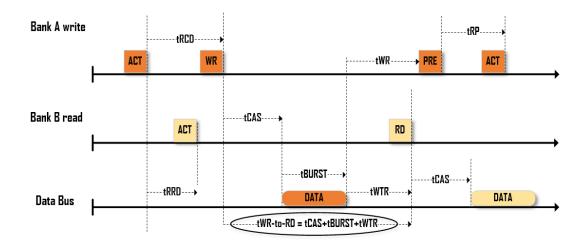

| Figure 4.3 Write-to-Read Switching effect                                       | 45     |

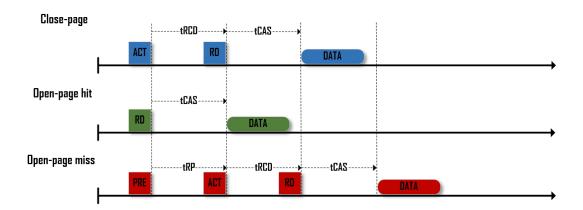

| Figure 4.4 Open and Close Page-Policies' Read Latencies                         | 48     |

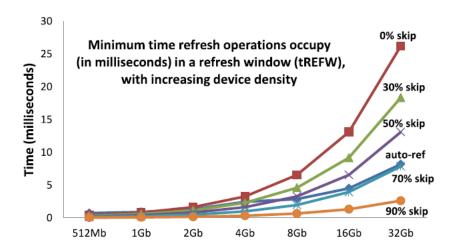

| Figure 4.5 Refresh-time vs Device Density for row-selective approach [41]       | 50     |

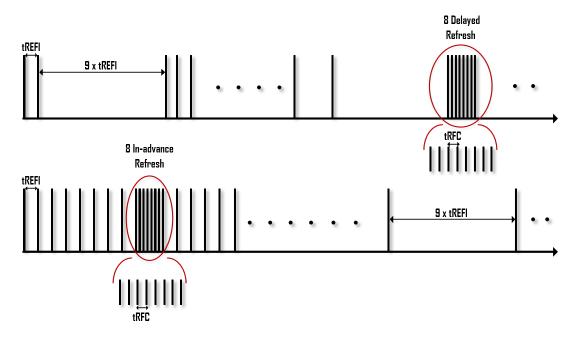

| Figure 4.6 Flexible Auto-Refresh Scheduling built-in DRAM devices               | 51     |

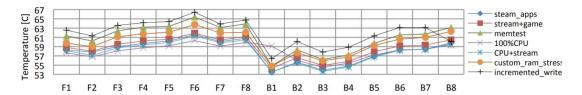

| Figure 4.7 Temperature variation across a DIMM vs Different Applications re     | ınning |

| on different sides of DIMM[42]                                                  | 52     |

| Figure 4.8 ChargeCache Algorithm [20]                                           | 52     |

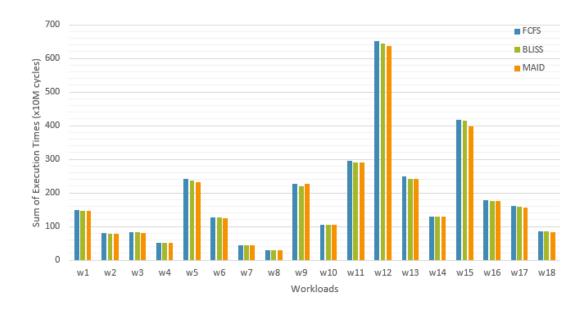

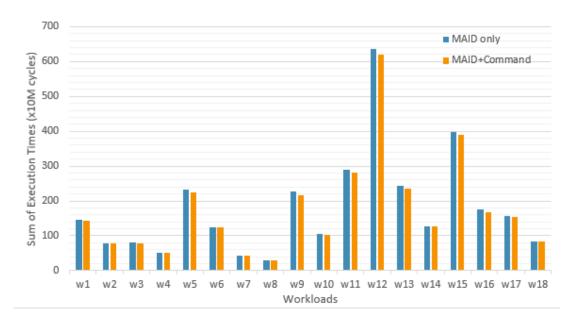

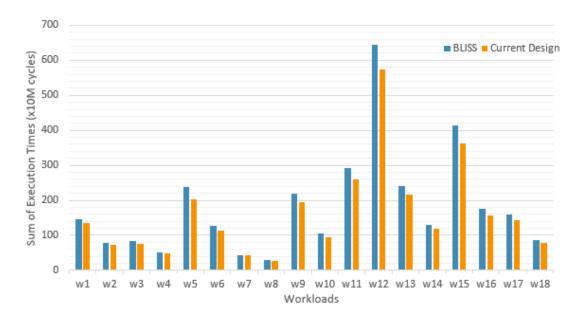

| Figure 5.1 Sum of Execution Times vs workloads under different schedulers       | 63     |

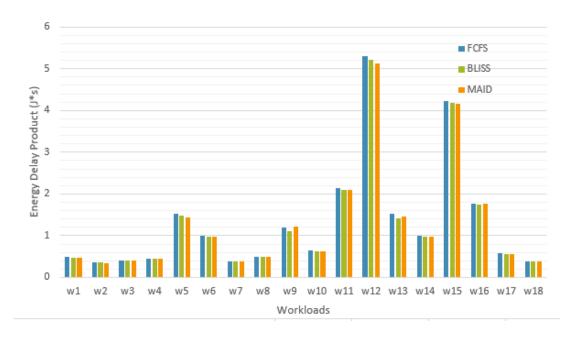

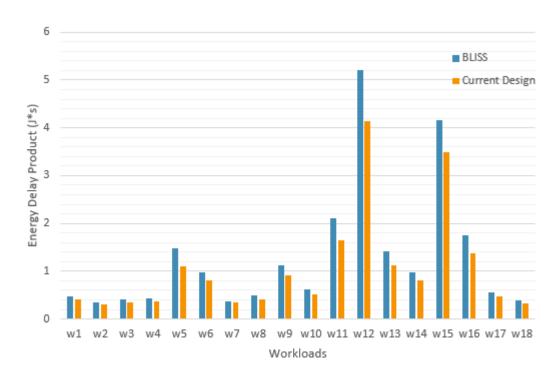

| Figure 5.2 EDP vs workloads under different schedulers                          | 64     |

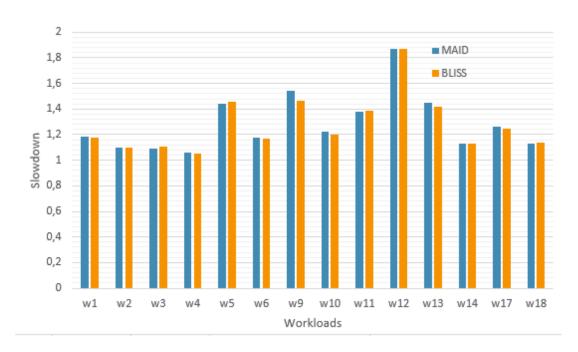

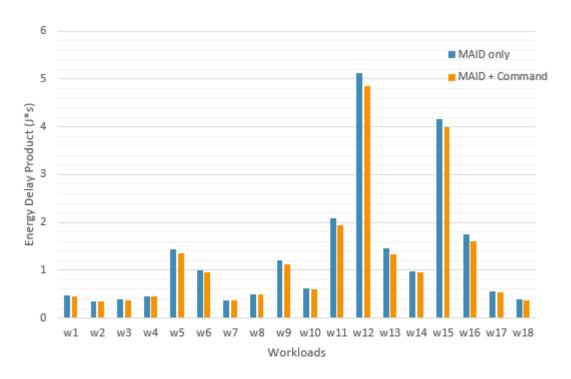

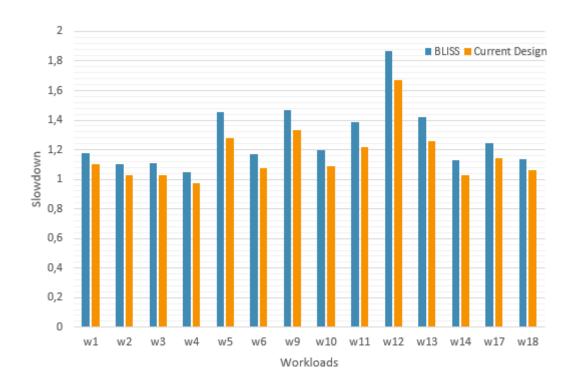

| Figure 5.3 Slowdown of workloads with MAID and BLISS algorithms                |

|--------------------------------------------------------------------------------|

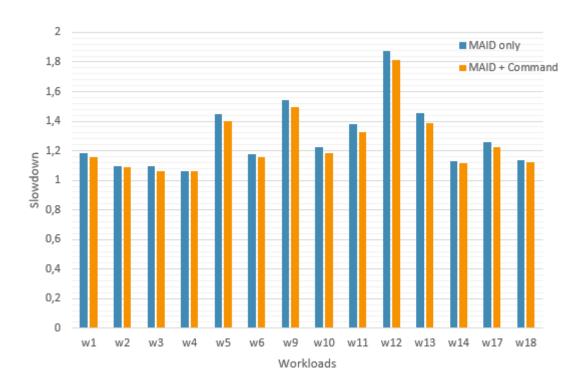

| Figure 5.4 Sum of Execution Times vs workloads reflecting Command Scheduling   |

| Effect                                                                         |

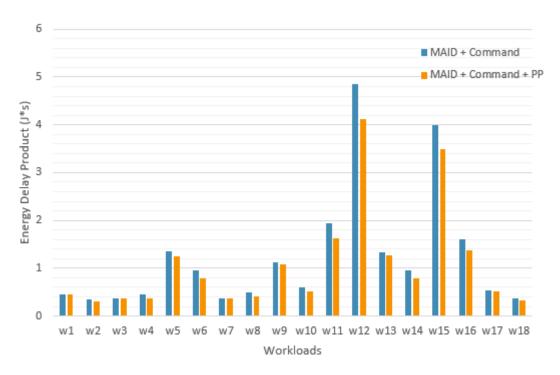

| Figure 5.5 EDP vs workloads showing Command Scheduling Effect                  |

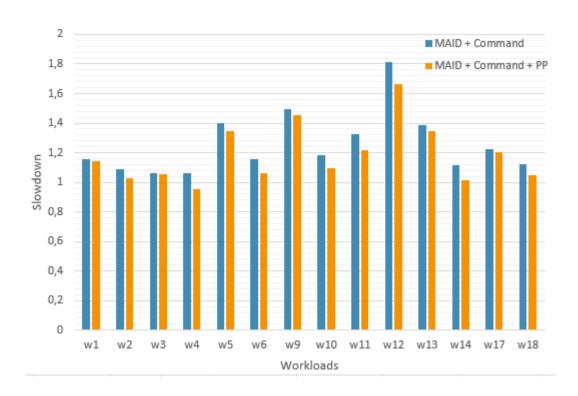

| Figure 5.6 Slowdown of workloads with Command Scheduling Policy 68             |

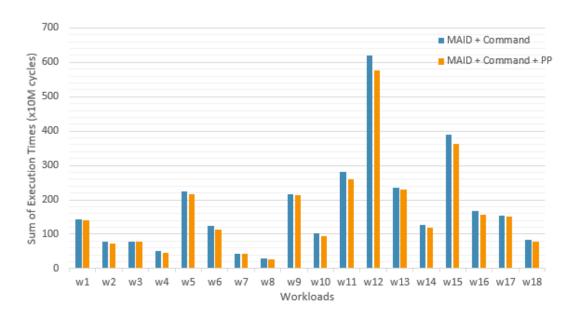

| Figure 5.7 Sum of Execution Times vs workloads with Dynamic Page-Policy effect |

| 69                                                                             |

| Figure 5.8 EDP vs workloads showing Dynamic Page-Policy Effect                 |

| Figure 5.9 Slowdown of workloads with Dynamic Page-Policy                      |

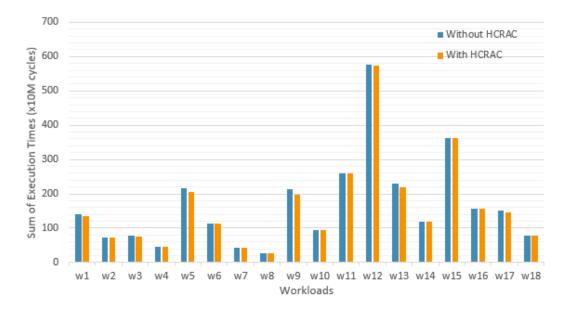

| Figure 5.10 Sum of Execution Times vs workloads with HCRAC effect 71           |

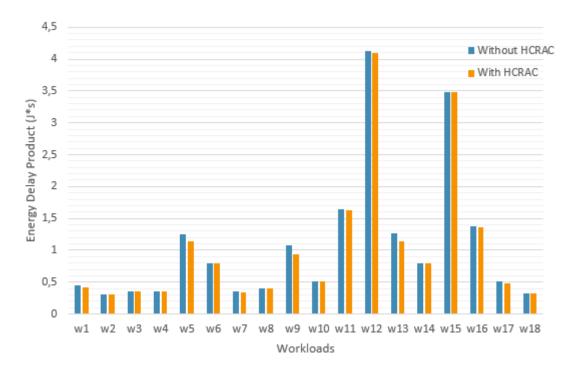

| Figure 5.11 EDP vs workloads showing HCRAC Effect                              |

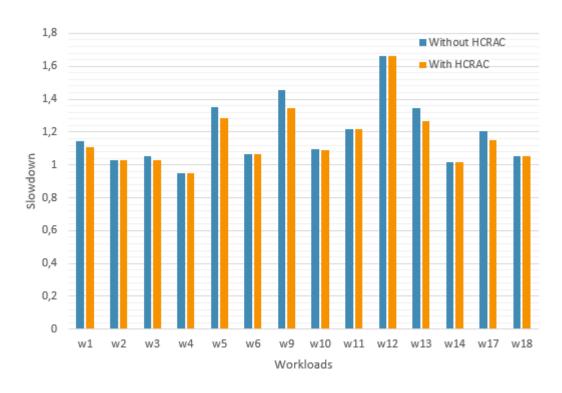

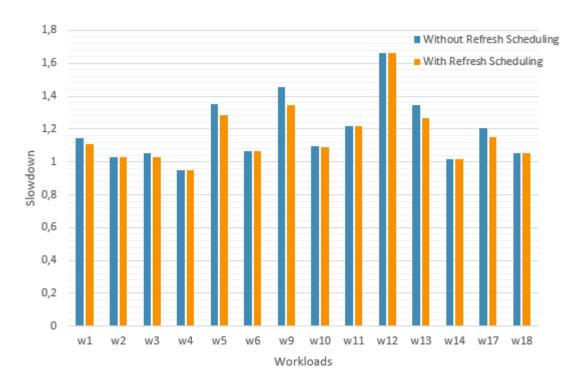

| Figure 5.12 Slowdown of workloads with HCRAC                                   |

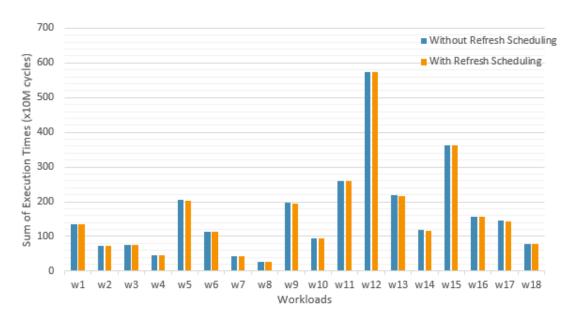

| Figure 5.13 Sum of Execution Times vs workloads with Refresh Scheduling Effect |

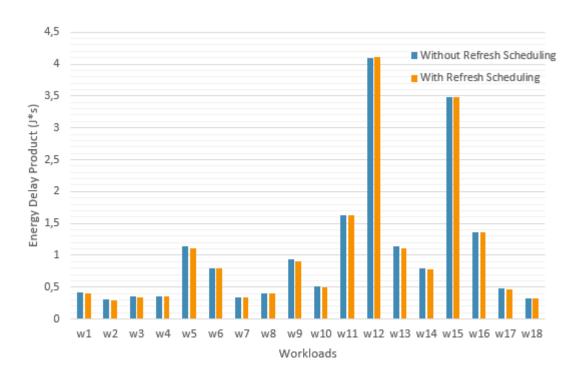

|                                                                                |

| Figure 5.14 EDP vs workloads showing Refresh Scheduling Effect                 |

| Figure 5.15 Slowdown of workloads with Refresh Scheduling                      |

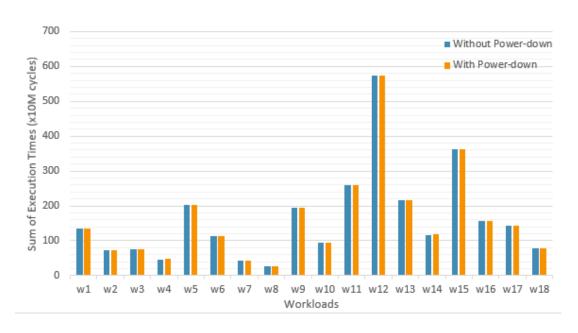

| Figure 5.16 Sum of Execution Times vs workloads with Power-down usage Effect77 |

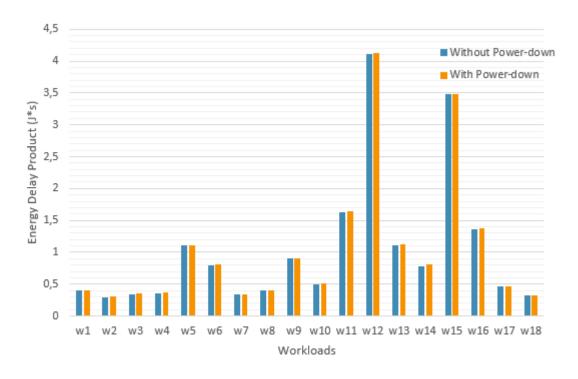

| Figure 5.17 EDP vs workloads showing Power-down usage Effect                   |

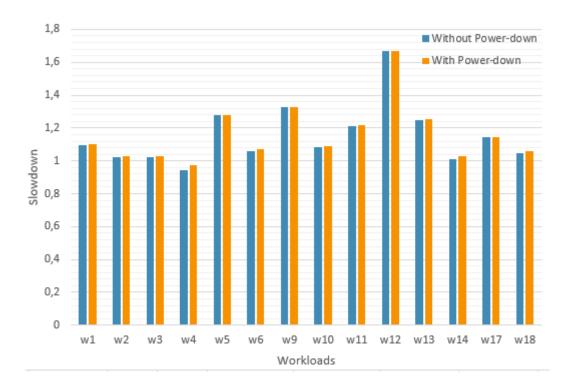

| Figure 5.18 Slowdown of workloads with Power-down                              |

| Figure 5.19 Memory System Power vs Workloads with Power-down usage 79          |

| Figure 5.20 Sum of Execution Times vs Workloads for BLISS and Current Design80 |

| Figure 5.21 Energy Delay Product vs Workloads for BLISS and Current Design 81  |

| Figure 5.22 Slowdown vs Workloads for BLISS and Current Design                 |

## LIST OF ABBREVIATIONS

AAMS Application-Aware Memory Scheduling

AL-DRAM Adaptive Latency DRAM

AR Auto-Refresh

AVATAR A Variable Retention-Time Aware Refresh

BLISS Blacklisting Scheduler

BWLOCK Bandwidth Lock

CKE Clock enable

COTS Commercial Off-The-Shelf

CPU Central Processing Unit

DDR Double Data Rate

DIMM Dual In-Line Memory Module

DRAM Dynamic Random-Access Memory

DTail A Flexible Approach to DRAM Refresh Management

FR-FCFS First-Ready First Come First Serve

IPC Instructions Per Cycle

JEDEC Joint Electron Device Engineering Council

LAMS A Latency-Aware Memory Scheduling Policy

LLC Last-Level Cache

LPDDR Low-Power Double Data Rate

MC Memory Controller

MEDUSA A Predictable and High-Performance DRAM Controller

MSC Memory Scheduling Championship

NUAT A Non-Uniform Access Time Memory Controller

PALLOC DRAM Bank-aware Memory Allocator

PARSEC Princeton Application Repository for Shared-Memory Computers

RAMS DRAM Rank-Aware Memory Scheduling

RBPP A Row-based DRAM Page Policy

ROB Reorder Buffer

SDRAM Synchronous Dynamic Random-Access Memory

SECDED Single-Bit Error Correction and Double-Bit Error Detection

SR Self-Refresh

SRAM Static Random-Access Memory

TCM Thread Cluster Memory Scheduling

USIMM Utah Simulated Memory Module

#### CHAPTER 1

## INTRODUCTION

#### 1.1. Overview

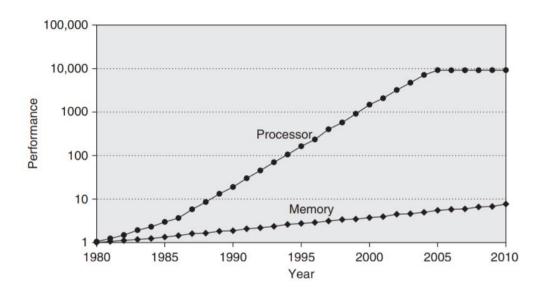

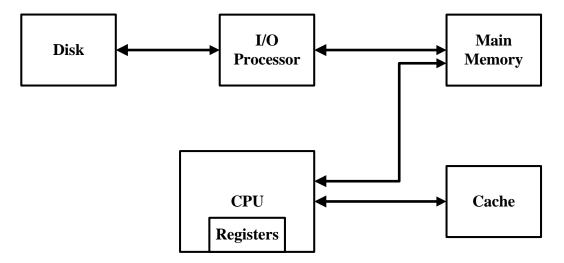

Memory has always been a crucial part of computing systems. In order to handle different needs, a memory hierarchy is built based on speed and cost requirements. While caches are used for faster movement of data to the CPU with limited capacity because of its large area requirement and high-cost, disks on the other hand can provide low-cost non-volatile storage at the expense of very slow operation speed. Other than these two choices, main memory provides a balance between operation speed and cost. Recent developments have been shaping the requirements for memory systems. One might think that cloud-data centers seem to need huge amount of memory, not only data centers but also autonomous cars and several technologies using artificial intelligence need a considerable sized memory. Even smartphones and personal computers can process heavy workloads for virtual and augmented reality which implies that efficient memory and processing speed should be granted for many systems. While computing systems' CPU speed continues to increase in a satisfactory fashion, and the parallel operation for faster execution has become a major issue, the main memory has been and will seemingly be the bottleneck for the future systems. This bottleneck is also known as the "Memory Wall" [1]. It is a phenomenon indicating that no matter how fast CPUs can operate, they will be bounded by how fast they can obtain data from the main memory. The above-mentioned problem is depicted in Figure 1.1.

Figure 1.1. Processor vs Memory performance improvement over the years [40]

Besides the insufficient core speed of main memory with respect to CPU, current systems use mostly chip-multiprocessors which treat main memory as a shared resource. The requestors try to issue memory requests in an aggressive manner while memory channel capacity is limited. Because of this limitation, applications interfere at the main memory resulting in longer execution times and more power consumption.

While choosing the main memory there are different expectations such as performance predictability, higher bandwidth and energy efficiency. Among different choices for the main memory, DDRx SDRAM (Double Data Rate Synchronous Dynamic Random-Access Memory) is the most prominent one. It has relatively low latency, high density and low cost. Other than generic main-memory specific problems, DRAM has additional drawbacks as follows:

- Since it is a volatile memory type, it needs refresh operations that incur extra latency and power consumption.

- Regardless of the generation (DDR3, DDR4, etc.) it has a variety of complex timing constraints that should be met in order to perform correct operation.

- DRAMs can be damaged by malicious attacks.

- Some additional error-correction mechanisms should be integrated to make DRAM more reliable and adding these mechanisms comes with hardwaresoftware cost.

- The power-down modes should be handled carefully to provide a balance between performance and energy.

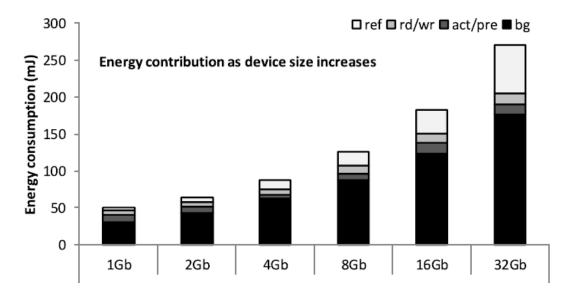

With every new generation DRAM standard, the drawbacks might get worse. Since device density increases, the latency and power consumption start to have significant effect during memory operations. Two important negative effects are illustrated in Figures 1.2 and 1.3.

Figure 1.2 Refresh effect on energy consumption vs device density [41]

As can be seen in the above figure, refresh effect on energy consumption increases drastically as DRAM size increases since more energy is consumed to refresh increasing number of rows in DRAM. Whereas, read/write/activate/precharge commands and background power continue to have relatively the same share in the overall energy consumption.

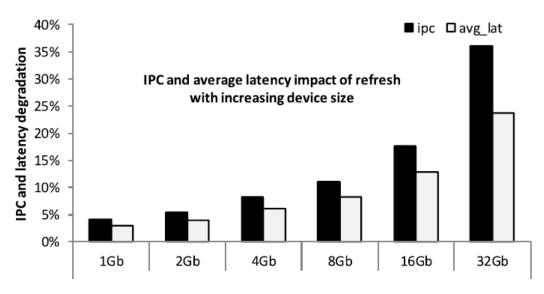

Figure 1.3 Refresh effect on IPC (Instruction Per Cycle) and average latency vs device density [41]

Second important effect of refresh is depicted in Figure 1.3. Refreshing more rows means much more time is spent for refresh operations resulting in essential operations of DRAM (read/write) to wait more since refresh is mostly uninterruptable and stalls the device.

Another important drawback of DRAMs is its security. Besides what was known, in the last couple of years DRAMs were discovered to be extremely vulnerable to malicious attacks. As first mentioned in [2] there exists a possibility of harming DRAMs that can be done just by reading from the exact same address exhaustively. This exhaustive readings from the same address physically harms the nearby rows by corrupting their content. In [2], the authors pointed out that they were able to induce errors in most DRAM modules (110 out of 129) from three manufacturers.

Researchers continue to seek for solutions to mitigate the effect of drawbacks, however DRAM market is a cost-sensitive one and advancements cannot be realized in a short time. However, there is another possible area of improvement for memory systems containing DRAM. There exists a component called "Memory Controller" (MC) for every memory system. In current computing systems, I/O devices and processors can target the data in the memory sub-system via using one