# $\mathbb{C}^3$ : CONFIGURABLE CAN FD CONTROLLER: DESIGN, IMPLEMENTATION AND EVALUATION

# A THESIS SUBMITTED TO THE GRADUATE SCHOOL OF NATURAL AND APPLIED SCIENCES OF MIDDLE EAST TECHNICAL UNIVERSITY

BY

MEHMET ERTUĞ AFŞİN

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS

FOR

THE DEGREE OF MASTER OF SCIENCE

IN

ELECTRICAL AND ELECTRONICS ENGINEERING

FEBRUARY 2018

# Approval of the thesis:

# ${\cal C}^3$ : CONFIGURABLE CAN FD CONTROLLER: DESIGN, IMPLEMENTATION AND EVALUATION

submitted by **MEHMET ERTUĞ AFŞİN** in partial fulfillment of the requirements for the degree of **Master of Science in Electrical and Electronics Engineering Department, Middle East Technical University** by,

| Prof. Dr. Gülbin Dural Ünver                                                                               |  |

|------------------------------------------------------------------------------------------------------------|--|

| Dean, Graduate School of Natural and Applied Sciences                                                      |  |

| Prof. Dr. Tolga Çiloğlu<br>Head of Department, <b>Electrical and Electronics Engineering</b>               |  |

| Prof. Dr. Şenan Ece Güran Schmidt<br>Supervisor, <b>Electrical and Electronics Eng. Dept., METU</b>        |  |

| Assoc. Prof. Dr. Klaus Werner Schmidt<br>Co-supervisor, <b>Electrical and Electronics Eng. Dept., METU</b> |  |

| Examining Committee Members:                                                                               |  |

| Prof. Dr. Gözde Bozdağı Akar<br>Electrical and Electronics Engineering Department, METU                    |  |

| Prof. Dr. Şenan Ece Güran Schmidt<br>Electrical and Electronics Engineering Department, METU               |  |

| Assoc. Prof. Dr. Cüneyt F. Bazlamaçcı<br>Electrical and Electronics Engineering Department, METU           |  |

| Prof. Dr. İlkay Ulusoy<br>Electrical and Electronics Engineering Department, METU                          |  |

| Assoc. Prof. Dr. Orhan Gazi<br>Electronic and Communication Eng. Dept., Çankaya University                 |  |

Date:

**February 7, 2018**

| I hereby declare that all information presented in accordance with academ     | nic rules and e | ethical conduct. I also | o declare |

|-------------------------------------------------------------------------------|-----------------|-------------------------|-----------|

| that, as required by these rules and comaterial and results that are not orig |                 |                         | enced all |

|                                                                               |                 |                         |           |

| N                                                                             | T (N)           | MEUMET EDTUĞ            | A EGİNI   |

| Name                                                                          | e, Last Name:   | MEHMET ERTUĞ            | AFŞIN     |

| Signa                                                                         | ture :          |                         |           |

|                                                                               |                 |                         |           |

|                                                                               |                 |                         |           |

|                                                                               |                 |                         |           |

# **ABSTRACT**

# C<sup>3</sup>: CONFIGURABLE CAN FD CONTROLLER: DESIGN, IMPLEMENTATION AND EVALUATION

# AFŞİN, Mehmet Ertuğ

M.S., Department of Electrical and Electronics Engineering

Supervisor : Prof. Dr. Şenan Ece Güran Schmidt

Co-Supervisor : Assoc. Prof. Dr. Klaus Werner Schmidt

February 2018, 120 pages

CAN FD (Controller Area Network with Flexible Data Rate) is a new communication standard, compatible with CAN. Different from CAN, CAN FD switches to high data rate during data transmission and allows payloads up to 64 bytes. In this thesis, we propose  $C^3$ : Configurable CAN FD Controller which features up to fully configurable 96 TX and 96 RX buffers organized as mailboxes. Each RX buffer has dedicated acceptance filters. The host MCU sees  $C^3$  as a memory mapped device and interfaces with it via SPI protocol which is designed and developed in the scope of this thesis. Different from existing CAN FD Controllers,  $C^3$  provides run time configurable number of buffers and individual buffer sizes which makes it best use of a single hardware for every application. Furthermore, it provides efficient and flexible usage of a limited embedded memory.  $C^3$  is implemented on a Xilinx Virtex 5 FPGA demo board as an IP Core and its functions are verified at 2 Mbps and the response time measurements are performed to evaluate the timing performance.

Keywords: CAN, CAN FD , CAN FD Controller, FPGA, Buffer Organization

# ${\cal C}^3$ : AYARLANABİLİR CAN FD KONTROLCÜSÜ: TASARIM, GERÇEKLEŞTİRİM VE DEĞERLENDİRME

# AFŞİN, Mehmet Ertuğ

Yüksek Lisans, Elektrik ve Elektronik Mühendisliği Bölümü

Tez Yöneticisi : Prof. Dr. Şenan Ece Güran Schmidt

Ortak Tez Yöneticisi : Doç. Dr. Klaus Werner Schmidt

Şubat 2018, 120 sayfa

CAN FD, CAN ile uyumlu yeni bir haberleşme protokolüdür. CAN protokolünden farklı olarak, CAN FD veri gönderim fazında yüksek hıza çıkmakta olup, 64 bayta kadar faydalı yük taşıyabilmektedir. Bu tez kapsamında posta kutusu formatında ayarlanabilir boyutlarda 96 adede kadar gönderici ve 96 adede kadar alıcı ara belleğine sahip  $C^3$ : Ayarlanabilir CAN FD kontrolcüsü sunulmaktadır. Her bir alıcı arabelleği için mesaj tanımlama filtresi bulunmaktadır. Kullanıcı mikro denetleyici,  $C^3$ 'ü hafıza haritalı bir cihaz olarak görmektedir ve SPI haberleşme protokolü ile  $C^3$ 'e erişmektedir. Bu tez kapsamında mikro denetleyici ve  $C^3$  arasındaki SPI protokolü de tasarlanmıştır. Mevcut CAN FD kontrolcülerinden farklı olarak  $C^3$  uygulama zamanında ayarlanabilir sayıda arabellek ve ayarlanabilir boyutlarda arabellek yapısı sunmaktadır. Bu esneklik sayesinde tek bir kontrolcü tüm uygulamalar için kullanılabilmektedir. Ayrıca kısıtlı olan gömülü hafızadan en verimli şekilde faydalanılmaktadır.  $C^3$ , Xilinx firmasının Virtex 5 FPGA geliştirme kartında IP çekirdeği olarak gerçeklenmiştir.  $C^3$ 'ün tüm özellikleri 2 Mbps hızda doğrulanmış olup tepki süreleri de ölçülerek zamanlama performansı değerlendirilmiştir.

Anahtar Kelimeler: CAN, CAN FD, CAN FD Kontrolcüsü, FPGA, Ara Bellek Organizasyonu

To My Family

## **ACKNOWLEDGMENTS**

I would like to express my great appreciations to my supervisor Prof. Dr. Şenan Ece Güran Schmidt and co-supervisor Assoc. Prof. Dr. Klaus Werner Schmidt for their support and guidance throughout this thesis. I am thankful for their guidance, which was very helpful in my research and writing of the thesis.

I wish to thank ASELSAN A.Ş. for giving me the opportunity of continuing my education and providing financial support for my conference attendances. I wish to thank my colleagues and seniors in the hardware design department. This thesis work was supported by the Middle East Technical University as a Scientific Research Project with contract number of BAP-03-01-2017-002. I would like to thank Empa Electronics for their donated transceiver components.

I would like to express my special appreciation to Onur Aktop for his contributions to improve my engineering skills. I would like to express special thanks to my family. Finally, I would like to express my appreciation to my friend, Mehmet Ufuk Büyükşahin. During thesis work, he helped me in every matter and he didn't leave me alone.

# TABLE OF CONTENTS

| ABSTR  | ACT                |                                                  |

|--------|--------------------|--------------------------------------------------|

| ÖZ     |                    |                                                  |

| ACKNO  | )WLEDO             | GMENTS                                           |

| TABLE  | OF CON             | ITENTS xi                                        |

| LIST O | F TABLE            | ES xiii                                          |

| LIST O | F FIGUR            | ES xiv                                           |

| LIST O | F ABBRI            | EVIATIONS                                        |

| СНАРТ  | ERS                |                                                  |

| 1      | INTRO              | DUCTION                                          |

| 2      | IN-VEI             | HICLE NETWORKS                                   |

|        | 2.1                | CAN                                              |

|        | 2.2                | CAN FD                                           |

|        | 2.3                | CAN/CAN FD Controllers                           |

| 3      | PREVI              | OUS WORK ON CAN/CAN FD CONTROLLERS 15            |

| 4      | $\mathrm{C}^3$ (CC | ONFIGURABLE CAN FD CONTROLLER) ARCHITECTURE 23   |

|        | 4.1                | Hardware Blocks: Memory Mapped Register Block 25 |

|        | 4.2                | Hardware Blocks: SPI Protocol Control Block      |

|        | 4.3                | Hardware Blocks: Interrupt Control Block         |

|       | 4.4   | Hardware Blocks: Transmitter Module                          |

|-------|-------|--------------------------------------------------------------|

|       | 4.5   | Hardware Blocks: Receiver Module                             |

|       | 4.6   | Configuration Phase                                          |

|       | 4.7   | Data Phase and Timing                                        |

|       | 4.8   | FPGA Implementation Results                                  |

| 5     | EVAL  | UATION OF $\mathbb{C}^3$ (CONFIGURABLE CAN FD CONTROLLER) 61 |

|       | 5.1   | Development and Test Environment 61                          |

|       | 5.2   | Host Simulator Implementation                                |

|       | 5.3   | Transmit Buffer Configuration and Transmission Tests 74      |

|       | 5.4   | Receive Buffer Configuration and Reception Tests 80          |

|       | 5.5   | Response Time Measurements                                   |

|       | 5.6   | Interrupt and Error Tests                                    |

|       | 5.7   | Arbitration and Other Tests                                  |

| 6     | CONC  | CLUSION                                                      |

| REFER | ENCES |                                                              |

# LIST OF TABLES

# **TABLES**

| Table 3.1 | CAN FD Controllers Comparison 1         | 9  |

|-----------|-----------------------------------------|----|

| Table 3.2 | CAN FD Controllers Comparison 2         | 20 |

| Table 3.3 | CAN FD Controllers Comparison 3         | 21 |

| Table 4.1 | Configuration Registers                 | 29 |

| Table 4.2 | SPI Commands and Responses              | 34 |

| Table 4.3 | Interrupt Register Set                  | 37 |

| Table 4.4 | TX Control Register Set                 | 39 |

| Table 4.5 | RX Control Register Set                 | 14 |

| Table 4.6 | TX(ID) Register Set                     | 18 |

| Table 4.7 | RX(ID) Register Set                     | 19 |

| Table 4.8 | FPGA Device Utilization Summary         | ;3 |

| Table 4.9 | FPGA Project Status                     | 54 |

| Table 5.1 | Xilinx Virtex 5 FPGA Familiy Comparison | 53 |

# LIST OF FIGURES

# **FIGURES**

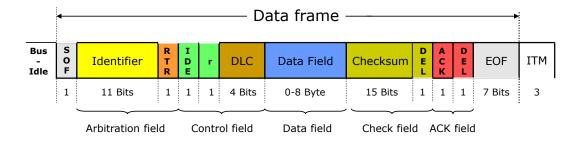

| Figure 2.1  | CAN Base Frame                                              | 7  |

|-------------|-------------------------------------------------------------|----|

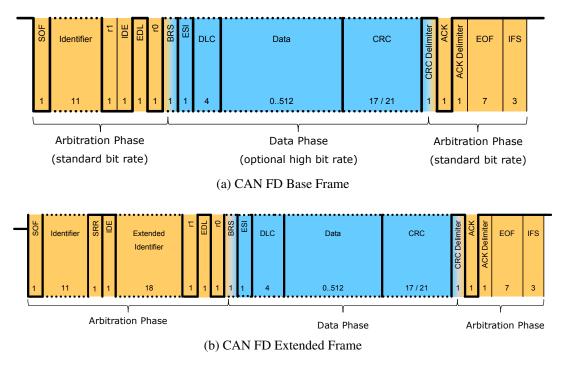

| Figure 2.2  | CAN FD Frames                                               | 10 |

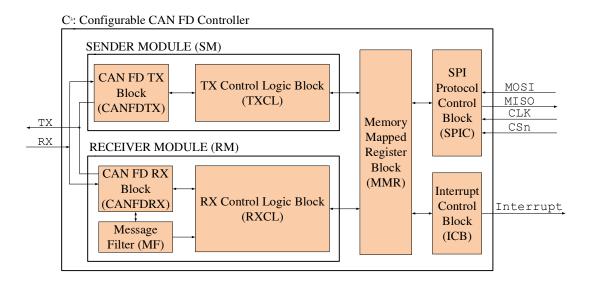

| Figure 4.1  | $C^3$ Architecture                                          | 23 |

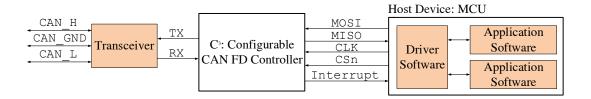

| Figure 4.2  | Top Level Architecture                                      | 24 |

| Figure 4.3  | Memory Mapped Register Block (MMR)                          | 26 |

| Figure 4.4  | Example Memory organizations: (a) 88 buffers (b) 44 buffers | 30 |

| Figure 4.5  | SPI Protocol Control Block                                  | 31 |

| Figure 4.6  | SPI Timing Diagrams                                         | 33 |

| Figure 4.7  | Interrupt Control Block                                     | 35 |

| Figure 4.8  | TX Control Logic Block (TXCL)                               | 38 |

| Figure 4.9  | Binary Search Algorithm                                     | 40 |

| Figure 4.10 | CAN FD Transmitter Block (CANFDTX)                          | 41 |

| Figure 4.11 | RX Control Logic Block (RXCL)                               | 42 |

| Figure 4.12 | CAN FD Receiver-RX Block (CANFDRX)                          | 45 |

| Figure 4.13 | Message Filter Block (MF)                                   | 46 |

| Figure 4.14 | FPGA Project Hierarchy                                      | 55 |

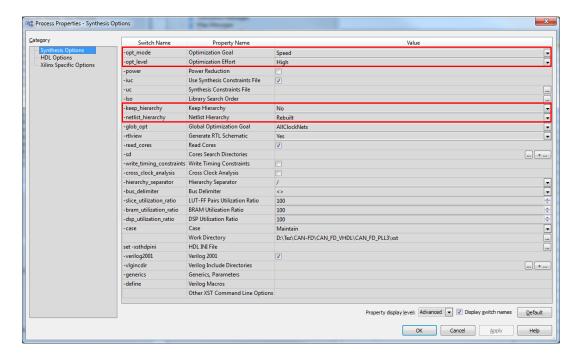

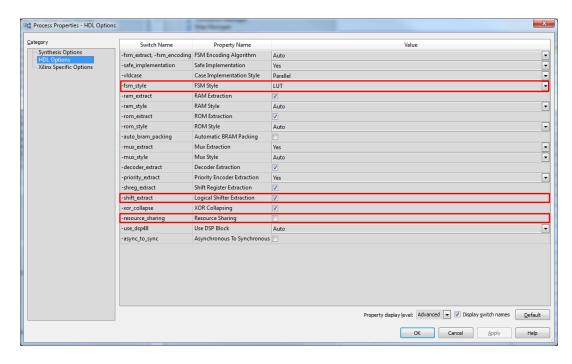

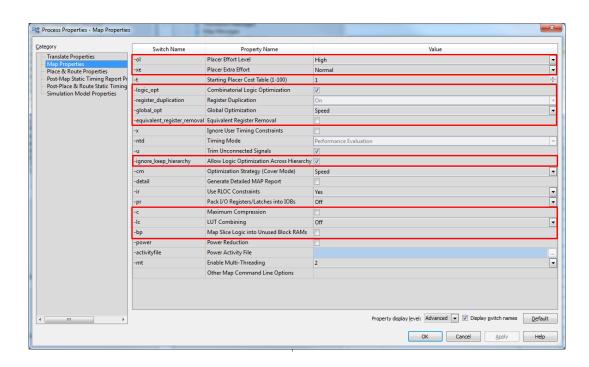

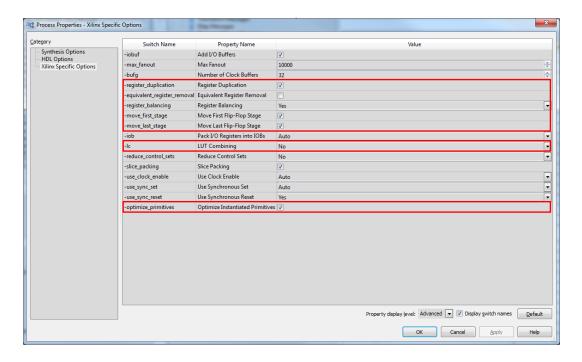

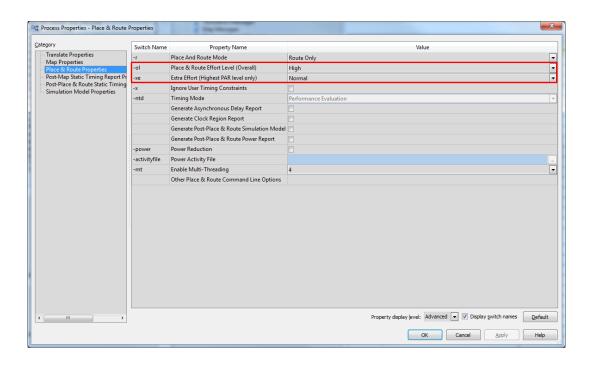

| Figure 4.15 FPGA Implementation Options 1                                      | 56         |

|--------------------------------------------------------------------------------|------------|

| Figure 4.16 FPGA Implementation Options 2                                      | 57         |

| Figure 4.17 FPGA Implementation Options 3                                      | 57         |

| Figure 4.18 FPGA Implementation Options 4                                      | 58         |

| Figure 4.19 FPGA Implementation Options 5                                      | 58         |

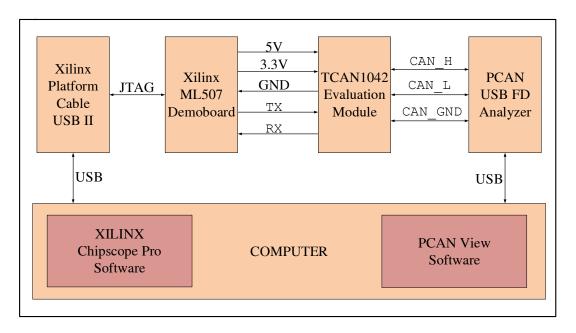

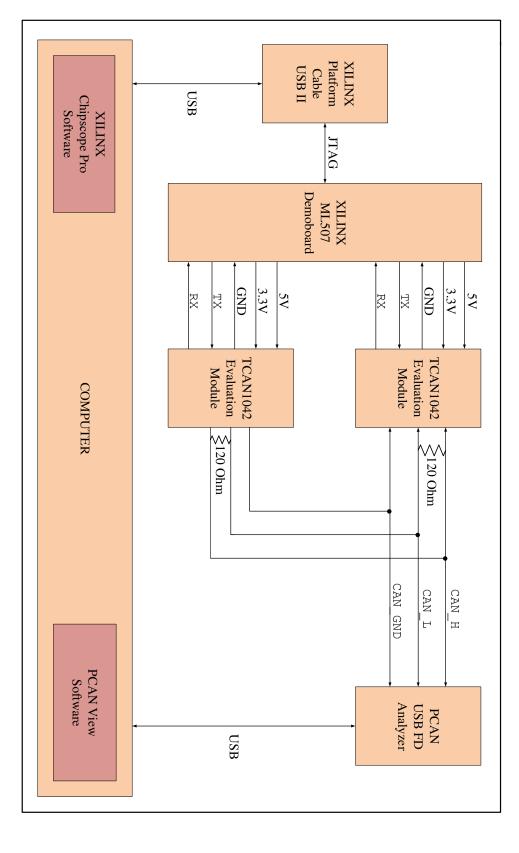

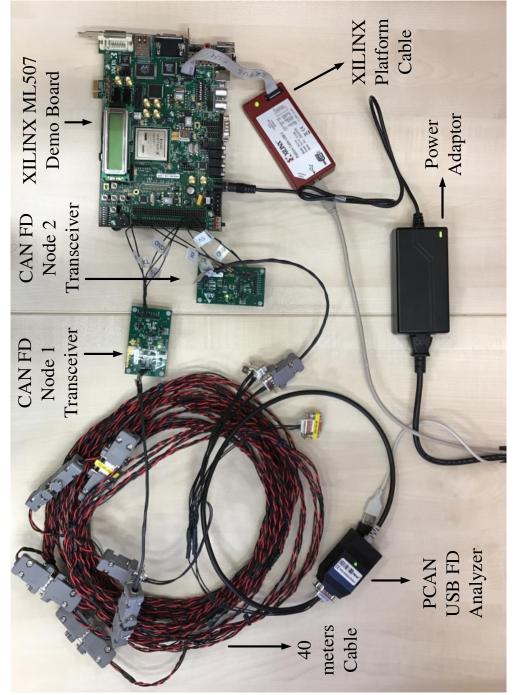

| Figure 5.1 Test Setup Block Diagram                                            | 51         |

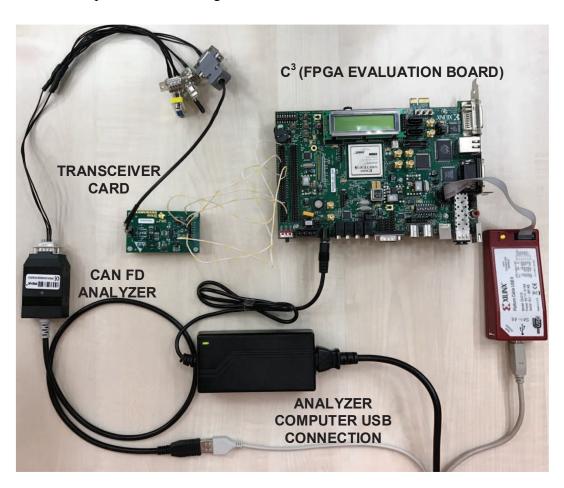

| Figure 5.2 Test Setup                                                          | 52         |

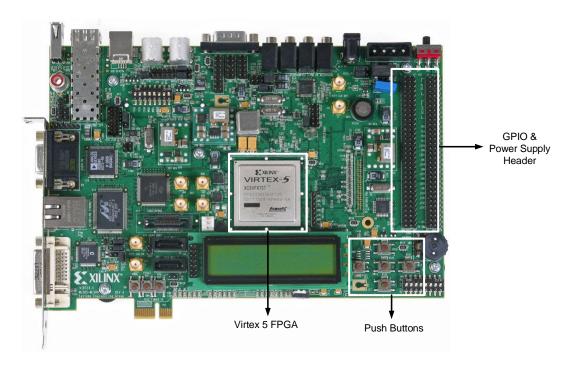

| Figure 5.3 Xilinx ML507 Demoboard                                              | 53         |

| Figure 5.4 CAN FD Transceiver Internal[31]                                     | 54         |

| Figure 5.5 Tranceiver Signals                                                  | 55         |

| Figure 5.6 CAN FD Transceiver Board                                            | 55         |

| Figure 5.7 PCAN USB FD Hardware                                                | 56         |

| Figure 5.8 Xilinx Platform Cable                                               | 57         |

| Figure 5.9 FPGA Implementation Block Diagram                                   | 57         |

| Figure 5.10 Host Simulator Block Diagram                                       | 59         |

| Figure 5.11 SPI Read Operation                                                 | <b>7</b> C |

| Figure 5.12 SPI Burst Read Operation                                           | 71         |

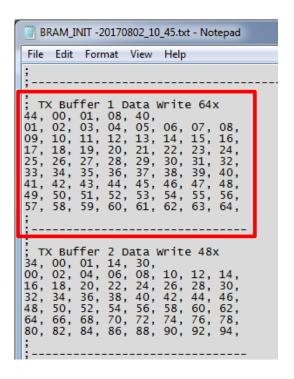

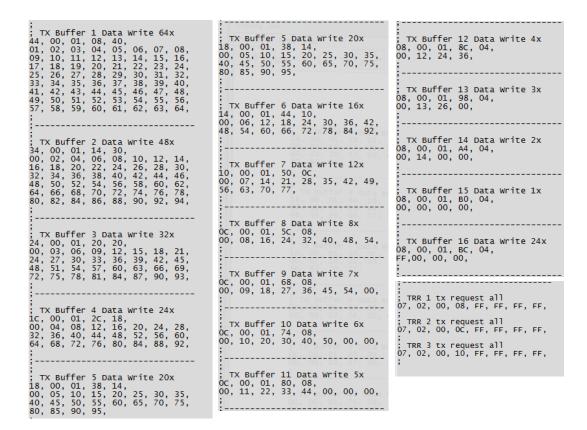

| Figure 5.13 Initialization Block Ram Data Content for 32 Bit SPI Write Command | 71         |

| Figure 5.14 Initialization Block Ram Data Content for 32 Bit SPI Read Command  | 72         |

| Figure 5.15 Initialization Block Ram Data Content for Burst SPI Write Command  | 73         |

| Figure 5.16 Initialization Block Ram Data Content for Burst SPI Read Command   | 74         |

| Figure 5.17 First 16 Buffers Configuration                         | /// |

|--------------------------------------------------------------------|-----|

| Figure 5.18 First 16 Buffers Transmission Data Content and Request | 78  |

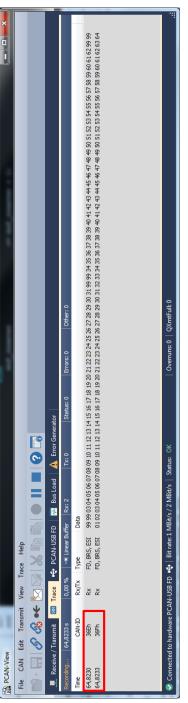

| Figure 5.19 PCAN Data Logging for First 16 Transmissions           | 79  |

| Figure 5.20 Transmission Requests for Priority Test                | 80  |

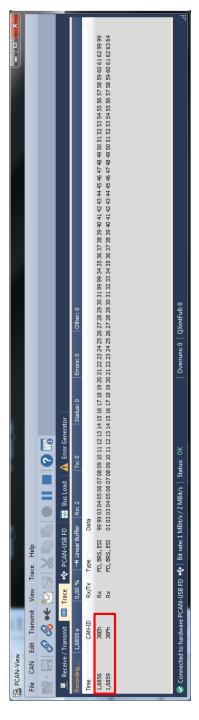

| Figure 5.21 PCAN Message Reception for Transmission Priority Test  | 81  |

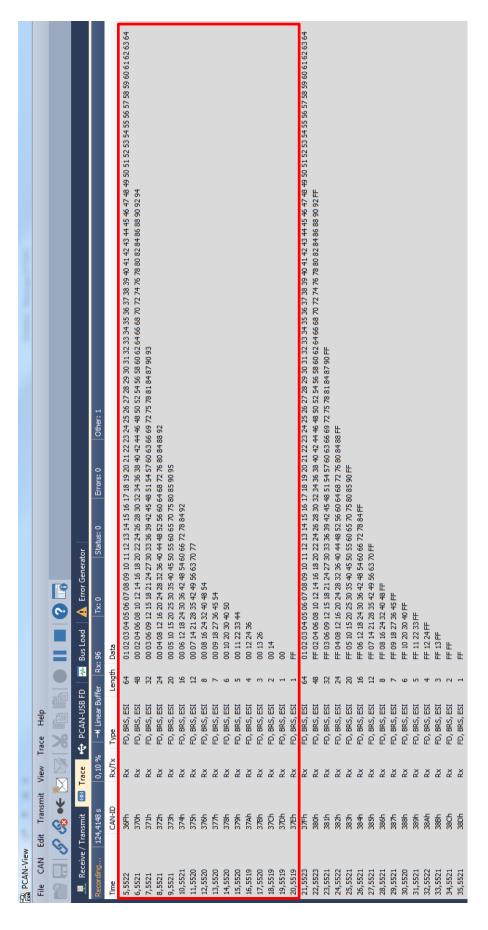

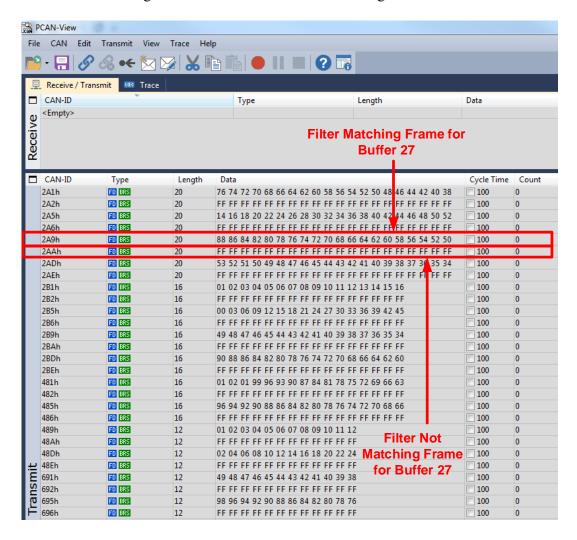

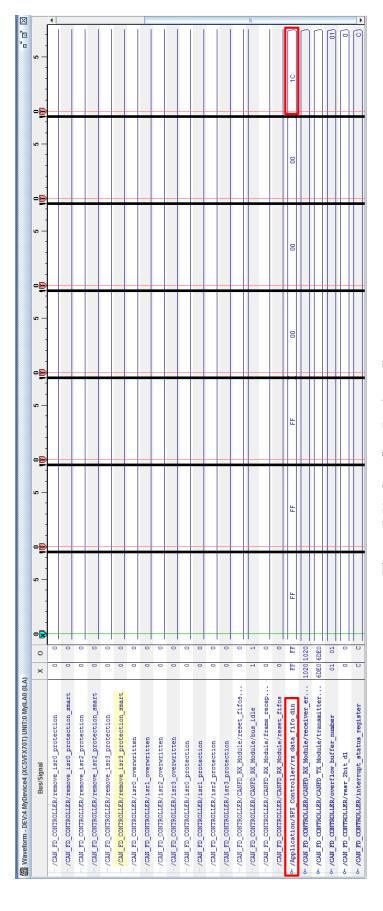

| Figure 5.22 Message Content for Buffer 27                          | 84  |

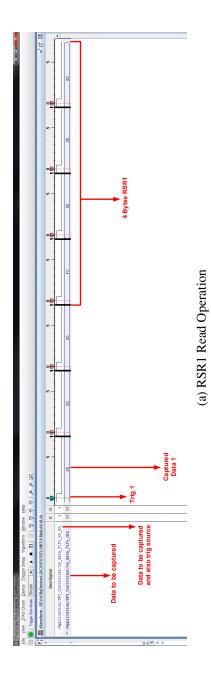

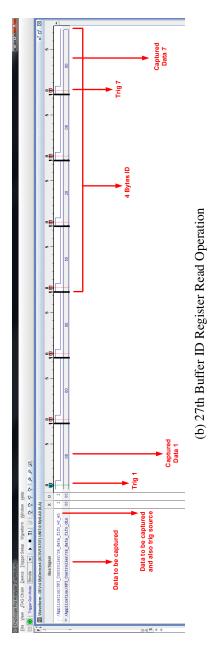

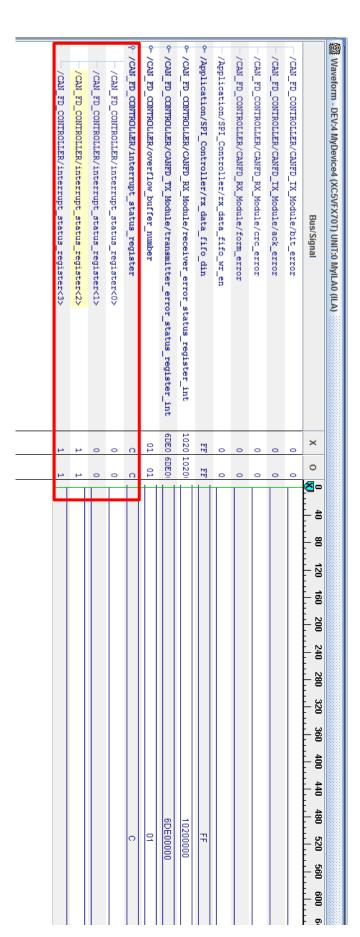

| Figure 5.23 Buffer 27 Read Operations 1                            | 86  |

| Figure 5.24 Buffer 27 Read Operations 2                            | 87  |

| Figure 5.25 TX Response Time Measurements 1                        | 89  |

| Figure 5.26 TX Response Time Measurements 2                        | 90  |

| Figure 5.27 FPGA Core Delay                                        | 92  |

| Figure 5.28 ISR Read Delay                                         | 93  |

| Figure 5.29 3x RSR Read Delay                                      | 93  |

| Figure 5.30 Burst SPI Read Delay                                   | 93  |

| Figure 5.31 RSR Clear Delay                                        | 94  |

| Figure 5.32 ISR Clear Delay                                        | 94  |

| Figure 5.33 Total Receive Response Time                            | 94  |

| Figure 5.34 Interrupt Generation                                   | 95  |

| Figure 5.35 ISR Read Operation                                     | 96  |

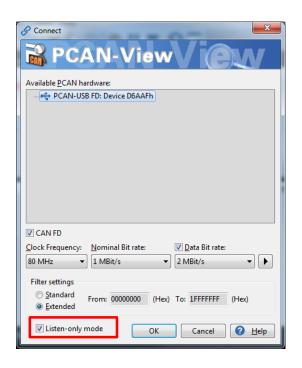

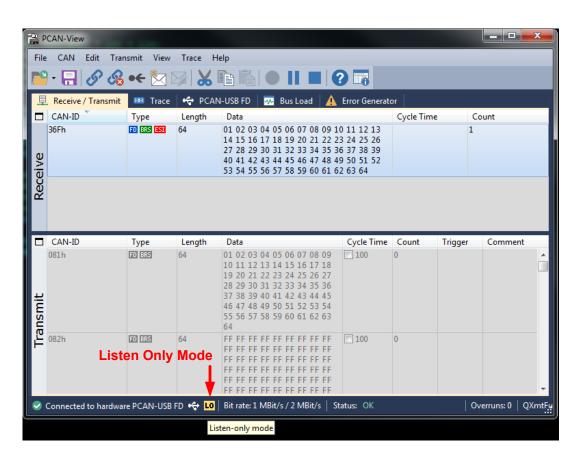

| Figure 5.36 PCAN Listen Only Mode Settings 1                       | 97  |

| Figure 5.37 PCAN Listen Only Mode Settings 2                       | 97  |

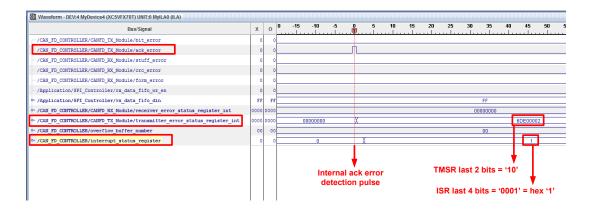

| Figure 5.38 TX Ack Error Register Content                          | 98  |

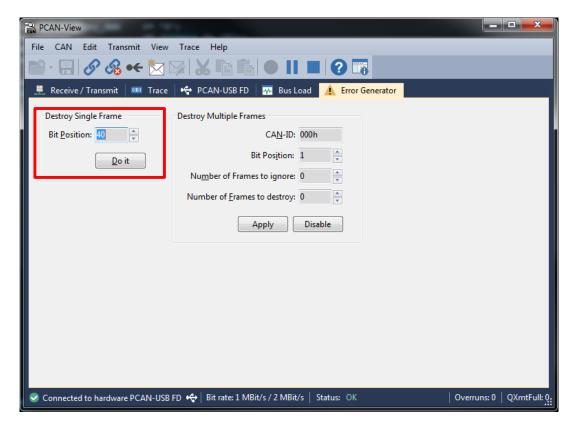

| Figure 5.39 PCAN Error Generator                 |

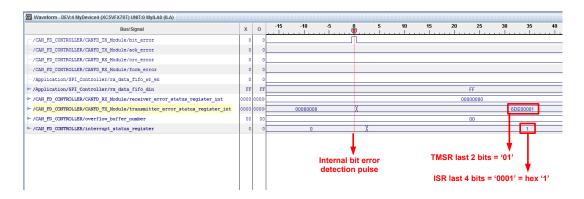

|--------------------------------------------------|

| Figure 5.40 Bit Error Register Content           |

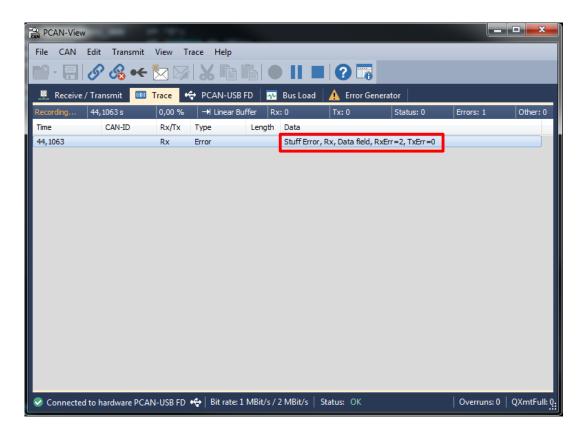

| Figure 5.41 PCAN Error Log                       |

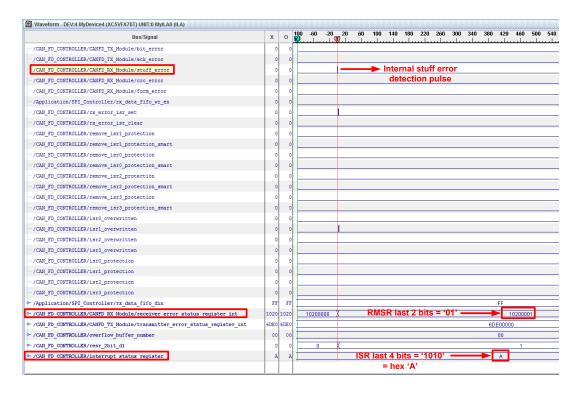

| Figure 5.42 RX Stuff Error Register Content      |

| Figure 5.43 PCAN Error Log                       |

| Figure 5.44 RX CRC Error Register Content        |

| Figure 5.45 Form Error Register Content          |

| Figure 5.46 PCAN Form Error Log                  |

| Figure 5.47 Arbitration Test Setup Block Diagram |

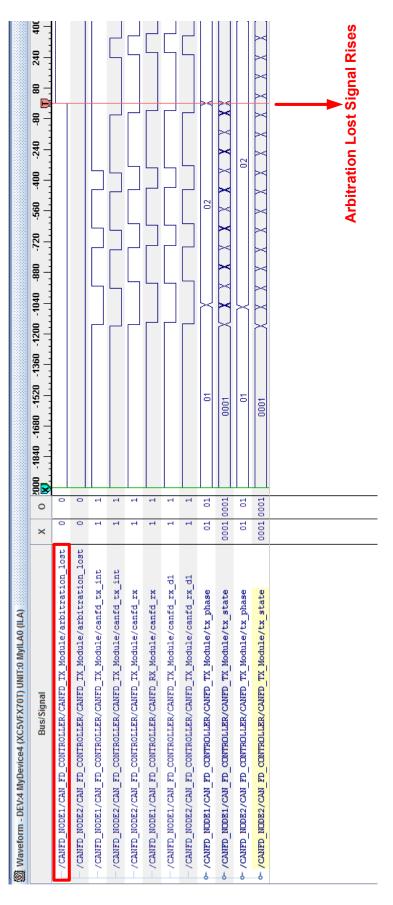

| Figure 5.48 Arbitration Loss                     |

| Figure 5.49 Message Reception Orders             |

| Figure 5.50 Arbitration Setup                    |

| Figure 5.51 Overflow Register Content            |

| Figure 5 52 Overflow ISR Read Operation 110      |

# LIST OF ABBREVIATIONS

SOF Start of Frame

RTR Remote Transmission Request

IDE Identifier ExtensionDLC Data Length CodeACK Acknowledgement

EOF End of Frame

EDL Extended Data Length

BRS Bit Rate Switch

ESI Error State Indicator IFS Inter Frame Spacing

CAN Controller Area Network

CAN FD Controller Area Network Flexible Data

IP Core Intellectual Property Core

VHDL VHSIC Hardware Description Language

ID Identification

#### **CHAPTER 1**

## INTRODUCTION

CAN (Controller Area Networks) is the most widely used communication standard in vehicle networks. ECUs (Electronic Control Units) in the vehicles exchange signals in the form of messages in a CAN network [35]. Due to CAN Bus network topology, multiple ECUs are connected to each other on a single bus. The CAN Bus transmission rates are up to 1 Mbps. However, the practical data rate is much lower than 1 Mbps. The data rate is limited by the arbitration and acknowledgment mechanisms. During arbitration, for the simultaneous transmissions, each signal transmitted by the nodes must reach to each other on time such that bit overwrite mechanism works. During acknowledgment phase, the transmitter's signal must propagate to the the receiving nodes and the nodes' acknowledgment responses must reach to the transmitter in time.

The number of ECUs in vehicles, the number of messages hence the amount of information carried on CAN BUS increase significantly day by day. CAN BUS is becoming slow and inadequate. However due to wide usage of CAN BUS and automotive industry's exacting reliability requirements, it is not easy to start using a completely new communication protocol. For these reasons, Bosch came up with CAN FD (CAN with Flexible Data Rate) protocol [28] in 2011. On the one hand, CAN FD preserves the physical layer of CAN which determines the bus arbitration signaling. On the other hand, CAN FD increases the data rate by simply switching to a high transmission rate of up to 10 Mbps after the arbitration is over. Furthermore it enables transmitting longer payloads of up to 64 Bytes instead of the 8 Byte CAN payload.

Since CAN FD is a new protocol, ECU manufacturers' plan to integrate CAN FD to

their design is at initial stage. The CAN FD Controllers available on the market are implemented as IP Cores [6, 1, 9, 18, 5, 10, 4, 8, 20, 7] and being developed since 2015. These IP cores are commercially sold and not available for academic evaluation and analysis.

The worst-case response times (WCRTs) of messages on CAN/CAN FD are computed assuming that the messages are stored in infinite priority queues. However, in practice it is possible that higher priority messages that are released by the application may get blocked due to the non-availability of transmission buffers in a CAN controller [30]. Hence, the timing and the scheduling of CAN/CAN FD messages improve if the transmit and the receive buffer numbers and sizes are compatible with the messages. On the one hand, the number of messages, their sizes and their priorities depend on the applications that run on the ECUs. The variation in the message sizes is particularly significant for CAN FD with a maximum data size of 64 Bytes. On the other hand, the CAN controllers are embedded devices with hardware resource constraints which do not allow implementing the buffer configurations for all possible message sets.

The CAN FD IP cores currently present in the literature either offer completely fixed size buffer arrangement without configuration capability or allow limited buffer configuration with some constraints. Therefore, it is not possible to have a single buffer configuration which fits to every application. Different buffer configurations for different message sets lead to inefficient memory usage for the controllers without memory configuration capability.

In this thesis, we present a novel CAN FD Controller denoted as  $C^3$  (Configurable CAN FD Controller). It supports non-ISO CAN FD protocol specification. It is implemented as an FPGA IP Core. The interface between the controller and the host MCU is widely used communication protocol called SPI (Serial Peripheral Interface).

Different from existing CAN/CAN FD controllers,  $C^3$  enables the configuration of the transmit and receive buffers via SPI during run time before the main applications on the ECU start to run. Such configuration capability enables appropriate buffer configurations on each ECU in the vehicle according to the messages of the applications running that ECU. Furthermore, it makes it possible to reconfigure the buffers if new

applications with new messages are added to the vehicle. The standard SPI interface of  $C^3$  enables any micro controller to run the applications and use  $C^3$  without any specific interface requirements.

C³ features up to 96 transmit and 96 receive buffers which can be configured via SPI during the configuration phase before the main ECU application begins to run. The buffers are organized as mailboxes. This configuration capability ensures that controller's memory is efficiently allocated for different message sets used for any CAN network present in vehicles. Moreover, it is quite easy to add new messages to the existing message set in a CAN network by reconfiguring the controller's buffer allocation. The mailboxes are allocated an average payload size of 16 bytes instead of maximum payload size of 64 bytes. Because it is very unlikely that all the messages in a message set of a network application will require 64 bytes payload size. This yields 96x16 bytes memory consumption instead of 96x64 bytes hence less memory usage and more memory utilization. The usage of SPI interface makes the integration of the controller to the host MCUs easy since SPI is present in almost every MCU on the market including the low cost ones.

The first main contribution of this thesis is the detailed design of  $C^3$ . The design is described in detail with functional blocks including the SPI block where a custom communication protocol is designed over SPI. This custom protocol defines the communication between the controller and the MCU. The signaling between the blocks and how they exchange and process data are explained. The second main contribution of this thesis is the transmit and receive response time analysis. The delay components contributing the response time are measured individually and overall response time is evaluated.  $C^3$  is implemented on Xilinx Virtex 5 ML507 demo board and the commercial CAN FD transceivers are used for CAN FD physical layer implementation. The design is verified by performing functional tests by sending and receiving CAN FD messages at 2 Mbps using a professional CAN FD analyzer hardware tool.

The thesis organization is as follows: CAN, CAN FD and CAN/CAN FD Controller basics are covered in Chapter.2. Existing CAN/CAN FD Controllers are discussed in Chapter 3.  $C^3$  hardware blocks are presented with details including the SPI communication protocol in Chapter 4. This chapter explains FPGA Implementation details

and the challenges faced. Furthermore, data phase, configuration phase and timing analysis are covered. The experimental setup, hardware components used, testing methods, functional verifications and the response time performance measurements of  $C^3$  are provided in Chapter 5. Finally, this thesis is concluded and future work is outlined in Chapter 6.

#### **CHAPTER 2**

## **IN-VEHICLE NETWORKS**

The contemporary vehicles contain a large number of electronic units which are actuators, sensors and microprocessor based Electronic Control Units (ECU)s. These electronic components and the software running on the microprocessors enable implementing complex functions that improve the safety, comfort and the efficiency of the vehicle. To this end, electronic systems assist the driver to control the vehicle with the functionality related to the steering, traction (i.e., control of the driving torque) or braking including the anti lock braking system (ABS), electronic stability program (ESP), electric power steering (EPS), active suspensions, or engine control. Furthermore employing the vehicle electronics enable the near future technologies such as autonomous driving.

The ECUs run applications which rely on the information coming from the other electronic components in the vehicle. Great majority of these applications are real-time and require deadlines. In other words, in-vehicle networks connect the electronic components together and provide the communication between them by meeting the timing requirements.

The benefits of in vehicle networking can be listed as below:

- The size of the cabling is dramatically reduced and the number of input/output pins required at ECUs is less since the point to point connection is replaced by a bus structure

- Common information such as temperature sensors or speed data is shared with every ECU on the bus.

It is easy to apply a modification by a software change without changing the hardware. This gives great flexibility to the system designer. For a point to point connections without any networking topology, any added data communication function would introduce a new point to point connections and more input and output pins.

The most frequently used in-vehicle network standard is Controller Area Network (CAN). The focus of this thesis is CAN FD (CAN with Flexible Data Rate) network which is based on CAN. Further in-vehicle network standards include FlexRay, MOST and Ethernet [35].

## 2.1 CAN

CAN (Controller Area Network) is a serial asynchronous bus network. It connects electronic devices, various sensors and actuators in a system or sub-system for various applications. It is multi master communication protocol. The protocol is developed by Robert Bosch GmbH in 1986. It was designed for automotive applications requiring a reliable communication. The data rate is up to 1 Mbps. Apart from being used in automotive industry, CAN is also used in embedded applications and industrial control systems [16]. CAN (Controller Area Network) is a serial asynchronous bus network. It connects electronic devices, various sensors and actuators in a system or sub-system for various applications. It is multi master communication protocol. The protocol is developed by Robert Bosch GmbH in 1986. It was designed for automotive applications requiring a reliable communication. The data rate is up to 1 Mbps. Apart from being used in automotive industry, CAN is also used in embedded applications and industrial control systems [16].

The CAN protocol defines the physical layer and data link layer specifications. It defines how the frames are formed and how the arbitration mechanism works. CAN is basically an event triggered protocol, there is no time slot mechanism where the messages are supposed to be transmitted, instead, they are transmitted whenever the bus is idle. If two nodes begin transmission at the same time, the one with the ID having more priority takes over the bus and the other node stops transmitting and

Figure 2.1: CAN Base Frame

attempts to transmit its frame again when the current transmission is over. The priority is determined by the bit values, 0 is a dominant bit whereas 1 is a recessive bit. 0 overwrites 1 when they are transmitted simultaneously. To this end, the message with the smallest ID has the highest priority and always takes over the bus for simultaneous message transmissions [22].

There are two types of IDs, which are base and extended IDs. Base ID data frame is a CAN bus frame with 11 bit ID representation. On the other hand, extended ID data frame is a CAN bus frame with 29 bit ID representation. CAN Bus data frame for Base ID can be seen in Fig.2.1.

Error detection and management is very important for in vehicle networking. There is an acknowledgment mechanism in a CAN frame. Cyclic Redundancy Check (CRC) is performed at the end of the frame. CRC is computed beginning from the start bit of the frame both by the transmitter and the receiver nodes. The CRC computation result calculated by the receiving node must be the same as the one transmitter node places in the frame for a successful communication, otherwise error condition occurs. The nodes which receive a sent frame send a dominant acknowledgment bit to indicate that the frame is received successfully after CRC operation. Bit stuffing provides an additional bit when 5 consecutive same bits are transmitted. Additional bit value is the complement of the value of the previous 5 bits. Bit stuffing is used to ensure that bus does not stay at the same voltage level for a long time and node clocks can synchronize to the bus to have accurate bit sampling point. Lastly, bus monitoring is performed for any bit errors by the transmitter node to check if the transmitted bit value is really on the bus. With all these mechanisms, it is easy to detect any errors and have a very reliable and safe communication with CAN Bus.

The worst case response time (WCRT) of a message is the maximum time between the message is generated at the transmitter node application and it is received at the receiver node application. WCRT depends on the priority levels of the other messages, hence, the messages with higher priority might make a given message m stay in the buffer for a long time. [26, 38, 37] explains the analytical ways to compute WCRT of the messages for transmission. These methods basically assign IDs such that the message is received at its destination before the deadline. In other words, by assigning IDs to the messages, they are given appropriate priority such that WCRT of the messages are smaller than the deadline they are obligated to meet. It is also possible that such WCRT analysis is not necessary for a lightly loaded network.

The data rate for a CAN bus is limited by the arbitration mechanism. During the arbitration phase, the bits transmitted by a node must be received by the other nodes in a single bit time. Therefore, during simultaneous transmissions, it is important that bit overwrite is detected on time such that a node losing arbitration stops transmission. Although the specified maximum bit rate is 1 Mbps, the practical rates are up to 500 kbps. 125 kbps is the mostly used bit rate. The payload of a CAN node is up to 8 bytes. When the other parts of a CAN FD frame are considered, the overhead is too much and it is about 50%. Due to low data rate, large number of messages, small payload size, large overhead and increase in vehicle complexity, the bus load of the networks is between 50% and 95% [33].

#### **2.2 CAN FD**

CAN Bus doesn't meet the data rate requirements of the contemporary in vehicle communication anymore. However, CAN is a trusted protocol being used for many years in countless applications in the automotive industry. For these reasons, CAN FD (CAN with Flexible Data Rate) which both offers much higher bandwidth than CAN and backward compatibility with CAN is developed by Bosch [28, 6].

CAN FD operates at two different bit rates within a message frame. It has the same bit rate and the arbitration method as CAN but it switches to a higher bit rate during the data phase. CAN FD payload is up to 64 Bytes. Therefore at a given bus load,

the overhead of the frame decreases down to 15% [33] and theoretical net bit rates about 5 Mbps are possible [6]. Furthermore, the arbitration phase baud rate limits the overall baud rate of the frame. For example, a frame with 64 bytes payload, 11 bit standard ID, 1 Mbps of arbitration phase baudrate, 8 Mbps of dataphase baud rate has net bit rate about 5.9 Mbps [40]. Furthermore, the increase of baud rate is also beneficial for higher layer software protocols.[41] assesses the effectiveness and performance of CAN FD with respect to CAN bus in agricultural systems using higher layer protocols like J1939 and ISOBUS.

According to [3], CAN FD data phase bit rates up to 2 Mbit/s will be used in the first CAN FD systems. The network topology will be like star or hybrid. Later generation CAN FD systems will increase the data rate up to 5 Mbit/s. CAN FD frames can be divided into three parts, which are arbitration phase, data phase and arbitration phase again as can be seen in Fig.2.2. The bit rate switches to higher rate only during data phase and switches back to its old rate when the data phase is over.

Car manufacturers begin to adapt CAN FD in their system design. Toyota, Denso, and Renesas cooperate for autonomous driving system developments. Renesas contributes with micro controllers and System on Chip (SoC) devices featuring CAN FD [17]. According to [14], Mercedes considers introducing CAN FD in their S-class series cars. There are some works to adopt CAN FD to real network systems and CAN FD is considered to be used in the same network with CAN [23], [24].

CAN FD frame format differs from CAN frame format in terms of payload length, Data Length Code (DLC) and CRC computation method. Therefore, some hardware changes are required in the controllers. If the payload size is kept as 8 Bytes as in standard CAN messages, there is no need for any software changes [25]. CAN FD supports payload size of up to 64 Bytes. In such implementations software changes are required. The cost to implement CAN FD is very similar to CAN implementation costs [28].

The frames with the base ID have 11 bits ID representation while the frames with the extended ID has 29 bits ID representation. Furthermore, some control bit values in the frame change according to the ID type. CAN FD data frames for Base and Extended ID can be seen in Fig.2.2a and in Fig.2.2b.

Figure 2.2: CAN FD Frames

Example use cases of CAN FD are listed below:

- Fast software downloads: Reprogramming of ECUs and performing their in vehicle calibrations are typical cases requiring high data rates[27]. The footprint of the software increases day by day. Most of the contemporary ECUs use CAN Bus for software downloads, removing the necessity of additional communication interface like Ethernet, hence reducing the hardware costs. Since CAN FD provides higher bandwidth with 64 byte payload support and increased bit rate when compared to CAN, it is quite faster to download the software. According to [27], CAN FD provides 1.4 to 14 times faster programming times. For example, it takes 4.45 times longer to download 32 byte data via 500 kbit/s CAN bus when compared with 2Mbit/s CAN FD as illustrated in the following example:

- Time to transmit 4 standard CAN messages with 8 data bytes and 15% stuff bits takes 1021  $\mu$ s [32].

- Time to transmit 1 CAN FD message with 32 data bytes and 15% stuff bits takes  $229\mu s$  [32].

Furthermore, although CAN FD offers better software programming performance when compared to CAN, it should be noted that Flexray and CAN FD

has comparable performance. Under some conditions Flexray is faster and under some other conditions CAN FD is faster according to [29].

- Avoiding split messages: Some information is represented with more than 8 bytes, in order to transmit such information multiple CAN frames are transmitted. This increases the work load of the software. With CAN FD's large payload capability up to 64 bytes, the information does not need to be splitted into several frames hence it is transmitted in a single message. Therefore, the transport layer software management becomes easier.

- Faster Communication: As the features increase in automotive industry, the data exchange between ECUs increases therefore CAN FD can handle the increased traffic with its higher bandwidth.

- Less Bus Load: Due to increase in bandwidth, the bus loading greatly reduces.

- Bus Length: As the number of nodes and the length of the stubs increase, the bit rate reduces. With the bus length of 40 meters, stub lengths of 3 meters and 30 nodes on the bus, SAE J1939-15 states 250 kbit/s bit rate for CAN Bus[32]. With CAN FD, data phase bit rate is independent of cable length therefore, with 250 kbit/s arbitration phase bit rate and 4 Mbit/s data phase bit rate, average bit rate is 810 kbit/s[32]. Therefore, communication speed is accelerated with long cables.

The CAN protocol is defined by the ISO 11898 standard. ISO 11898-1 specifies the Data Link Layer. CAN FD requirements are currently integrated as ISO 11898-1:201. Therefore, the first CAN FD version by Bosch [6] is called non-ISO CAN FD now. Different than the non-ISO CAN FD protocol, ISO CAN FD has different failure detection abilities. 3 bit stuff counter and an extra parity bit are added in the frame and the CRC computation value is modified when compared to non-ISO CAN FD. Therefore, non-ISO and ISO CAN FD protocols are incompatible with each other [11].

## 2.3 CAN/CAN FD Controllers

In order to participate in an in-vehicle network, an in-vehicle node needs to have micro controller (MCU), a bus controller and a transceiver. The MCU is the unit where the software application runs. The Controller implements the layer 2 protocol of the bus and transmits the data received from the MCU on the bus by executing necessary framing and arbitration. The transceiver connects the node to the physical medium of the Bus. The  $C^3$  controller that we present in this thesis is a CAN FD controller. However, we note that the architecture can be adopted for CAN controllers as well. To this end, we present previous work on CAN/CAN FD controllers in Chapter3.

The basic functions of the CAN/CAN FD Controllers are to convert the information that comes from the application into CAN/CAN FD frames by following the protocol specifications, extract the related information from the received frames and convey this data to the application. For transmission, the controllers perform physical level bit generation following the timing requirements, generate frames by implementing bit stuffing, perform CRC computation and error detection. For reception, they perform physical level bit sampling according to the timing requirements, apply ID based filtering, perform buffering of the received frames, remove the stuffed bits from the received bit sequence, check the CRC values and perform error detection.

The buffering is one of the most important features of CAN/CAN FD controllers. There are two types of buffer organization, which are FIFO (First In First Out) and mailbox. In FIFO organization, for transmission, what is written to FIFO first is taken out and transmitted first. The disadvantage of this method is that it is not possible to give priority to the messages which are required to be transmitted first. For the reception, the frame received first is written to FIFO first and is taken out by the application first. Similarly, the application should process the messages previously in the FIFO before it can finally reach the message with the high priority. This leads to undesirable delay for the high priority messages. Hardware cost of FIFO implementation is low and the controller design is simple.

In mailbox organization, there is a dedicated buffer for each message. The mailbox

buffers hold a single frame. For transmission, each mailbox has priorities assigned and they are transmitted in the order such that the highest priority mailbox is vacated first. Similarly for reception, the messages are placed in their corresponding mailboxes and the application reads the message with the highest importance first without having to read the others like in the case of FIFO concept. RX buffer organization particularly becomes significant if the MCU is slow at processing the received messages [36]. The hardware cost of the mailbox is higher since more memory is required, the controller design becomes more complex and the timing performance is better when compared to FIFO concept.

In order to reduce the MCU load, the receivers of the controllers have a filtering feature. Only the messages which pass the filters are placed to the buffers. By doing so, the unwanted messages are discarded by the controller so that MCU does not need to process them.

The controllers interface with the transceivers with the digital receive and transmit pins. Moreover, they communicate with the MCUs in two different ways. In the first method, the controller is integrated inside the MCU chip. The communication between the controller and the MCU processor core is the internal system bus which is a shared bus with the other peripheral controllers like UART, SPI, I2C and Ethernet. In the second method, the MCU does not contain the CAN/CAN FD controller inside the chip, instead, the controller is external to the MCU. This is the case for the low cost MCUs where the most of the peripherals already contained in higher cost MCUs are excluded from the chip to reduce the cost and the footprint of the chip. Common interfaces which can be used between the CAN/CAN FD Controller and the MCU are listed and discussed below:

• UART: UART is a serial communication protocol with the most common baud rate of 115.2 kbit/s There are some instances of UART which are used in high performance MCUs with the baud rates of several Mbit/s. Since our case is for the low cost MCUs, an interface with the bit rate of several hundred kbits is not acceptable when the baud rate of CAN/CAN FD is considered. Interfaces having baud rates lower than CAN/CAN FD baud rate would result in huge response time, thus reducing the timing performance of the controller signifi-

cantly.

- I2C: I2C is a serial communication protocol with the most common baud rate up to 400 kbit/s. Due to the same reasons listed for UART, I2C is not a suitable interface for CAN/CAN FD Controllers

- PCIe: PCIe is a serial communication protocol with bit rates in the range of Gbit/s. Since low cost MCUs do not have PCIe interface, this protocol is not suitable for standalone CAN/CAN FD controllers.

- SPI: SPI is a serial protocol with the most common baud rate of 10 Mbit/s. This baud rate is higher than CAN/CAN FD baud rates. When high baud rates of CAN FD like 4 Mbit/s is implemented, higher SPI baud rates would be used to get better response time. Serial communication is better than parallel when the I/O pin utilization of MCU is considered. Low cost MCUs have limited amount of I/Os and any unused peripheral I/Os can be used for other purposes as there is I/O multiplexing for unused pins. SPI seems to be the best communication interface for CAN/CAN FD controllers.

#### **CHAPTER 3**

## PREVIOUS WORK ON CAN/CAN FD CONTROLLERS

[34] covers CAN Controllers and their features. It presents a controller which has a maximum of 32 mailbox TX (Transmit) buffers. Regarding configurable CAN Controllers,[12] is a CAN Controller IP Core. TX buffers are organized as one high priority buffer and a FIFO with a configurable depth up to 64 message objects. RX (Receive) buffers are organized as FIFO with a configurable depth up to 64 messages. It features user configurable acceptance filters for the received messages, the number of the filters can be up to 4. The communication interface with the MCU is PLB v4.6 bus standard. [13] is an external CAN controller with SPI interface, it features two receive buffers with prioritized message storing. There are six 29 bit filters and two 29 bit masks for the received messages. It supports three transmit buffers with prioritization. The communication interface with the MCU is SPI. Since it is an ASIC (Application Specific Integrated Circuit), the depth of the buffers is fixed and not configurable like the controllers which are realized as IP Cores.

This thesis focuses on CAN FD Controller implementation. Bosch, the company that invented CAN and CAN FD protocols, has two CAN FD controllers which are realized as FPGA IP Cores. The first one is C\_CAN FD8. It supports CAN FD messages with the payload up to 8 bytes. It contains 32 message objects and ID masks for each of the objects. The message objects can also be programmed as FIFO and they are used for both the transmitted and the received messages. The user interface is AMBA APB bus for ARM processors and Avalon bus for ALTERA FPGAs. The purpose of this IP core is to maintain the compatibility with the existing Bosch CAN controller as CAN bus message payload is also up to 8 bytes. The second IP core by Bosch is M\_CAN, which supports both ISO 11898-1:2015 and non-ISO CAN FD imple-

mentation [2] (2015). The payload of CAN FD frames supported is up to 64 bytes. The memory where the buffers are located is not internal to the controller, instead it uses the existing single or dual port memory inside the MCU. The interface to the external memory is 32 bit generic master interface. It features two configurable Receive FIFOs with up to 64 message objects with filtering capability. Furthermore, it supports 32 TX buffers whose message size can be configured. However, the configuration sizes for all of the buffers are the same, therefore, the buffer sizes should be configured according to the longest message payload size. This leads to inefficient memory allocation especially for heterogeneous message sizes. TX handler block inside the controller picks the message with the highest priority to transmit among all the buffers. The controller interfaces with the MCU via its 8/16/32 bit generic slave interface.

[1, 9, 18] are the CAN FD IP cores developed in 2015. [1] supports non-ISO CAN FD implementation. Total buffer size is synthesis time configurable. Buffers are organized as transmit buffer, high-priority transmit buffer and receive buffer whose depths are individually configurable by the MCU. There are up to 16 acceptance filters. The interface to the MCU is AHB-Lite slave interface. [9] supports both non-ISO and ISO CAN FD implementation. It features synthesis time configurable depths for receive and transmit FIFOs. It contains 256 message filters for the received messages. It interfaces with the MCU with 8/16/32/64 bit system bus. [18] also supports non-ISO and ISO CAN FD. The size of the transmit and the receive buffers are configurable during synthesis time. The interface to the MCU is via the system bus.

[5, 10, 4] are the CAN FD IP cores on the market since 2016. [5, 10, 4] support ISO and non-ISO CAN FD formats. [5] features transmit buffers with up to 32 message objects. Receive buffers support up to 48 message objects with ID filtering featuring. The buffers can be configured as FIFO or mailbox. Transmit handler selects the highest priority message to begin transmitting. The number of the buffers is fixed and not configurable. The MCU interface is AXI4-Lite bus. [10, 4] are IP Cores similar to each other. [10] implements two types of transmit buffers. One is the high priority primary transmit buffer, the other one is the lower priority secondary transmit buffer. The high priority transmit buffer can store only one message. However, the depth of

the lower priority buffer is synthesis time configurable. The size of the receive FIFO can be configured during the synthesis and there are up to 16 independently programmed filters for the received messages. The MCU interface options are generic 32-bit host controller interface, AHB, APB (32 bit), generic 8 or 16 bit. Similarly, [4]offers one high priority transmit buffer and configurable number of low priority buffers. Moreover it supports RX FIFO buffering with up to 29 bit acceptance filtering. The configuration is done during synthesis. The interface to the host MCU is generic 8 bit host controller, 8/16/32 bit AMBA-APB or 32 bit AHB-Lite.

[8, 20, 7] don't have non-ISO CAN FD support. [8] has fixed size 128 byte receive buffer and transmit buffer. It supports message filtering. The communication between the controller and the MCU is 8/16/32-bit CPU slave interface. [20] offers synthesis time configurable mailboxes. The mailboxes can be used for both the transmitting and the receiving functions. Furthermore, there is a RX FIFO which can store 6 frames. The MCU communication interface is on-chip system bus. [7] CAN FD IP Core has TX and RX FIFOs with synthesis time configurable sizes. There are user configurable acceptance filters. MCU interface is AMBA-AXI4-Lite interface (32-bits) or standard address/data configuration Interface.

[39] is a recent paper which presents CAN FD IP Core with SPI interface. There are no details about the interface between the controller and the host MCU. The interface is described very briefly. The buffers have no configuration capability. The design is explained very coarsely with very little implementation detail. The design is only verified by oscilloscope signal inspection.

To sum up, to the best of our knowledge  $C^3$  is the first CAN FD IP core that offers very flexible and efficient configuration capability to the software developer during application run time (after synthesis), with a total number of 192 mailboxes. Mailboxes are organized as 96 transmit and 96 receive buffers. The mailboxes are allocated an average payload size of 16 bytes instead of maximum payload size of 64 bytes. Because it is very unlikely that all the messages in a message set of a network application will require 64 bytes payload size. This yields 96x16 bytes memory consumption instead of 96x64 bytes hence less memory usage and more memory utilization. It is the first controller with SPI interface whose response time is measured, academically

evaluated, tested and analyzed. Different from other controllers,  $C^3$  supports up to 96 filters for each RX buffer for the received messages.

The comparison of the CAN FD IP cores mentioned in this chapter can be seen in Table 3.1, Table 3.2 and Table 3.3. We define the performance criteria for comparison as follows:

- Year: Release year of the controllers

- Transmit Buffer Type: Buffer organization structure for the transmit messages, either FIFO or mailbox

- Transmit Buffer Configuration: Configurability properties of the transmit buffers

- Receiver Buffer Type: Buffer organization structure for the received messages, either FIFO or mailbox

- Receive Buffer Configuration: Configurability properties of the receive buffers

- Buffer Configuration Time: The time when the configuration takes place, either

synthesis time or application time. Synthesis time configuration is one time

configuration before the application runs and does not give the user the ability

to reconfigure the buffers during run time while application time configuration

gives the user the ability to reconfigure the buffers during run time for different

applications.

Table 3.1: CAN FD Controllers Comparison 1

| 4] [1] | 2015 | FO FIFO                          | ondary transmit Primary ve secondary transmit e of the secondary buffers' total size is configurable     | FO FIFO                          | buffers' total size is Receive buffers' total size is configurable | Total memory size is synthesis time, each FIFO size is application time configurable |  |

|--------|------|----------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------------------------|--|

| [4]    | 2016 | FIFO                             | Primary ve secondary transmit<br>buffers. Total size of the secondary<br>transmit buffer is configurable | FIFO                             | Receive buffers' total size is<br>configurable                     | Synthesis time                                                                       |  |

| [10]   | 2016 | FIFO                             | Primary ve secondary transmit<br>buffers. Total size of the secondary<br>transmit buffer is configurable | FIFO                             | Receive buffers' total size is<br>configurable                     | Synthesis time                                                                       |  |

| [12]   | 2016 | FIFO or mailbox with 32 elements | Transmit buffers' total size is<br>configurable                                                          | FIFO or mailbox with 48 elements | Receive buffers' total size is<br>configurable                     | Synthesis time                                                                       |  |

|        | Year | Transmit Buffer Type             | Transmit Buffer Configuration                                                                            | Receiver Buffer Type             | Receive Buffer Configuration                                       | Buffer Configuration Time                                                            |  |

Table 3.2: CAN FD Controllers Comparison 2

|                               | [2]                                                                                                   | [8]                                               | [20]                                        | [6]                                                  |

|-------------------------------|-------------------------------------------------------------------------------------------------------|---------------------------------------------------|---------------------------------------------|------------------------------------------------------|

| Year                          | 2016                                                                                                  | 2016                                              | 2016                                        | 2015                                                 |

| Transmit Buffer Type          | FIFO or mailbox with 32 elements                                                                      | FIFO                                              | Mailbox                                     | FIFO                                                 |

| Transmit Buffer Configuration | All mailboxes can be configured but<br>the configuration size have to be the<br>same for each mailbox | 128 byte transmitter FIFO is fixed size           | Total number of mailboxes can be configured | Transmit buffers' total size is<br>configurable      |

| Receiver Buffer Type          | FIFO or mailbox with 64 elements                                                                      | FIFO                                              | Mailbox or FIFO                             | FIFO                                                 |

| Receive Buffer Configuration  | All mailboxes can be configured but<br>the configuration size have to be the<br>same for each mailbox | 128 Byte Receive FIFO is fixed size               | Total number of mailboxes can be configured | Receive buffers' total size is<br>configurable       |

| Buffer Configuration Time     | Application time                                                                                      | Synthesis time                                    | Unknown                                     | Synthesis time                                       |

| User Interface                | 8/16/32 bit CPU Interface                                                                             | CPU Interface, 8/16/32-bit CPU slave<br>interface | CPU Interface, Peripheral BUS<br>Interface  | CPU Interface, 8/16/32/64-bit CPU<br>slave interface |

Table 3.3: CAN FD Controllers Comparison 3

|                               | [18]                                            | [7]                                                                       | C <sup>3</sup> : Configurable CAN FD Controller                                                                                                       |

|-------------------------------|-------------------------------------------------|---------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| Year                          | 2015                                            | 2016                                                                      | 2017                                                                                                                                                  |

| Transmit Buffer Type          | FIFO                                            | FIFO                                                                      | Mailbox                                                                                                                                               |

| Transmit Buffer Configuration | Transmit buffers' total size is<br>configurable | Transmit buffers' total size is<br>configurable                           | Configurable total size of memory. Each mailbox can be configured with desired size and the number of the mailboxes can be configured up to 96        |

| Receiver Buffer Type          | FIFO                                            | FIFO                                                                      | Mailbox                                                                                                                                               |

| Receive Buffer Configuration  | Receive Buffers' total size is<br>configurable  | Receive Buffers' total size is<br>configurable                            | Total size of memory is configurable. Each mailbox can be configured with the desired size and the number of the mailboxes can be configured up to 96 |

| Buffer Configuration Time     | Synthesis time                                  | Synthesis time                                                            | Total memory size is synthesis time, all the other settings are application time configurable                                                         |

| User Interface                | CPU Interface, System Bus Interface             | CPU Interface, System Bus Interface   CPU Interface, System Bus Interface | IdS                                                                                                                                                   |

#### **CHAPTER 4**

## C3 (CONFIGURABLE CAN FD CONTROLLER) ARCHITECTURE

This chapter presents the hardware architecture of our proposed  $C^3$  Configurable CAN FD Controller. A brief presentation for the implementation details, evaluation and the response time measurements of  $C^3$ : Configurable CAN FD Controller can be found in [22], [21] which are presented in the Appendix of this thesis.

Figure 4.1:  $C^3$  Architecture

$C^3$  implements the CAN FD Base & Extended Format Data Frame according to the non-ISO specification [6] as we introduce in Section 2.2. Our proposed hardware architecture features a TX Buffer memory and an RX Buffer memory each with a fixed size. The MCU programmer can organize these memory areas into respective TX and RX buffers with desired message size and message count. In our implementation, a maximum of 96 TX buffers and 96 RX buffers can be configured in mailbox form.  $C^3$  transmits the messages in the TX buffers according to the priority order. Each RX

buffer has an ID-Mask pair for message filtering. The interface between  $C^3$  and the host MCU is through SPI (Serial Peripheral Interface).

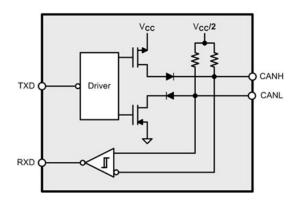

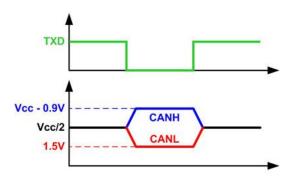

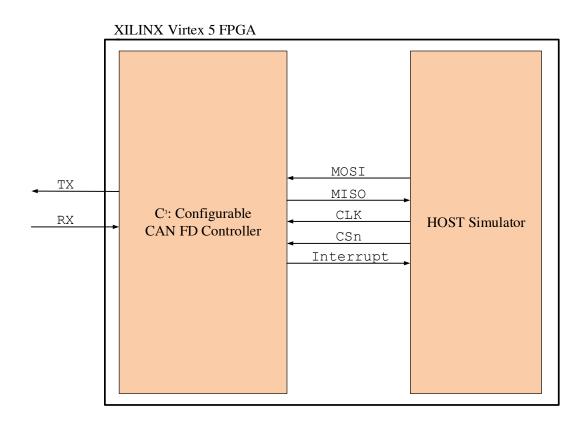

We present the  $C^3$  FPGA IP Core block architecture together with the host MCU and a transceiver in Fig.4.2. Transceiver is used to convert controller's single ended TTL/CMOS level signals to differential ended CAN BUS physical layer signals, CAN High and CAN Low.

Figure 4.2: Top Level Architecture

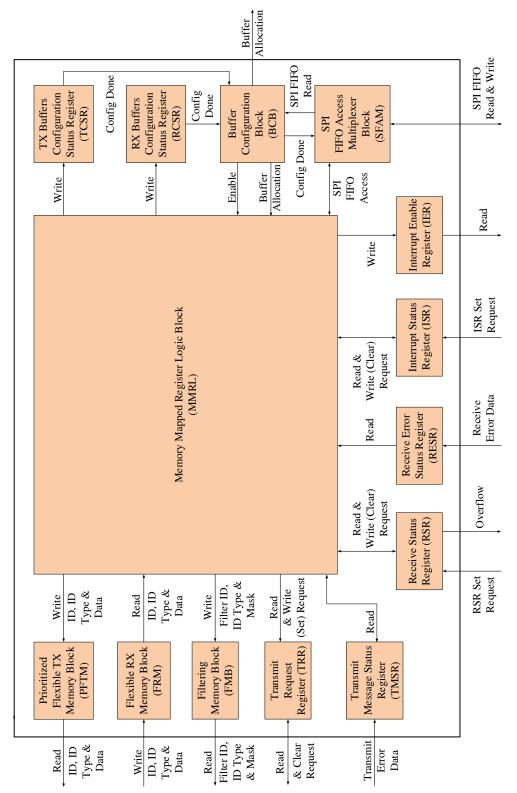

The top level hardware blocks of  $C^3$  are; Sender Module (SM), Receiver Module (RM), and the user interface blocks which are the Memory Mapped Register Block (MMR), SPI Control Block (SPIC) and Interrupt Control Block (ICB). The CAN standard requires sending an acknowledgment after each message reception. To this end, the SM and RM are both connected to the physical layer TX/RX lines on the transceiver. The RX and TX buffers are realized on Prioritized Flexible TX Memory Block (PFTM) and Flexible RX Memory Block (FRM) in MMR respectively as in Fig.4.3.

The hardware resources of  $C^3$  are configured by writing the register array implemented in the MMR. These registers are accessible by the  $C^3$  Driver software using the standard SPI protocol signals MISO (Master In Slave Out), MOSI (Master Out Slave In), CSn, CLK and interrupt signal. After the configuration, the application software starts to run on the host MCU which generates and consumes the data carried in the CAN FD message payload. Host CPU sees the controller as a set of registers which can be read and be written to according to the controller's protocol requirements. The application software sends and receives message data together with their CAN IDs through the driver software.  $C^3$  runs at 100 MHz. We provide implementation details in Section 4.8 together with the evaluation results in Section

5.

## 4.1 Hardware Blocks: Memory Mapped Register Block

The host MCU communicates with  $C^3$  for configuration and data transmission using a memory mapped architecture that is realized with a set of registers in MMR. The addresses of these registers are known to the Driver Software. The host device reads and writes these registers via our SPI protocol signals.

The block diagram of Memory Mapped Register Block (MMR) can be seen in Fig. 4.3.

There are 96 sets of TX registers and 96 sets of RX registers to support up to 96 TX and RX buffers respectively.

Each TX register set consists of

- TX ID Register

- TX DLC (Data Length Code) Register

- TX Data Register

Each RX register consists of

- RX ID Register

- RX Mask Register

- RX DLC (Data Length Code) Register

- RX Data Register

MMR also features the following registers: Transmit Control & Status Registers

- Transmission Request Register (TRR)

- Transmit Message Status register (TMSR)

Receive Control & Status Registers

Figure 4.3: Memory Mapped Register Block (MMR)

- Receive Status Register (RSR)

- Receive Error Status Register (RESR)

Interrupt Control & Status Registers

- Interrupt Enable Register (IER)

- Interrupt Status Register (ISR)

**Buffer Configuration Control Registers**

- RX Buffers Configuration Status Register (TCSR)

- RX Buffers Configuration Status Register (RCSR)

For the rest of the thesis we write  $\mathbf{TX}(\mathbf{ID})$  and  $\mathbf{RX}(\mathbf{ID})$  to indicate a specific register set for a CAN ID. The content of the data register of  $\mathbf{TX}(\mathbf{ID})$  is the payload of the message with the specified CAN ID.

SPI FIFO Access Multiplexer Block (SFAM): As described in detail in Sec.4.2, Host MCU interfaces  $C^3$  with SPI, and MMR communicates SPCB with FIFO accesses. SFAMB multiplexes FIFO signals between MMR Logic Block (MMRL) and Buffer Configuration Block (BCB). Due to the nature of hardware design, a signal cannot be driven by two sources, therefore for situations where multiple drivers are required, a multiplexing method is used. This multiplexer first gives access to BCB, after the buffer allocation is done, access is given completely to MMRL.

Buffer Configuration Block (BCB): This Block manages the **TX DLC** (**Data Length Code**) **Register** and **RX DLC** (**Data Length Code**) **Register**. **DLC Registers** must be configured to arrange the size of the buffers. The content of a **DLC Register** can be seen in Fig.4.6 and Fig.4.7

Host MCU has to configure the registers one by one in an ordered way. First TX buffers then RX buffers configuration should be done. After TX buffer sizes are configured, host should write **TX Buffers Configuration Status Register (TCSR)** to indicate TX buffer configuration is finished so that RX buffer configuration can start.

Same process is also repeated for RX buffers. Finally, **RX Buffers Configuration Status Register (RCSR)** is written by the host to indicate whole configuration process is finished. As the configuration finishes, the buffer allocation information, the address and size of each buffer in the Prioritized Flexible TX Memory Block (PFTM) and Flexible RX Memory Block (FRM), is kept as registers and used by Sender Module (SM) and Receiver Module (RM) and MMR Logic Block (MMRL). Furthermore, after the whole buffer configuration process is complete, SFAM block is informed so that SPI signals are routed to MMRL block. The content of **TCSR** and **RCSR** are shown in Table 4.1.

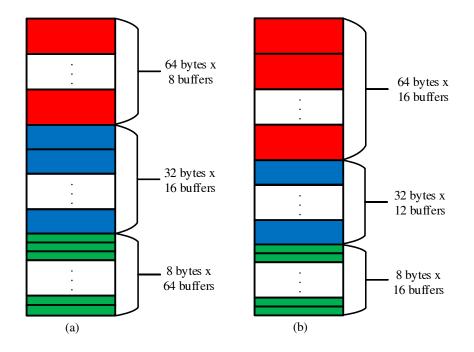

Prioritized Flexible TX Memory Block (PFTM): The host MCU can partition PFTM to implement up to 96 TX buffers in desired sizes. This block is designed as a 1920 bytes block RAM. However, the size of PFTM can be increased during synthesis. There are 480 addressable locations each with a depth of 32 bits. We implement the buffers in the mailbox architecture where each TX buffer is allocated for a specific CAN ID and can store the payload for a single frame. The memory is organized with an appropriate size to store 4 byte ID registers and an average of 16 bytes data for each of the 96 buffers. (96x4 + 96x16) = 384+1536 = 1920 bytes) Using payload size average of 16 bytes per mailbox instead of allocating 64 bytes for each mailbox yields less memory consumption and more memory utilization. Two example buffer configurations that fully utilize 1536 bytes data area are depicted in Fig.4.4

The first buffer in the memory has the highest priority. This information is known to host MCU and configuration is done with taking this information into account. MMRL writes ID & Data to be transmitted to the related buffer location when a write request comes from Host MCU. TX Control Logic Block (TXCL) has read access to this memory block to get the ID and data to transmit.

Flexible RX Memory Block (FRM): This block is designed as a 1920 bytes block ram. There are 480 addressable locations each with a 32 bit depth. Memory is organized as large as it can store 4 byte ID registers and 16 bytes data for each 96 buffers. (96x (4 + 16) = 1920 bytes). Using payload size average of 16 bytes per mailbox instead of allocating 64 bytes for each mailbox yields less memory consumption and more memory utilization. RX Control Logic Block (RXCL) has write access to this

Table4.1: Configuration Registers

|               | Address (0x) | Register Name            | Read (R)/<br>Write (W) | Description                                                                                                                |

|---------------|--------------|--------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------|

|               |              |                          |                        | Host should write to this register once the configuration is completed                                                     |

|               | ,            | TX Buffers Configuration | :                      | Register[0] => 1 => Transmit Buffers Initialization is completed                                                           |

|               | 0            | Status Register (TCSR)   | >                      | Register[0] => 0 => Transmit Buffers Initialization is not completed                                                       |

| Config Status |              |                          |                        | Register[7:1] => # of Transmit Buffers whose Initialization is completed, e.g. => 23 means buffers 1 to 23 are initiliazed |

| Kegister set  |              |                          |                        | Host should write to this register once the configuration is completed                                                     |

|               | ,            | RX Buffers Configuration | , i                    | Register[0] => 1 => Receive Buffers Initialization is completed                                                            |

|               | 4            | Status Register (RCSR)   | ^                      | Register[0] => 0 => Receive Buffers Initialization is not completed                                                        |

|               |              |                          |                        | Register[7:1] => # of Receiver Buffers whose Initialization is completed,                                                  |

|               |              |                          |                        | e.g. => 23 means buffers 1 to 23 are initiliazed                                                                           |

Figure 4.4: Example Memory organizations: (a) 88 buffers (b) 44 buffers

memory block to put the ID and data of the received frames in the related location. As read request comes from the Host MCU, MMRL reads the related information from the related buffer address and responds to the request.

Filtering Memory Block (FMB): The Memory consists of 32 bits of ID & Mask pairs for each 96 buffers. There are 192 locations with depth of 32 bits. During configuration, Host MCU programs ID & Mask pair for each buffer to be used. MMRL has write access to this memory block, it writes ID & Mask pairs as requested by the Host MCU. Message Filter (MF) reads from this memory during filtering process.

MMR Logic Block (MMRL): After buffer allocation is done, this block takes over the SPI FIFO access from BCB. All of the CPU's write and read requests are handled here. This logic block has control for all of the registers except the ones with buffer size configuration (TX DLC (Data Length Code) Register, RX DLC (Data Length Code) Register, TX Buffers Configuration Status Register (TCSR) and RX Buffers Configuration Status Register (TCSR)). The state machine here polls the SPI instruction FIFO to see if there are any pending requests. The machine has two different state sets, one for write requests and one for read requests. The write state set gets the address of the register from the address FIFO in SPCB, gets the burst

data size from burst data FIFO in SPCB and finally gets the data part from RX Data FIFO in SPCB. The amount of data to be read from the RX data FIFO depends on the instruction type and burst data size. For the write requests, either a related memory address is written or related register is written. The addresses read from Address FIFO is mapped to PFTM, FMB memory addresses and directly to some registers as seen in the Fig.4.3.

Similarly, the read state set gets the address of the register from the address FIFO in SPCB, gets the burst data size from burst data FIFO in SPCB. The addresses read from Address FIFO are mapped to FRM memory addresses and directly to some registers as seen in the Fig.4.3. Since the read requests are non posted requests, MMRL gets the data from the related mapped address or from a register and writes the data to the TX Data FIFO quickly such that when SPB reads the data to respond, the data is present in the FIFO.

The mechanism of each register accessed by MMRL will be described in the related block descriptions.

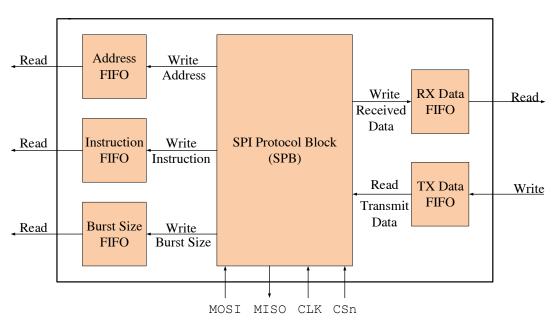

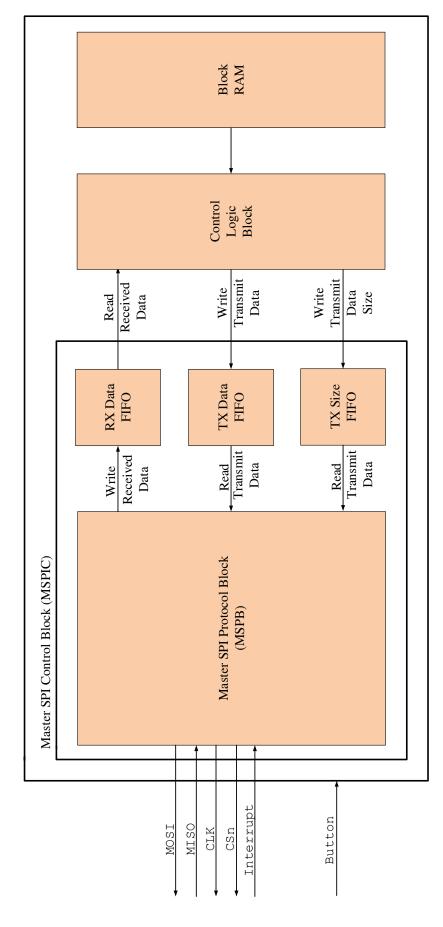

#### 4.2 Hardware Blocks: SPI Protocol Control Block

Figure 4.5: SPI Protocol Control Block

We develop and implement the SPI (Serial Peripheral Interface) control block in the

scope of this thesis work. The block diagram of SPI Protocol Control Block (SPCB) can be seen in Fig.4.5. The SPI standard defines the physical layer of the interface, timing of the signals and the roles of the master and the slave devices. The SPI physical layer signals going out of the controller are as follows:

- CSn (Chip Select)

- CLK (Clock)

- MOSI (Master Out Slave In)

- MISO (Master In Slave Out)

Master device has the following tasks:

- It controls CSn, MOSI, CLK signals

- It asserts CSn along with the CLK and data on MOSI line

- It deasserts CSn to indicate that the communication is over

Slave device has the following tasks:

- When CSn is asserted by the host, it starts to sample data at the rising edges of the clock.

- It gets the data on MOSI line and responds on MISO line if a response is required. If not, it just gets the data until the CSn is deasserted

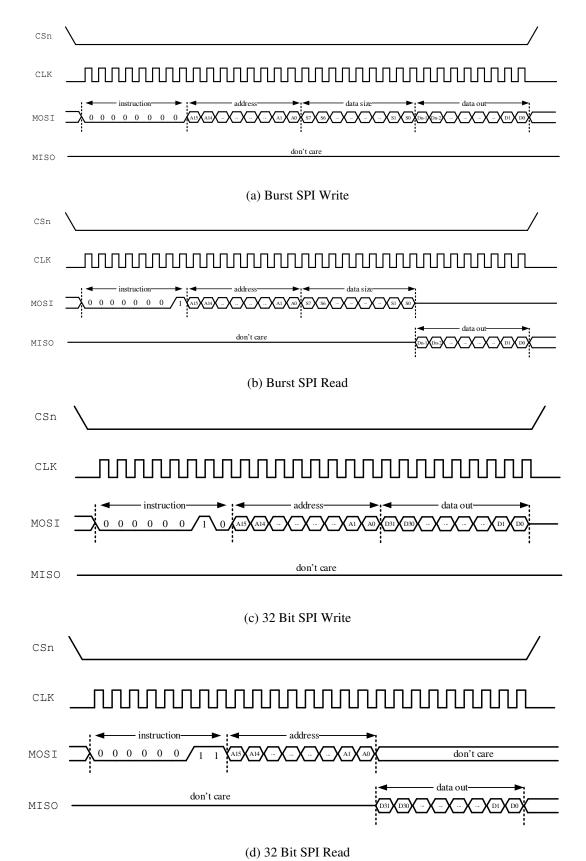

The SPI protocol only defines the mechanisms listed above. The custom protocols using SPI define the data amount and data content which the master device sends on MOSI line and the data content to which slave needs to send a response, the content and the amount of the data slave puts on MISO line, the time when the slave begins to respond when the slave response is required. Accordingly, we designed and implemented our own communication protocol with SPI. Our communication protocol over SPI between the host MCU and  $C^3$  is described in Table 4.2.

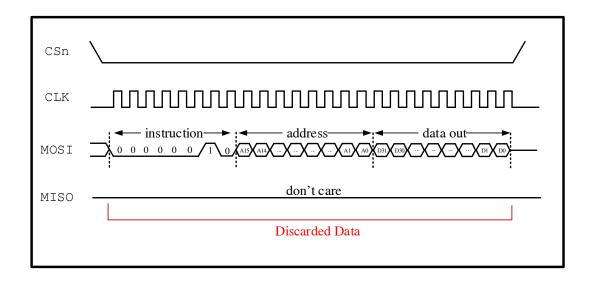

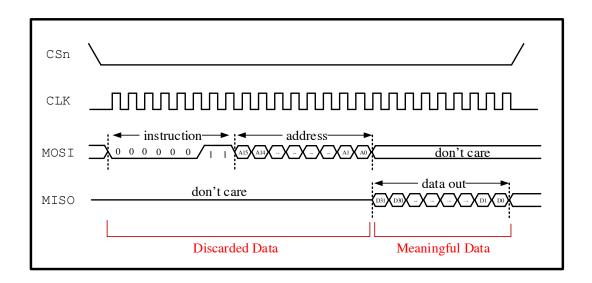

Figure 4.6: SPI Timing Diagrams

Table4.2: SPI Commands and Responses

| Access    | Host Request<br>Inst. Code | Host<br>Data         | C <sup>3</sup> Response |

|-----------|----------------------------|----------------------|-------------------------|

| Type      | mst. Code                  | Data                 | Kesponse                |

| Burst     |                            | Address (16 bits)    | _                       |

| SPI       | 0x00                       | + Data size (8 bits) |                         |

| Write     |                            | + Burst data         |                         |

| Burst     | 0x01                       | Address (16 bits)    | Burst data              |

| SPI Read  | UXU1                       | + Data size (8 bits) | Durst data              |

| 32 bit    | 0x02                       | Address (16 bits)    | _                       |

| SPI Write | 0x02                       | + Data (32 bits)     |                         |

| 32 bit    | 0x03                       | Address (16 bits)    | Data (32 bits)          |

| SPI Read  | 0.003                      | Address (10 bits)    | Data (32 01ts)          |

The host requests are on the MOSI line and the  $C^3$  response is on the MISO line. The request types are defined with the instruction codes of 8 bits. After the instruction, regardless of its type, master device puts the 16 bit address of the register on MOSI. Depending on the instruction type, host might go on transmitting data or slave responds to the request. During Burst Read or Write instructions, the amount of data is also provided to the slave with 8 bits of burst data size. The burst data transfers are in multiples of 4 bytes. Fig.4.6 depicts the signaling of our protocol for the 32 bit and burst instructions.

Our implementation is a high-speed SPI with 10 MHz clock frequency.

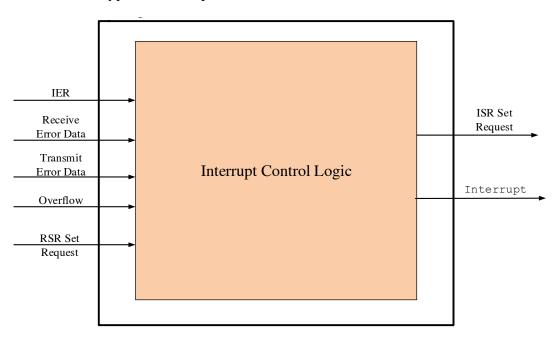

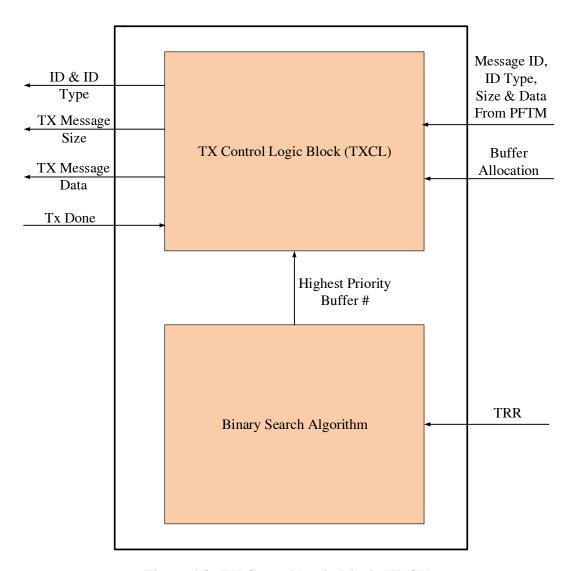

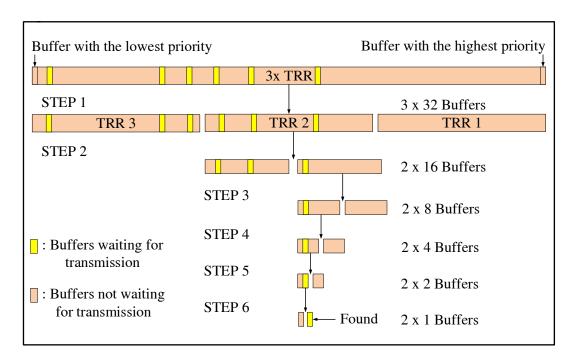

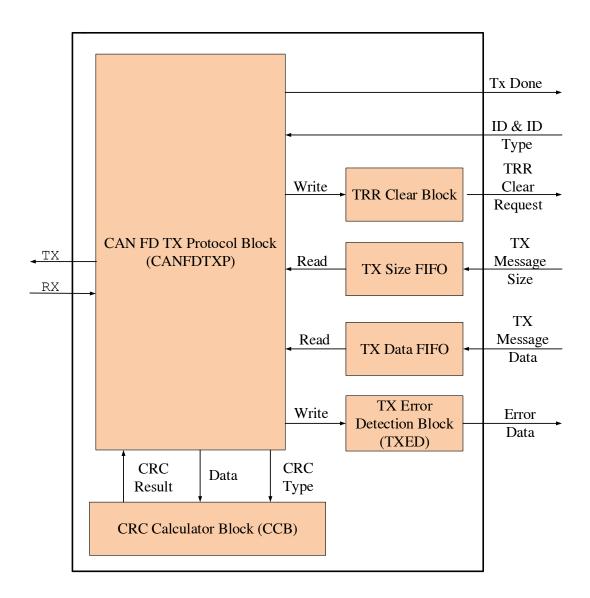

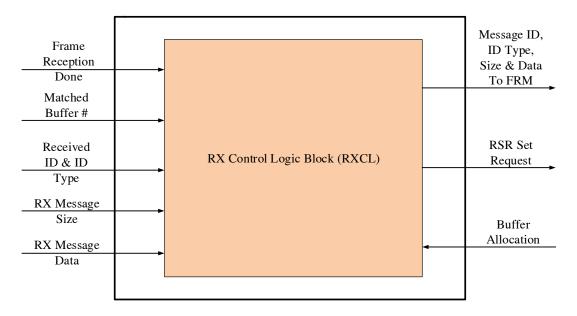

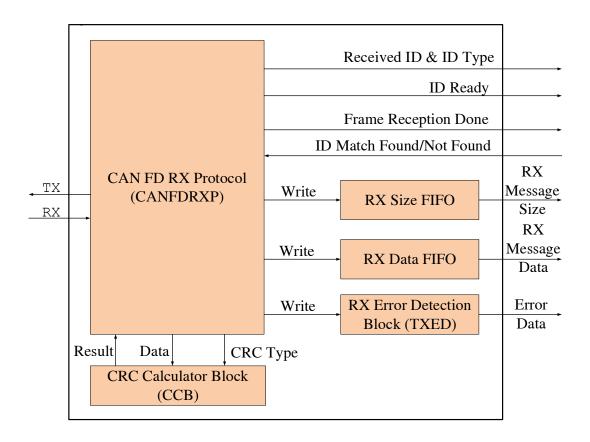

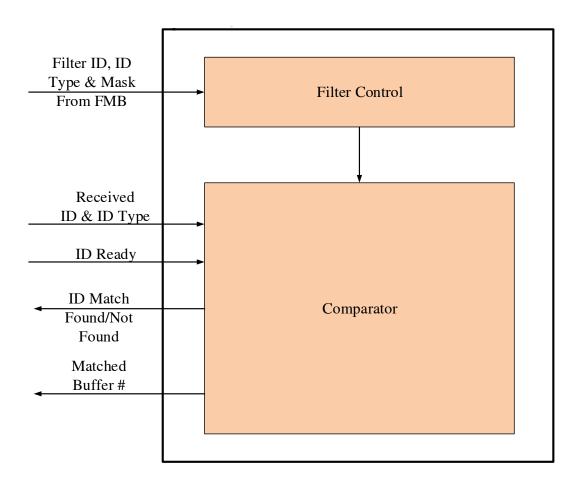

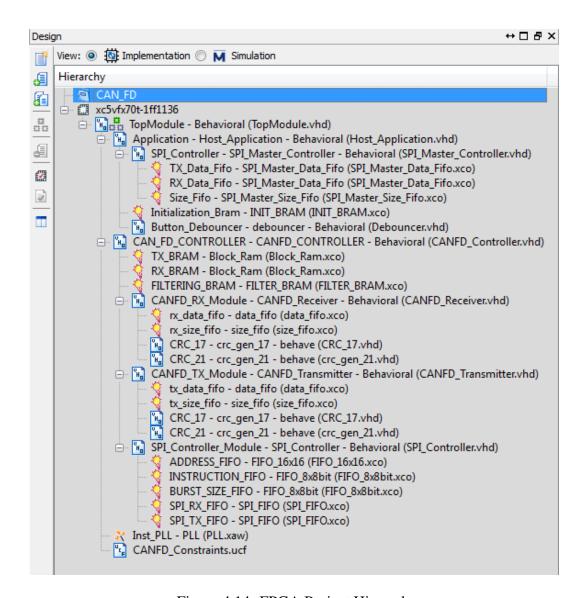

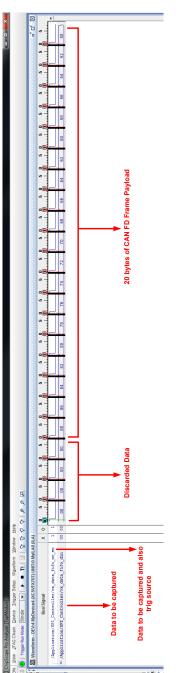

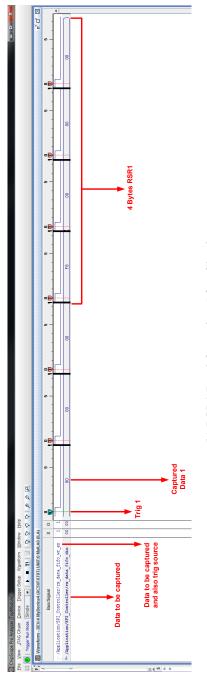

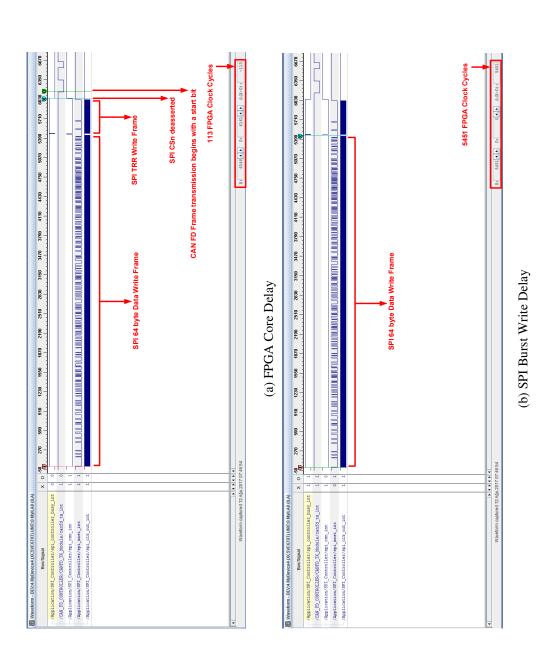

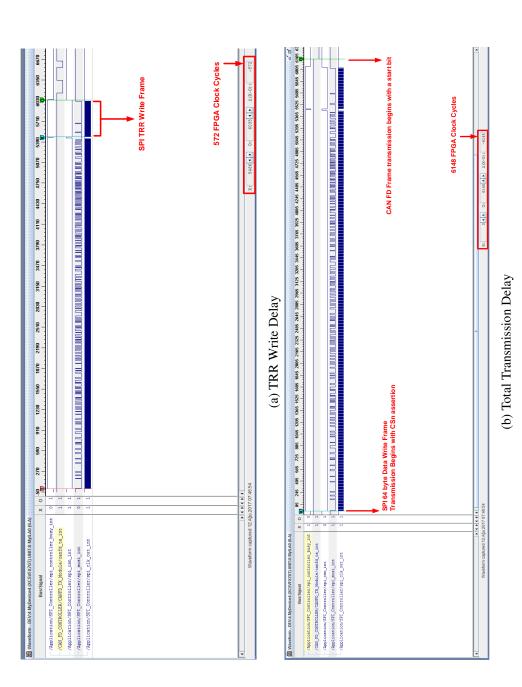

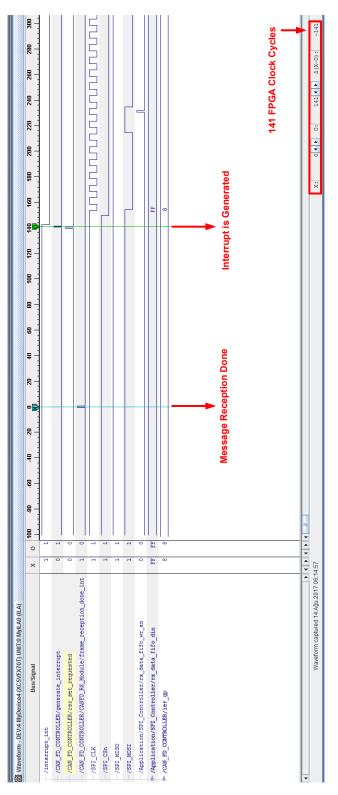

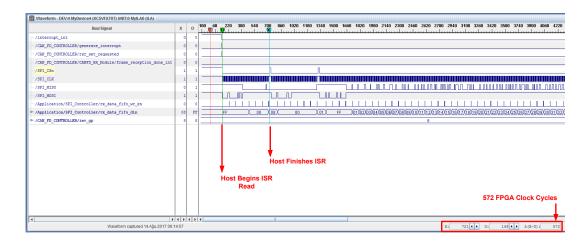

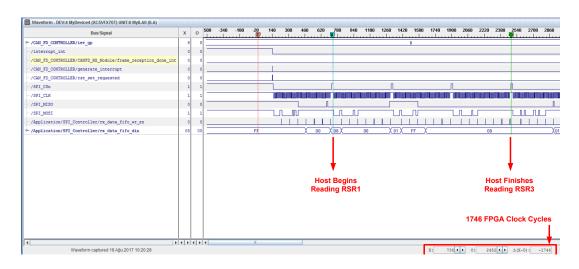

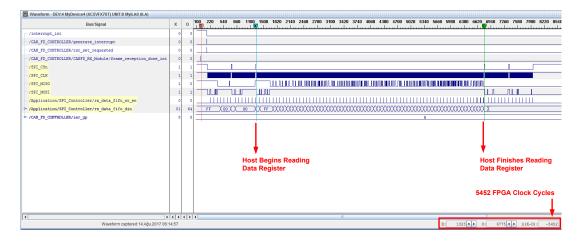

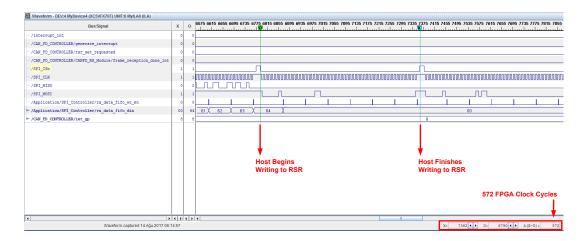

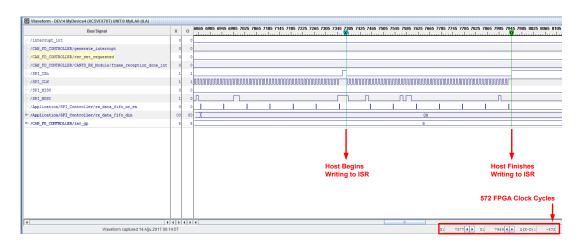

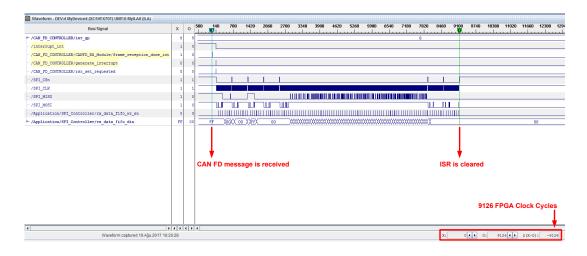

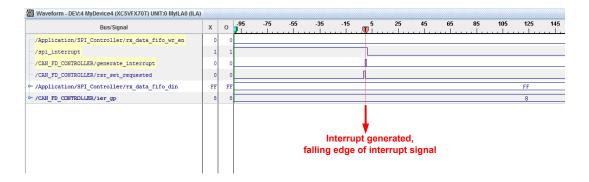

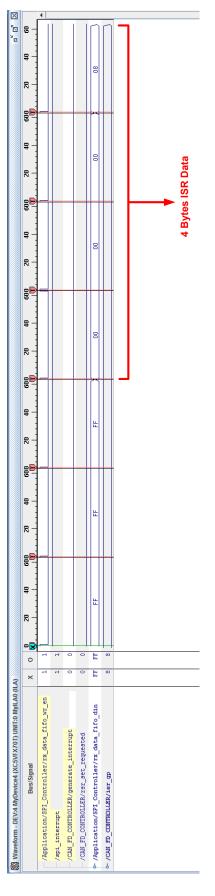

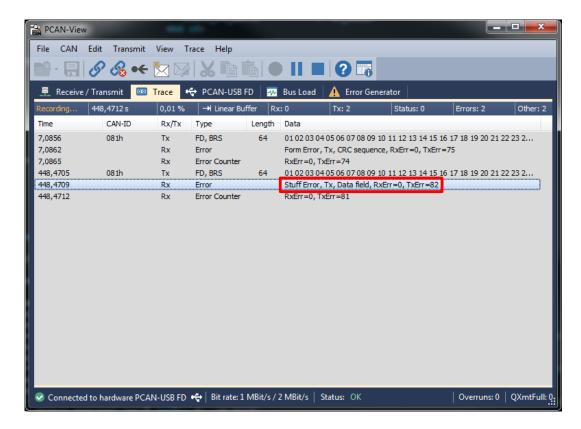

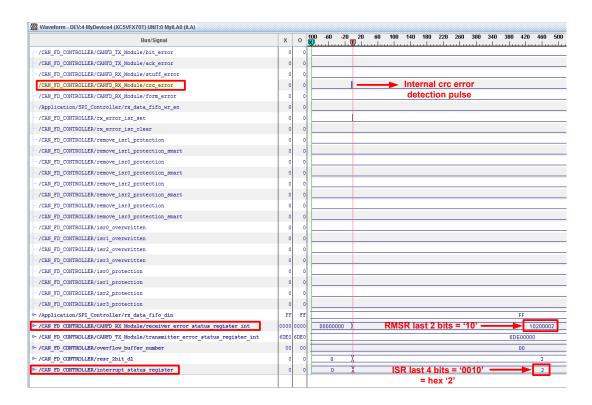

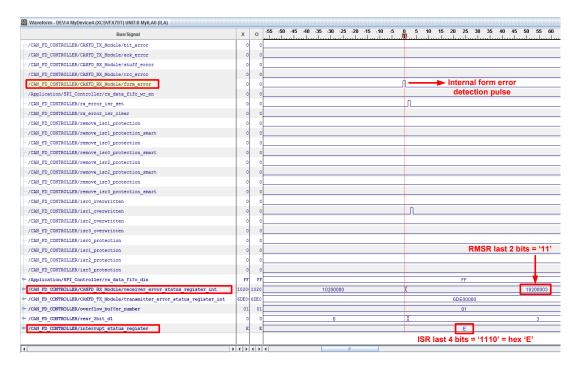

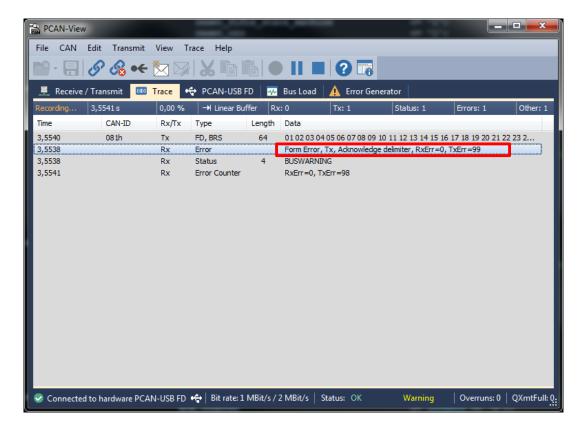

During master write operations, SPI Protocol Block (SPB) samples the bits at the rising edges of the clock when the CSn signal is low. It first gets 8 bit instruction and writes this data to the Instruction FIFO, then gets 16 bit address and writes the address into the Address FIFO. Depending on the instruction type, it either gets 8 bits of burst data size and writes it to the burst size FIFO or just skips to the data part. In the data phase, the data is written to RX Data FIFO in multiples of 32 bits. If it's a 32 bit SPI Write, only 32 bit data is written to the FIFO, otherwise the quantity of data to be written to the FIFO is determined according to the amount of data contained in the burst data size field. During master read operation, 8 bit instruction and 16 bit address is fetched by the SPB and written to the respective FIFOs. If the instruction is 32 bit SPI Read, SPB gets the data from TX Data FIFO and responds to the master on MISO line. Otherwise, SPB fetches burst data size and writes this information to Burst Size FIFO and gets as much as data as indicated in burst data size from TX