### ELECTRICAL CHARACTERIZATION OF ELECTRON SELECTIVE TITANIUM DIOXIDE AND HOLE SELECTIVE MOLYBDENUM TRIOXIDE HETEROCONTACTS ON CRYSTALLINE SILICON

### A THESIS SUBMITTED TO THE GRADUATE SCHOOL OF NATURAL AND APPLIED SCIENCES OF MIDDLE EAST TECHNICAL UNIVERSITY

BY

DOĞUŞCAN AHİBOZ

### IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE IN PHYSICS

SEPTEMBER 2017

### Approval of the thesis:

### ELECTRICAL CHARACTERIZATION OF ELECTRON SELECTIVE TITANIUM DIOXIDE AND HOLE SELECTIVE MOLYBDENUM TRIOXIDE HETEROCONTACTS ON CRYSTALLINE SILICON

submitted by DOĞUŞCAN AHİBOZ in partial fulfillment of the requirements for the degree of Master of Science in Physics Department, Middle East Technical University by,

| Prof. Dr. Gülbin Dural Ünver<br>Dean, Graduate School of Natural and Applied Sciences |                  |

|---------------------------------------------------------------------------------------|------------------|

| Prof. Dr. Altuğ Özpineci<br>Head of Department, Department of Physics                 |                  |

| Prof. Dr. Rașit Turan<br>Supervisor, Department of Physics, METU                      |                  |

| Examining Committee Members:                                                          |                  |

| Prof. Dr. Çiğdem Erçelebi<br>Physics Dept., METU                                      |                  |

| Prof. Dr. Rașit Turan<br>Physics Dept., METU                                          |                  |

| Assoc. Prof. Dr. Alpan Bek<br>Physics Dept., METU                                     |                  |

| Asst. Prof. Dr. Selçuk Yerci<br>EEE Dept., METU                                       |                  |

| Assoc. Prof. Dr. Nurdan Demirci Sankır<br>MSNT Dept., TOBB ETU                        |                  |

|                                                                                       | Date: 08/09/2017 |

I hereby declare that all information in this document has been obtained and presented in accordance with academic rules and ethical conduct. I also declare that, as required by these rules and conduct, I have fully cited and referenced all material and results that are not original to this work.

Name, Last name: Doğuşcan Ahiboz

Signature:

#### ABSTRACT

# ELECTRICAL CHARACTERIZATION OF ELECTRON SELECTIVE TITANIUM DIOXIDE AND HOLE SELECTIVE MOLYBDENUM TRIOXIDE HETEROCONTACTS ON CRYSTALLINE SILICON

Ahiboz, Doğuşcan

M. S., Department of Physics

Supervisor: Prof. Dr. Raşit Turan

September 2017, 79 pages

Transition metal oxides are promising materials as an alternative to the conventional charge transport layers in photovoltaic solar cells with the advantages of carrier selectivity and low processing temperatures. In this study, electronic properties of the hole transporting – electron blocking layer (HT-EBL) of sub-stoichiometric Molybdenum (III) Oxide ( $MoO_{3-x}$ ) and electron transporting – hole blocking layer (ET-HBL) of Titanium (II) Oxide ( $TiO_{2-x}$ ) were studied. For this purpose, carrier selective metal oxide layers with different thickness and deposition conditions were deposited over n-type and p-type crystalline silicon wafers in the structure of Metal-Oxide-Semiconductor (MOS) capacitor. Admittance analysis (capacitance and conductance methods) and current – voltage methods were employed for the characterization of the MOS capacitors. At the end of this study, best deposition

condition and the metal oxide thickness for the most effective carrier transportation at the silicon – metal oxide interface and through the metal oxide layer were determined.

**Keywords:** Sub-stoichiometric Titanium Dioxide, Sub-stoichiometric Molybdenum Trioxide, Admittance Measurement, Current Voltage Measurement, Hole Selectivity, Electron Selectivity.

## ÖZ

# SİLİSYUM ALTTAŞ ÜZERİNDE BÜYÜTÜLMÜŞ, ELEKTRON GEÇİRGEN TİTANYUM DİOKSİT VE HOL GEÇİRGEN MOLİBDEN TRİOKSİT İNCE FİLM TABAKALARININ ELEKTRİKSEL KAREKTERİZASYONU

Ahiboz, Doğuşcan

Yüksek Lisans, Fizik Bölümü

Tez Yöneticisi: Prof. Dr. Raşit Turan

Eylül 2017, 79 sayfa

Düşük sıcaklıkta üretim ve seçici yük geçirgenliği üstünlüğü taşıyan geçiş metallerinin oksitleri, fotovoltaik güneş gözelerinde geleneksel olarak kullanılan yük taşıyıcı tabakaların umut veren bir alternatifidir. Bu araştırmada, eksik katlı Molibden (III) Oksiti'nin hol geçirgen – elektron engelleyici ve Titanyum (II) Oksiti'nin elektron geçirgen – hol engelleyici tabakalarının elektronik özellikleri çalışıldı. Bu amaç için metal oksitler, n-tipi ve p-tipi silisyum alt taş üzerinde farklı koşullar altında ve tabaka kalınlıklarında Metal - Oksit – Yarı İletken (MOS) Kapasitörler yapmak üzere büyütüldü. MOS kapasitörlerin karakterizasyonu için Admitans Analizi (kapasitans ve iletkenlik yöntemleri) ve Akım – Gerilim yöntemleri kullanılmıştır. Bu çalışmanın sonucunda silisyum – metal oksit ara yüzeyinde ve metal oksit tabakası boyunca en etkili yük iletimini sağlamak için gerekli olan ideal metal oksit tabaka büyütme şartları ve tabaka kalınlığı tespit edilmiştir.

Anahtar kelimeler: eksik katlı titanyum dioksit, eksik katlı molibden trioksit, admitans ölçümü, akım gerilim ölçümü, elektron geçirgenliği, hol geçirgenliği.

To my family

#### ACKNOWLEDGMENTS

First and foremost I offer my heartfelt gratitude to my supervisor, Prof. Dr. Raşit Turan, who has supported me during the course of my thesis with his patience and knowledge at the same time as allowing me the room to work in my own way. I attribute the level of my Masters degree to his encouragement and effort and without him this thesis, too, would not have been completed.

I would like to thank Dr. Hisham Nasser who encouraged me to study transition metal oxide, for many perceptive conversations during the development of the ideas in this thesis, and for helpful comments and reviews on the text.

I am much obliged to GÜNAM members Prof. Dr. Mehmet Parlak, Hande Emine Çiftpınar, Dr. Fırat Es, and Ergi Dönerçark for their help during my research. I am also highly grateful to Dr. Özlen Ferruh for her guidance and valuable comments.

I am very thankful to my precious friends Gilda Afshari (Zerrin Taş), Nevra Akalın,Merve Akkaya, Erolcan Akbaba, Koray Kaymazlar and Fırat Yalçın who I spent my years together at the physics department

I feel very lucky to have valuable friendship and support of Yasemin Durmuş, Havle Güney, Serra Memiş, Başak Sezgi Bilen. I appreciate the joy Araylım Gaipova and my beloved bacanak Okan Ata Küçük brought to my house while I am dealing with this thesis.

My uttermost gratitude to Özge Azeri for her love, patience and invaluable support which have been encouraging me in my professional and personal life. It is my greatest honor and biggest happiness to have her in my life.

The last but not the least, specials thanks to my mother Feriha Gül supporting me whenever I need her, and my grandparents who brought me up with love and encouragement - Saadet Gül and Ahmet Kaya Gül. I would like to thank all members of my family for their continuous affection and heartening.

# TABLE OF CONTENT

| ABSTRACT             | v    |

|----------------------|------|

| ÖZ                   | vii  |

| ACKNOWLEDGMENTS      | x    |

| TABLE OF CONTENT     | xi   |

| LIST OF TABLES       | xiii |

| LIST OF FIGURES      | xiv  |

| LIST OF ABBREVATIONS | xvii |

# CHAPTERS

| 1. INTRO | DUCTION                                                 | 1  |

|----------|---------------------------------------------------------|----|

| 1.1. Ser | miconductor Heterojunctions                             | 2  |

| 1.1.1.   | Band Alignment of Heterojunctions                       | 3  |

| 1.1.2.   | Current Characteristics of a Heterojunction             | 6  |

| 1.1.3.   | Capacitance of a Heterojunction                         | 16 |

| 1.1.4.   | Differential Conductance of a Heterojunction            | 21 |

| 1.2. Me  | etal – Oxide – Semiconductor Capacitors                 | 22 |

| 1.2.1.   | Equilibrium Under Applied External Potential Difference | 23 |

| 1.2.2.   | Charges Trapped at Interface and Inside Oxide Layer     | 29 |

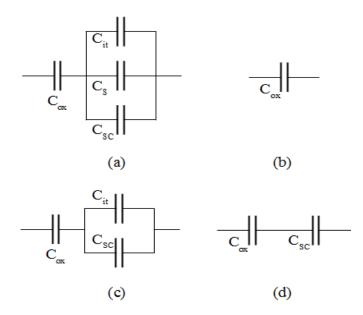

| 1.2.3.   | Equivalent Circuit Models of MOS Capacitor.             | 31 |

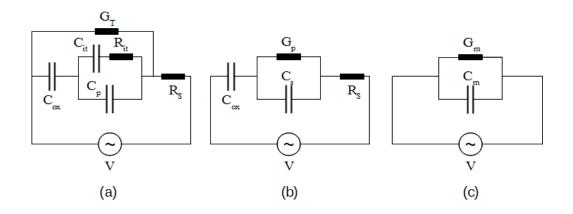

| 1.2.4.   | Admittance of a MOS Capacitor                           | 33 |

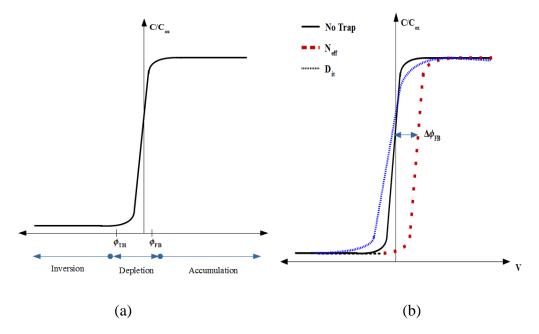

| 1.2.5.   | High-Frequency Curve of a MOS Capacitor                 | 36 |

| 1.2.6.   | The Conductance Method                                  | 37 |

| 1.3. Ele | ectrical Conduction in Amorphous Semiconductors         | 39 |

| 1.4. Tra            | unsition Metal Oxides41                                                    |

|---------------------|----------------------------------------------------------------------------|

| 1.4.1.              | Sub-stoichiometric Titanium Dioxide41                                      |

| 1.4.2.              | Sub-Stoichiometric Molybdenum Trioxide43                                   |

| 2. EXPER            | IMENTAL DETAILS                                                            |

| 2.5. De             | vice Preparation45                                                         |

| 2.5.1.              | Crystalline Silicon Wafer Preparation45                                    |

| 2.5.2.              | Titanium Dioxide Thin Film Atomic Layer Deposition45                       |

| 2.5.3.              | Molybdenum Trioxide Deposition by Thermal Evaporation47                    |

| 2.5.4.              | Metallization                                                              |

| 2.6. De             | vice Characterization                                                      |

| 2.6.1.              | Electrical Transport Measurements                                          |

| 2.6.2.              | Optical Measurements                                                       |

| 3. RESUL            | TS & DISCUSSION                                                            |

| 3.1. Ele            | ectron Selective Atomic layer Deposited TiO2-x/cSi Metal-Oxide-            |

| Semicono            | luctor-Capacitor                                                           |

| 3.1.1.              | Effect of ALD Temperature on Electrical Properties of the TiO2-            |

| <sub>x</sub> /cSi N | IOS Capacitors53                                                           |

| 3.1.2.              | Effect of PDA on $TiO_{2-x}$ / n-type- cSi MOS Capacitor with ALD at       |

| 250°C               |                                                                            |

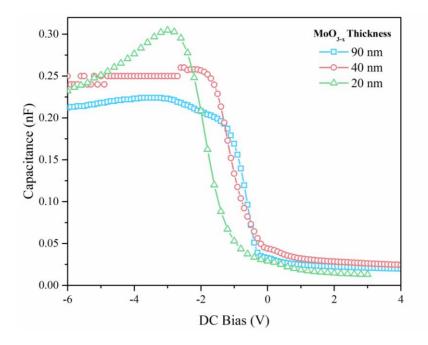

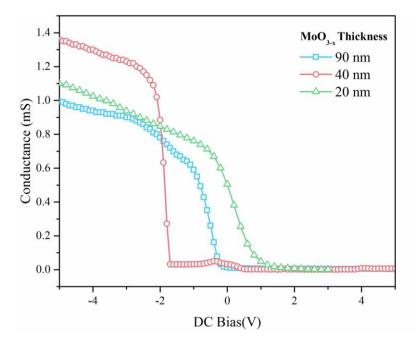

| 3.2. Но             | le Selective Thermally Evaporated MoO <sub>3-x</sub> /cSi MOS Capacitor 63 |

| 3.2.1.              | Effect of MoO <sub>3-x</sub> Thickness                                     |

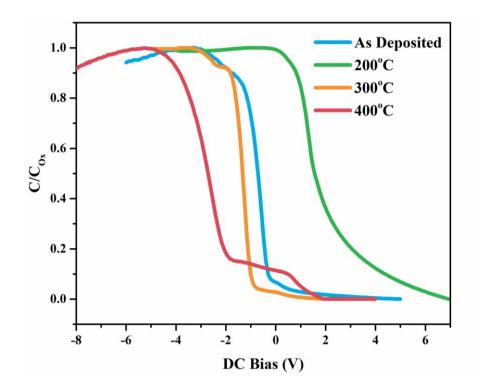

| 3.2.2.              | Effect of PDA on P-Type MoO <sub>3-x</sub> / cSi MOS Capacitor66           |

| 4. CONCI            | LUSIONS71                                                                  |

| REFERENC            | ZES                                                                        |

# LIST OF TABLES

| Table 1. Measured electrical parameters of $TiO_{2-x}$ /n-tye cSi MOS capacitors with                  |

|--------------------------------------------------------------------------------------------------------|

| different ALD temperature                                                                              |

| Table 2. Measured electrical parameters of TiO2-x /n-tye with 250 ALD temperature                      |

| before and after PDA cSi MOS capacitors with different ALD temperature60                               |

| Table 3. Effect of the MoO <sub>3-x</sub> thickness on MoO <sub>3-x</sub> / p-type cSi MOS capacitors' |

| electrical parameters                                                                                  |

| <b>Table 4.</b> Effect of the PDA on the electrical properties of 90 nm p-type $MoO_{3-x} - cSi$       |

| MOS capacitor                                                                                          |

# LIST OF FIGURES

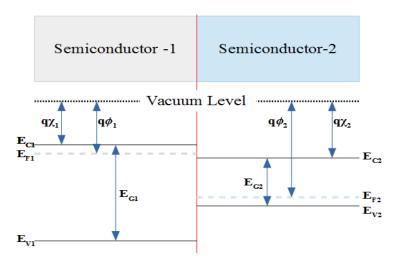

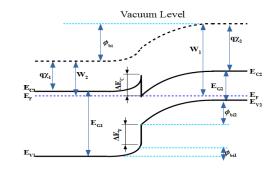

| Figure 1. Band diagram of two distinct semiconductors before heterojunction            |

|----------------------------------------------------------------------------------------|

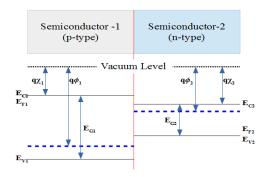

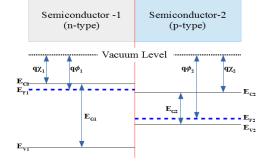

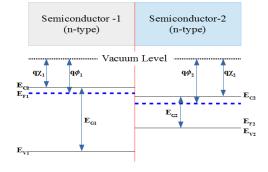

| formation                                                                              |

| Figure 2. Energy levels before heterojunction formation (left) and band alignments     |

| of (a) p-n, (b) n-p, (c) n-n, (d) p-p semiconductors4                                  |

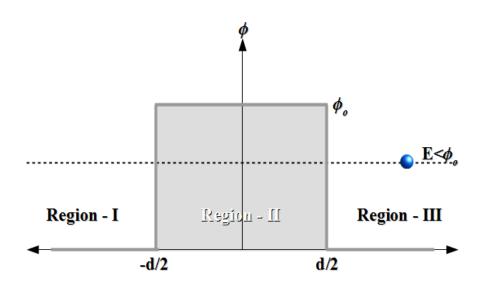

| Figure 3. A step function for a particle with an energy less then barrier height 11    |

| Figure 4. A generic potential barrier approximated as infinitesimal rectangular        |

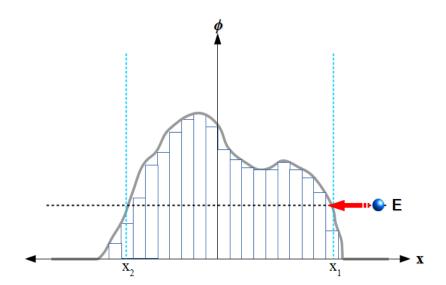

| potential barriers                                                                     |

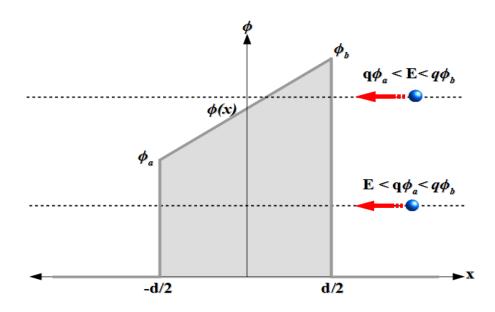

| Figure 5. Direct and Fowler-Nordheim tunneling through barrier15                       |

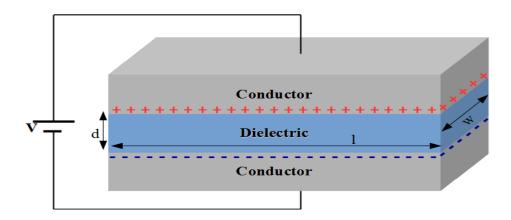

| Figure 6. Schematic diagram of a parallel plate cpacitor                               |

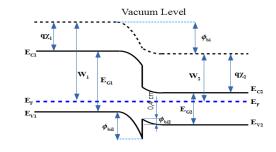

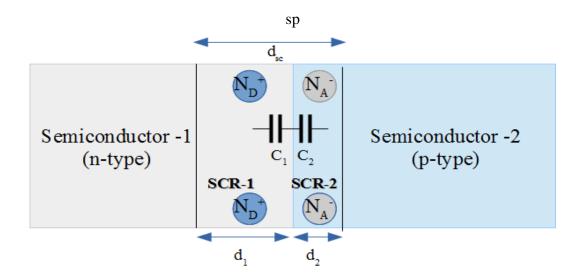

| Figure 7. Space –charge region of an isotype heterojunction                            |

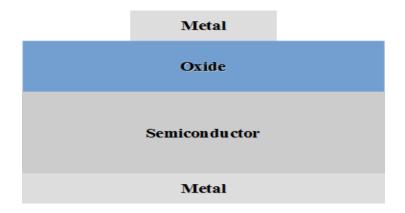

| Figure 8. A schematic of a typical MOS capacitor                                       |

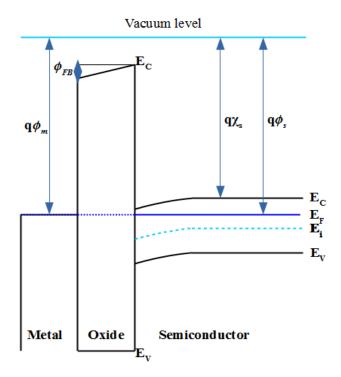

| Figure 9. Band diagram of an ideal MOS capacitor at equilibrium without any external   |

| applied potential difference                                                           |

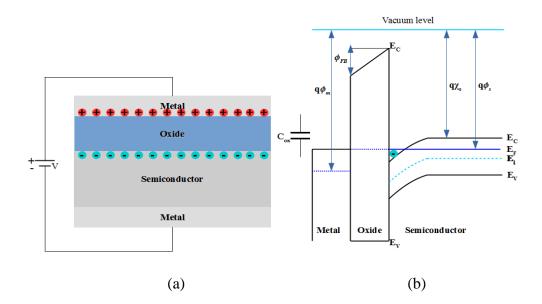

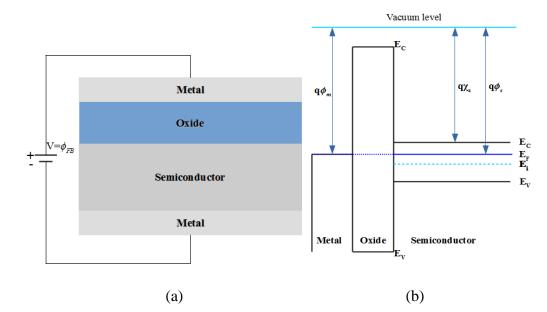

| Figure 10. MOS capacitor at accumulation condition (a) charge distribution over MOS    |

| capacitor, (b) band diagram                                                            |

| Figure 11. MOS capacitor at flat band condition (a) charge distribution over MOS       |

| capacitor, (b) band diagram                                                            |

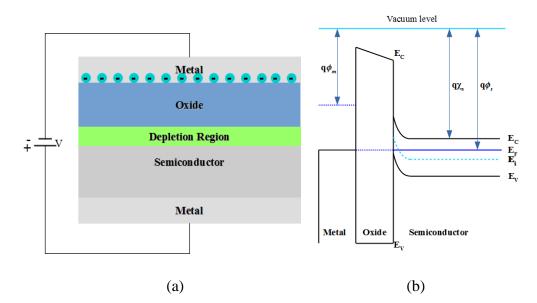

| Figure 12. MOS capacitor at depletion condition (a) charge distribution over MOS       |

| capacitor, (b) band diagram27                                                          |

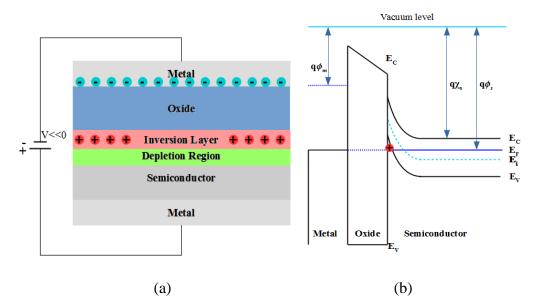

| Figure 13. MOS capacitor at inversion condition (a) charge distribution over MOS       |

| capacitor, (b) band diagram                                                            |

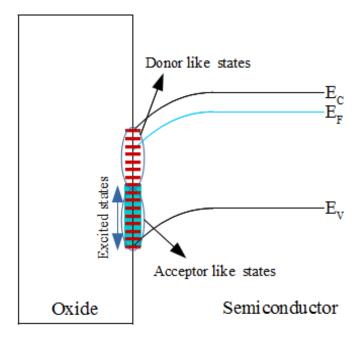

| Figure 14. Oxide – semiconductor interface in the presence of interface trapped states |

|                                                                                        |

| Figure 15. PPC circuit models for a MOS capacitor; (a) general form, (b)               |

| accumulation, (c) depletion, (d) inversion                                             |

| Figure 16. Equivalent circuits of a MOS capacitor; (a) exact, (b) simplified, (c)      |

| measured                                                                               |

| <b>Figure 17.</b> High frequency capacitance–voltage curves of an n–type MOS capacitor;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (a) without traps charges, (b) with oxide charges and interface trapped charges 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Figure 18. Density of electronic states in an amorphous semiconductor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

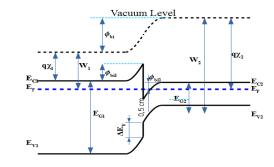

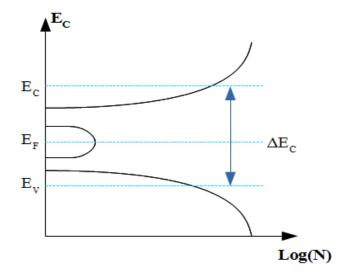

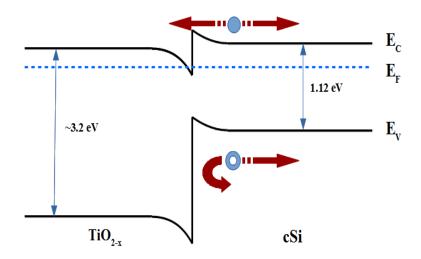

| <b>Figure 19.</b> Energy band diagram of n-n isotype $TiO_{2-x}$ – cSi heterojuncion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

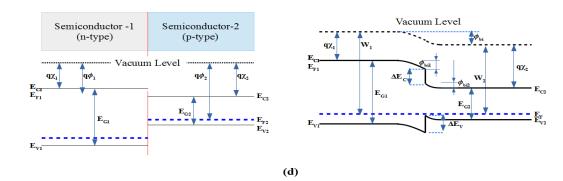

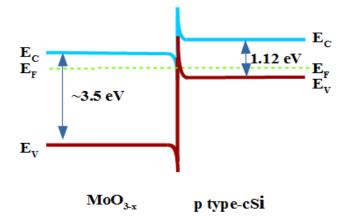

| <b>Figure 20.</b> Energy band diagram of $MoO_{3-x}$ /p-type cSi n-p anisotype heterojunction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

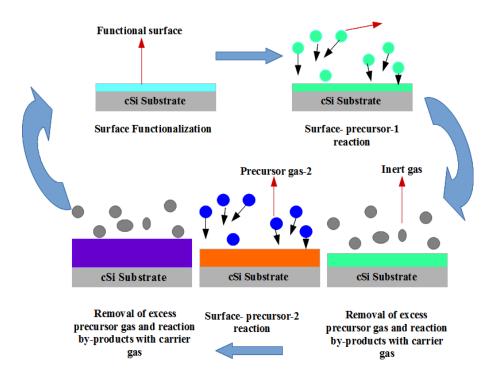

| Figure 21. Atomic layer deposition cycle       46         Figure 21. Atomic layer deposition cycle       47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

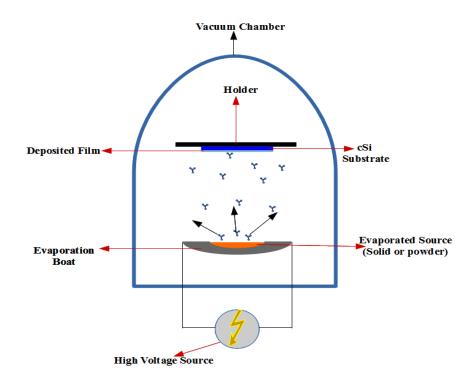

| Figure 22. Thermal evaporation deposition mechanism    47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

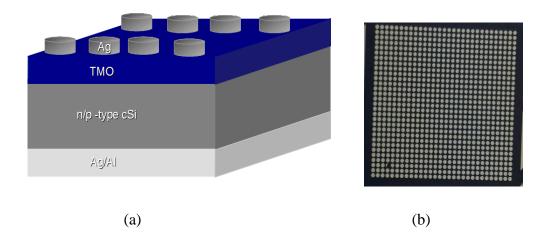

| Figure 23. (a) Schematic of Transition Metal-Oxide-Semiconductor (TMOS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| capacitor(b) actual device (top view)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

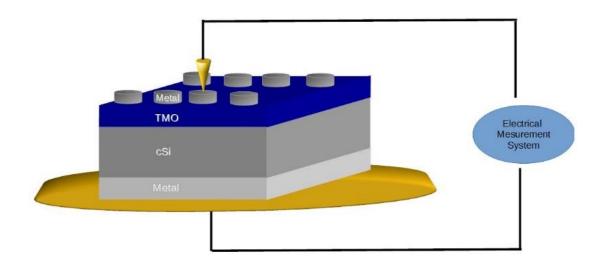

| Figure 24. Electrical measurement setup schematics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

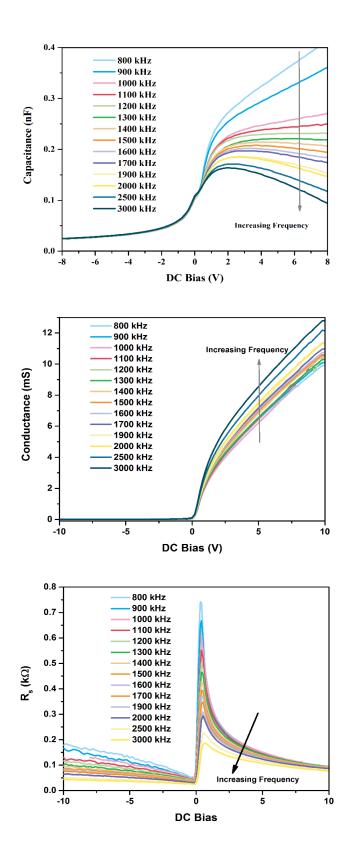

| Figure 25. (a) C-V, (b) G-V, and (c) $R_s$ -V high frequency hysteresis curves of n-type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| TiO <sub>2-x</sub> MOS capacitor deposition at 200°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

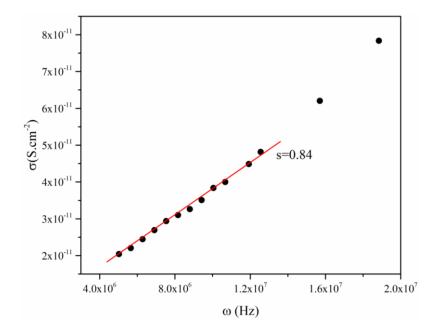

| Figure 26. $\sigma$ - $\omega$ graph of n-type TiO <sub>2-x</sub> MOS capacitor deposited at 200°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

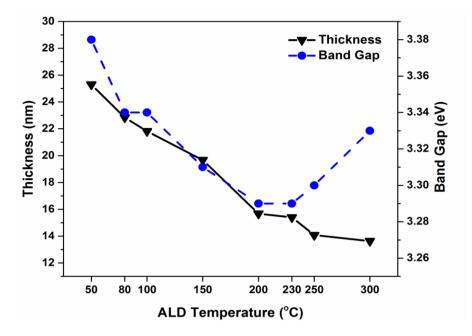

| Figure 27. Thickness and band gap of the TiO <sub>2-x</sub> prepared at different deposition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| temperatures as measured by spectroscopic ellipsometry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

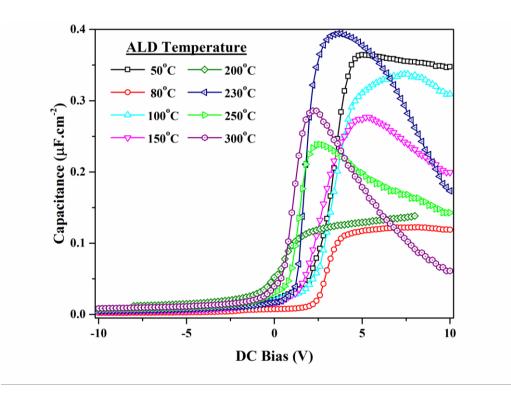

| Figure 28. C-V characteristics of the $TiO_{2-x} - cSi MOS MOS$ capacitors with different                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ALD temperatures under 1MHz AC modulation frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

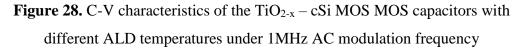

| Figure 29. J-V curves in semi-log scale for the MOS capacitors with different                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| deposition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

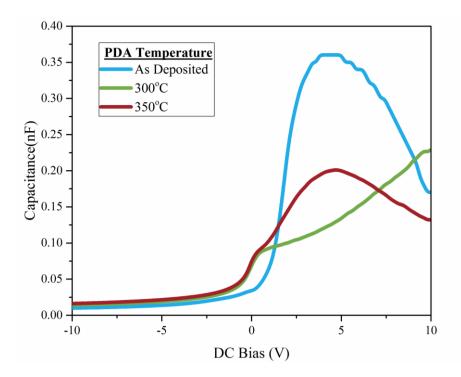

| Figure 30. C-V curves of the TiO <sub>2-x</sub> / n-type- cSi MOS capacitors with 250°C ALD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| temperature annealed at 300°C and 350°C under 1MHz AC modulation frequency59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

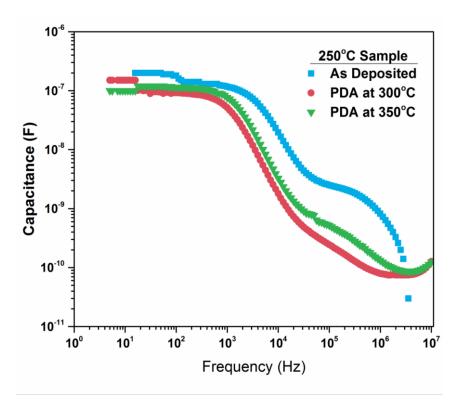

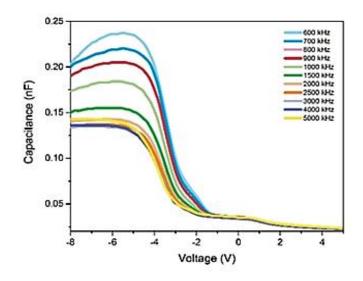

| Figure 31. Frequency dependence of the accumulation capacitance of the MOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| capacitor deposited at 250°C and treated with different post-deposition temperatures.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

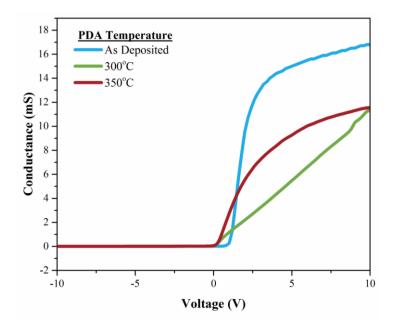

| <b>Figure 32.</b> G-V curves of the TiO <sub>2-x</sub> / n-type- cSi MOS capacitors with 250°C ALD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| temperature annealed at 300°C and 350°C under 1MHz AC modulation frequency62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

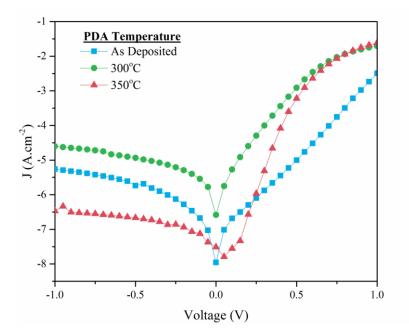

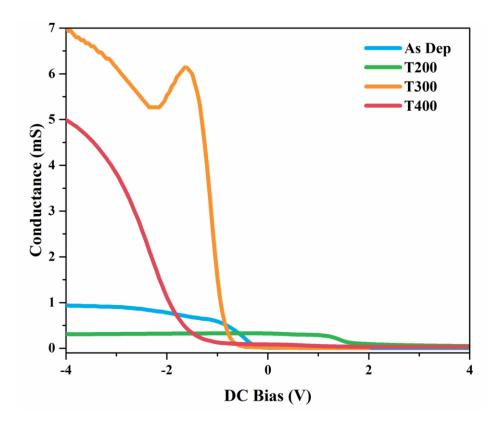

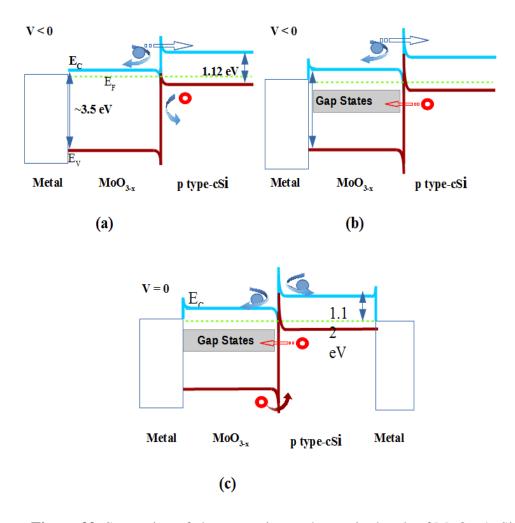

| <b>Figure 33.</b> J-V curves of the $TiO_{2-x}$ / n-type- cSi MOS capacitors with 250°C ALD temperature encoded at 200°C and 250°C (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) (200°C) |