# OPENCL IMPLEMENTATION OF MONTGOMERY MULTIPLICATION ON FPGA

## A THESIS SUBMITTED TO THE GRADUATE SCHOOL OF NATURAL AND APPLIED SCIENCES OF MIDDLE EAST TECHNICAL UNIVERSITY

BY

# MEHMET UFUK BÜYÜKŞAHIN

## IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE IN ELECTRICAL AND ELECTRONICS ENGINEERING

SEPTEMBER 2014

### Approval of the thesis:

# OPENCL IMPLEMENTATION OF MONTGOMERY MULTIPLICATION ON FPGA

submitted by **MEHMET UFUK BÜYÜKŞAHIN** in partial fulfillment of the requirements for the degree of **Master of Science** in **Electrical and Electronics Engineering Department, Middle East Technical University** by,

| Prof. Dr. Canan Özgen<br>Dean, Graduate School of <b>Natural and Applied Sciences</b>                   |  |

|---------------------------------------------------------------------------------------------------------|--|

| Prof. Dr. Gönül Turhan Sayan<br>Head of Department, <b>Electrical and Electronics Engineering</b>       |  |

| Assoc. Prof. Dr. Cüneyt F. Bazlamaçcı<br>Supervisor, <b>Electrical and Electronics Eng. Dept., METU</b> |  |

| Examining Committee Members:                                                                            |  |

|                                                                                                         |  |

| Prof. Dr. Semih Bilgen<br>Electrical and Electronics Engineering Department, METU                       |  |

| Assoc. Prof. Dr. Cüneyt F. Bazlamaçcı<br>Electrical and Electronics Engineering Department, METU        |  |

| Prof. Dr. Gözde B. Akar<br>Electrical and Electronics Engineering Department, METU                      |  |

| Assoc. Prof. Dr. Ece Güran Schmidt<br>Electrical and Electronics Engineering Department, METU           |  |

| Assoc. Prof. Dr. Alptekin Temizel<br>Graduate School of Informatics, METU                               |  |

|                                                                                                         |  |

Date:

I hereby declare that all information in this document has been obtained and presented in accordance with academic rules and ethical conduct. I also declare that, as required by these rules and conduct, I have fully cited and referenced all material and results that are not original to this work.

Name, Last Name: MEHMET UFUK BÜYÜKŞAHIN

Signature :

# ABSTRACT

# OPENCL IMPLEMENTATION OF MONTGOMERY MULTIPLICATION ON FPGA

Büyükşahin, Mehmet Ufuk M.S., Department of Electrical and Electronics Engineering Supervisor : Assoc. Prof. Dr. Cüneyt F. Bazlamaçcı

September 2014, 79 pages

Galois Field arithmetic has been used very frequently in popular security and errorcorrection applications. Montgomery multiplication is among the suitable methods used for accelerating modular multiplication, which is the most time consuming basic arithmetic operation. Montgomery multiplication is also suitable to be implemented in parallel.

OpenCL, which is a portable, heterogeneous and parallel programming framework, is recently supported by a major FPGA vendor, Altera. Therefore it is now possible to exploit the advantages of using both FPGA and C based OpenCL language simulataneously.

In this thesis, Montgomery multiplication algorithm is implemented on FPGA using OpenCL programming language. Performance of the proposed FPGA implementation is evaluated and compared with CPU and GPU platforms. Using different OpenCL specific directives, several FPGA configurations corresponding to different parallel architectures are implemented for different multiplication sizes.

Keywords: Parallel Programming, OpenCL on FPGA, Montgomery Multiplication

## OPENCL İLE FPGA ÜZERİNDE MONTGOMERY ÇARPIMININ GERÇEKLENMESİ

Büyükşahin, Mehmet Ufuk Yüksek Lisans, Elektrik ve Elektronik Mühendisliği Bölümü Tez Yöneticisi : Doç. Dr. Cüneyt F. Bazlamaçcı

Eylül 2014, 79 sayfa

Galois alanı aritmetiği, popüler güvenlik ve hata düzeltme uygulamaları içinde sıklıkla kullanılmaktadır. En çok zaman alan temel arithmetik operasyonu olan modüler çarpma işlemi için de Montgomery çarpma işlemi uygun metotlar arsındadır. Montgomery çarpması paralellel gerçekleştirme için de uygundur.

Taşınabilir, heterojen ve paralel programlama çerçevesi sunan OpenCL, artık önemli FPGA üreticisi Altera tarafından desteklenmektedir. Böylece, uygulamalarda hem FPGA'in hem de C tabanlı OpenCL dilinin avantajlarından beraberce yararlanmak mümkündür.

Bu tez çalışmasında, Montgomery algoritması OpenCL programlama dili ile FPGA üzerinde gerçeklenmiştir. Önerilen FPGA gerçeklemesinin başarımı, CPU ve GPU platformları ile karşılaştırılmıştır. OpenCL'e özel direktiflerle, farklı paralel yapılar çeşitli çarpma boyutları için gerçeklenmiştir.

Anahtar Kelimeler: Paralel Programlama, FPGA üzerinde OpenCL, Montgomery Çarpma

To my family and friends

# ACKNOWLEDGMENTS

First of all, I would like to express my gratitude to my family for their love, support and patience over the years.

I sincerely thank my supervisor Assoc. Prof. Dr. Cüneyt F. Bazlamaçcı for all his guidance and support throughout my study.

I would like to thank to my employer, ASELSAN for supporting me.

I also express my gratitude to TÜBİTAK BİDEB "National Scholarship Program for MSc Students".

Finally, I would like to thank my friends Nusret Bayhan, Cem Tarhan and Ömer Alper Özkan for their support and letting me use their computers.

Last but not least, I would like to thank Gizem Kocalar for her support throughout the study.

# **TABLE OF CONTENTS**

| ABSTRA  | СТ     |          |              |     |      |      |      |      | •      |                |         | •  | <br>• | • | <br>V   | V |

|---------|--------|----------|--------------|-----|------|------|------|------|--------|----------------|---------|----|-------|---|---------|---|

| ÖZ      |        |          |              |     |      |      |      |      |        |                |         | •  |       | • | <br>v   | i |

| ACKNO   | WLEDG  | MENTS .  |              |     |      |      |      |      | •      |                |         | •  |       |   | <br>vii | i |

| TABLE ( | OF CON | TENTS .  |              |     |      |      |      |      | •      |                |         | •  |       |   | <br>iz  | X |

| LIST OF | TABLE  | S        |              |     |      |      |      |      | •      |                |         | •  |       | • | <br>xii | i |

| LIST OF | FIGUR  | ES       |              |     |      |      |      |      | •      |                |         | •  |       | • | <br>xiv | V |

| LIST OF | ALGO   | RITHMS . |              |     |      |      |      |      | •      |                |         | •  |       | • | <br>XV  | i |

| LIST OF | ABBRI  | EVIATION | IS           |     |      |      |      |      | •      |                |         | •  |       | • | <br>xvi | i |

| CHAPTE  | ERS    |          |              |     |      |      |      |      |        |                |         |    |       |   |         |   |

| 1       | INTRO  | DUCTION  | ι            |     |      |      |      |      |        |                |         |    |       | • | <br>]   | 1 |

| 2       | BACKO  | GROUND   |              |     |      |      |      |      | •      |                |         | •  |       |   | <br>-   | 7 |

|         | 2.1    | Mathema  | tical Backgr | oun | nd.  |      |      |      |        |                |         |    |       | • | <br>-   | 7 |

|         |        | 2.1.1    | Galois Field | d.  |      |      |      |      |        |                |         |    |       | • | <br>-   | 7 |

|         |        | 2.1.2    | Galois Field | d A | rith | met  | ic . |      |        |                |         | •  |       |   | <br>-   | 7 |

|         |        |          | 2.1.2.1      | A   | ddit | ion  | in ( | GF(  | $(2^m$ | $^{\imath})$ . |         | •  |       |   | <br>8   | 8 |

|         |        |          | 2.1.2.2      | Μ   | ulti | plic | atio | n ir | n G    | F(             | $2^{m}$ | ۱. |       | • | <br>Ģ   | 9 |

|   | 2.2   | Develop   | ment Enviror  | ment and Tools 10                                                     |

|---|-------|-----------|---------------|-----------------------------------------------------------------------|

|   |       | 2.2.1     | FPGA          |                                                                       |

|   |       |           | 2.2.1.1       | FPGA as Computation Unit 10                                           |

|   |       |           | 2.2.1.2       | CPUs in the FPGA 11                                                   |

|   |       |           | 2.2.1.3       | FPGA as an OpenCL Device 11                                           |

|   |       | 2.2.2     | OpenCL .      |                                                                       |

|   |       | 2.2.3     | OpenCL or     | n FPGA vs. GPU 13                                                     |

|   |       | 2.2.4     | Developme     | ent Environment                                                       |

|   |       |           | 2.2.4.1       | Host Application Development 16                                       |

|   |       |           | 2.2.4.2       | Kernel Development                                                    |

| 3 | RELAT | TED WOR   | К             |                                                                       |

|   | 3.1   | Multiplic | cation Algori | thms                                                                  |

|   |       | 3.1.1     | Karatsuba 1   | Multiplication                                                        |

|   |       | 3.1.2     | Karatsuba I   | Multiplication in $GF(2^m)$ 20                                        |

|   |       | 3.1.3     | Montgome      | ry Multiplication in $GF(2^m)$ 21                                     |

|   |       |           | 3.1.3.1       | Parallel Implementations of Montgomery<br>Multiplication              |

|   |       |           | 3.1.3.2       | Partitioning of Separated Operand Scan-<br>ning (SOS) Method          |

|   |       |           | 3.1.3.3       | Partitioning of Coarsely Integrated Operand<br>Scanning (CIOS) Method |

|   |       | 3.1.4     | -             | ion in $GF(2^m)$ using Residue Number NS)                             |

|   | 3.2 | FPGA Ir  | nplementatio   | ons of Various Galois Field Multipliers . 28 |

|---|-----|----------|----------------|----------------------------------------------|

|   |     | 3.2.1    | Logic Leve     | el Designs                                   |

|   |     | 3.2.2    | Soft Proces    | ssor Designs                                 |

|   | 3.3 | GPU Im   | plementation   | s                                            |

|   | 3.4 | Other M  | ulti-core Solu | utions                                       |

|   | 3.5 | Software | e Solutions .  |                                              |

| 4 |     |          |                | VALUATION OF MONTGOMERY MUL-<br>ING OPENCL   |

|   | 4.1 | Prelimin | ary Calculati  | ons                                          |

|   | 4.2 | Extended | d Euclidean A  | Algorithm                                    |

|   | 4.3 | Impleme  | entation       |                                              |

|   |     | 4.3.1    | Inputs and     | Outputs                                      |

|   |     | 4.3.2    | Kernel Attr    | ibutes                                       |

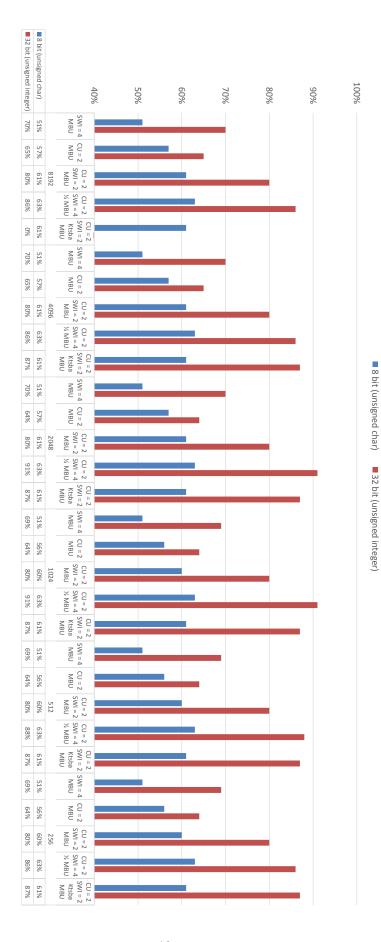

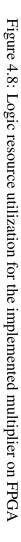

|   |     |          | 4.3.2.1        | FPGA Resource Usages 40                      |

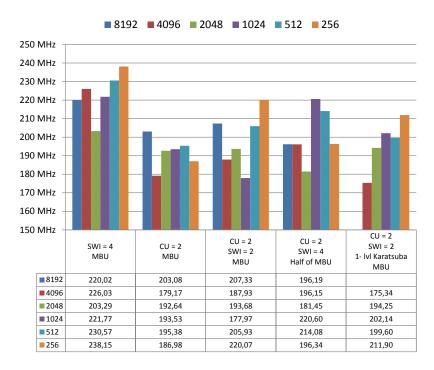

|   |     |          | 4.3.2.2        | Kernel Frequencies 41                        |

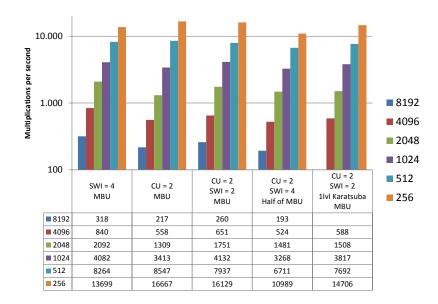

|   |     |          | 4.3.2.3        | Kernel Performances 43                       |

|   |     | 4.3.3    | Primitive S    | izes                                         |

|   |     | 4.3.4    | Offline Cor    | npilation                                    |

|   | 4.4 | Function | nal Testing.   |                                              |

|   |     | 4.4.1    | Reference      | Results                                      |

|   |     | 4.4.2    | Benchmark      | as and Profiling 53                          |

| 5      |       | ARISON OF OPENCL FPGA MONTGOMERY MULTIPLIER<br>GPU AND CPU PLATFORMS | 59 |

|--------|-------|----------------------------------------------------------------------|----|

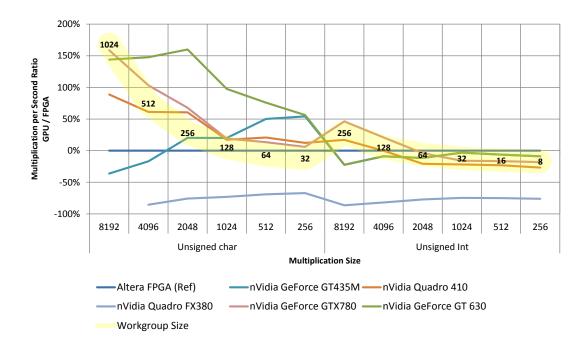

|        | 5.1   | Comparison with GPU                                                  | 59 |

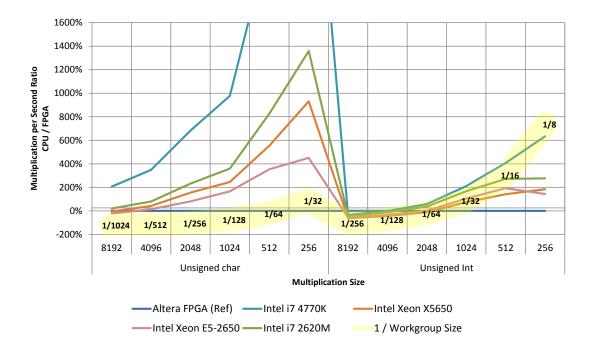

|        | 5.2   | Comparison with CPU                                                  | 62 |

|        | 5.3   | Comparison with other Implementations in the Literature              | 64 |

| 6      | CONCI | LUSION                                                               | 67 |

| REFERI | ENCES |                                                                      | 71 |

| APPENI | DICES |                                                                      |    |

| А      |       | CANT IRREDUCIBLE POLYNOMIALS (N) USED IN RE-<br>ON                   | 75 |

|        | A.1   | Multiplication size = 256                                            | 75 |

|        | A.2   | Multiplication size = 512                                            | 75 |

|        | A.3   | Multiplication size = 1024                                           | 75 |

|        | A.4   | Multiplication size = 2048                                           | 76 |

|        | A.5   | Multiplication size = 4096                                           | 76 |

|        | A.6   | Multiplication size = 8192                                           | 77 |

| В      | OPENC | CL CODE                                                              | 79 |

# LIST OF TABLES

# TABLES

| Table 4.1 | Chosen irreducible polynomials for different multiplication sizes                                                                               | 39 |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1024      | Comparison of area utilizations (in chip's resource percentage) of<br>bit Montgomery SOS algorithm implementations for different kernel<br>utes | 41 |

|           | Comparison performances (in multiplications per second) for dif-                                                                                |    |

| feren     | t kernel attributes                                                                                                                             | 44 |

| Table 4.4 | Multiplication size vs. work group sizes                                                                                                        | 47 |

| Table 5.1 | Specifications of GPUs tested                                                                                                                   | 60 |

| Table 5.2 | Specifications of CPUs tested                                                                                                                   | 63 |

|           | Comparison of performance of multiplier implementations in the ture.                                                                            | 65 |

# LIST OF FIGURES

# FIGURES

| Figure 1.1 | Tren in CPUs in terms of clock speed and number of cores $1 \ldots$                                                                                               | 3  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

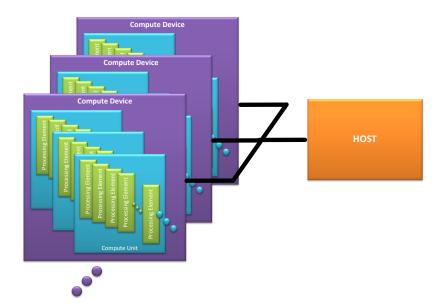

| Figure 2.1 | Overview of of OpenCL architecture [1]                                                                                                                            | 12 |

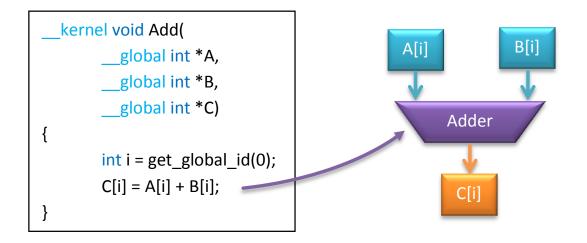

| Figure 2.2 | Simple OpenCL code mapped into custom logic [2]                                                                                                                   | 14 |

| Figure 2.3 | Branching in SIMD structure vs. pipeline structure [2]                                                                                                            | 14 |

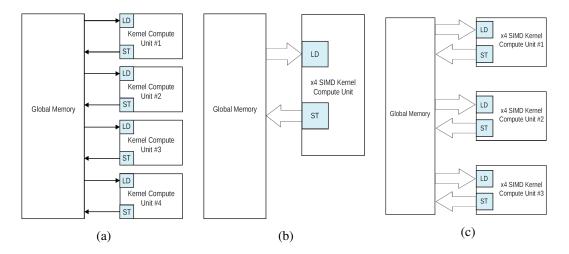

| Figure 2.4 | Multiple compute units vs. SIMD vs. both                                                                                                                          | 18 |

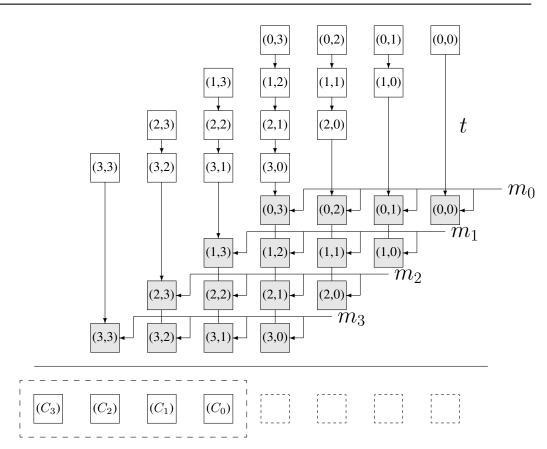

| Figure 3.1 | Data flow of Montgomery multiplication (SOS)                                                                                                                      | 25 |

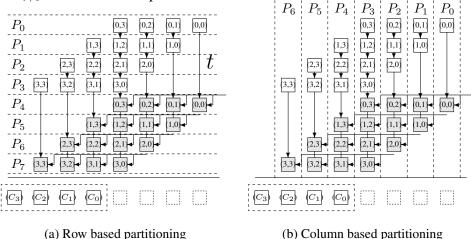

| Figure 3.2 | Partitioning of SOS given in algorithm 6                                                                                                                          | 26 |

| [3]. N     | An example flow of regular (left) and proposed (right) iterations in fultiplier sizes are given as $KOM_{SIZE}$ and number of multipliers s given next to arrows. | 29 |

| Figure 3.4 | An example implementation of [4] with four soft processor cores                                                                                                   | 31 |

| Figure 4.1 | Flow of Montgomery multiplication.                                                                                                                                | 37 |

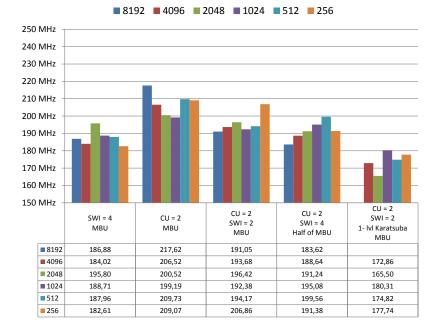

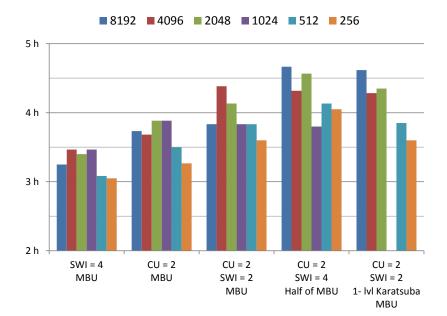

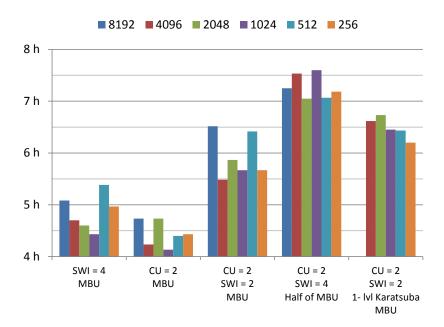

| U          | Comparison of implemented ( <i>unsigned char</i> ) kernel frequencies ferent kernel attributes and multiplication sizes                                           | 42 |

| -          | Comparison of implemented ( <i>unsigned int</i> ) Kernel frequencies for<br>ent kernel attributes and multiplication sizes                                        | 43 |

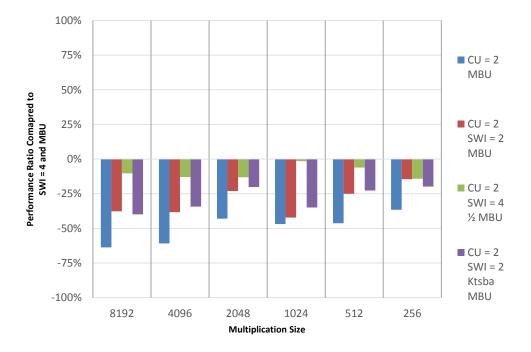

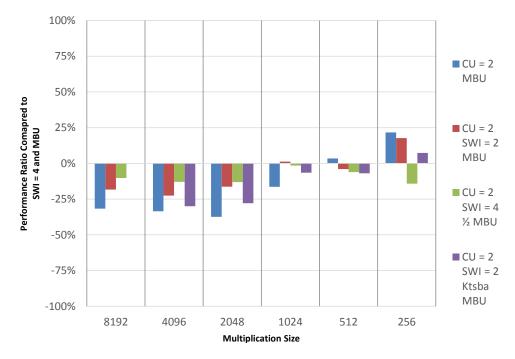

| -          | Comparison of normalized kernel performances for different kernel tes ( <i>unsigned char</i> )                                                                    | 44 |

| -          | Comparison of normalized kernel performances for different kernel tes ( <i>unsigned int</i> )                                                                     | 45 |

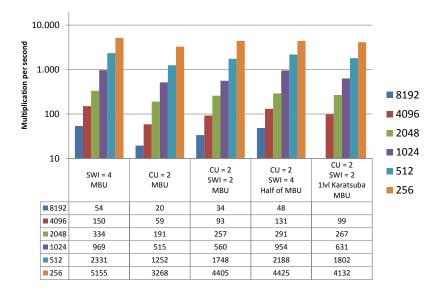

| e          | Comparison of Kernel performances for different multiplication <i>unsigned char</i> )                                                                             | 46 |

| e           | Comparison of Kernel performances for different multiplication <i>unsigned int</i> ) | 46 |

|-------------|--------------------------------------------------------------------------------------|----|

| Figure 4.8  | Logic resource utilization for the implemented multiplier on FPGA                    | 48 |

| Figure 4.9  | Memory utilization for the implemented multiplier on FPGA                            | 49 |

| Figure 4.10 | C# application for compilation                                                       | 50 |

| Figure 4.11 | Compilation times for <i>unsigned char</i> implementations                           | 51 |

| Figure 4.12 | Compilation times for <i>unsigned int</i> implementations                            | 51 |

| -           | A screenshot of multiplier application written in C# for functional                  | 53 |

| e           | Benchmark results (in microseconds) obtained by host application GA multiplier       | 55 |

| e           | Benchmark results (in microseconds) obtained by host application<br>U/GPU multiplier | 57 |

| Figure 5.1  | Performance comparison of FPGA implementation with GPUs                              | 61 |

| Figure 5.2  | Performance comparison of FPGA implementation with CPUs                              | 64 |

# LIST OF ALGORITHMS

# ALGORITHMS

| Algorithm 1 | Addition in $GF(2^m)$                             | 8  |

|-------------|---------------------------------------------------|----|

| Algorithm 2 | Multiplication in $GF(2^m)$                       | 9  |

| Algorithm 3 | Host application algorithm                        | 16 |

| Algorithm 4 | Karatsuba Multiplication in $GF(2^m)$             | 20 |

| Algorithm 5 | Montgomery Product                                | 22 |

| Algorithm 6 | Montgomery product with SOS method                | 25 |

| Algorithm 7 | Montgomery product with CIOS method               | 27 |

| Algorithm 8 | Montgomery multiplication over trinomial residues | 28 |

| Algorithm 9 | Extended Euclidean Algorithm                      | 36 |

# LIST OF ABBREVIATIONS

| AOC    | Altera Offline Compiler                                                                          |

|--------|--------------------------------------------------------------------------------------------------|

| AOCL   | Altera OpenCL                                                                                    |

| API    | Application programming interface                                                                |

| ASIC   | Application-specific integrated circuit                                                          |

| CPU    | Central processing unit                                                                          |

| CvP    | Configuration via Protocol                                                                       |

| CRC    | Cyclic redundancy check                                                                          |

| DSP    | Digital signal processor                                                                         |

| FPGA   | Field-programmable gate array                                                                    |

| GF     | Galois Field                                                                                     |

| GPU    | Graphics processing unit                                                                         |

| JTAG   | Joint Test Action Group, IEEE 1149.1 Standard Test Access<br>Port and Boundary-Scan Architecture |

| LUT    | Lookup table                                                                                     |

| NIST   | National Institute of Standards and Technology                                                   |

| OpenCL | Open Computing Language                                                                          |

| PCIe   | PCI Express (Peripheral Component Interconnect Express)                                          |

| RNS    | Residue number system                                                                            |

| SDK    | Software development kit                                                                         |

| SIMD   | Single instruction multiple data                                                                 |

| SoC    | System on chip                                                                                   |

# **CHAPTER 1**

# **INTRODUCTION**

Computers, laptops, mobile devices became very important in our daily life. Most of the time those devices are connected to each other via Internet. One can watch video, listen to music, do some work, store pictures, communicate with relatives/friends, etc. and possibilities are unlimited. It is also possible to work on sensitive or even confidential information. For example, on-line banking can save time and money by eliminating the need to drive to an ATM, which is available in a 7/24 fashion.

However, all those possibilities would be practical if they are reliable. No one would like sensitive information, pictures/videos of memories to be lost or even worse, stolen. Therefore reliability and security are very important topics for our daily used devices. Security is a very important issue especially for connected devices. Reliability and security attributes have to be provided in a fast and efficient manner.

**Reliability:** Some extra information is used in order to increase reliability in an application. This redundant information is often called error-correcting codes. There are many methods for generating and decoding of error-correcting codes [5]. Cyclic redundancy check (CRC) is one of the most commonly used error-detecting method. CRC is used in basic hardware, mobile networks, dvd/blu-ray players, hard drives, Internet communication, etc.<sup>1</sup>.

**Security:** Sensitive information should be protected against eavesdropping. It might not always be possible to prevent eavesdropping, especially when the transfer medium

<sup>&</sup>lt;sup>1</sup> Some examples: CRC-1, parity bit in basic hardware; CRC-6-CDMA2000, CRC-10-CDMA2000, CRC-12-CDMA2000, CRC-16-CDMA2000, CRC-30 in mobile networks; CRC-32 in Ethernet/Internet communication, Reed-Solomon coding in storage

is air as in wireless communication. Data can also be transferred through unknown networks as in the Internet. Therefore, information is encrypted into some other form such that unwanted third-parties cannot understand it. Some widely used cryptographic systems are RSA<sup>2</sup>, ECC (Elliptic Curve Cryptography), Schnorr signature, PGP (Pretty Good Privacy), AES (Advanced Encryption Standard), DES (Data Encryption Standard), etc.

**Speed:** Both redundant information for reliability and encryption/decryption for security are required to protect sensitive information. Unfortunately, both operations are computationally time consuming and are complex problems. No one would like to have huge delays in secure communication. Long waiting times during on-line secure banking/shopping that drains battery or secure but slow-motion DVD movie, etc. are not generally acceptable. Therefore, developing efficient algorithms in this domain is crucial.

Many of those algorithms such as RSA, ECC, Reed-Solomon coding, CRC etc. have mathematical basics on Galois Field. Therefore, it is important to accelerate operations in Galois Field to improve overall performance in such cryptographic and checksum algorithms. Thus Galois Field multiplication, which is one of the most time consuming operations in Galois Field, is a very hot topic.

Unfortunately, these Galois Field operations are computationally intensive calculations. Therefore, usually custom hardware solutions are preferred. Alternatively, parallel processing capabilities of recent processing devices with high processing power can be utilized.

Parallel programming has always been a trendy topic and still is in recent years. This is mainly due to the fact that major CPU manufacturers tend to produce CPUs that have more cores rather than having higher clock frequencies to increase performance as shown in Figure 1.1.

$<sup>^2</sup>$  RSA: initials of surnames of inventors, Ron Rivest, Adi Shamir, and Leonard Adleman

Figure 1.1: Tren in CPUs in terms of clock speed and number of cores <sup>3</sup>

This trend also leads graphics processing units (GPUs) to be used in general purpose programming. Results are quite promising since GPUs can offer very high computation power compared to CPUs [6].

Parallelism is offered by FPGAs as well. Additionally, FPGAs provide better flexibility compared to GPUs and CPUs. FPGAs can perform custom and high speed I/O operations. Major FPGA manufacturers introduced advanced I/O capabilities in their products. Modern FPGAs support PCIe, SATA, SAS, 10G-Ethernet, RapidIO, SDI, DDR, QDR connection interfaces [7]. FPGAs are already widely used in the industry to perform special tasks at a low supply cost. However, they lack ease of programming. Therefore development process is longer and usually more complicated than CPU/GPU development.

With recent improvements in FPGA development tools, major FPGA manufacturers start offering OpenCL support on their FPGAs. Altera already supports OpenCL on FPGA development platforms starting from Quartus 13.0sp1. The other major company Xilinx will also provide OpenCL support in their 2014.1 version Vivado

<sup>&</sup>lt;sup>3</sup>Sources: ark.intel.com/products and www.amd.com/en-us/products accessed on 13 September 2014

software [8]. Therefore, developers can now benefit from both flexibilities of FPGA and easy programming of CPU/GPU by utilizing the C based programming language OpenCL.

As a consequence, OpenCL based FPGA designs may allow very promising solutions to existing or new problems. Hence, a Galois Field multiplier design on FPGA using OpenCL is potentially an efficient and worth to investigate solution approach.

There are several methods existing for Galois Field multiplication. Trivial methods like look-up table or old-school multiplication followed by long division are not suitable for large fields such as order of hundreds. Therefore, more complicated algorithms such as Karatsuba-Ofman, RNS (Residue number system) and Montgomery are developed.

Karatsuba-Ofman algorithm, actually, just divides large numbers into smaller pieces. It introduces a tree-like structure for multiplication. Unfortunately, it lacks the reduction part. So reduction must be implemented separately after multiplication. RNS algorithm provides easy method for multiplication that is highly parallel by design. RNS also lacks reduction operation and additionally it requires computationally intensive forward and backward transitions. Montgomery algorithm, on the other hand, includes both multiplication and reduction operations. It can be parallelized as well. Therefore, Montgomery algorithm is selected to be implemented on FPGA using OpenCL.

This thesis covers evaluation of Montgomery multiplier implementation on FPGA using OpenCL. Effects of OpenCL specific Kernel attributes have been investigated and performances of FPGA, GPU and CPU as computation platform have been compared.

Evaluation hardware is Nallatech P385-d5<sup>4</sup>. The board is connected to the host system via PCIe bus and includes an Altera Stratix V GS D5 FPGA and 8 GB on board DDR3. Altera Stratix V GS D5 FPGA has 457K logic elements, 690K registers, 28 fractional PLLs, 3550 18x18 multipliers, 1775 27x27 multipliers. However, hardware multipliers are not utilized due to mathematical differences in integer multiplication and Galois Field multiplication. Multiplication modules are coded in OpenCL. Code

<sup>&</sup>lt;sup>4</sup> Details: http://www.nallatech.com/images/stories/product\_briefs/openclcardspb\_v1\_5.pdf

is compiled using Altera OpenCL SDK with Quartus II version 13.0 service pack 1. Host application is based on Nallatech Hello World example and coded in Visual Studio 2010.

The thesis is organized as follows: First, a brief mathematical background on Galois Field arithmetic and on OpenCL framwork is given in Chapter 2. An introduction to OpenCL development environment is also given in this chapter. Chapter 3 presents a literature survey of the related work on Galois Field multiplication. Some sample implementations are briefly summarized in Chapter 3. Chapter 4 describes the implementation details of the OpenCL Montgomery multiplier on FPGA. In addition, Chapter 4 includes FPGA test results and our observations. Comparison of the performances of the implemented code on FPGA, GPU and CPU platforms and also comparison with the performances of previous works are presented in Chapter 5. Finally, Chapter 6 summarizes and concludes the thesis work.

## **CHAPTER 2**

# BACKGROUND

#### 2.1 Mathematical Background

#### 2.1.1 Galois Field

**Galois field** is a finite set of numbers with some special mathematical properties so that defined operations always results in the set.

It is required that defined operations must satisfy fixed axioms, associativity, commutativity and distributivity rules over its elements. Additionally, any element must have a unique additive inverse and any non-zero element should have a unique multiplicative inverse [9].

#### 2.1.2 Galois Field Arithmetic

Easiest example would be on prime Galois fields, GF(p). So arithmetic is identical to regular integer addition and multiplication with modulo prime p. Some examples in GF(3) where elements are (0, 1, 2) are as follows:

$$\begin{array}{ll} 0+0=0 & 1+2=0 & 2+2=1 \ (2+2\equiv 1 \pmod{3}) \\ 0\times 0=0 & 1\times 2=2 & 2\times 2=1 \ (2\times 2\equiv 1 \pmod{3}) \end{array}$$

In order GF(p) to form a field, p must be a prime, otherwise some elements might not have a unique multiplicative inverse. For instance, there is no x value satisfying  $2 \times x = 1 \mod 6$ . We can also use vectors to enhance the field, so we can use GF(m) such that  $m = p^n$ where p is a prime and n is an integer. Furthermore, given n > 1, finite field  $GF(p^n)$ can be represented as the field of equivalence classes of polynomials in which coefficients are in the field GF(p). Therefore the elements of  $GF(p^n)$  can be represented by polynomials with degree less than n [10].

Moreover, addition in a vector field is relatively easier than addition of integers because integer addition has carry. Since there is no carry generated in vector addition, all computations are guaranteed to be in the finite set. Here are some examples of addition operation in  $GF(2^3)$ :

000 + 000 = 000 010 + 100 = 110 011 + 110 = 101

Multiplication, on the other hand, could lead to larger results that do not fit into finite space [11]. Therefore multiplication includes one more step referred as reduction. Actually, GF multiplication is done by first doing a regular multiplication using carryless additions, then by dividing the result with the reduction polynomial and by noting the remainder as the final result. Therefore, both p, n in  $GF(p^n)$  and the reduction polynomial must be known in order to carry out multiplication in GF.

Multiplication with randomly chosen reduction polynomials can be very costly and ineffective in certain operations. Therefore, National Institute of Standards and Technology (NIST) has chosen several polynomials which are optimized for the efficiency of the elliptic curve operations [12].

### **2.1.2.1** Addition in $GF(2^m)$

Addition is very easy for computers since it is only an exclusive or (XOR) operation for each bit (see algorithm 1).

| <b>Algorithm 1:</b> Addition in $GF(2^m)$                                          |

|------------------------------------------------------------------------------------|

| <b>Input</b> : $a(x) = \sum_{0}^{m-1} a_i x^i$ and $b(x) = \sum_{0}^{m-1} b_i x^i$ |

| <b>Output:</b> $c(x) = \sum_{0}^{m-1} c_i x^i = a(x) + b(x)^{-1}$                  |

| 1 <b>Procedure</b> $Sum(\overline{a(x)}, b(x))$                                    |

| <b>2 for</b> $i = 0$ to $m - 1$ <b>do</b>                                          |

| 3 $c_i = a_i \oplus b_i$                                                           |

| 4 return $c(x)$                                                                    |

# **2.1.2.2** Multiplication in $GF(2^m)$

Straight and old fashioned school multiplication followed by a long division is very costly in GF multiplication. Since GF multiplication is widely used in the core of many applications such as cryptography/security applications, it is crucial to have a fast and efficient multiplier.

A simple method for multiplication is shift-and-add [9]. Given,

$$a(x) = \sum_{0}^{m-1} a_{i}x^{i} \qquad b(x) = \sum_{0}^{m-1} b_{i}x^{i} \qquad c(x) = \sum_{0}^{m-1} c_{i}x^{i} \qquad f(x) = \sum_{0}^{m-1} f_{i}x^{i}$$

$$c(x) = a(x) \cdot b(x) \mod f(x)$$

$$= \left(a_{m-1}x^{m-1}b(x) + \dots + a_{2}x^{2}b(x) + a_{1}xb(x) + a_{0}b(x)\right) \mod f(x)$$

(2.1)

We observe that Equation 2.1, iterating through i (on  $a_i$ ), calculates  $x^i b(x) \mod f(x)$ and accumulates the result if  $a_i$  is non-zero.

$$b(x)x = (b_{m-1}x^m + b_{m-2}x^{m-1} + \dots + b_2x^3 + b_1x^2 + b_0x) \mod f(x)$$

=  $b_{m-1}x^m \mod f(x) + (b_{m-2}x^{m-1} + \dots + b_2x^3 + b_1x^2 + b_0x) \mod f(x)$

=  $b_{m-1}r(x) + (b_{m-2}x^{m-1} + \dots + b_2x^3 + b_1x^2 + b_0x) \mod f(x)$

(2.2)

Therefore,  $b(x)x \mod f(x)$  can be calculated iteratively by a shift operation and then adding  $r(x) = x^m \mod f(x)$  to b(x) if the most significant bit,  $b_{m-1}$ , is 1 (see algorithm 2).

| <b>Algorithm 2:</b> Multiplication in $GF(2^m)$                                    |

|------------------------------------------------------------------------------------|

| <b>Input</b> : $a(x) = \sum_{0}^{m-1} a_i x^i$ and $b(x) = \sum_{0}^{m-1} b_i x^i$ |

| Reduction Polynomial: $f(x) = \sum_{i=0}^{m-1} f_i x^i$                            |

| <b>Output:</b> $c(x) = \sum_{i=0}^{m-1} c_i x^i = a(x) \cdot b(x) \mod f(x)$       |

| 1 <b>Procedure</b> $Multipy(a(x), b(x))$                                           |

| 2 <b>if</b> $a_0 = 1$ <b>then</b>                                                  |

| 3 $c(x) \leftarrow b(x)$                                                           |

| 4 else                                                                             |

| 5 $c(x) \leftarrow 0$                                                              |

| 6 for $i = 1$ to $m - 1$ do $/*$ $i = 0$ already processed $*/$                    |

| 7 $b(x) \leftarrow b(x)x \mod f(x)$                                                |

| 8 if $a_i = 1$ then                                                                |

| 9 $c(x) \leftarrow c(x) \oplus b(x)$                                               |

| 10 return $c(x)$                                                                   |

#### 2.2 Development Environment and Tools

## 2.2.1 FPGA

A field-programmable gate array (FPGA) is a large integrated circuit that can be configured to perform specific tasks. Although FPGAs have flexible structure, they can offer quite high computation power because they perform calculations at the gate level. Nowadays, FPGAs are very rich in terms of resources. It is possible to find a single FPGA chip that includes logic elements up to millions, a large memory up to tens of Mbits, hard peripheral blocks/transceivers and hard computation units such as multiple CPU cores, DSP cores, thousands of multipliers, etc. [13] [14].

FPGAs require special equipment for programming and a very common way is using a JTAG connection. Reprogramming of an FPGA completely restarts the device. This is not a problem for most of the times because it happens at system start-up. However, this may not be so practical for some applications such as an application where FPGA is connected as a PCIe device to the host computer. Any change in FPGA requires complete reprogramming and hence PCIe core requires to be restarted. That makes the FPGA inaccessible by the host until a complete restart of the host system. The solution is to use partial reconfiguration. Partial reconfiguration, as the name implies, allows FPGA to be programmed partially. Moreover, this method is further enhanced to use PCIe connection to eliminate the need for special equipment. This is called as configuration via protocol (CvP) by Altera [15].

#### 2.2.1.1 FPGA as Computation Unit

FPGAs are massively parallel processors by design. Unlike sequential C programs, it could be very hard and time consuming to design, debug and verify an FPGA system. Moreover, compilation time may easily exceed several hours. Also, abstraction is limited because a programmer may need to consider very low level hardware related issues such as timing.

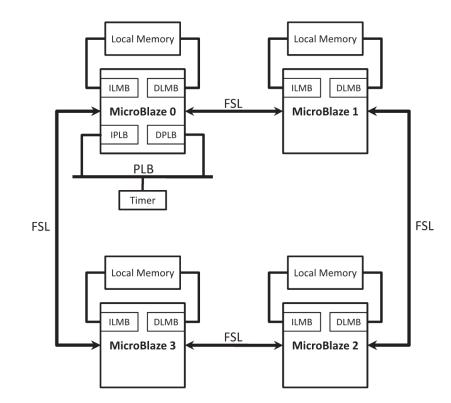

#### 2.2.1.2 CPUs in the FPGA

In order to speed up the design process, major FPGA manufacturers introduced soft processors. Altera named their soft processor as NIOS II and Xilinx named theirs as MicroBlaze. Soft processor is basically a simple CPU core using logic resources of the FPGA. With the increasing number of logic elements in an FPGA, it is even possible to implement many soft CPU cores in a single chip. Moreover, major FPGA vendors started manufacturing chips including single or many hard CPU cores <sup>1</sup> [16] [17].

#### 2.2.1.3 FPGA as an OpenCL Device

Recently, Altera released a high performance computation solution using a Stratix V FPGA as an OpenCL device. Therefore, an FPGA can be used as a parallel computing device similar to a GPU. Moreover, the solution provides a highly customizable architecture that regular GPUs do not have. Additionally, this solution may decrease power consumption dramatically while increasing the throughput compared to CPU or GPU based solutions [18].

OpenCL is a portable programming language, meaning that applications can run on different hardware. However, it may be very time consuming to optimize an OpenCL code for different brands/models of GPU hardware. Therefore, migration is easy from functional point of view but may be hard is an efficient migration is desired. Since GPU hardware is fixed and varies a a lot among brands/models, a code optimized for "GPU-A" must be re-optimized manually for "GPU-B". FPGA hardware on the other hand can adapt itself to a specific piece of code. Therefore, in an FPGA solution, which includes an optimal hardware-software co-design, migration to another FPGA just becomes re-compilation of the code. For instance, work group sizes should be optimized depending on number of processing units in the GPU in order to maximize utilization. However, FPGA implementation will generate required number of cores during compilation.

<sup>&</sup>lt;sup>1</sup> Xilinx released Zynq-7000 series with dual ARM Cortex-A9 based application processor unit with CPU frequency up to 1 GHz [16]. Similarly, Altera has ARM-based hard processor system that utilizes dual-core ARM Cortex-A9 MPCore processor [17].

#### 2.2.2 OpenCL

OpenCL is a framework for parallel programming. Its applications run on heterogeneous platforms consisting of one or more single/multi core CPUs, GPUs, DSPs, FP-GAs, and other processing units [19]. It uses the heterogeneous programming model. Operations such as memory management, data transfers to/from devices, queuing tasks to devices, and error management are handled by the host device. It is based on C99 programming language with additional keywords.

OpenCL is maintained by Khronos Group and supported by a variety of companies including Intel, AMD, Qualcomm, IBM, Samsung, Apple, nVidia, Nokia, Altera, Xilinx, ARM, Broadcom, Ericsson, Freescale [19].

An OpenCL application basically has two parts: (i) the main code that runs on the host to prepare and orchestrate the heterogeneous platform and (ii) kernels that run on OpenCL device(s) that perform the actual computation (see Figure 2.1). The application running on the host submits tasks to OpenCL devices.

Figure 2.1: Overview of of OpenCL architecture [1]

First, the OpenCL host application (usually a sequential code written in C++) queries and selects computation devices using OpenCL API. Then it manages them using work queues. Kernels written in OpenCL runs on each computation unit in parallel.

There are basically two models in parallelizing a computation task, which are called as data-parallel and task-parallel.

- **Data-parallel model:** A sequence of instructions are executed on a unique element of an array, which are mapped by unique-ids of each processing unit. For example,  $\sum_{1}^{NumOfPU} A_i + B_i$  can be calculated at once by each core summing two inputs mapped by ids.

- **Task-parallel model:** Each processing unit can be used independently to execute given task.

Memory management is explicit. Host application must transfer data from host memory to OpenCL devices' memories and then get the results back [19].

Memory regions in OpenCL are differentiated depending on access type and scope.

- **Global memory** can be accessed by all work-items of all work-groups. Access type is read/write.

- **Local memory** can be accessed by all work-items of the same work-group. Access type is read/write.

- **Constant memory** is read-only accessible by all-work items.

**Private memory** is read/write accessible by individual work-items.

#### 2.2.3 OpenCL on FPGA vs. GPU

Kernel execution is handled differently on FPGA and GPU. GPU consists of many (usually in the order of hundreds) simple SIMD processing units on which work-items are computed instruction-by-instruction. Due to fixed size SIMD architecture same instruction must be executed on a number of processing units. However, each kernel is mapped into a custom dedicated logic on FPGA [2]. All data paths (including conditional paths) in the code are converted into piece of hardware as illustrated in Figure 2.2.

Figure 2.2: Simple OpenCL code mapped into custom logic [2].

FPGA, on the other hand, utilizes pipeline parallelism. Therefore, its branching behavior is different than SIMD, which is usually found in GPUs. Because of having SIMD architecture on GPU, following different paths across work items after a branching would cause idle times in the process. This is because only a single instruction can be executed at a time [2]. On the other hand, programmers are not faced with this issue on FPGA. Because all possible branchings are already built into the custom hardware and any path could be followed at any place of the pipeline. A simple behavior of pipelined FPGA and SIMD GPU are compared in Figure 2.3 where all three work-items first execute A and then B, C and D stages are executed conditionally.

|                                                                                             |                         |   | _                       | -                  | -                         |                           |       |                 |

|---------------------------------------------------------------------------------------------|-------------------------|---|-------------------------|--------------------|---------------------------|---------------------------|-------|-----------------|

| A();                                                                                        |                         | Α | $B_1$                   | $C_1$              | IDLE                      |                           |       |                 |

| <i>u</i> .                                                                                  | SIMD                    | Α | <b>IDLE</b> $B_2$ $C_2$ |                    |                           | IDLE                      |       |                 |

| if( <i>COND</i> <sub>1</sub> ) { <i>B</i> <sub>1</sub> (); <i>C</i> <sub>1</sub> (); }      | Parallelism             | Α | IDLE                    |                    |                           |                           | $B_3$ | $\mathcal{C}_3$ |

| else if( $COND_2$ ) { $B_2(); C_2(); $ }                                                    | Pipeline<br>Parallelism | Α | A                       | A                  |                           |                           |       |                 |

| else if( <i>COND</i> <sub>3</sub> ) { <i>B</i> <sub>3</sub> (); <i>C</i> <sub>3</sub> (); } |                         |   | B <sub>1,2,3</sub>      | B <sub>1,2,3</sub> | B <sub>1,2,3</sub>        |                           |       |                 |

| // poor coding, just an example                                                             |                         |   |                         | C <sub>1,2,3</sub> | <i>C</i> <sub>1,2,3</sub> | <i>C</i> <sub>1,2,3</sub> |       |                 |

|                                                                                             |                         |   |                         |                    |                           |                           |       |                 |

Figure 2.3: Branching in SIMD structure vs. pipeline structure [2]

Scenario: First execute A on all CUs (compute units) then conditionally execute  $B_i$  and  $C_i$  on *i*th CU.

• GPU

- 1. Execute A on SIMD processor in parallel. A is common for all Kernels.

- 2. Execute  $B_1C_1$  which are conditionally executed on CU 1.

- 3. Execute  $B_2C_2$  which are conditionally executed on CU 2.

- 4. Execute  $B_3C_3$  which are conditionally executed on CU 3.

### • FPGA

- 1. Execute A for CU 1.

- 2. Execute either B<sub>1</sub>, B<sub>2</sub> or B<sub>3</sub> for CU 1 depending on condition.

Execute A for CU 2.

- 3. Execute either  $B_1$ ,  $B_2$  or  $B_3$  for CU 2 depending on condition.

- Execute either  $C_1$ ,  $C_2$  or  $C_3$  for CU 1 depending on condition.

- Execute A for CU 3.

- 4. Execute either B<sub>1</sub>, B<sub>2</sub> or B<sub>3</sub> for CU 3 depending on condition.

Execute either C<sub>1</sub>, C<sub>2</sub> or C<sub>3</sub> for CU 2 depending on condition.

- 5. Execute either  $C_1$ ,  $C_2$  or  $C_3$  for CU 3 depending on condition.

One other difference between GPU and FPGA exists in the design process, which will be explained in more detail in the following sections. Normally, OpenCL kernels are compiled at runtime for the target device, i.e., for CPU or GPU. Compiling kernels for GPU usually takes just a few seconds. However, FPGA logic synthesis is a computationally intensive work and may take quite a long time. Therefore, Altera provides an offline compiler (Altera Offline Compiler, AOC) to prepare FPGA logic from OpenCL code. So, instead of runtime compilation, Altera just loads prepared FPGA content. At this point, portability of OpenCL can shorten the design process dramatically. It would be a good practice to test OpenCL code first on CPU or GPU, then compile it for FPGA using AOC.

#### 2.2.4 Development Environment

Development of software for OpenCL based Altera FPGA consists of two parts, software focused host application development and hardware focused kernel development.

### 2.2.4.1 Host Application Development

Host application is a C++ program that uses OpenCL API. Host application runs on a regular CPU. It uses OpenCL APIs to manage compute devices as described in algorithm summarized in algorithm 3. Normally kernels (at line 5 ) would be compiled at runtime for the selected device [20]. However, in FPGA kernels are compiled by AOC [21] and image is loaded by partial reconfiguration (CvP).

| A  | Algorithm 3: Host application algorithm                    |  |  |  |  |

|----|------------------------------------------------------------|--|--|--|--|

| 1  | 1 Function Main()                                          |  |  |  |  |

| 2  | Discover OpenCL devices.                                   |  |  |  |  |

| 3  | Query their capabilities and decide which ones to use.     |  |  |  |  |

| 4  | Initiate OpenCL device. Create context, command queue etc. |  |  |  |  |

| 5  | Prepare kernel(s).                                         |  |  |  |  |

| 6  | repeat                                                     |  |  |  |  |

| 7  | Allocate memory buffers, prepare kernel arguments.         |  |  |  |  |

| 8  | Launch kernel.                                             |  |  |  |  |

| 9  | Collect results.                                           |  |  |  |  |

| 10 | until Application exits                                    |  |  |  |  |

| 11 | Exit program                                               |  |  |  |  |

Host application provides timing information for performance measurements. Additionally, host application can perform computations using software libraries to compare results.

### 2.2.4.2 Kernel Development

OpenCL is a portable solution, which means that the same code could be executed on different hardware. Therefore optimizing kernel for all devices is almost impossible as this task is highly dependent on hardware. On the other hand, an FPGA based OpenCL system could overcome this situation by configuring itself depending on the kernel, i.e., by producing an optimal hardware for each specific problem. So, the developer can only focus on solving the problem in a parallel manner. Therefore, Altera offers Altera SDK for OpenCL, which allows designers to use OpenCL C. Generally, OpenCL Kernels would be compiled at runtime depending on target hardware.

However, Altera solution uses pre-compiled hardware binary file [21].

Data processing efficiency can further be increased by instructing the compiler to use specific architectures. Altera provides several kernel attributes for this kind of customizations, details of which are given in [22]. Some exemples are as follows:

**#pragma unroll** tells AOC to try to unroll loops to decrease the number of iterations at the expense of increased hardware resource usage. Loop unrolling will fail if loop bounds are not constant, loop contains too much data dependency, or loop is too large so that it does not fit into hardware (in this case #pragma unroll <N> could be used to limit unrolling).

**max\_work\_group\_size** instructs compiler to limit work group size. Compiler assumes 256 work-items for work group size by default. Therefore, software requiring smaller work groups would lead unnecessary hardware to be generated when this attribute is not set.

**reqd\_work\_group\_size** is similar to max\_work\_group\_size attribute but specifies the exact size per work group to allow further hardware resource optimization.

**num\_compute\_units** allows the compiler to generate multiple compute units per kernel in order to increase throughput. It increases both global memory bandwidth requirement and hardware resource utilization (see Figure 2.4a).

num\_simd\_work\_items is similar to num\_compute\_units but it also requires reqd\_work\_group\_size to be specified. It increases throughput by vectorizing kernel, which enables multiple work-items to be processed in SIMD fashion (see Figure 2.4b). Using SIMD compute units usually results in more efficient hardware than using multiple compute units because SIMD compute units only duplicates data paths [22]. Using both could be a better option (see Figure 2.4c). A comparison is depicted in Figure 2.4.

Figure 2.4: (a) Multiple compute units (using num\_compute\_units(4) attribute) (b) Compute unit with multiple SIMD lanes (using num\_simd\_work\_items(4) attribute) (c) Multiple compute unit with multiple SIMD lanes (using num\_compute\_units(3) and num\_simd\_work\_items(4) attributes).

# **CHAPTER 3**

# **RELATED WORK**

Parallel implementations of various multiplication algorithms exist in the literature. The present chapter gives an overview of a sample of such implementations with a focus on FPGA, GPU and multi-core solutions. The implemented multiplication algorithms are also briefly summarized first.

# 3.1 Multiplication Algorithms

## 3.1.1 Karatsuba Multiplication

Karatsuba algorithm was introduced as a general integer multiplication method based on divide and conquer approach. Basic idea is to replace multiplication with less complex addition/subtraction operations [23].

Suppose, we need to calculate c = ab. First divide inputs as  $a = a_H x^m + a_L$  where  $x^m > a_L$  and  $b = b_H x^m + b_L$  where  $x^m > b_L$ . Then,

$$c = ab = (a_H X^m + a_L)(b_H x^m + b_L)$$

$$c = c_1 x^{2m} + c_2 x^m + c_3$$

$$c = a_H b_H x^{2m} + (a_H b_L + a_L b_H) x^m + a_L b_L$$

(3.1)

Equation 3.1 would require four multiplications of size m/2. On the other hand,

$$a_H b_L + a_L b_H = (a_H + a_L)(b_H + b_L) - a_H b_H - a_L b_L$$

$c_2 = (a_H + a_L)(b_H + b_L) - c_1 - c_3$

Therefore,  $c_2$  can be calculated using one multiplication instead of two and the whole result can be expressed as in Equation 3.2 with three multiplications plus some shift and add operations.

$$c = a_H b_H x^{2m} + ((a_H + a_L)(b_H + b_L) - a_H b_H - a_L b_L) x^m + a_L b_L$$

(3.2)

This method is especially useful for recursive multiplication of very large integers using limited size multipliers such as the ones we encounter in modern day processors, which have 32, 64 bit multipliers. For example, Intel's *PCLMULQDQ* instruction uses this method to compute carryless multiplication of large numbers on 64 bit multipliers [24]. Any type of multiplication can be employed at the end of recursion.

# **3.1.2** Karatsuba Multiplication in $GF(2^m)$

Finite field multiplication is performed in two steps; first one is classic multiplication and the second one is modular reduction as described in algorithm 4 using multipliers of size  $N_{MultiplierSize}$  in line 8 [3]. Note that all summations (additions and subtractions) in line 12 are the same operation exor in  $GF(2^m)$ .

| <b>Algorithm 4:</b> Karatsuba Multiplication in $GF(2^m)$                                                                     |

|-------------------------------------------------------------------------------------------------------------------------------|

| <b>Input</b> : $A(x) = \sum_{0}^{2^{n}-1} A_{i}x^{i}$ and $B(x) = \sum_{0}^{2^{n}-1} B_{i}x^{i}$ where <i>n</i> is an integer |

| <b>Output:</b> $C(x) = \sum_{0}^{2^{n}-1} C_{i} x^{i} = AB \mod f(x)$ where n is an integer                                   |

| 1 Function Multiply(Å, B)                                                                                                     |

| $2 	 C_{Partial} = Karatsuba(A, B)$                                                                                           |

| $3 	 C = Modular Reduction(C_{Partial})$                                                                                      |

| 4 return C                                                                                                                    |

|                                                                                                                               |

| <b>Input</b> : $a(x) = \sum_{0}^{2^{n-1}} a_i x^i$ and $b(x) = \sum_{0}^{2^{n-1}} b_i x^i$ where n is an integer              |

| <b>Output:</b> $c(x) = \sum_{0}^{2 \times 2^{n}-2} c_{i} x^{i} = ab$ where <i>n</i> is an integer                             |

| <b>5</b> Function Karatsuba(a, b)                                                                                             |

| $6 \qquad N \leftarrow max(degree(a), degree(b))$                                                                             |

| 7 if $N > N_{MultiplierSize}$ then                                                                                            |

| 8 return $Mult(a, b)$                                                                                                         |

| Let: $a = a_H x^{N/2} + a_L$ and $b = b_H x^{N/2} + b_L$                                                                      |

| 9 $c_{HH} \leftarrow Karatsuba(a_H, b_H)$                                                                                     |

| 10 $c_{HL} \leftarrow Karatsuba(a_H + b_L, a_L + b_H)$                                                                        |

| 11 $c_{LL} \leftarrow Karatsuba(a_L, b_L)$                                                                                    |

| 12 return $c_{HH}x^N + (c_{HL} - c_{HH} - c_{LL})x^{N/2} + c_{LL}$                                                            |

Any method can be used for Mult(a, b). Karatsuba algorithm calculates multiplication of two numbers but it does not perform reduction operation, which has to be performed separately.

## **3.1.3** Montgomery Multiplication in $GF(2^m)$

Montgomery multiplication, first introduced in 1985, replaces time consuming division and reduction operations in GF multiplication with less costly operations [25].

Suppose we need to calculate c(x) in  $GF(2^m)$ , i.e.,

$$c(x) = \sum_{0}^{m-1} c_i x^i = a(x)b(x) \mod f(x)$$

Instead of directly working on a(x) and b(x), Montgomery algorithm suggests to use  $\bar{a} \equiv aR(x) \mod f(x)$  and  $\bar{b} \equiv bR(x) \mod f(x)$  where R(x) is chosen such that R(x) > f(x) and is relatively prime to f(x) (that is gcd(R(x), f(x)) = 1). Here, gcd(a, b) stands for greatest common divisor of a and b.

As described in [26], for modulo f(x) = N,

$$c = ab \mod N$$

$$\bar{c} = cR \mod N$$

$$= abR \mod N = (aRbRR^{-1}) \mod N = (\bar{a}\bar{b}R^{-1}) \mod N$$

$$= (\bar{a}\bar{b}RR^{-1}/R) \mod N$$

(3.3)

Using identity  $RR^{-1} - NN' = 1$ ,

$$\bar{c} = (\bar{a}\bar{b}(1+NN')/R) \mod N$$

=  $((\bar{a}\bar{b} + \bar{a}\bar{b}NN')/R) \mod N$  (3.4)

For any integer k,

$$\bar{c} = ((\bar{a}\bar{b} + \bar{a}\bar{b}NN')/R + kN) \mod N$$

$$= ((\bar{a}\bar{b} + \bar{a}\bar{b}NN' + kNR)/R) \mod N$$

$$= ((\bar{a}\bar{b} + (\bar{a}\bar{b}N' + kR)N)/R) \mod N$$

$$= ((\bar{a}\bar{b} + ((\bar{a}\bar{b}N') \mod R)N)/R) \mod N$$

(3.5)

Notice that,  $(\bar{a}\bar{b}N') \mod R < R$  and  $\bar{a} < N$ ,  $\bar{b} < N$  therefore  $\bar{a}\bar{b} < N^2$ . So,

$$(\bar{a}\bar{b} + ((\bar{a}\bar{b}N') \mod R)N)/R < (N^2 + RN)/R$$

Since R > N and addition is xor operation in GF, expression  $\bar{a}\bar{b}+((\bar{a}\bar{b}N') \mod R)N)/R$ will always be less than N. Therefore  $\mod N$  in the last line of Equation 3.5 has no effect for GF. Therefore  $\bar{c} = \bar{a}\bar{b} \mod N$  can be calculated by algorithm 5.

Algorithm 5: Montgomery Product

| <b>Given</b> : $R$ a power of 2, $R > N$ and $gcd(R, N) = 1$ |

|--------------------------------------------------------------|

| $N'$ such that $RR^{-1} - NN' = 1$                           |

| <b>Input</b> : $\bar{a} \equiv aR \mod N$                    |

| $\bar{b} \equiv bR \mod N$                                   |

| <b>Output:</b> $\bar{c} \equiv cR \mod N$                    |

| 1 Function $MontProd(\bar{a}, \bar{b})$                      |

| 2 $t = \bar{a}\bar{b}$                                       |

| 3 $\bar{c} = (t \oplus (tN' \mod R)N)/R$                     |

| 4 return $\bar{c}$                                           |

Modulo and division by R are both easy operations for computers as R is a power of 2. However, switching to N residue and computation on N' are costly. Therefore, this algorithm is more appropriate for operations where several multiplication products are required (i.e. exponentiation) with the same modulus [27].

Montgomery algorithm is also valid for integers. However, Montgomery for integers has one more step in the end. Expression  $\bar{a}\bar{b}+((\bar{a}\bar{b}N')\mod R)N)/R$  in Equation 3.5 is smaller than 2N for integers. Therefore, additional subtraction operation is required if expression is larger than N. Following example illustrates Montgomery algorithm for integer multiplication:

# **Example:**

Suppose we would like to perform  $25 \times 53 \mod{97}$ , take R = 100

So, pre-calculated constants  $R^{-1} = 65 \mod 97$  and  $RR^{-1} - NN' = 1 \Rightarrow N' = 67$

First, transforms inputs into Montgomery domain,

$$a = 25$$

$\bar{a} = 25 \times 100 \mod 97 = 75$

$b = 53$   $\bar{b} = 53 \times 100 \mod 97 = 62$

Then, perform Montgomery reduction as given in algorithm 5.

$$t = \bar{a}\bar{b} = 75 \times 62 = 4650$$

$$\bar{c} = (4650 + (4650 \times 67 \mod 100) \times 97)/100$$

$$= (4650 + (311550 \mod 100) \times 97)/100$$

$$= (4650 + (50 \times 97)/100)$$

$$= (4650 + 4850)/100$$

$$= 9500/100$$

$$\bar{c} = 95$$

Finally, convert result back from Montgomery domain.

$$c = \bar{c}R^{-1} \mod 97 = 95 \times 65 \mod 97$$

$c = 64 = 25 \times 53 \mod 97$

As illustrated in the example, Montgomery method converts expensive modulo operation with less costly divisions and modulo operations. For computers those division and modulo operations will become just shifting and neglecting.

Montgomery reduction method is not suitable for single multiplication due to forward and backward conversions. However for repeated multiplications like exponentiation, it is very useful. Because, all computations can remain in Montgomery domain. Therefore only initial and final domain conversions would be enough.

## 3.1.3.1 Parallel Implementations of Montgomery Multiplication

Montgomery based multiplication is performed when modulo multiplication of two s-word numbers is required, where s is relatively large and a multiplier hardware exits for multiplying word size numbers. Montgomery based algorithms can basically be categorized in terms of two factors [27]:

- 1. whether multiplication and reduction stages are integrated<sup>1</sup> or separate, and

- 2. whether the algorithm loops on operand's words or product's words.

$<sup>^{1}</sup>$  called as *finely* when reduction is performed just after a word or *coarsely* when reduction is performed on an array of words

**Separated Operand Scanning (SOS):** Multiplication and reduction steps are separated in this technique. First, 2s-word product of two s-word integers is calculated and then reduction is performed to obtain the final result.

**Coarsely Integrated Operand Scanning (CIOS):** Unlike SOS, this methods switches between multiplication and reduction in the loop, therefore directly producing the s-word final result instead of computing 2s-word complete product.

**Finely Integrated Operand Scanning (FIOS):** This method unrolls nested loops of CIOS into singe loops to perform reduction word by word.

**Finely Integrated Product Scanning (FIPS):** This method loops on final product's words. It would be beneficial for microprocessors as most of the read, write operations are on accumulator words which would most likely be placed in registers.

**Coarsely Integrated Hybrid Scanning (CIHS):** This is similar to SOS but requires less space by hybrid design. The method mixes product scanning and operand scanning.

There are many studies on Montgomery multiplication algorithm. Some of them are [27], [28], [29], [4], [30].

# 3.1.3.2 Partitioning of Separated Operand Scanning (SOS) Method

SOS Methodology is given in algorithm 6, which is a more detailed version of algorithm 5 for modular multiplication of multi word numbers. It is observed that the most time consuming parts are the inner loops at line 4 and line 8. Therefore parallelization should be targeted in these loops. Additionally, data flow is given in Figure 3.1.

Algorithm 6: Montgomery product with SOS method **Input** : s-word operands A, B; an odd modulus N. Constant  $n' = -n_0^{-1} \mod 2^w$  where w is the word length **Output:** s-word  $C = AB \mod N$ 1 **Procedure** *MontMultSOS*(*A*, *B*) for i = 0 to s - 1 do 2 for j = 0 to s - 1 do 3 4  $t[i+j] = t[i+j] + a[j] \times b[i]$ // Multiplication is OK. Now, reduction. for i = 0 to s - 1 do 5  $m_i = t[i] \times n' \mod 2^w$ 6 for j = 0 to s - 1 do 7  $t[i+j] = t[i+j] + m_i \times n[j]$ 8  $C = (t_{s-1}, \cdots, t_1, t_0)$ // Lower s-word of t9 10 return C

Figure 3.1: Data flow of Montgomery multiplication (SOS) given in algorithm 6. White boxes show multiplication stages and gray boxes represent reduction steps.

With the analysis of data flow given in Figure 3.1, it is observed that there are basically

two options for partitioning, which can be row based or column based. Both methods are illustrated in Figure 3.2, where  $P_i$  denotes the *i*-th partition.

**Row Based Partitioning:** Row based partitioning is depicted in Figure 3.2a. One can easily observe that it has perfect task balancing since all partitions have equal number of boxes. However, t must be transferred between partitions, which introduces communication overhead.

**Column Based Partitioning:** Column based partitioning is depicted in Figure 3.2b. First of all, it has better communication overhead compared to row based partitioning. Only  $m_i$  terms are transferred. On the other hand, it could be argued that it does not have a good task balancing. However, tasks can be balanced by computing for example  $P_0$  and  $P_4$  on same computation unit. This case can be generalized by assigning  $P_i$  and  $P_{i+s}$  to the same computation unit.

Figure 3.2: Partitioning of SOS given in algorithm 6.

# 3.1.3.3 Partitioning of Coarsely Integrated Operand Scanning (CIOS) Method

Instead of calculating the whole product first and than reducing it as in algorithm 6, CIOS combines two large loops at line 2 and line 5 into a single loop. Because calculation of m at line 6 depends only on i. Then algorithm 6 becomes algorithm 7.

This method requires less amount of temporary memory space compared to SOS method. Therefore, it is suitable for GPU implementations since most variables could

fit into GPU registers [28].

| Algorithm 7: Montgomery product with CIOS method              |

|---------------------------------------------------------------|

| <b>Input</b> : s-word operands $A, B$ ; an odd modulus $N$ .  |

| Constant $n' = -n_0^{-1} \mod 2^w$ where w is the word length |

| <b>Output</b> : s-word $C = AB \mod N$                        |

| 1 <b>Procedure</b> <i>MontMultSOS</i> ( <i>A</i> , <i>B</i> ) |

| <b>2</b> for $i = 0$ to $s - 1$ do                            |

| <b>3 for</b> $j = 0$ <b>to</b> $s - 1$ <b>do</b>              |

| 4 $t[i+j] = t[i+j] + a[j] \times b[i]$                        |

| 5 $m = t[i] \times n' \mod 2^w$                               |

| 6 <b>for</b> $j = 0$ <b>to</b> $s - 1$ <b>do</b>              |

| 7 $t[i+j] = t[i+j] + m \times n[j]$                           |

| 8 $C = (t_{s-1}, \cdots, t_1, t_0)$ // Lower s-word of $t$    |

| 9 return C                                                    |

# **3.1.4** Multiplication in $GF(2^m)$ using Residue Number System (RNS)

RNS is a number representation, which divides a large integer into smaller size integers [31]. Suppose that we have pairwise relatively prime moduli set  $\{m_1, m_2, \dots, m_N\}$ with the least common multiple of  $m_i$  being M. Then any number X < M has a unique representation in the defined residue number system as  $\{x_1, x_2, \dots, x_N\}$ , which satisfies  $x_i = X \mod m_i$ .

RNS could be used in the computation of  $C = A \cdot B \mod M$ . Then the product can be obtained by calculating  $c_i = a_i \cdot b_i \mod m_i$ , which provides perfect parallelism by design.

A highly parallel multiplication method using RNS is given in algorithm 8. It is based on Montgomery method in RNS [32]. The algorithm is fully parallel except two base extensions computed in line 4 and line 7. Unfortunately, these base extensions are quite time consuming.

Algorithm 8: Montgomery multiplication over trinomial residues **Given** : Precomputed constant matrices of multiplications by  $p_i^{-1} \pmod{t_i}$ ,  $p_{n+i} \pmod{t_{n+i}}, m_{n+i}^{-1} \pmod{t_{n+i}}$ **Input** :  $A : \{a_1, \dots, a_{2n}\}, B : \{b_1, \dots, b_{2n}\}, P : \{p_1, \dots, p_{2n}\}$ **Output:**  $R: \{r_1, \dots, r_{2n}\}$  where  $r_i = a_i b_i m^{-1} \pmod{p_i}$  and m is Montgomery factor **1** Function Mult(A, B) $\{c_1, \cdots, c_{2n}\} = \{a_1, \cdots, a_{2n}\} \times \{b_1, \cdots, b_{2n}\}$ 2  $\{q_1, \cdots, q_n\} = \{c_1, \cdots, c_n\} \times \{p_1^{-1}, \cdots, p_n^{-1}\}$ 3  $\{q_{n+1},\cdots,q_{2n}\} = BaseExt(\{q_1,\cdots,q_n\})$ 4  $\{r_{n+1}, \cdots, r_{2n}\} = \{c_{n+1}, \cdots, c_{2n}\} + \{q_{n+1}, \cdots, q_{2n}\} \times \{p_1, \cdots, p_{2n}\}$ 5  $\{r_{n+1}, \cdots, r_{2n}\} = \{r_{n+1}, \cdots, r_{2n}\} \times \{m_{n+1}^{-1}, \cdots, m_{2n}^{-1}\}$  $\{r_1, \cdots, r_n\} = BaseExt(\{r_{n+1}, \cdots, r_{2n}\})$ 6 7 **return**  $\{r_1, \dots, r_{2n}\}$ 8 **Input** :  $\{q_1, \dots, q_n \text{ residue representation of } Q \pmod{M}$ **Input** :  $\{q_{n+1}, \dots, q_{2n} \text{ residue representation of } Q \pmod{M'}$ **9** Function *BaseExt(Q)* // Newton's interpolation[32]  $tmp_1 = q_1$ 10 for i = 2 to n do // Can be calculated in parallel 11 12  $tmp_i = q_i$ for j = 0 to i - 1 do 13  $tmp_i = \left( (tmp_i + tmp_i) \times t_i^{-1} \right) \mod t_i$ 14 for i = 2 to n do // Can be calculated in parallel 15 16  $q_{n+i} = tmp_n \mod t_{n+i}$ for j = 0 to i - 1 do 17  $q_{n+i} = ((q_{n+i} \times t_j + tmp_j) \mod t_{n+i}$ 18 **return**  $\{q_{n+1}, \cdots, q_{2n}\}$ 19

## 3.2 FPGA Implementations of Various Galois Field Multipliers

## 3.2.1 Logic Level Designs

Although it requires more effort and it takes more time to implement a low level design, it usually results in high performance due to highly customizing and optimizing the circuit.

There are many research works on Galois Field multipliers that use bare FPGAs as their computation units. One example is [3]. In [3], the authors analyzed complexities of bit parallel Karatsuba-Ofman multiplier for both FPGA and ASIC. They have com-

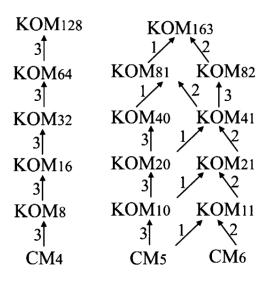

pared the area-time product of their design with previous designs and achieved the lowest area utilization in terms of logic resources for ASIC and LUTs for FPGA. Normally, *i* step Karatsuba-Ofman algorith can operate on  $m = 2^i n$  bits long operands. However, usual operand lengths are not powers of two but usually prime numbers as recommended by NIST. Therefore most designs pad zeroes to achieve a size such that it is a power of two. But authors in [3] selected an asymmetrical method for iterations to achieve non-power of two lengths as illustrated in Figure 3.3.

Figure 3.3: An example flow of regular (left) and proposed (right) iterations in [3]. Multiplier sizes are given as  $KOM_{SIZE}$  and number of multipliers used is given next to arrows.

#### 3.2.2 Soft Processor Designs

Another approach is to make use of soft processors in FPGAs, which provides both easy programming of C language and flexibility of FPGA. In soft processor use in FPGA, the processors are created out of FPGA resources. Therefore such designs can be scalable that is more processors can be added and also whole system can be migrated to another FPGA brand or model as long as the FPGA resources are sufficient. In soft processor based systems, mostly the clock frequency becomes the bottleneck of the system, which has a big impact on the overall performance. Clock frequencies in soft processors are usually around 100-200 MHz.

Practical applications of Galois field multiplication usually requires lengths of mul-

tiplicands to be many times larger than word length of computation unit. First part of the multiplication, that is straightforward multiplication to obtain partial products, has quadratic complexity. In addition, reduction part at the end will make the computation even longer. For instance, a straightforward implementation of a 2048-bit long multiplier would require 4096 32-bit multiplications. Therefore, parallelization could lead to huge performance improvements.

In general, some key properties such as *balanced task partitioning*, *low intercommunication delay, high scalability* should be considered in order to maximize the efficiency of a parallel design [4]. Consequently, parallel designs differ from sequential designs in many aspects.

In [4] authors suggest a parallel Montgomery multiplier and compare row and column based partitioning in terms of task partitioning balance and communication overheads. Finally, they suggest a novel method, called as parallel Separated Hybrid Scanning (pSHS). They implement a prototype on Xilinx Virtex 5 FPGA using two, four and eight 32-bit MicroBlaze soft processor cores running at 100 MHz. Each MicroBlaze soft processor core has an independent local memory and are connected with each other via Fast Simplex Link (FSL). An example with four soft processor cores is illustrated in Figure 3.4 where timer connected to MicroBlaze0 measures the execution time.

Figure 3.4: An example implementation of [4] with four soft processor cores.

## **3.3 GPU Implementations**

High number of computation units in modern GPUs provide a great computation power and allow parallel operations to be performed very efficiently on GPUs. Therefore, major GPU manufacturers created lots of tools to make GPU kernel development process fast and easy. As a result, idea of using GPU as computation unit is widely accepted among authors especially for heavily parallel workloads. Even GPGPU (General purpose GPU) applications have emerged recently.

GPU implementations tend to differ from multi-core CPU implementations in the sense of parallelization. GPU implementations are supposed to be massively parallel due to GPU hardware design. One can simply think of a multicore CPU as a small number of large compute units whereas a GPU as a large number of small compute units.

In [28] authors proposed a method to implement Montgomery multiplication and optimized it for SIMD architecture of GPUs. They have implemented a design on nVidia

#### GTX-480 GPU.

GPUs can work not only in data-parallel way but also in task-parallel manner. Capability of performing different tasks at the same time makes GPUs suitable for RNS algorithm which basically performs similar but not the same operations on different numbers. In [30] authors proposed residue number system (RNS) based Montgomery multiplication. The advantage of RNS is that it is inherently parallel. They evaluated their design on nVidia 285 GTX GPU. In [29], it is shown that alternative Montgomery RNS designs are possible with same cost in terms of number of additions, multiplications and base extension/conversions. RNS algorithm is also safe for side channel attacks due to fully independent parallelism and arbitrary selection of numbers.

Although RNS algorithm introduces very good parallelism for multiplication, reduction process requires too much cross thread communication. In addition, the process needs preliminary and post conversion computations.

## 3.4 Other Multi-core Solutions