# IMPLEMENTATION AND EVALUATION OF THE DEPENDABILITY PLANE FOR THE DYNAMIC DISTRIBUTED DEPENDABLE REAL TIME INDUSTRIAL PROTOCOL (D $^3$ RIP)

#### A THESIS SUBMITTED TO THE GRADUATE SCHOOL OF NATURAL AND APPLIED SCIENCES OF MIDDLE EAST TECHNICAL UNIVERSITY

$\mathbf{B}\mathbf{Y}$

ÖMER BERAT SEZER

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE IN ELECTRICAL AND ELECTRONICS ENGINEERING

SEPTEMBER 2013

#### Approval of the thesis:

#### IMPLEMENTATION AND EVALUATION OF THE DEPENDABILITY PLANE FOR THE DYNAMIC DISTRIBUTED DEPENDABLE REAL TIME INDUSTRIAL PROTOCOL (D<sup>3</sup>RIP)

submitted by ÖMER BERAT SEZER in partial fulfillment of the requirements for the degree of Master of Science in Electrical and Electronics Engineering Department, Middle East Technical University by,

| Prof. Dr. Canan Özgen<br>Dean, Graduate School of <b>Natural and Applied Sciences</b>                  |       |

|--------------------------------------------------------------------------------------------------------|-------|

| Prof. Dr. Gönül Turhan Sayan<br>Head of Department, <b>Electrical and Electronics Engineering</b>      |       |

| Assoc.Prof. Dr. Şenan Ece Schmidt<br>Supervisor, <b>Electrical and Electronics Eng. Dept., METU</b>    |       |

| Assoc. Prof. Dr. Klaus Werner Schmidt<br>Co-Supervisor, <b>Dept., of Mechatronics Eng., Çankaya U.</b> |       |

| Examining Committee Members:                                                                           |       |

| Prof. Dr. Semih Bilgen<br>Electrical and Electronics Engineering Dept., METU                           |       |

| Assoc. Prof. Dr. Şenan Ece Schmidt<br>Electrical and Electronics Engineering Dept., METU               |       |

| Assoc. Prof. Dr. Cüneyt Bazlamaççı<br>Electrical and Electronics Engineering Dept., METU               |       |

| Assoc. Prof. Dr. Halit Oğuztüzün                                                                       |       |

| Yusuf Bora Kartal<br>M.Sc. ASELSAN A.Ş                                                                 |       |

|                                                                                                        | Date: |

I hereby declare that all information in this document has been obtained and presented in accordance with academic rules and ethical conduct. I also declare that, as required by these rules and conduct, I have fully cited and referenced all material and results that are not original to this work.

Name, Last Name: ÖMER BERAT SEZER Signature:

#### ABSTRACT

#### IMPLEMENTATION AND EVALUATION OF THE DEPENDABILITY PLANE FOR THE DYNAMIC DISTRIBUTED DEPENDABLE REAL TIME INDUSTRIAL PROTOCOL (D<sup>3</sup>RIP)

Sezer, Ömer Berat

M.Sc., Department of Electrical and Electronics Engineering Supervisor : Assoc. Prof. Dr. Şenan Ece Schmidt Co-Supervisor : Assoc. Prof. Dr. Klaus Werner Schmidt

September 2013, 93 pages

Dynamic Distributed Dependable Real Time Ethernet Industrial Protocol ( $D^3RIP$ ) is a real time industrial communication protocol that runs over shared-medium Ethernet with COTS hardware. The protocol consists of an interface layer that enables time slotted communication and a coordination layer that guarantees collision avoidance and timely delivery of real time messages generated by the control application. At the current development stage, these two layers of the protocol are fully implemented and tested. The scope of this thesis is the implementation of a new plane for  $D^3RIP$  to achieve dependability. To this end, mechanisms of fault detection and roll back recovery are applied. The interface of the dependability plane to the existing interface layer and coordination layer is defined. Finally the dependability plane is implemented and integrated to the existing protocol stack. A number of tests under different fault scenarios are conducted to demonstrate the plane functionality.

Keywords: Ethernet, industrial communication network, real time industrial communication

## ÖZ

#### DİNAMİK DAĞITILMIŞ GÜVENİLİR GERÇEK ZAMANLI ENDÜSTRİYEL PROTOKOLÜ (D<sup>2</sup>G<sup>2</sup>EP) İÇİN GÜVENİLEBİLİRLİK DÜZLEMİ GERÇEKLENMESİ VE DEĞERLENDİRİLMESİ

Sezer, Ömer Berat

Yüksek Lisans, Elektrik ve Elektronik Mühendisliği Bölümü Tez Yöneticisi : Doç. Dr. Şenan Ece Schmidt Ortak Tez Yöneticisi : Doç. Dr. Klaus Werner Schmidt

Eylül 2013, 93 sayfa

Dinamik Dağıtılmış Güvenilir Gerçek Zamanlı Endüstriyel Protokolü ( $D^2G^2EP$ ), (COTs) orjinal donanımıyla ortam paylaşımlı Ethernet üzerinde çalışan gerçek zamanlı endüstriyel haberleşme protokolüdür. Protokol zaman oluklu iletişimi sağlayan arayüz katmanından (AK) ve kontrol uygulaması tarafından üretilen gerçek zamanlı mesajların iletimini ve çakışmayı önlemeyi garantileyen koordinasyon katmanından (KK) oluşur. Mevcut geliştirme aşamasında, bu iki protokol katmanı eksiksiz gerçeklenmiş ve test edilmiştir. Bu tezin kapsamı  $D^2G^2EP$ 'in güvenirliliğini sağlayan yeni bir düzlem uygulamasıdır. Bu amaçla, hata belirleme ve hata öncesi duruma geri döndürme mekanizmaları oluşturulmuştur. Varolan arayüz katmanı ve koordinasyon katmanı için güvenirlilik düzlemi arayüzü tanımlanmıştır. Son olarak güvenirlilik düzlemi uygulanmış ve varolan yapıya entegre edilmiştir. Farklı hata senaryolarına göre bir çok test gerçekleştirilmiş ve düzlemin işlevselliği gösterilmiştir.

Anahtar Kelimeler: Ethernet, endüstriyel iletişim ağları, gerçek zamanlı endüstriyel haberleşme

To My Family

#### ACKNOWLEDGEMENTS

I would like to thank my thesis supervisor Associate Prof. Dr. Şenan Ece Schmidt and my co-supervisor Associate Prof. Dr. Klaus Werner Schmidt for their valuable supervision and support. In addition to this, I like to thank them for giving me an opportunity to study industrial communication protocols. I also thank my colleagues Adem Kaya and Yusuf Bora Kartal for their contribution on integration of my thesis work to the system and system tests. My thesis was a part of a research project that was funded by The Scientific and Technological Research Council of Turkey (TUBITAK). I would like to thank TUBITAK for their project support.

I would like to thank my family, my wife and my colleagues in TUBITAK-UZAY for their support.

# **TABLE OF CONTENTS**

| ABSTRACT                                                                     | v    |

|------------------------------------------------------------------------------|------|

| ÖZ                                                                           | vi   |

| ACKNOWLEDGEMENTS                                                             | viii |

| TABLE OF CONTENTS                                                            | ix   |

| LIST OF TABLES                                                               | xi   |

| LIST OF FIGURES                                                              | xii  |

| INTRODUCTION                                                                 | 1    |

| BACKGROUND                                                                   |      |

| 2.1 Real -Time Ethernet for Industrial Communication Protocols               | 3    |

| 2.1.1 Requirements                                                           | 5    |

| 2.1.2 Real Time Ethernet Protocols                                           | б    |

| 2.2 Dependability                                                            | 10   |

| PREVIOUS WORK                                                                |      |

| 3.1 Dynamic Distributed Dependable Real Time Industrial Protocol (D Overview |      |

| 3.2 D <sup>3</sup> RIP Formal Protocol Model:                                |      |

| 3.2.1 Generic Interface Layer:                                               |      |

| 3.2.2 Generic Coordination Layer:                                            |      |

| 3.2.3 Generic Shared Medium Model:                                           |      |

| 3.2.4 Generic Dependability Plane Model:                                     |      |

| 3.3 D <sup>2</sup> RIP Implementation                                        |      |

| 3.3.1 Interface Layer (IL) :                                                 |      |

| 3.3.2 Coordination Layer (CL):                                               |      |

| 3.3.3 D <sup>2</sup> RIP Implementation Summary and Its Operation            |      |

| DEPENDABILITY PLANE IMPLEMENTATION                                           | 41   |

| 4.1 Overview                                                                 | 41   |

| 4.1.1 DP Implementation                                                      |      |

| 4.2 Data Structures                                                          |      |

| 4.3 Actions and Operation                                                    | 54   |

| 4.3.1 Actions                                                                |      |

| 4.3.2 Operations                      | 55 |

|---------------------------------------|----|

| EVALUATION OF THE DEPENDABILITY PLANE | 59 |

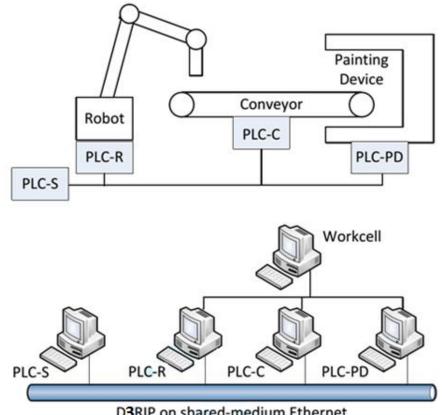

| 5.1 Example Description               | 59 |

| 5.2 Performance Parameters            | 66 |

| 5.3 Experiments and Results           | 69 |

| CONCLUSION & FUTURE WORK              | 73 |

| 6.1 Conclusion                        | 73 |

| 6.2 Future Work                       | 74 |

| REFERENCES                            | 75 |

| APPENDIX                              | 79 |

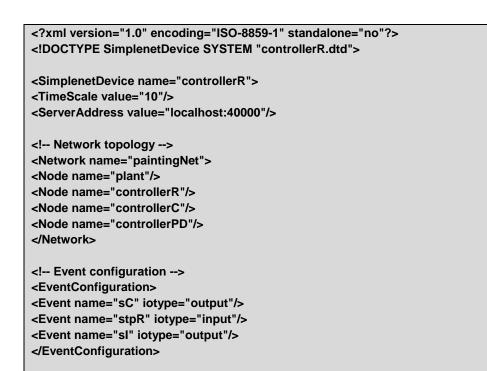

| XML FILES                             | 79 |

# LIST OF TABLES

#### TABLES

| Table 1:Shared Medium Industrial Ethernet Protocol                                   | 10               |

|--------------------------------------------------------------------------------------|------------------|

| Table 2: Frame Header Structure                                                      |                  |

| Table 3: vCL_Q_TYPE                                                                  |                  |

| Table 4: vIL_Q_TYPE                                                                  |                  |

| Table 5: QUEUE_TYPE                                                                  |                  |

| Table 6: Synchronization Accuracy and Sequential Actions in D <sup>3</sup> RIP Opera | tion Without Any |

| Fault                                                                                |                  |

| Table 7: Sequential Actions in D <sup>3</sup> RIP Operation With Fault               |                  |

| Table 8: Synchronization Accuracy and Sequential Actions in D <sup>2</sup> RIP       | Operation Before |

| Adding Dependability Plane [44]                                                      |                  |

|                                                                                      |                  |

### **LIST OF FIGURES**

#### FIGURES

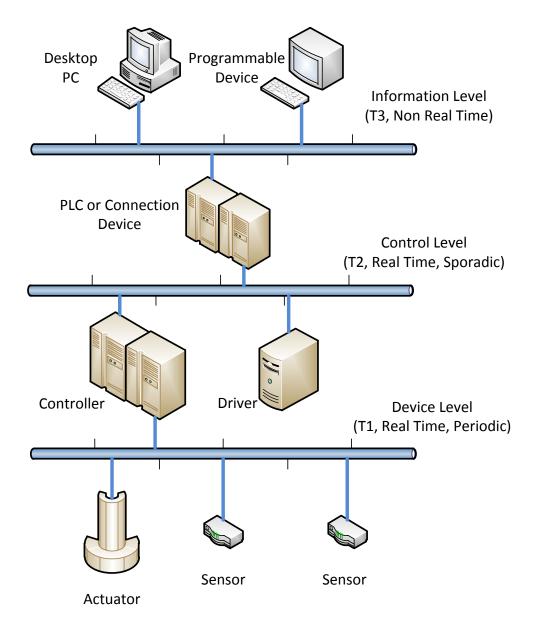

| Figure 1: Industrial Communication Levels [14]                                         | 4  |

|----------------------------------------------------------------------------------------|----|

| Figure 2: Additional Protocol on Ethernet Layers [29]                                  | 8  |

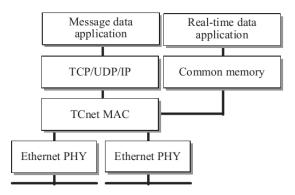

| Figure 3: TC-Net Structure [31]                                                        | 9  |

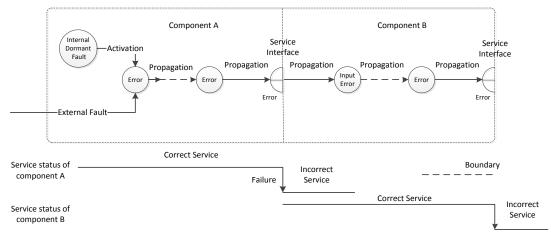

| Figure 4: Dependability Threats [20]                                                   | 11 |

| Figure 5: Domino Effect [38]                                                           | 12 |

| Figure 6: Creating Control Point and Rollback [40]                                     | 13 |

| Figure 7: D <sup>3</sup> RIP Layer Architecture                                        |    |

| Figure 8: Time Slot Structure                                                          | 16 |

| Figure 9: IL Model as TIOA                                                             | 19 |

| Figure 10: Internal Functions in IL Layer                                              | 20 |

| Figure 11: CL Model as TIOA                                                            | 22 |

| Figure 12: Update Functions for CL                                                     | 23 |

| Figure 13: SM Model as TIOA                                                            | 24 |

| Figure 14: Functions in Dependability Plane                                            | 25 |

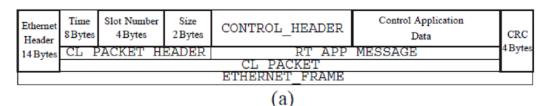

| Figure 16: Data Encapsulation of RT and Long nRT messages [44]                         | 28 |

| Figure 17: Message Transmission in IL layer                                            | 29 |

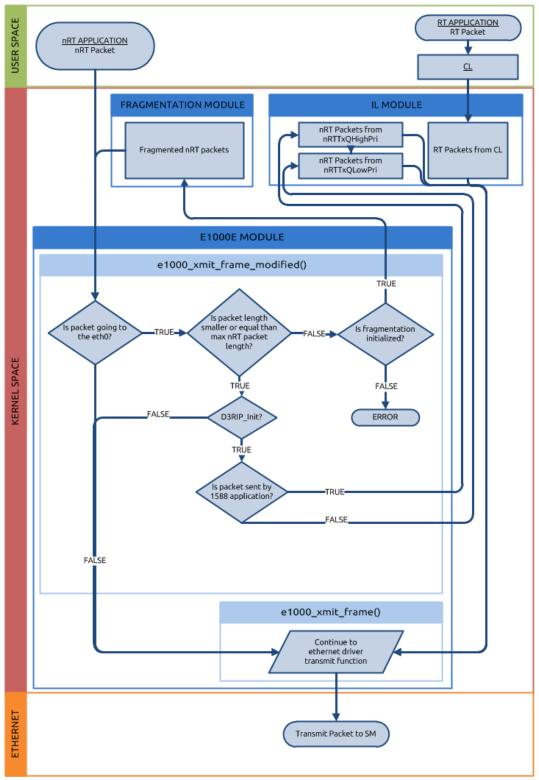

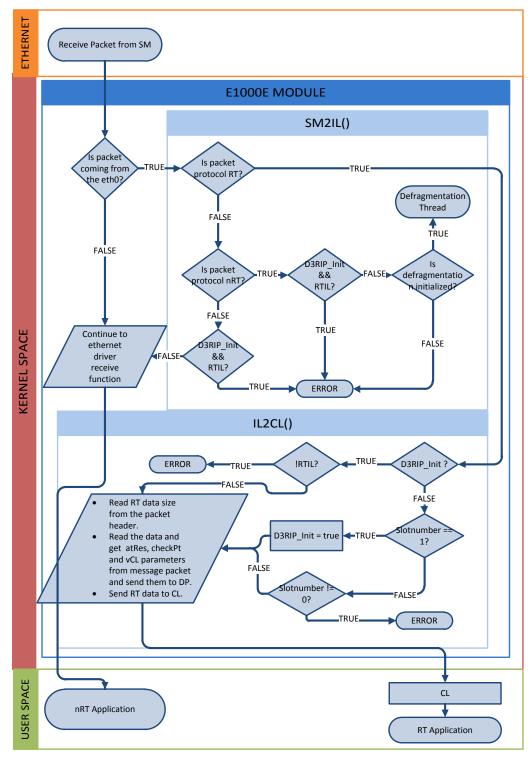

| Figure 18: The Algorithm of the Transmit Function                                      | 32 |

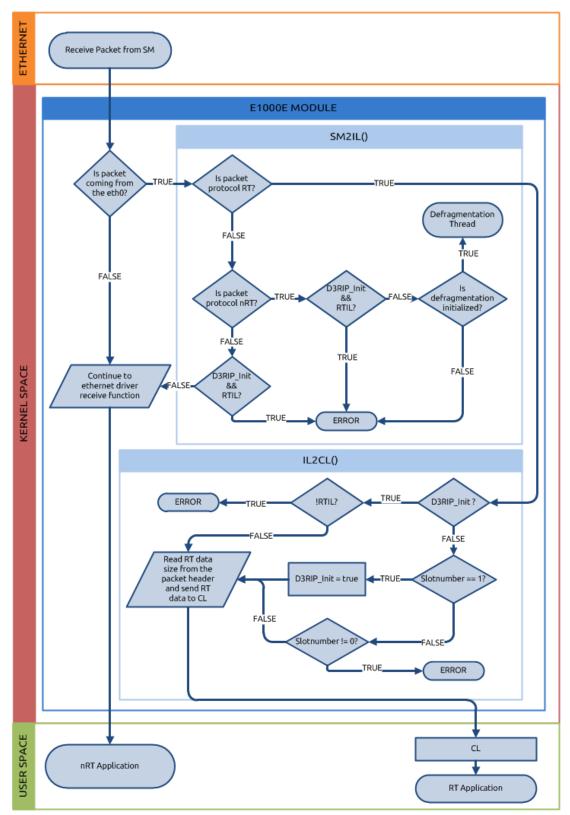

| Figure 19: The Algorithm of the Receive Function                                       | 33 |

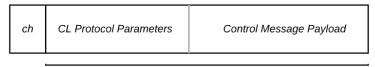

| Figure 21: Message Structure                                                           | 35 |

| Figure 22: Message Format in CL [29]                                                   | 35 |

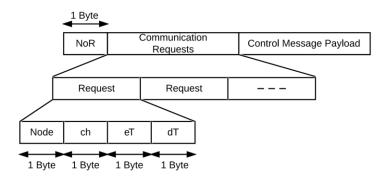

| Figure 23: CL Algorithm [29] [41]                                                      | 36 |

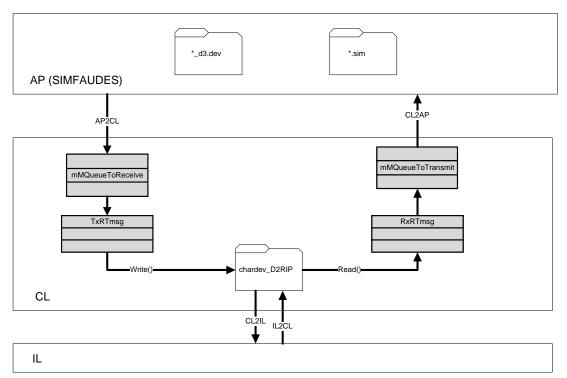

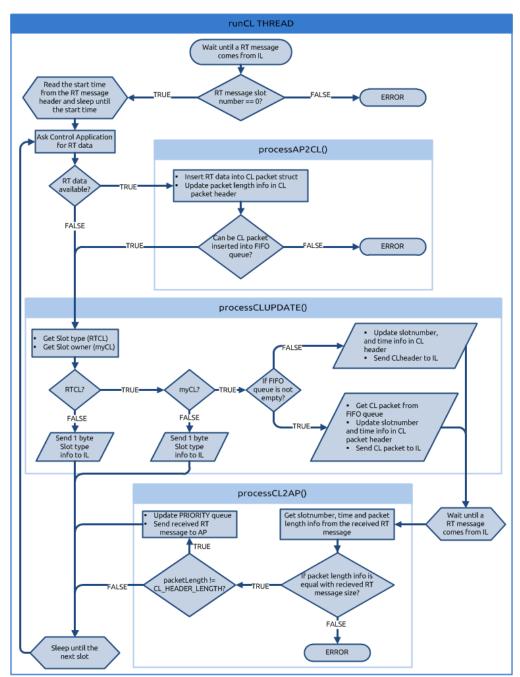

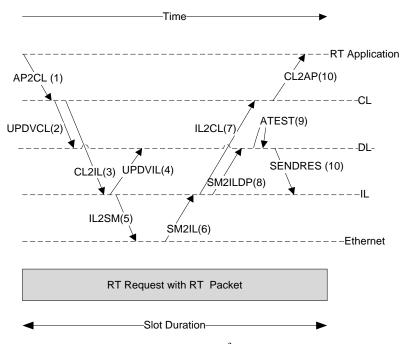

| Figure 24: The Message Transmissions of the Layers and Functions of D <sup>2</sup> RIP | 37 |

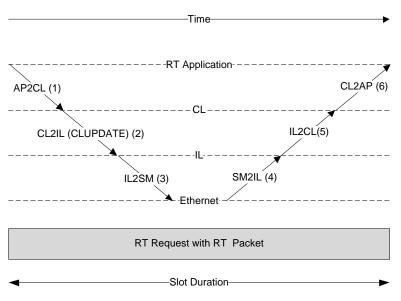

| Figure 25: The Timing of the Sending RT request with RT packet                         |    |

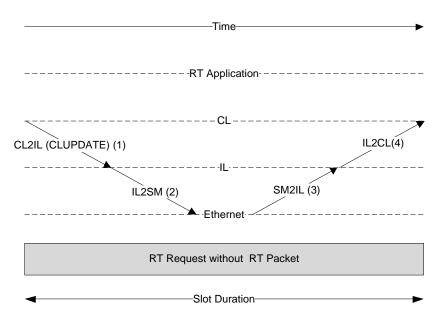

| Figure 26: The Timing of the Sending RT request without RT packet                      | 38 |

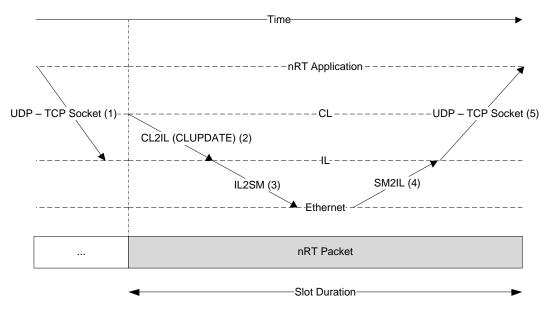

| Figure 27: The Timing of the Sending nRT packet                                        | 39 |

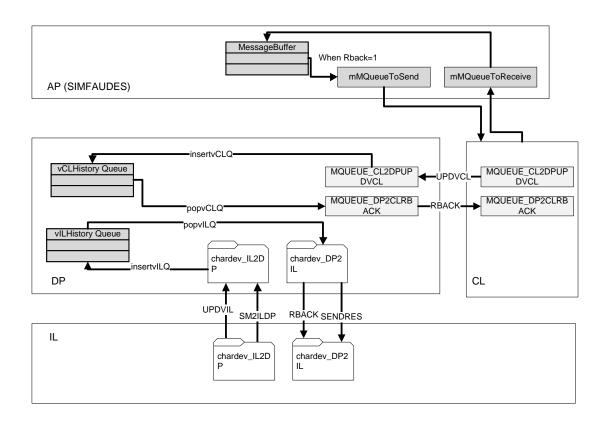

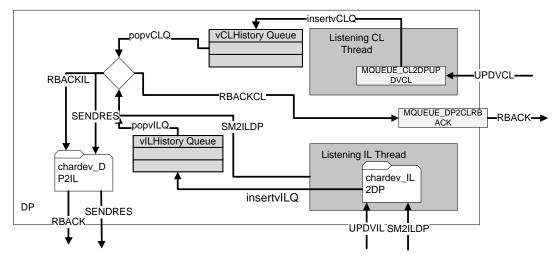

| Figure 28: Message exchange of DP with other layers.                                   | 42 |

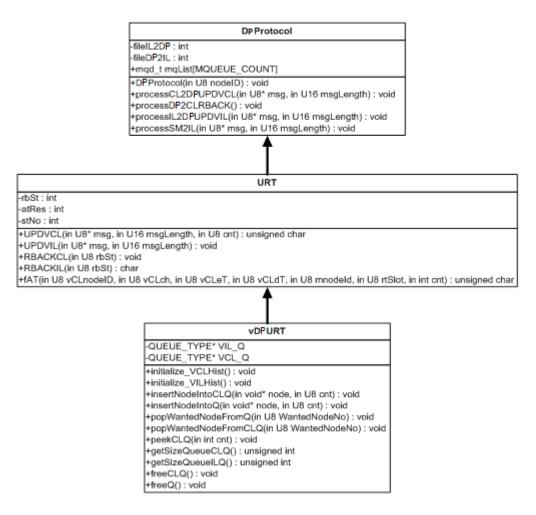

| Figure 29: Structure of DP                                                             | 43 |

| Figure 30: CL Implementation with DP                                                   | 44 |

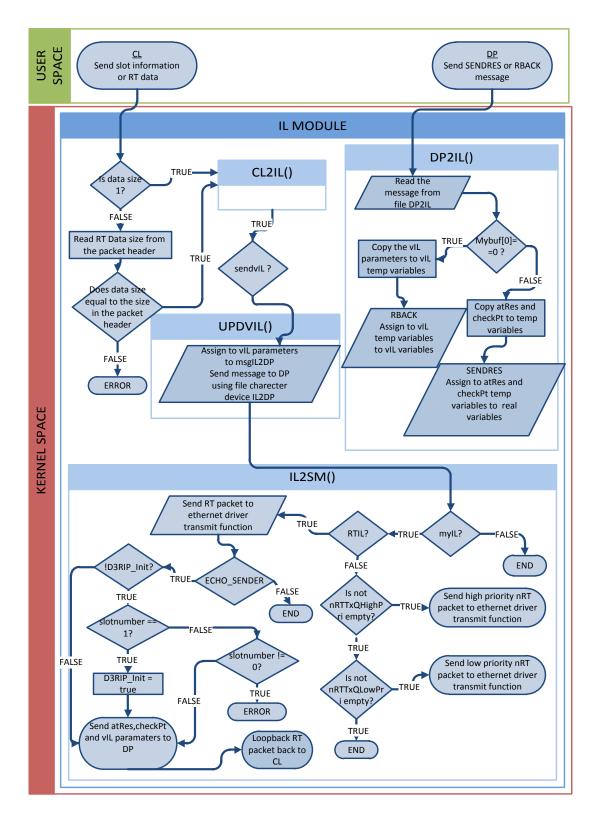

| Figure 31: Transmission Part of IL with DP Implementation                              | 45 |

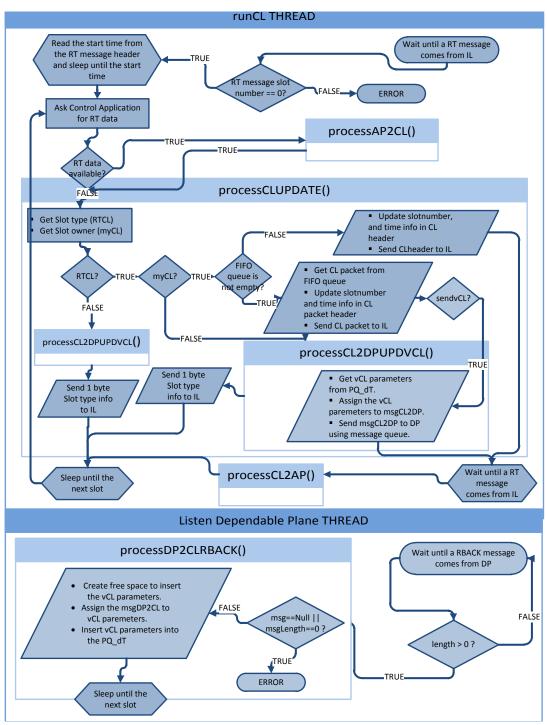

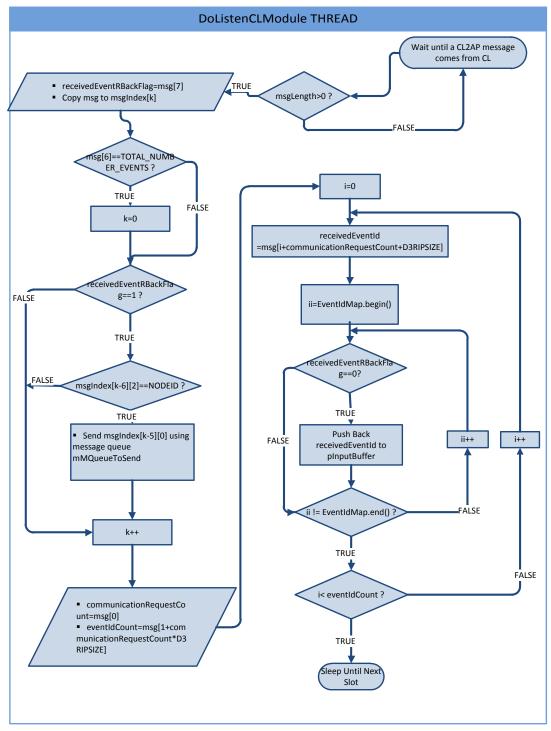

| Figure 33: DoListenCLModule Thread in AP                                               | 47 |

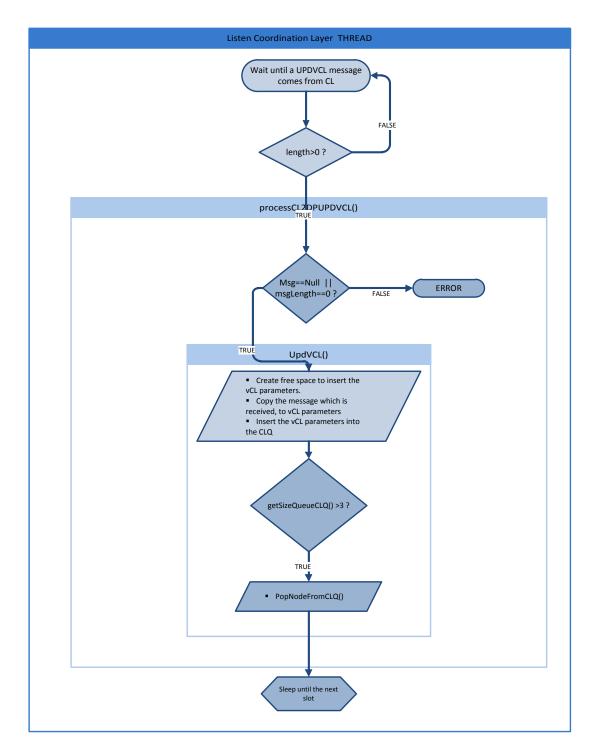

| Figure 34: listenCoordinationLayer Thread in DP Implementation                         | 49 |

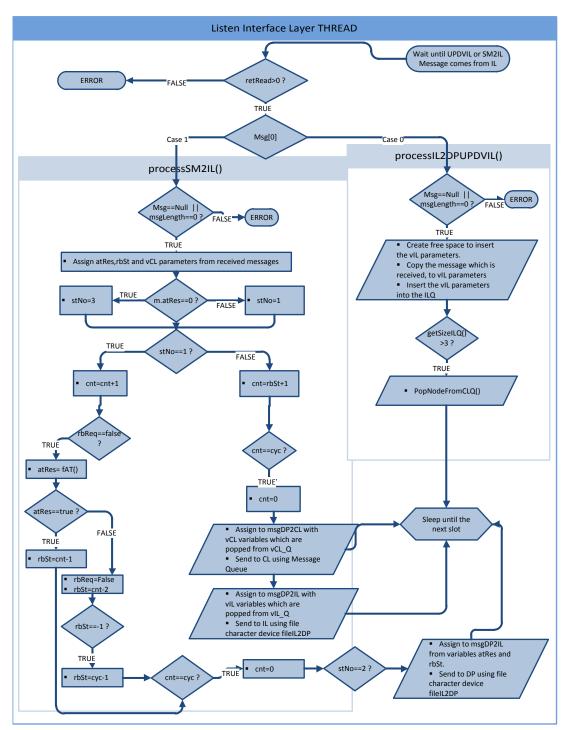

| Figure 35: listenInterfaceLayer in DP Implementation                                   | 50 |

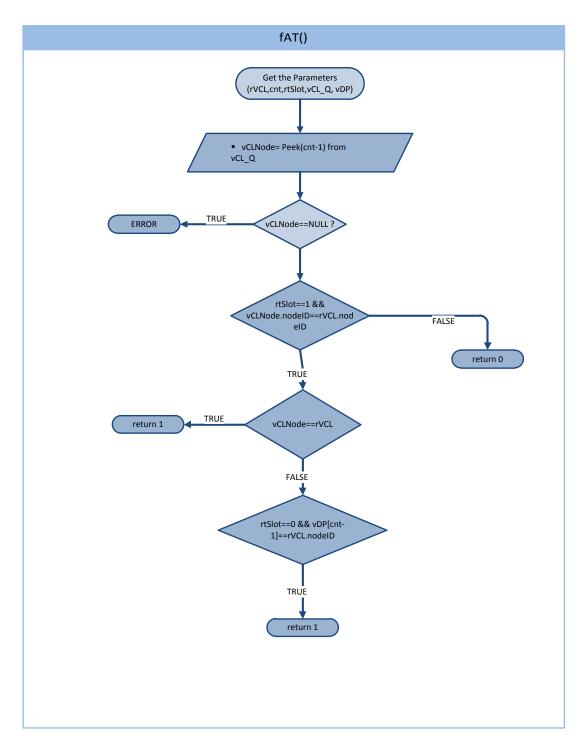

| Figure 36: f <sub>AT</sub> Implementation in DP                                        |    |

| Figure 37: Dependability Plane UML Class Diagram                                       | 52 |

| Figure 38: The Timing of the D <sup>3</sup> RIP without Any Fault                      |    |

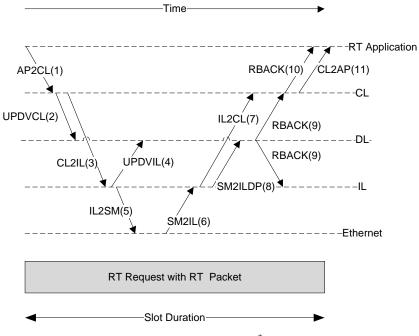

| Figure 39: The Timing of the D <sup>3</sup> RIP with Fault                             |    |

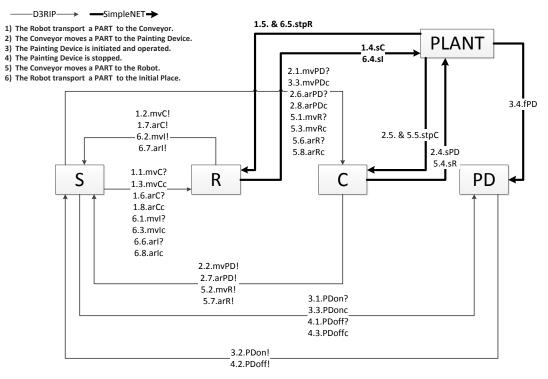

| Figure 40: A Manufacturing System [44]                                                 |    |

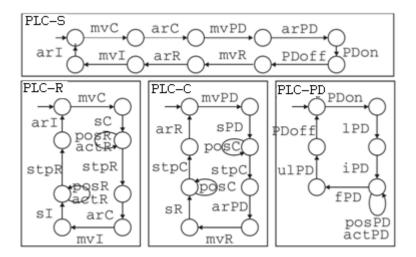

| Figure 41: State Machines of Workcell [12]                                             |    |

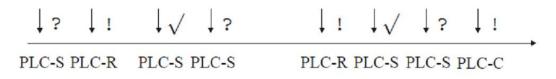

| Figure 42: The Timing Diagram for the PLC Communication of the Example Workcell [4     |    |

|                                                                                        |    |

| 1 |

|---|

| 4 |

| 4 |

| 6 |

| 9 |

| 0 |

| 0 |

|   |

#### **CHAPTER 1**

#### **INTRODUCTION**

Industrial control applications are nowadays realized using distributed controller devices that are connected by a real-time communication network. The amount of the transmitted data has been increased with the new control systems and the demand of these systems will be increased more and more in the near future. Traditional bus and control network solutions such as CAN [1], ProfiBus [2] and LonWorks [3] do not support the demanded requirements, because of their low speed, high cost and incompatibility with other devices and equipment.

Therefore, a different protocol is needed to support the stated requirements. Ethernet (IEEE 802.3) is a common proposition for the support of industrial control applications since it is cheap, commonly used, high speed andcompatible with other protocols. However, there is a problem to use Ethernet in real time (RT) communication. The reason is the CSMA/CD (Carrier Sense Multiple Access / Collision Detection) access protocol. In CSMA/CD access protocol, if a collision occurs on the network, the node which sends the packet to the other node, waits a random time to resend the packet. Also, the random amount of time is double increased if a collision occurs again. This causes non-determinism and impairs the RT timing requirements. To overcome this problem, there are various solutions in the literature. Common solutions are:

- Modification of the Medium Access Control

- Adding Transmission Control Over Ethernet

- Using Switched Ethernet

In modification of MAC solution, specialized chips (ASICs) are used to modify the Ethernet hardware. Sercos [4], Ethercat [5], Profinet IO [6] are examples of modification of MAC solutions. They are used as RT Ethernet protocol, but their high cost and incompatible with other equipments are the problem of the modification of MAC. In adding transmission control over Ethernet solution, there are several different ways of doing this. Master /slave, Token Passing and TDMA methods are used to solve the problem by adding transmission control over Ethernet. Virtual Token Passing Ethernet [7], Ethernet Powerlink [8], Modbus/TCP [9], Ethernet for Plant Automation (EPA) [10], FTT Ethernet [11] are examples of adding transmission control over Ethernet. In using switched Ethernet solution, there are multiple transmission paths and switches are used instead of hubs that is, each network interface card (NIC) only receives traffic which is addressed to it. However, this solution is not enough to make Ethernet real-time due to the non-deterministic queuing delays in switches.

The new RT Ethernet protocol, Dynamic Distributed Dependable Real Time Ethernet Industrial Protocol ( $D^{3}RIP$ ) is proposed in article [12]. This protocol is fully distributed, uses COTS Ethernet hardware and time-slotted transmission control based on the IEEE 1588 time synchronization protocol [13]. No hardware modification is required. It supports both RT and nRT traffic. D<sup>3</sup>RIP is an extension of the two-layer protocol D<sup>2</sup>RIP by dependability functionality in the form of a dependability plane. The interface layer (IL) and coordination layer (CL) of D<sup>2</sup>RIP were implemented in [41]. In this thesis, the additional dependability plane of D<sup>3</sup>RIP is studied, implemented and evaluated based on an application example, In this example, four distributed controller devices communicate with each other over  $D^{3}RIP$ . Several test scenarios show the functionality of the dependability plane. The remainder of the thesis is organized as follows. RT Ethernet for industrial communication, requirements of them and dependability are discussed and available RT Ethernet protocols are reviewed in Chapter 2. Formal protocol models and the implementation of a generic shared medium, a generic interface layer, a generic coordination layer and a generic dependability plane are explained in Chapter 3. The implementation of the dependability plane is described in detail in Chapter 4. The test scenario with 4 controllers and configuration of simulator, performance parameters, experiments and results are studied in Chapter 5. The conclusion and future works are presented in Chapter 6.

#### **CHAPTER 2**

#### BACKGROUND

#### 2.1 Real -Time Ethernet for Industrial Communication Protocols

In industrial applications, industrial communication network and protocol are used for communication among control nodes and equipments. RT access, deterministic behavior and RT are the reasons why industrial communication protocols are used so often in control applications. In control applications, different components are used to implement the control system: controllers, remote controllers, supervisory stations, actuators and sensors are some of the components that are used. Sensors collect feedback data, controllers control the system according to receiving data from sensors using actuators. Actuators transform input signals into motion. Supervisory stations are the intelligent part of the control system. It is used as a monitoring part and computer in the system. All different parts are connected with each other using industrial communication networks.

Nowadays, industrial communication networks are widely used by industrial control applications and these industrial control applications become more complex and large-scale. Also computer aided industrial control devices with the network access are manufactured in recentyears. These developments make industrial control systems become an important industrial and academic research topic. Different industrial communication networks have been developed for the last twenty years for these systems.

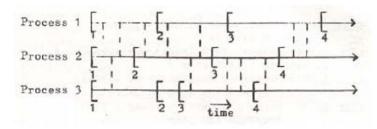

In different industrial communication networks, messages for the different purposes are transmitted to each device in the system. These industrial communication networks are divided as follows: [14] (Figure 1)

- T1) Device level data transmission between sensors, controllers and actuators: The receiving sampled data is periodic and it must be sent with time constraints.

- T2) Control level data transmission between supervisory controllers and the system components: It is needed that controllers and the system components at different hierarchical levels communicate each other for their coordination in the system. Mostly, components and controllers send the data which is event-based and requires deterministic response times, to each other. Because of the changing of the system behavior in discrete time, the next state of the system and the message which is sent in that case, have been already known using system dynamic model. For example, the controller which controls the two machines sends a message to the second machine to start, when the first machine completes its operation.

- T3) Information level data transmission: Mostly, it is used for the nRT and eventbased communication.

When these traffic types are analyzed, there are four requirements that should be fulfilled by

the network to make it usable for industrial control: there should be RT traffic transfer, synchronized communication, dependable operation and support for nRT traffic. In RT traffic transfer requirement, when a node in the control system wants to send a message to other nodes, this message transfer time should be less than a deadline time of the message. In synchronized communication requirement, before the RT communication starts, all nodes in the system are synchronized to get the RT message successfully. In dependability requirement, if there is a failure in the system, the system should be able to fix the problem and resume its correct operation. In support for nRT traffic requirement, nRT messages should be sent without corrupting the RT traffic.

Figure 1: Industrial Communication Levels [14]

In 1980's CAN, Lonworks, Profibus started to be used as industrial communication network. [15]. But, their implementation cost is high, expanding the system is difficult and they are not compatible with other communication protocols. So, these problems are the reason for developing and using different protocols. Ethernet can be used for industrial communication protocol. However, Ethernet is not directly usable as industrial communication protocolwithout any modification on hardware or software. Because, it does not support the RT traffic when collisions occur in the system. When a collision happens, back-off algorithm runs and the node which wants to send a message to the system, waits a random time. It creates non-determinism on the system. So, generic Ethernet without any modifications cannot be used for industrial communication. However, the application of Ethernet is simple, widely used and low cost are the reason why there is a considerable research effort on modifications and additions to Ethernet in order to make 1t usable as a RT communication protocol.

#### 2.1.1 Requirements

The requirements for the development of the real-time Ethernet protocol are listed below: [16]

<u>Real Time Data Transmission</u>: Message transmission time is measured between the applications which are sent and received. The requirements of the message transmission time for the different level communications are different. While the applications including human operators require 100 ms transmission time, applications working with programmable logic controllers (PLCs) require 10 ms transmission time and applications which coordinate many devices, require 1 ms transmission time.

<u>Synchronization Support:</u> In industrial communication network, RT response time and common reference time between nodes are provided by synchronization protocol. The sensitivity of the synchronization is defined the maximum deviation between the time of two nodes [16]. To protect this sensitivity of the synchronization, guard periods are used and this causes the increasing of the time delay. The most common and used synchronization protocol for Ethernet is IEEE 1588 time synchronization protocol [13] [17].

IEEE 1588 time synchronization protocol works according to Precision-time protocol (PTP). In this protocol, time difference and delay time between the selected master node and other nodes are calculated using message exchanges between master node and slave nodes. Thus, nodes are synchronized. Except IEEE 1588, special time synchronization mechanisms are used in EtherCAT [4] and Sercos (IEC 61491) [5] protocols.

<u>Non-Real Time Traffic Support:</u> It is provided that while nRT traffic is supported, the RT traffic is not affected nRT traffic.

<u>Compatibility</u>: The most important reason that makes Ethernet an attractive technology is inexpensive hardware and software interface. It is required that when industrial Ethernet works, it is compatible with standard Ethernet to make implementation with COTS (Commercial Off-The-Shelf) components and to take advantage of inexpensive hardware andsoftware interface. In addition to this, it is also supposed that commonly used application protocols such as HTTP and FTP and synchronization protocols such as IEEE 1588 are supported. There are backward-compatibility requirements. For this reason, it is expected that

once a protocol has been established, it works for years. As a result, an industrial Ethernet protocol should be conducive to adding new devices.

Dynamic Resource Separation for the Real-Time Traffic: The communication requirements of the industrial system which communicates with a network, change dynamically in time [18]. For instance, in the self-triggered control concept, at the device level, calculation times are reserved before. In addition to this, high-level controllers which coordinate the distributed systems, communicate only when they are needed. It is supposed that according to instantaneous needs, RT bandwidth should be separated to devices in the industrial Ethernet protocols.

Dependability: Dependability is an important requirement for the applications which have critical security constraints and work in the industrial control systems [19]. Availability, safety, integrity and maintainability are the elements of dependability [20]. To talk about the dependability of a distributed industrial control system which communicates with the network, it is provided that the dependability of the network and controller is necessary. designing a dependable industrial communication network, dependable When synchronization and the consistence of values which are sent with messages, are important. The problem of dependability stands outmore RT Ethernet-based solutions due to nondeterministic feature of Ethernet [21]. Dependable communications provide that accurate information should be sent to the right place, at the right timeand right order. Dependability support is often done by the separation of the static additional capacity according to default worst case [22]. For example, for the TDMA-based protocol additional time slots might be allocated to the transmitting nodes inorder to send each message which is lost, in repetition time and only half of the capacity can be used.

#### **2.1.2 Real Time Ethernet Protocols**

In the literature, there are four major approaches to add Ethernet real-timeliness:

- Changing the non-deterministic sending messages mechanism with the hardware modification on Ethernet network interface card,

- Minimizing response time and the probability of the collision,

- Removal of the probability of collision on shared medium using point-to-point connections and switches,

- Constructing layers on top of shared medium to avoid collision.

<u>Specialized Hardware</u>: EtherCat [4], SERCOS III [5] and ProfiNet [6] use specially designed node and switch hardware. Ethercat and ProfiNet use IEEE 1588 for time synchronization. On the other hand, SERCOS III uses special messages to synchronize the nodes in the system. These three protocols are supported by special designed dependable protocols. Special designed, Twinsafe Protocol operates as separate layer under EtherCAT protocol. Devices get addresses and data safety is provided with CRC. In SERCOS III Safety, there are sequence numberanda timestamp in the message. The receiver node sends an acknowledgment message to the sender node. Devices get addresses and data safety is provided with HDLC coding.PROFIsafe is developed for ProfiNet [6]. Sequence number and a timestamp are added in the message. Devices get addresses and data safety is provided with CRC.

<u>Non-Guaranteed Approaches:</u> MODBUS/TCP [9] and similar protocols work on TCP/IP to be compatible with standard Ethernet [23] [24]. With traffic shaping, it low delays can be achieved in these systems. In these approaches, there is no guarantee that messages will be transmitted in time.

<u>Switched Ethernet:</u> Since collisions are possible on standard Ethernet, the solution of the non-deterministic network access problem is full-duplex, switched and point-to-point Ethernet (IEEE802.3x). With this structure, even if shared medium and the collision problem are eliminated, the problem of network access is carried to queueuing delays in the network [22][25][26]. To provide the RT communication, Ethernet switches that make scheduling and prioritization are needed. Giving priority to the messages, according to these priorities, providing different service like 802.1p and 802.1Q Ethernet protocols and protocol extensions are proposed. Unlike the standard Ethernet protocols, these protocols require specialized switches. Under the assumption of an infinite buffer for real-time traffic, even if scheduling analysis can be made, the actual conditions require the use of a limited buffer [27]. On switched Ethernet, the implementation of the sensitive time synchronization which is important for RT communication, can be difficult.

Ethernet/IP (EIP) [28] works on the TCP/IP with full-duplex Ethernet switches which have special prioritization mechanism. Ethernet /IP protocol does notensure the real-time communication. Time synchronization is made with special messages which are compatible with IEEE 1588 protocol. Also, the coordination between sender and receiver, is provided with the ping messages. There is also timestamp in the messages. Devices get addresses and data safety is provided with CRC.

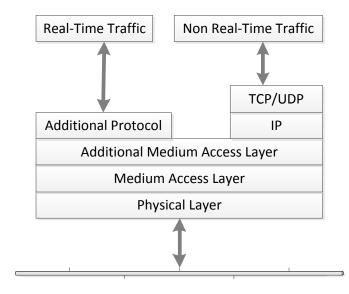

<u>Constructing Layer on Shared Medium</u>: A variety of academic and industrial protocols are proposed to prevent collisions on shared medium by adding RT properties. These protocols aim at adding a layer on IEEE 802.3 that prevents collision and non-deterministic sending messages after collision. NRT and RT traffic pass over this layer. On this layer, there may be a specific protocol which is responsible for transmission of RT traffic. TCP-UDP/IP layers may be responsible for transmission of RT traffic. Figure 2 shows the additional protocol on Ethernet layers.

There are 3 different approaches for adding layer on medium access layer:

- Time Division Multiple Access (TDMA)

- Master-Slave

- Token Passing

<u>Time Division Multiple Access (TDMA)</u>: In this approach, time is divided into equivalent slots. The owners of one or more time slots are determined statically for each node. Time synchronization between all nodes in the system, is important for communication between nodes. This approach provides reliable network access for all nodes. Working with low efficiency is the disadvantage of TDMA. If a node does not send a message in the time slot which is belongs to that node, another node in the system cannot send a message in that unused time slot. In addition to this, the delay in the software and switches is also considered while choosing the time slot. If the messages in the network arelostdue to network errors, additional time periods must be allocated to send messages again.

Communication Network Figure 2: Additional Protocol on Ethernet Layers [29]

<u>Master-Slave</u>: A chosen master node sends messages to the other nodes (slaves) to ask whether it needs to send a message or not (polling). Slave nodes only send message when master nodes poll them. This approach is used in the network which has small number of nodes. The efficiency of master slave is affected negatively while polling the system. Especially in cases wherethe trafficis very variable and nodes do not have any message to send, the efficiency decreases. Also, the delay time which is passed when the master node waits slave node's answer, decreases the efficiency. When the number of nodes is large, the polling cycle time for all nodes, is more than the delay time of sending message. In that case, the delay time is much more than acceptable limit. The speed of software in the slave nodes also is the one of thedetermining factors of the polling process time. If the software is too slow, the importance of the network speed is ignored and the efficiency of the network is decreased. In addition to the problem of the efficiency, master-slave communication is not a suitable structure for distribution. Because of master node, it is single-centered and there might be a problem at a single point.

<u>Token Passing</u>: In this approach, one node can send a message if and only if it has a token to send a message. When it sends its message, it transmits the token to another node with a special message. In token-based approaches, the possibility of losing the token, token circulationtime which causes decreased communication speed and the difficulty of adding a new component are the disadvantages of token passing system.

There are lots of solutions which are created in industry and academia. These solutions and standards follow the approaches which are explained the section above and they carry on the negative aspects of them.

Time Critical Control Network (TC-Net) [30] is implemented with adding a layer on standard Ethernet which provides the token passing. NRT traffic has low priority. Time

synchronization is provided with the special message. The dependability of the protocol is also provided using an extra TC-Net card. Figure 3 shows the TC-Net structure. [26][31].

Figure 3: TC-Net Structure [31]

Powerlink (EPL) [8] is implemented with adding a layer on standard Ethernet which provides the master-slave. With the inefficiency of the master-slave structure, EPL efficiency is calculated as 25% [22]. Time synchronization is provided with the special message similar to the IEEE 1588 protocol. RT and nRT data are sent in different time slots. Sequence number and a timestamp are added in the message. Devices get addresses and data safety is provided with CRC.

Ethernet for Plant Automation (EPA) [10] works with static TDMA. Time slots for nRT and RT are determined before the communication. It supports both RT and nRT traffic. IEEE 1588 time synchronization protocol is used to synchronize the nodes in the network. The disadvantage of this protocol is static slot scheduling and TDMA. Slot scheduling is done by periodic message broadcast. Also, to the guard periods and error recovery precautions cause low efficiency in TDMA solutions like EPA. [16] [26]

In FTT Ethernet protocol, master/multi-slave model is used to implement the protocol. It uses COTS Ethernet hardware. The communication is TDMA based and time slot durations are fixed. Nodes can be connected to share or switched medium. It supports both RT and nRT traffic, also in addition to them, there is online admission control to guarantee timeliness to the RT traffic. Also there is no specific synchronization protocol. But, elementary cycle begins with master node trigger. When master node broadcast to trigger message, elementary cycle is started with that trigger message. The disadvantage of the FTT Ethernet protocol is that master-slave method. Master-slave models have single point of failure, undistributed structure and low efficiency. [11][32]

In Virtual Token Passing Ethernet (VTPE), if a node wants to hold a network, it should takethe virtual token to send a message to other node. In this method a virtual token is circulating between nodes and it works with closing the binary exponential back off (BEB) algorithm. When there is collision in the system, it provides that the nodes send the RT message again immediately. In this protocol, Ethernet hardware is not modified. It uses

COTS (commercial off-the-shelf) Ethernet. Software Ethernet driver modification is required for RT stations. Figure 4 shows the algorithm of VTPE. The disadvantage of the VTPE is losing token which is the dependability problem of token passing method. [7]

The focus of this study is working with compatible components without changing the working principle of Ethernet and providing guaranteed real-time performance for shared media protocols. Table 1 shows the comparison of the defined requirements and performance criteria for these protocols. In table, A/I: Academic/ Industrial Purpose, RT Cap: RT Data Transmission Capacity, nRT Cap: NRT Data Transmission Capacity, Time Sync: Time Synchronization Protocol are used as abbreviations.

|     |                                                   | Mediu             |                       | Node            | RT                                                    |                 |                                                                    |

|-----|---------------------------------------------------|-------------------|-----------------------|-----------------|-------------------------------------------------------|-----------------|--------------------------------------------------------------------|

| A/I | Protocol                                          | m<br>Access       | Delay Number          | Cap.(bps<br>)   | nRT Cap.                                              | Time Sync       |                                                                    |

| I   | EPA                                               | TDMA              | 5ms,<br>100μs         | 32, 64          | 12.28M                                                | 0,85            | ΙΕΕΕ<br>1588,10μs,<br>1μs                                          |

| I   | EPL                                               | Master-<br>Slave  | 400μs,<br>5.5ms       | 4,15            | 15.2M,<br>32M                                         | 19.6%,<br>4.4%  | IEEE 1588,1s                                                       |

| I   | Time<br>Critical<br>Control<br>Network<br>(TCNet) | Token-<br>Passing | 2ms/<br>20ms/<br>200m | 24,13           | 58.4M/<br>51.2M/<br>7.2M,<br>45.6M/<br>40.8M/<br>4.8M | 0%,<br>20%      | -                                                                  |

| А   | FTT-E                                             | Master-<br>Slave  | 1ms                   | Unspecifie<br>d | 36M,<br>36%                                           | 0,11            | Periodic Time<br>Sychronizatio<br>n Message<br>from Master<br>Node |

| А   | VTPE                                              | Token-<br>Passing | 5.8ms                 | 256             | Under<br>40%<br>Ethernet<br>Cap.                      | Unspecifie<br>d | -                                                                  |

Table 1: Shared Medium Industrial Ethernet Protocol

#### 2.2 Dependability

Dependability is defined as the ability to deliver service that can be justifiably trusted. Also, it includes the attributes below: [20][33].

- Availability: A system is ready to provide the right service.

- Reliability: A system continues to right service in a time.

- Safety: A system does not lead to irreversible errors at the user level.

- Maintainability: A system can be conducive to repair and can be available to maintain when needed

- Integrity: System changes are suitable for designed sequence and there are not any unexpected system changes in the system design sequence.

System is dependable when it fulfills (some of) the above attributes. Also, system must have precautions against threatened dependability of the system elements at the design and operation stages. Threatened dependability of the system elements are divided into the three main categories. These categories are: [20] [33] [34]

- Component-Level Errors (Faults)

- System-Level Errors (Errors)

- User-Level Errors (Failures)

Figure 4 shows the faults cause-effect relationship.

Figure 4: Dependability Threats [20]

As can be seen in Figure 5, faults which occurred and are not solved at the component level proceed to the user level. After that the system cannot work properly. Bringing back the correct function of the system, error conditions should be eliminated.

Means (dependability activities) are activities for elimination of errors and allocation of the dependability of the system at various levels. They are divided into 4 main groups: [20] [33] [35]

- Component-Level Fault Prevention Activities: Fault prevention activities are the activities which prevent the faults at the design stage. Keeping records of faults at the designed system and modify it during the design process is the most common example. [36] [37].

- Component-Level Fault Removal Activities: Error detection, classification and validation phases of the system design phase of these activities aims to eliminate the errors. System verification is a method which provides confirmation of fault before debugging and supports system requirements after debugging.

- Component-Level Fault Forecasting Activities: Fault forecasting activities are the activities which determine the state changes that cause user-level faults after completed system design.

- Component-Level Fault Tolerance Activities: Activities of detection and elimination of errors that can occur during operation of the system. Elimination of effects of the system faults is called system recovery [20]. The most common method without having to initialization (reset) while system is operating is making checkpoint and rolling back.

In this method, functions in a distributed system record their state in error conditions that may occur. In the event of any error, functions return to their pre-recorded states within the scope of the error recovery scenario operated by the system. Although at first glance it seems to be an easy method of application, in some conditions rollback mechanism causes consecutive rollbacks which might return the system to its initial state. In other words, it causes reset of the system. Figure 5 shows that situation which is called domino effect.

Figure 5: Domino Effect [38]

In Figure 6, lines with dashed vertical show the communication of functions. 3 processes in Figure determine the rollback point periodically. For example in process 3, an error after 4th recovery block is identified. This situation causes that process 3 returns to the 4th recovery block. When process 3 returns to the 4th recovery block, the other two processes have to return to their previous recovery point to be compatible with process 3. The reason why the other two processes have to return to their previous recovery point is that process 3 communicates with the other two processes between error and 4th recovery block. With the same logic, rollback mechanism causes that the system returns to its initial state, like toppled dominoes one after the other.

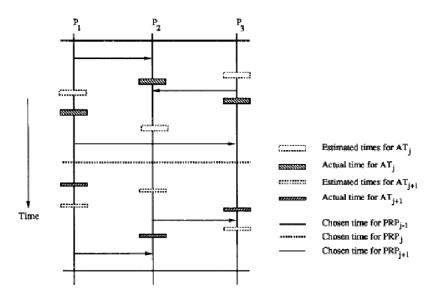

In order to stop the domino effect, a communication mechanism between processes is recommended [39] [40]. In these articles, proposed communication mechanisms cause additional load on the system message traffic. However, it seems that [40]'s proposed idea causes less additional load on the system message traffic than other one. In [40], the use of a common reference time between functions is proposed to reduce the additional load on the system message traffic. Figure 6 shows the proposed control point description and rollback mechanism.

Figure 6: Creating Control Point and Rollback [40]

Figure 7 shows that distributed nodes run synchronous with each other. Common period of time is determined for synchronous nodes to make an acceptance test. Node which does not complete acceptance test within the specified time, sends its delay time to other nodes to determine the synchronous recovery points. This reduces the additional load on the system message traffic. However, currently only available in recovery point messages are used for identification purposes in the network, and this adversely affects the efficiency of the network. In our framework, distributed nodes are synchronous. In addition to this, communication between the nodes is on the shared medium. Dependability plane in our framework uses the advantages of these two features and it is aimed to eliminate the additional message load on the system.

#### **CHAPTER 3**

#### **PREVIOUS WORK**

# **3.1 Dynamic Distributed Dependable Real Time Industrial Protocol (D<sup>3</sup>RIP) Protocol Overview**

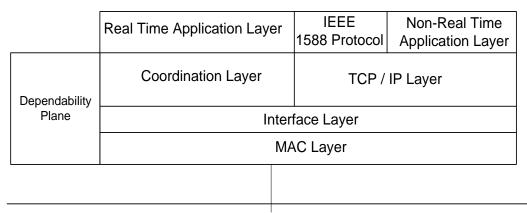

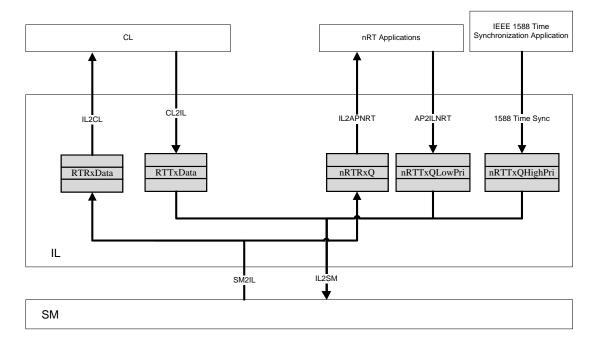

Dynamic Distributed Dependable Real Time Ethernet Industrial Protocol can be used for the communication of controllers in distributed control systems. Dynamic Distributed Real Time Ethernet Industrial Protocol works over Ethernet protocol with non-real and RT traffic. There is no need to change the physical MAC layer, it uses COTS Ethernet hardware.  $D^{3}RIP$  protocol works on shared medium without using any switch. It realizes TDMA on top of Ethernet, whereby synchronization is achieved by the IEEE 1588 protocol. It requires small software Ethernet driver modification and modifications of the software stack between MAC and Application layer. Figure 7 shows the layered architecture of  $D^{3}RIP$ . The Dependability Plane works over  $D^{2}RIP$  structure that is implemented in [41].

Shared Medium

Figure 7: D<sup>3</sup>RIP Layer Architecture

In D<sup>3</sup>RIP Layer Architecture, there are 3 different layers added to the original Ethernet layer architecture namely interface layer (IL), coordination layer (CL) and dependability plane (DP). Interface layer is responsible for the time-slotted TDMA structure that is implemented and synchronized with other nodes using IEEE 1588 time synchronizing protocol. At the beginning of each time slot, CL sends information to the IL about the usage of the time slot and IL sends Ethernet frame within time slot when it gets information from CL. Coordination layer is responsible for determining the allocation of the type of slot whether

RT or nRT and the allocation of the owner of the slot. CL is implemented in the user space of Linux and IL is implemented in the kernel space of Linux in previous works [29][42]. In these works, CL is implemented as 2 types: DART (Dynamic Allocation Real-Time Protocol) and URT (Urgency-Based Real-Time Protocol). In DART, variables in the protocol are hold in the form of allocated RT slots. In URT, control application variables are stored in the form of the communication requests [29]. Also, IL is implemented as 2 types: RAIL (Real-Time Access Interface Layer Protocol) and TSIL (Time-Slotted Interface Layer). In RAIL, slot allocations for nRT and RT traffic are made statistically. In TSIL, slot allocations for nRT and RT traffic are made dynamically by CL [42].

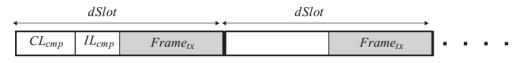

Dependability Plane is responsible for dependability of the framework. DP makes an acceptance test whether the protocol works without problem or not. If there is a fault, it sends stored CL parameters using rollback message to CL and when CL gets the rollback message from DP, it warns application layer to resend the fault messages. Thus DP protects the framework. Timing of messaging between layers is important to determine the slot timing duration. Figure 8 illustrates the timings of 1 slot.  $CL_{cmp}$  which is a calculation time for IL and Message Tx, which represents transmission of an application message on Ethernet.

Figure 8: Time Slot Structure

$D^{3}RIP$  Layer Architecture works on the RT operating system. RT features of the operating system kernel are gained with RT patches over the Linux kernel. The latest stable kernel is 3.6.2. The configurations below are needed for RT operating system after RT patches implemented over Linux kernel:

- Activate Tickless System (Dynamics Ticks).

- Activate High Resolution Timer Support.

- Set"Preemption Model" parameter to "Fully Preemptible Kernel(RT)".

- Set "Timer frequency" parameter to "1000Hz".

- Deactivate "Suspend to RAM and standby".

- Activate "Timestamping in PHY devices".

- Activate "PTP Hardware Clock (PHC)".

- Activate "PTP clock support".

- Deactivate "Show timing information on printks".

- Set "I/O scheduler" parameter to "Deadline".

#### **3.2 D<sup>3</sup>RIP Formal Protocol Model:**

#### 3.2.1 Generic Interface Layer:

Interface Layer Generic Model is defined using TIOA Model in [12][43]. Figure 9 shows the IL Model using TIOA. There are 6 parameters in the IL Model: dSlot, t0,t1,t2, t3, M, Q, AIL,HIL.

- *dSlot:* Slot duration,

- t0, t1, t2, t3: Time of events,

- *M*: The type of transmitted messages,

- *Q*: The type of a FIFO queue messages,

- AIL: Abstract variable of IL.

- *HIL*:Abstract variable of IL

IL Model as TIOA has variables to define the model and operations:  $now_i^a$ ,  $next_i^d$ ,  $TxRT_i^d$ ,  $TxnRT_i^d$ ,  $RxRT_i^d$ ,  $RxnRT_i^d$ ,  $RTIL_i^d$ ,  $myIL_i^d$ ,  $vIL_i^d$ ,  $reqIL_i^d$ .

- *now*<sub>*i*</sub><sup>*a*</sup>: Analog variable which evolves with the time derivative of 1, the updated time information is provided by this variable.

- $next_i^d$ : The end of the current time slot is stored by this variable.

- $TxRT_i^d$ : The buffer that stores the RT messages to be transmitted.

- $TxnRT_i^d$ : The buffer that stores the nRT messages to be transmitted.

- $RxRT_i^d$ : The buffer that stores the RT messages that are received.

- $RxnRT_i^d$ : The buffer that stores the nRT messages that are received.

- $RTIL_i^d$ : The variable that stores the type of next slot whether RT or nRT.

- $myIL_i^d$ : The variable that stores whether the device owns the next time slot or not.

- $vIL_i^d$ : The variable that holds the additional information of the protocol operations.

- $reqIL_i^d$ : The variable that stores the request to the CL to determine RTIL and myIL.

- $sendVIL_i^d$ : The variable that stores the whether vIL is sent or not.

- $at_i^d$ : The variable that shows the acceptance test result.

- $checkPT_i^d$ : The variable that stores the rollback status of that node.

Actions in IL:

- output IL2SM  $(m:M)_i$

- *output UPDVIL(vIL: A<sub>IL</sub>, TxnRT: Q, RxnRT:Q)*<sub>i</sub>

- *input SENDRES(atRes:bool, rbSt: int)*

- *input RBACK(ILHT: H<sub>IL</sub>, cLHT: H<sub>IL</sub>, rbSt: int)*

- *input SM2ILDP (m:M)*<sub>i</sub>

- *input CL2ILRT*(*b*<sub>my</sub>:*bool*, *b*<sub>RT</sub>:*bool*, *m*:*M*)<sub>*i*</sub>

- *input AP2ILNRT(m:M)*<sub>i</sub>

- *input IL2APNRT(q:Q)*<sub>i</sub>

- output IL2CLRT  $(m:M)_i$

- *internal UPDATE()*<sub>i</sub>

- *output REQRT()*<sub>i</sub>

**TIOA**  $IL_i(dSlot: int, t_0: int, t_1: int, t_2: int, t_3: int, M: Type, Q: Type, A_{IL}: Type, H_{IL}: Type)$ states  $now_i^a: R := dSlot$ signature  $TxRT_i^d: M := empty$ output IL2SM(m: M)i  $TxnRT_i^d: Q := empty$  $RxRT_i^d: M := empty$ output UPDVIL(vIL:  $A_{IL}$ , TXnRT: Q,  $RXnRT: Q)_i$ input SENDRES(atRes: bool, rbSt: int) input RBACK( $ilHT: H_{IL}$ ,  $clHT: H_{CL}$ , rbSt: int) RxnRT<sup>d</sup><sub>i</sub>: Q := empty RTIL<sup>d</sup><sub>i</sub>: bool := false input SM2ILDP(m: M) input CL21LRT( $b_{my}$ : bool,  $b_{RT}$ : bool, m: M)<sub>i</sub> input AP21LNRT(m: M)<sub>i</sub> myILid: bool := false regILid: bool := false input IL2APNRT(q: Q) sendVILid: bool := false output IL2CLRT(m: M); internal UPDATE(); at<sup>d</sup>: bool := true checkPT/: int := -1 output REQRT(); vIL1 := InitV transitions input IL2APNRT(RxnRT<sup>d</sup><sub>i</sub>)<sub>i</sub> internal UPDATE() pre: eff:  $now_i^a = dSlot$ set RxnRTi empty eff: input AP2ILNRT(m)i  $vIL_i^d = f_{upd}(vIL_i^d, RTIL_i^d)$ eff:  $now_i^a := 0$  $TxnRT_{i}^{d}.Push(m)$  $regIL_i^d := true$ sendVIL<sup>d</sup> := true output IL2SM(m); pre: output UPDVIL(vIL, TXnRT, RXnRT);  $(now_i^a = t_2) \land myIL_i^d \land$ pre:  $(\neg (TxRT_{i}^{d} empty) \land RTIL_{i}^{d}) \lor (\neg RTIL_{i}^{d} \land$  $sendVIL_i^d = true$ ¬(TxnRT<sup>d</sup>.Top empty))  $now_i^a = t_0$ eff: eff:  $if \, \mathtt{RTIL}^d_{\mathit{i}}$  $sendVIL_i^d := false$ set  $m = T x R T_i^d$ input SENDRES(atRes, rbSt); set TxRT/ empty eff: else set  $m = TxnRT_{i}^{d}$ . Top at<sup>d</sup> := atRes  $checkPT_i^d := rbSt$ TxnRT<sup>d</sup>.Pop  $sct m.rbSt = checkPT_i^d$ input RBACK(ilHT, clHT, rbSt)i set  $m.atRes = at_i^d$ eff:  $myIL_i^d = false$  $vIL_i^d := ilHT.vIL_i^d$  $ViL_i^{-} := 1iHT.VIL_i^{-}$   $TXnRT_i^{d} := iIHT.TXnRT_i^{d}$   $RXnRT_i^{d} := iIHT.RXnRT_i^{d}$   $now_i^{a} := 0$ input SM2ILDP(m) eff: if RTIL  $regIL_i^d := true$  $RxRT_{i}^{d} = m$ sendVIL<sup>d</sup> := true else  $at_i^d := true$ RxnRT<sup>d</sup><sub>i</sub>.Push(m) output REQRT(); output IL2CLRT(m)i pre: pre:  $regIL_i^d = true$  $now_i^a = t_3$  $now_i^a = t_1$ ¬(RxRT<sup>d</sup> empty) eff: eff:  $reqIL_i^d = false$ set  $m = RxRT_i^d$ set RxRT4 empty

$\begin{array}{ll} \textbf{input CL2ILRT}(b_1, b_2, m)_i \\ \textbf{eff:} \\ \texttt{RTIL}_i^d = b_1 \\ \texttt{myIL}_i^d = f_{my}(\texttt{vIL}_i^d, \texttt{RTIL}_i^d, b_2, i) \\ \texttt{TxRT}_i^d = m \\ \hline \\ \hline \\ \textbf{stop when} \\ \texttt{now}_i^a = dSlot \\ (\texttt{sendVIL}_i^d = \texttt{true}) \land (\texttt{now}_i^a = t_0) \\ (\texttt{now}_i^a = t_1) \land (\texttt{reqIL}_i^d = \texttt{true}) \\ ((\texttt{now}_i^a = t_2) \land (\texttt{myIL}_i^d = \texttt{true}) \land \\ (\neg(\texttt{TxRT}_i^d \texttt{empty}) \land \texttt{RTIL}_i^d) \lor (\neg\texttt{RTIL}_i^d \land \\ \neg(\texttt{TxnRT}_i^d.\texttt{Top empty}))) \\ \texttt{now}_i^a = t_3 \land \neg(\texttt{RxRT}_i^d \texttt{empty}) \\ \hline \end{array}$

Figure 9: IL Model as TIOA

$myIL_i^d$  and  $vIL_i^d$  variables are updated by internal operations  $f_{my}$  and  $f_{upd}$ . After the data transmission is finished, UPDATE () is called for the update of variables of the next slot. vIL is updated first. When IL does not need the information if the next time slot is RT or nRT, reqIL gets false value ( $reqIL_i^d$ =false) and the owner of the next time slot is determined locally. If IL needs to information if the next time slot is RT or nRT, reqIL gets true value ( $reqIL_i^d$ =true). IL triggers the action REQRT to the CL. REQRT () requests the type of the next time and the owner of the next time slot. After the calculation time of CL, the action CL2ILRT ( $b_1$ ,  $b_2$ , m) indicates the type of the next time slot ( $b_1$ ), the owner of the next time slot ( $b_2$ ) and RT message (m) in CL if it has. *RTIL* and *myIL* variables update their new values according to  $b_1$  and  $b_2$ .

In IL2SM(*m*), IL sends messages to all nodes, when current time now equals to next starting time *next* and *myIL* is true. The value in  $RTIL_i^d$  determines if the transmitted message is RT or nRT message. Also, in SM2ILDP(*m*),  $RTIL_i^d$  is important too, to send message to upper layer RT buffer ( $RxRT_i^d$ ) or nRT buffer ( $RxnRT_i^d$ ). In IL2CLRT (*m*), RT messages are send to the upper layer immediately. In IL2APNRT ( $RxnRT_i^d$ ) and AP2ILNRT (*m*), upper layer can reach  $TxnRT_i^d$  and  $RxnRT_i^d$  buffers in the IL at any time.

If there is no collision on the shared medium, IL sends message to SM in a one slot and after every update in IL, parameters which are related protocol are same. But, *RTIL* variable gets its  $b_1$  parameter from upper layer CL and this  $b_1$  parameter shows the next time slot is RT or NRT. Also,  $\inf_{my} (vIL_i^d, RTIL_i^d, b_2, i)$  function gets its  $b_2$  parameter from CL and  $b_2$ parameter indicates that the next time slot belongs to the device *i* or not.

$$f_{my}(vIL_i^d, false, -, i) = true$$

$$(\forall j \in I - \{i\}) \quad f_{my}(vIL_i^d, false, -, i) = false$$

$$f_{my}(vIL_i^d, true, b_2, i) = b_2$$

In UPDVIL, if *sendVIL* is true, IL sends vIL parameters of that time slot to DP in each time slot. In SENDRES (*atRes*, *rbSt*), IL gets information from the DP about acceptance test

result (*atRes*) and rollback status (*rbSt*). After getting *atRes* and *rbSt*, these variables are sent to other nodes with IL2SM(m).In RBACK, IL gets stored *vIL* parameters, *Rx* and *Tx* message from DP and updates its *vIL* parameters with the received *vIL* parameters.

Also, IL obeys some requirements below:

- Transmission window covers all messages.  $m.length < dSlot rem \ \ \forall \ m \in M$

- The time between REQRT<sub>i</sub> and CL2ILRT<sub>i</sub> is rem-cmp. After each REQRT<sub>i</sub> function, CL2ILRT<sub>i</sub> occurs.

- If REQRT(t)<sub>i</sub> and REQRT(t)<sub>j</sub>i, j ∈ I, i≠ j occur at the same time t, then, it holds for the

next occurrence of CL2ILRT ( $b_1$ ,  $b_2$ , m) and CL2ILRT ( $\hat{b_1}$ ,  $\hat{b_2}$ ,  $\hat{m}$ ) j that and  $\mathbf{b}_2 = b_1 = \hat{b_1}$

true  $\rightarrow \hat{b_2}$  = false [12]

In framework, IL asks to the CL layer whether the next time slot is RT or nRT. There are 3 variables in vIL such asvIL.cnt, vIL.cyc, vIL.slots. These vIL parameters show which node owns the nRT slot at that time slot. Internal functions  $f_{upd}$  and  $f_{my}$  are defined in Figure 10. In  $f_{upd}$  function, vIL.cnt is incremented with modulo vIL.cyc. After sending action REQRT to the CL, CL does action CL2ILRT ( $b_1$ ,  $b_2$ , m). In  $f_{my}$  internal function, if the next time slot is RT, it determines with action CL2ILRT,  $f_{my}$  function returns  $b_2$  variable which returns with action CL2ILRT. If the next time slot is nRT, it determines with  $RTIL_i^d$  and vIL.nRTSet,  $f_{my}$  internal function returns true and the owner of the next time slot is determined by IL.

$$f_{\text{upd}}(\text{vIL}_{i}^{d}, \text{RTIL}_{i}^{d}).\text{cnt} = \{ (\text{vIL}_{i}^{d}.\text{cnt}+1) \mod \text{vIL}_{i}^{d}.\text{cyc} \\ f_{\text{my}}(\text{vIL}_{i}^{d}, \\ \text{RTIL}_{i}^{d}, b_{2}, i) = \begin{cases} b_{2} & \text{if } \text{RTIL}_{i}^{d} = \text{true} \\ \text{true} & \text{if } \neg \text{RTIL}_{i}^{d} \wedge \text{vIL}_{i}^{d}.\text{cnt} \\ & \in \text{vIL}_{i}^{d}.\text{nRTSet} \\ \text{false otherwise.} \end{cases}$$

Figure 10: Internal Functions in IL Layer

#### 3.2.2 Generic Coordination Layer:

Coordination Layer Generic Model is defined using TIOA Model in the article [12] [43]. Figure 11 shows the CL Model using TIOA. There are 8 parameters in the CL Model :  $del_i$ , t0, M, Q, V,  $A_{CL}$ ,  $H_{CL}$ , InitCL.

- *del<sub>i</sub>*: A processing delay value,

- *t0*: Time of event,

- *M*: The type of transmitted messages,

- *Q*: The type of a FIFO queue messages,

- V: A vector of messages with type M,

- $A_{CL}$ : Abstract variable of CL.

•  $H_{CL}$ : Abstract variable of CL.

CL Model as TIOA has variables to define the model and operations:  $send_i^a$ ,  $Tx_i^d$ ,  $Rx_i^d$ ,  $RTCL_i^d$ ,  $myCL_i^d$ ,  $ch_i^d$ ,  $reqCL_i^d$ ,  $vCL_i^d$ .

- *send*<sup>*a*</sup>: Analog variable which evolves with the time derivative of 1 defines the passage of time after a request is sent by IL, it is bounded by del<sub>*i*</sub>.

- $Tx_i^d$ : The buffer that represents the transmission of messages.

- $Rx_i^d$ : The buffer that represents the reception of messages.

- $RTCL_i^d$ : The variable that stores the type of next slot whether RT or nRT.

- $myCL_i^d$ : The variable that stores whether the device owns the next time slot or not.

- $ch_i^d$ : The channel variable.

- $reqCL_i^d$ : The variable that stores the request from IL to determine RTIL and myIL.

- $sendvCL_i^d$ : The variable that stores the whether vCL is sent or not.

- $vCL_i^d$ : The variable that holds the additional information of the protocol operations. Actions in CL:

- *input AP2CL (m:M, ch: int)*<sub>i</sub>

- *input IL2CLRT(m:M)*<sub>i</sub>

- *input REQRT(m:M)*

- *output UPDVCL*(*vCL*: *A<sub>CL</sub>*, *Tx*: *V*, *Rx*:*Q*, *RTCL*<sup>*d*</sup>; *bool*)<sub>*i*</sub>

- output RBACK(ILHT:  $H_{IL}$ , cLHT:  $H_{IL}$ , rbSt: int)<sub>i</sub>

- *output CL2ILRT(RTCL*<sup>*d*</sup>:*bool,myCL*<sup>*d*</sup>:*bool, m:M*)<sub>*i*</sub>

- *input CL2AP*(q:Q)<sub>i</sub>

The transmission of messages for different channels are supported in CL. Channels have 2 parameters namely *b* which shows the device number and *c* which shows the channel number of that device. Current message for one channel is stored in Tx message buffer. Tx and Rx buffers are used to stores messages.  $RTCL_i^d$ , myCl and channel variable *ch* indicate if the next time slot is RT or nRT, the owner of the next time slot and its channel. These variables are updated when *vCL* is updated with internal functions. Send variable shows the passage of the time after a request is sent by IL and it is also bounded by del<sub>i</sub>.

When CL gets message REQRT  $(t)_i$  from IL layer,  $RTCL_i^d$ , myCL and ch variables are updated for the next time slot using  $g_{RT}(vCL_i^d, RTCL_i^d, t)$  and  $g_{my}(vCL_i^d, RTCL_i^d, t, i)$  functions. After getting REQRT  $(t)_i$  message from IL, send analog variable gets 0 and reqCL boolean variable gets true. In the computation, unique sender for RT slot is determined to avoid collision. myCL variable shows the owner of the next time slot. While computing in CL layer,  $RTCL_i^d$ ,  $myCL_i^d$ ,  $vCL_i^d$ ,  $reqCL_i^d$ ,  $ch_i^d$ , t (timing information) and m.par (RT message parameters) are used by CL. If send (the computation time) does not exceed the  $del_i$  and  $reqCL_i^d$  variable is true, CL sends CL2ILRT ( $RTCL_i^d$ ,  $myCL_i^d$ , m) to the IL layer. Also  $del_i$  variable should be less than rem-cmp time. In CL2ILRT ( $RTCL_i^d$ ,  $myCL_i^d$ , m), if  $myCL_i^d$  variable is true,  $Tx_i^d$  buffer gives message m to the IL layer.

In action UPDVCL, if *sendVCL* is true, CL sends *vCL* parameters of that time slot to DP each time slot. In action RBACK, IL gets *vCL* parameters, Rx and Tx message from DP and update its *vCL* parameters with the received *vCL* parameters.

```

TIOA CL_i(del_i: int, t_0: int, M: Type, Q: Type, V: Type, A_{CL}: Type, H_{CL}: Type, InitCL: A_{CL})

states

send_i^a: real := del_i

signatures

Tx_i^d: V := empty

input AP2CL(m: M,ch: int)i

Rx_i^{\tilde{d}}: Q := empty

input IL2CLRT(m: M)i

RTCL_i^d: bool := false

input REQRT()<sub>i</sub>

myCL_i^d: bool := false

output UPDVCL(vCL: ACL, Tx: V, Rx: Q, RTCL<sup>d</sup>: bool)i

ch_i^d: int := 0

input RBACK(ilHT : HIL, clHT : HCL, rbSt: int)

regCL_i^d: bool: = false

output CL2ILRT(RTCL<sup>d</sup>: bool, myCL<sup>d</sup>: bool, m: M)i

sendvCL_i^d: bool: = false

input CL2AP(q: Q)_i

vCL_i^d: A_{CL}: = InitCL

transitions

input AP2CL(m,ch)i

input RBACK(ilHT,clHT,rbSt);

eff:

eff:

vCL_i^d := clHT_i^d.vCL

Tx_i^d[ch].data := m.dat

Tx_i^d := clHT_i^d Tx

Tx_i^d[ch].par := m.p

Rx_i^{\dot{d}} := clHT_i^{\dot{d}}.Rx

input IL2CLRT(m)i

eff:

output CL2ILRT(RTCL<sup>d</sup>, myCL<sup>d</sup>, m)<sub>i</sub>

Rx_i^d.Push(m)

pre:

vCL_i^d := g_{upd}(vCL_i^d, m.par)

\operatorname{reqCL}_{i}^{d} \wedge (\operatorname{send}_{i}^{a} = del_{i})

input REQRT()<sub>i</sub>

eff:

eff:

if myCL;

\text{RTCL}_i^d = g_{RT}(\text{vCL}_i^d, \text{RTCL}_i^d)

m := Tx_i^d[ch_i^d]

(myCL_i^d, ch_i^d) := g_{my}(vCL_i^d, i)

m.vCL := vCL

set Tx_i^d[ch_i^d] empty

send_i^a := 0

reqCL_i^d := true

else

set m empty

sendVCL_i^d := true

reqCL_i^d := false

output UPDVCL(vCL, Tx, Rx, RTCL);

input CL2AP(Rx<sup>d</sup>);

pre:

sendVCL_i^d = true

eff:

send_i^a = t_0

set Rxid empty

eff:

sendVCL_i^d := false

trajectories

stop when

evolve

d(\text{send}_i^a) := 1

(\text{sendVCL}_{i}^{d} = \text{true}) \land (\text{send}_{i}^{a} = t_{0}))

\operatorname{reqCL}_{i}^{d} \wedge (\operatorname{send}_{i}^{a} = del_{i})

```

Figure 11: CL Model as TIOA

CL shares the action AP2CL  $(dat, p, ch)_i$  with the upper layer. and the action IL2CLRT  $(m, t)_i$  with the lower layer. After AP2CL  $(dat, p, ch)_i$ , data *dat* and the protocol parameters *p* are stored in  $Tx_i^d[ch].data$  and  $Tx_i^d[ch].par$  on the CL layer. After IL2CLRT (m, t), the message *m* from IL is stored in  $Rx_i^d$  buffer and  $vCL_i^d$  variable is updated with the action of  $g_{upd} (vCL_i^d, m.par, t)$ . Upper Layer control application shares the action CL2AP  $(Rx_i^d)_i$  with CL. After CL2AP  $(Rx_i^d)$ , message in  $Rx_i^d$  buffer is sent to the control application. The decision variables  $vCL_i^d$ , the slot type  $RTCL_i^d$ , variable which indicates the owner of the next slot time  $myCL_i^d$  and related channel variable  $ch_i^d$  are updated with  $g_{upd} (vCL_i^d, m.par, t)$ ,  $g_{RT} (vCL_i^d, RTCL_i^d, t)$  and  $g_{my} (vCL_i^d, RTCL_i^d, t, i)$  functions.

$$g_{my}(vCL_i^d, false, t, i) = (false, 0),$$

$$g_{my}(vCL_i^{d}, true, t, i) = (true, ch),$$

$$\Rightarrow g_{my}(vCL_i^{d}, true, t, j) = (false, 0) \text{ for all } j \in I - \{i\}$$

In CL, variables are stored in the form of communication requests. Priority queue is a queue which stores the communication requests in the form of (b,c,eT,dT). *b* indicates a device, *c* shows the channel of that device, *eT* holds the eligibility time of the message and *dT* is the deadline time of the message which is started when the request is issued. In other words, the message in the priority queue is sent by device *b* with channel *c* at the eligible time *eT* and it should be sent before the deadline time *dT*. m.par.req parameter is a set of request from control application. After getting messages from control application, messages are pushed into *vCL.PQ* and they are ordered according to their eligibility time *eT* and deadline time *dT*. The request which is the most urgent eligibility time *eT* is sent to the lower layer.

$$g_{\text{RT}}(\text{vCL}_i, \text{RT}_i, t) = \begin{cases} \text{true} & \text{if vCL}_i.\text{PQ}.\text{Top.}eT \leq t \\ \text{false} & \text{otherwise} \end{cases}$$

$$g_{\text{my}}(\text{vCL}_i, \text{RT}_i, t, i) = \begin{cases} (\text{true}, a) & \text{if PQ}_i.\text{Top.}b = i \land \text{RT}_i \\ & = \text{true} \land \text{PQ}_i.\text{Top.}c = a \\ (\text{false}, 0) & \text{otherwise} \end{cases}$$

Figure 12: Update Functions for CL

Figure 12 shows the update functions for CL. In  $g_{upd}(vCL_i^d, m.par, t)$  function, if RTCL equals true, in other words, the next time slot is RT slot, the first request in the priority queue is popped and the request is sent to the lower layer. However, if RTCL is false (the next time slot is nRT slot), the first request reenters the priority queue. If the eligibility time of the request at the top of the priority queue ( $vCL_i^d$ . PQ. Top.eT) is smaller than current time t,  $g_{RT}(vCL_i^d, RTCL_i^d, t)$  function returns true. Thus, the type of next slot time is determined whether it is RT or nRT. If the request at the top of the priority queue's channel is that device's channel  $g_{my}(vCL_i^d, RTCL_i^d, t, i)$  function returns true and that device's channel a.

#### 3.2.3 Generic Shared Medium Model:

Shared Medium Layer Generic Model is defined using TIOA Model in the article [12] [43]. Figure 13 shows the SM Model using TIOA. There are 6 variables in the SM Model :  $mess^d$ ,  $coll^d$ ,  $next^d$ ,  $now^a$ , M, N.

- *mess<sup>d</sup>*: The parameter that indicates currently transmitted message

- *coll*<sup>d</sup>: Theparameter that indicates whether the collision is happened or not.

- *next<sup>d</sup>*: The parameter that indicates the next reception time

- *now<sup>a</sup>*: Analog parameter which evolves with the time derivative of 1, the updated time information is provided by this variable.

• *M*: The type of transmitted messages.

• *N*: The parameter that indicates the number of messages. Actions in SM:

- *input IL2SM(m:M)<sub>i</sub>*

- output SM2ILDP(m:M)

```

TIOA SM(N:int, M:type)

states

mess<sup>d</sup> : M := empty

coll<sup>d</sup> : Bool := false

signature

next^d: int := 0

input IL2SM(m: M)_i

now^{a}: Real := 0

output SM2ILDP(m:M)

transitions

input IL2SM(m)_i

output SM2ILDP(m)

eff:

pre:

if ((coll<sup>d</sup> = false)

∧(mess<sup>d</sup> is empty))

(now^{a} = next^{d}) \land (mess^{d} not empty

mess^d := m

eff:

next^d := m.length

set messd empty

else

next^d := 0

\operatorname{coll}^d := \operatorname{true}

\operatorname{next}^{\operatorname{d}} := 0

set mess<sup>d</sup> empty

now^{a} := 0

trajectories

stop when

(now^a = next^d) \land (mess^d not empty)

evolve

d(now^a) = 1

```

There are 2 actions shared with the IL layer namely IL2SM(m) and SM2IL(m). In IL2SM(m), if *mess* variable is empty in SM layer, message *m* is sent to the SM layer and next variable is updated. If *mess* variable is not empty in SM layer, collision is occurred and *coll* variable equals true. In this case *next* variable is set to 0 and mess variable is set to empty. If next equals to now in SM layer, SM does action SM2IL to the IL layer. In SM2IL transition, *m* variable is set to *mess* variable. Thus the message *m* can be sent by SM. After that, *mess* variable is set to be empty.

#### 3.2.4 Generic Dependability Plane Model:

Dependability Plane (DP) Generic Model is defined using TIOA Model [43]. Figure 14 shows the DP Model using TIOA. There are 7 parameters in the DL Model : *cyc*,  $t_0, t_1, A_{IL}$ ,  $A_{CL}$ ,  $A_{DP}$ , *InitDP*.

• *cyc:* The variable shows the number of the cycle.

- $t_0, t_1$ : Time of events.

- $A_{IL}$ : Abstract variable of IL.

- $A_{CL}$ : Abstract variable of CL.

- $A_{DP}$ : Abstract variable of DP.

- InitDP: Abstract variable of DP

```

TIOA DP. (cyc: int, to: int, t1: int, AIL: Type, ACL: Type, ADP: Type, InitDL: ADP. Q: Type)

signatures

states

now_i^a : R := 0

input UPDVIL(vIL: AIL, TXnRT: Q, RXnRT: Q)(

atResid: bool := true

input UPDVCL(vCL: ACL, Tx: V, Rx: Q, RTCLi : bool)1

rbReq_i^d: bool := false

rtSlot_i^d: bool := false

stNo_i^d: int := -1

input SM21LDP (m: M)

internal ATEST(),

output RBACK(ILHT : HIL, cIHT : HCL, rbSt : int)i

nodeID_i^d: int := -1

output SENDRES(atRes: bool, rbSt: int);

rbSt_i^d: int := -1

cnt_i^d: int := 0

trajectories

stop when

ILHist<sup>d</sup><sub>i</sub>[cyc]: H<sub>IL</sub>

vCLHist<sup>d</sup><sub>i</sub>[cyc]: A<sub>CL</sub>

(stNo_i^d = 1) \land (now_i^a = t_0)

vDP_i^d: A_{DP} := InitDL

rVCL_i^d: A_{CL}

(\text{stNo}_i^d = 2) \land (\text{now}_i^a = t_1)

(\text{stNo}_i^d = 3) \land (\text{now}_i^a = t_0)

transitions

input UPDVIL(vIL, TXnRT, RXnRT),

internal ATEST(),

eff:

pre:

stNo_i^d = 1

ILHist<sup>d</sup>[cnt].vIL := vIL

now_i^n = t_0

ILHist<sup>d</sup>[cnt].TXnRT := TXnRT

eff:

ILHist<sup>d</sup><sub>i</sub>[cnt].RXnRT := RXnRT

cnt_i^d + = 1

input UPDVCL(vCL, Tx, Rx, RTCL),

if rbReq<sup>d</sup> == false

eff.

atRes_{i}^{d} = fAT(CLHist[cnt - 1].vCL,vDP,

rtSlot_{i}^{d} = RTCL

rVCL, nodeID, rtSlot)

CLHist<sup>d</sup>[cnt].vCL := vCL

if at Res_i^d == true

CLHist_i^d[cnt].Tx := Tx

rbSt_i^d = cnt_i^d - I

CLHist [cnt].Rx := Rx

else

input SM21LDP (m)

rbReq_i^d = true

rbSt_{i}^{d} = cnt_{i}^{d} - 2

eff:

ifrbSt_{i}^{d} = = -1

nodeID_i^d = m.nodeID

rVCL_i^d = m.vCL

rbSt_i^d = cyc - 1

if \operatorname{cnt}_i^d == cyc

rbSt_i^d = m.rbSt

cnt_i^d = 0

now_i^a := 0

if m.atRes == false

stNo_i^d = 2

stNo_i^d = 3

output RBACK(ilHTi, clHTi, rbSti),

else

pre:

stNo_i^d = 1

stNo_i^d = 3

output SENDRES(atRes(, rbSt))

now_i^a = t_0

pre:

eff:

stNo_i^d = 2

cnt_i^d = rbSt_i^d

now_i^a = t_1

if \operatorname{cnt}_i^d == cyc

eff:

\operatorname{cnt}_i^d = 0

stNo_i^d = -1

ilHT<sub>1</sub><sup>d</sup> = ILHist<sub>1</sub><sup>d</sup>[rbSt]

clHT_d = CLHist_d[rbSt]

```

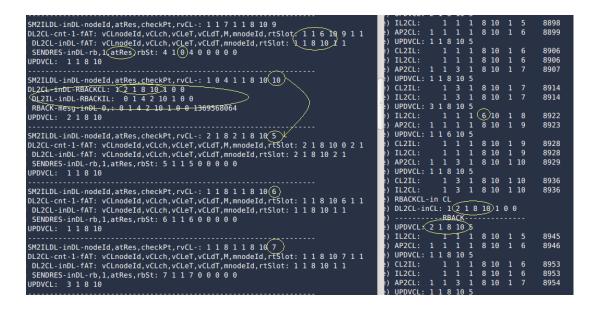

#### Figure 14: Functions in Dependability Plane

$stNo_i^d = -1$ rbReq\_i^d = false DP Model as TIOA has variables to define the model and operations:  $atRes_i^a$ ,  $rbReq_i^d$ ,  $rtSlot_i^d$ ,  $stNo_i^d$ ,  $nodeID_i^d$ ,  $rbSt_i^d$ ,  $cnt_i^d$ ,  $vILHist_i^d[cyc]$ ,  $vCLHist_i^d[cyc]$ ,  $vDP_i^d$ ,  $rVCL_i^d$ .

- $atRes_i^a$ : Boolean variable keeping the acceptance test results

- $rbReq_i^d$ : Boolean variable keeping the rollback requirement.

- $rtSlot_i^d$ : Boolean variable keeping the type of the time slot.

- $stNo_i^d$ : Integer variable used for state transition

- *nodeID*<sup>*d*</sup>. Integer variable keeping the message transmitting node ID

- $rbSt_i^d$ : Integer variable keeping the rollback state number

- $cnt_i^d$ : Integer counter variable for periodic operation

- $vILHist_i^{d}[cyc]$ : Data structure keeping the vIL history

- $vCLHist_i^{d}[cyc]$ : Data structure keeping the vCL history

- $vDP_i^d$ : Data structure to keep the information required for dependability checks. Now it just holds the non real-time slot ownership information as an integer array

- *rVCL*<sup>*d*</sup>. Data structure keeping the transmitting node's vCL variable for dependability checks.

Also, some new parameters are added to the header of the messages.

- $nodeID_i^d$ : transmitting node's ID.

- $vCL_i^d$ : transmitting node's vCL.

- $atRes_i^a$ : transmitting node's acceptance test result.

- $rbSt_i^d$ : the rollback state in case of a failure.

Actions in DP:

- *input UPDVIL(vIL: A<sub>IL</sub>, TxnRT: Q, RXnRT: Q)*<sub>i</sub>

- *input UPDVCL*(*vCL*:  $A_{CL}$ , *Tx*: *V*, *Rx*:*Q*, *RTCL*<sup>*d*</sup>: *bool*)<sub>*i*</sub>

- *input SM2ILDP(m:M)*

- *internal*  $ATEST()_i$

- *output RBACK(ILHT: H<sub>IL</sub>, cLHT: H<sub>IL</sub>, rbSt: int)*<sub>i</sub>

- *output SENDRES(atRes:bool, rbSt:int )*<sub>i</sub>

Dependability Plane has interfaces with IL and CL. There are input actions shared with IL and CL namely UPDVIL (*vIL*) and UPDVCL (*vCL*, *RTCL*). In UPDVIL (*vIL*), vIL history *vILHist*<sub>i</sub> <sup>d</sup>[*cyc*] is updated with vIL decision variable taken from IL. In UPDVCL (*vCL*, *RTCL*), the type of the time slot, *rtSlot*<sub>i</sub><sup>d</sup> is updated with *RTCL* which is taken from CL layer that shows the next time slot is whether RT or nRT. Also, vCL history *vCLHist*<sub>i</sub> <sup>d</sup>[*cyc*] is updated with vCL decision variable taken from CL. Also, an action SM2ILDP (*m*) is occurred in DP. In SM2ILDP (*m*), transmitting node's ID (*m.nodeID*) is assigned to *nodeID*<sub>i</sub><sup>d</sup>, transmitting node's vCL is assigned to *rVCL*<sub>i</sub><sup>d</sup> which keeps the transmitting node's vCL variable for dependability checks. The rollback state number *rbSt*<sub>i</sub><sup>d</sup> of message m is assigned to *rbSt*<sub>i</sub><sup>d</sup> in DP. If transmitting node's acceptance test result *atRes*<sub>i</sub><sup>a</sup> equals to false, the state transition number *stNo*<sub>i</sub><sup>d</sup> equals 1.

There are 2 output actions from dependability plane: SENDRES  $(atRes_i^a, rbSt_i^d)$  and RBACK  $(vIL_i^d, vCL_i^d)$ . Before SENDRES occurs, the state transition number  $stNo_i^d$  should be 2, and after SENDRES  $stNo_i^d$  is -1. Before RBACK occurs  $stNo_i^d$  should be, and after that, counter variable for periodic operation equals to rollback state number plus 1  $(cnt_i^d = rtSlot_i^d + 1)$ . If counter for periodic operation  $cnt_i^d$  equals to number of the cycle,  $cnt_i^d$  gets 0.

*vILHist*<sup>*d*</sup><sub>*i*</sub>[*cyc*] and *vCLHist*<sup>*d*</sup><sub>*i*</sub>[*cyc*] variables are assigned to *vIL*<sup>*d*</sup><sub>*i*</sub> and *vCL*<sup>*d*</sup><sub>*i*</sub> variables in IL and CL. The state transition number *stNo*<sup>*d*</sup><sub>*i*</sub> equals -1 and the rollback requirement *rbReq*<sup>*d*</sup><sub>*i*</sub> gets false.