# COMPARISON OF CRYSTAL SI SOLAR CELLS FABRICATED ON P-TYPE AND N- TYPE FLOAT ZONE SILICON WAFERS

# A THESIS SUBMITTED TO THE GRADUATE SCHOOL OF NATURAL AND APPLIED SCIENCES OF MIDDLE EAST TECHNICAL UNIVERSITY

BY

MAKBULE BİLGEN

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS

FOR

THE DEGREE OF MASTER OF SCIENCE

IN

PHYSICS

SEPTEMBER 2013

# Approval of the Thesis:

# COMPARISON OF CRYSTAL SILICON SOLAR CELLS FABRICATED ON P-TYPE AND N-TYPE FLOAT ZONE SILICON WAFERS

submitted by **Makbule Bilgen** in partial fulfillment of the requirements for the degree of **Master of Science in Physics Department, Middle East Technical University** by,

| Prof. Dr. Canan Özgen<br>Dean, Graduate School of <b>Natural and Applied Sciences</b> |       | _          |

|---------------------------------------------------------------------------------------|-------|------------|

| Prof. Dr. Mehmet Zeyrek<br>Head of Department, <b>Physics</b>                         |       |            |

| Prof. Dr. Raşit Turan<br>Supervisor, <b>Physics Dept., METU</b>                       |       |            |

| <b>Examining Committee Members:</b>                                                   |       |            |

| Prof. Dr. Mehmet Parlak<br>Physics Dept., METU                                        |       |            |

| Prof. Dr. Raşit Turan<br>Physics Dept., METU                                          |       |            |

| Prof. Dr. Nizami Hasanlı<br>Physics Dept., METU                                       |       |            |

| Assist. Prof. Dr. Alpan Bek<br>Physics Dept., METU                                    |       |            |

| Assist. Prof. Dr. Kadir Ertürk<br>Physics Dept., NKU                                  |       |            |

|                                                                                       | Date: | 02.09.2013 |

| in accordance with academic rules as | in this document has been obtained and presented<br>and ethical conduct. I also declare that, as required<br>fully cited and referenced all material and results |

|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                      | Name, Last Name: Makbule Bilgen                                                                                                                                  |

|                                      | Signature :                                                                                                                                                      |

|                                      |                                                                                                                                                                  |

|                                      |                                                                                                                                                                  |

|                                      |                                                                                                                                                                  |

|                                      |                                                                                                                                                                  |

|                                      |                                                                                                                                                                  |

|                                      |                                                                                                                                                                  |

|                                      |                                                                                                                                                                  |

#### **ABSTRACT**

# COMPARISON OF CRYSTAL SI SOLAR CELLS FABRICATED ON P-TYPE AND N-TYPE FLOAT ZONE SILICON WAFERS

Bilgen, Makbule

Master of Science, Department of Physics

Supervisor : Prof. Dr. Raşit TURAN

September 2013, 91 pages

Solar cells are traditionally fabricated on p-type Si substrates due to the high electron diffusion length in p-type substrate. However, high quality float zone silicon wafers provide higher carrier life time for holes in the n-type substrates, making it possible to fabricate high efficiency solar cells in this type of substrate. Superior properties of n-type substrates have created a tendency towards fabrication of n-type solar cells in photovoltaic market technology considerably. It is even forecasted that photovoltaic (PV) industry will completely shift from p-type systems to n-type systems in the near future.

This technology shift leads to new research activities related to production steps since it should be optimized to get better performance of solar cells.

In this work, we have focused on the development of solar cells based on n-type substrate. Several different routes have been followed and compared with each other. Comparison was made between solar cells fabricated on n- and p-type substrates having a good quality. The conditions yielding high solar cell efficiency was studied in this direction. Both the fabrication and characterization of solar cells were carried out at METU-GÜNAM facilities

**Keywords:** n-type solar cell, p-type solar cell, float zone silicon wafer, photovoltaic technology

#### ÖZ

### P VE N-TİPİ FLOAT ZON Sİ DİLİMLER ÜZERİNDE ÜRETİLMİŞ GÜNEŞ GÖZELERİNİN KARŞILAŞTIRILMASI

Bilgen, Makbule

Yüksek Lisans, Fizik Bölümü

Tez Yöneticisi : Prof. Dr. Raşit TURAN

Eylül 2013, 91 sayfa

Yüksek elektron difüzyon uzunluğu nedeni ile güneş gözeleri geleneksel olarak p-tipi alttaş üzerinde üretilir. Ancak, yüksek kaliteli float zon silisyum dilimler n-tipi alttaşlarda da yüksek verimli güneş gözelerinin üretilmesini sağlar. N-tipi alttaşların daha iyi özelliklere sahip olması nedeni ile fotovoltaik market, teknoloji araştırmalarını n-tipi alttaşlar kullanarak güneş gözesi üretmek üzerine yönlendirmiştir. Bu araştırmalar sonucunda fotovoltaik teknolojinin p-tipi alttaşlar verine tamamen n-tipi alttaşlara döneceği bile öngörülmektedir.

Güneş gözelerinden daha yüksek verim elde edebilmek için bu teknoloji değişimi yeni üretim teknikleri ve araştırma alanları ortaya çıkarmıştır.

Bu çalışmada n-tipi alttaş kullanılarak farklı yollardan üretilen güneş gözelerinin kıyaslaması yapıldı ve üretim stepleri optimize edilmeye çalışıldı. Daha sonra ise n-tipi ve p-tipi güneş gözeleri float zon dilimler üzerinde üretilerek karşılaştırıldı. Bu yöntemle daha yüksek verimli güneş gözelerinin elde edilmesini sağlayan şartlar araştırıldı. Güneş gözelerinin üretim ve karakterizasyonu ODTÜ-GÜNAM tesislerinde gerçekleştirildi.

**Anahtar kelimeler**: n-tipi güneş gözesi, p –tipi güneş gözesi, float zon silisyum dilim fotovoltaik teknoloji

To my mom and dad

#### **ACKNOWLEDGMENTS**

I would like to express my deepest thanks to my supervisor Prof. Dr. Raşit Turan for his advice, guidance, help and patience. I would also like to thank him for giving me an opportunity to work in his research group.

I would like to thank Fırat Es for all his guidance, valuable advice and help throughout my thesis studies, and for his friendship and support since the first day that I joined the group. Specially thanks to Emine Hande Çiftpınar for her endless support and great friendship. Discussions with her, morning gossip accompanied by coffee in the early hours of the day have been indispensable for me. I would also like to thank Demircioğlu Couple for all their endless support and sincere friendship. I would like to thank Serim Kayacan İlday for her friendly support, Mete Günöven for his help and support, Gülsen Baytemir, Bilge Can Yıldız, Burcu Barutçu and Engin Özkol and for their friendship. I would like to thank all LAB 118 friends and GÜNAM technicians. I would also like to thank İbrahim Güllü and Doğan Mansuroğlu for their beautiful friendship and support. Other special thanks goes to Zehra Aras, thank you for being such an invaluable friend.

I would like to express my endless thanks and gratitude to Selçuk Bilmiş for his endless academic and technical support, patience and great friendship. Without him, that master period would be more difficult.

I would also like to thank Prof. Dr. Bayram Tekin, who has been a milestone for my education life, for his encouragement, advice and patience.

Finally, I would like to express my deepest gratitude to my family. Nothing would be easy without their love, support and patience. I am also thankful to my husband for his encouragement and endless patience during this period.

# TABLE OF CONTENTS

| ABSTRACT                                                                            | v   |

|-------------------------------------------------------------------------------------|-----|

| ÖZ                                                                                  |     |

| ACKNOWLEDGMENTS                                                                     |     |

| TABLE OF CONTENTS                                                                   |     |

| LIST OF TABLES                                                                      | xi  |

| LIST OF FIGURES                                                                     | xii |

| LIST OF ABBREVIATIONS                                                               | XV  |

| CHAPTERS                                                                            |     |

| 1. INTRODUCTION                                                                     | 1   |

| 1.1. Historical Perspective of Photovoltaic Technology                              | 2   |

| 1.2. Photovoltaic Market                                                            | 3   |

| 1.3. Summary of the thesis                                                          | 6   |

| 2. AN OVERVIEW OF MATERIALS AND DEVICES WITH IMPORTANCE FOR SOLAR CELL APPLICATIONS |     |

| 2.1. Float Zone and Czochralski Crystal Silicon Wafer Growth                        | 7   |

| 2.2. Type of semiconductors                                                         |     |

| 2.2.1. Intrinsic Semiconductors                                                     | 11  |

| 2.2.2. Extrinsic Semiconductors                                                     | 13  |

| 2.3. P-n junction                                                                   | 15  |

| 2.4. Fundamental concepts of photovoltaic technology                                | 17  |

| 2.4.1. Solar Irradiation                                                            | 17  |

| 2.4.2. Photovoltaic cell parameters                                                 | 18  |

| 3. PRODUCTION STEPS OF N-TYPE AND P-TYPE Si SOLAR CELLS                             | 21  |

| 3.1. Saw Damage Etching:                                                            | 22  |

| 3.1.1. Aim of Saw Damage Etching                                                    | 22  |

| 3.1.2. Experiment                                                                   | 22  |

| 3.1.2.1. Reflection Measurement                                                     | 22  |

| 3.1.3. Results of Etching Experiments                                               | 23  |

| 3.2. Surface Texturing for Lower Reflection                                         | 25  |

| 3.2.1. Theory of texturing                                                          | 25  |

| 3.2.2. Experimental Procedures                                                                | 28   |

|-----------------------------------------------------------------------------------------------|------|

| 3.2.3. Results of Texturing Experiments                                                       | 29   |

| 3.3. Diffusion.                                                                               | 35   |

| 3.3.1. Theory                                                                                 | 35   |

| 3.3.1.1. Atomistic Approach                                                                   | 35   |

| 3.3.1.2. Fick's Laws of Diffusion                                                             | 36   |

| 3.3.2. Experimental details of diffusion process for n-type and p-type solar cells production | 39   |

| 3.3.3. Production Approaches for n-type Solar Cells: Results of Experiments                   | 40   |

| 3.4. Antireflective Coating                                                                   | 49   |

| 3.4.1. Theory                                                                                 | 49   |

| 3.4.2. Experiment                                                                             | 52   |

| 3.4.3. Experimental Results for Si <sub>3</sub> N <sub>4</sub> Ar Coating                     | 52   |

| 3.5. Metallization                                                                            | 55   |

| 3.5.1. Theory of Metal Semiconductor Contacts                                                 | 55   |

| 3.5.1.1. Contact Resistance Measurement Using Transmission Line Method (TLI                   | M)59 |

| 3.5.2. Screen Printing as a Method of Metallization                                           | 60   |

| 3.5.3. Edge Isolation                                                                         | 62   |

| 3.5.4. Metallization Results                                                                  | 62   |

| 4. PERFORMANCE OF N-TYPE SOLAR CELLS PRODUCED WITH DIFFERENT APPROACHES                       | 67   |

| 4.1. I-V Characteristics of Solar Cells                                                       | 67   |

| 4.1.1. Experimental Setup                                                                     | 67   |

| 4.1.2. Experimental Results                                                                   | 68   |

| 4.2. Quantum Efficiency Measurement                                                           | 73   |

| 4.2.1. Quantum Efficiency Setup                                                               | 74   |

| 4.2.2. Quantum Efficiency Results                                                             |      |

| 5. CONCLUSION                                                                                 |      |

| REFERENCES                                                                                    |      |

| ADDENDIY                                                                                      | 87   |

# LIST OF TABLES

### **TABLES**

| Table 3. 1: Variables of texturing process                                 | 47 |

|----------------------------------------------------------------------------|----|

| Table 3. 2: Results of I-V measurement under illumination of samples       |    |

| Table 3. 3: Results of contact resistance at different transition velocity |    |

| Table 4. 1: Result of I-V measurement by solar simulator                   |    |

| Table 4. 2: Results of SunsVoc Measurement                                 |    |

# LIST OF FIGURES

### **FIGURES**

| Figure 1. 1: Evolution of Global PV cumulative installed Capacity 2000-2012 (MW) [1] 1            |

|---------------------------------------------------------------------------------------------------|

| Figure 1. 2: NREL's cell efficiency graph[5]2                                                     |

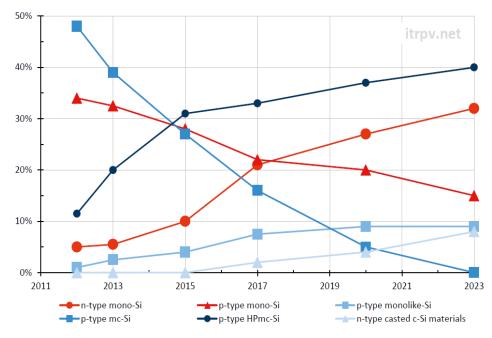

| Figure 1. 3: Commercial market shares of photovoltaic technologies[6]3                            |

| Figure 1. 4 : Calculated and recorded solar cell efficiency [5]                                   |

| Figure 1. 5: Industrial multi-crystalline solar cell and single crystalline solar cell5           |

| Figure 1. 6: Estimation of market share for p-type and n-type based solar cells [7]5              |

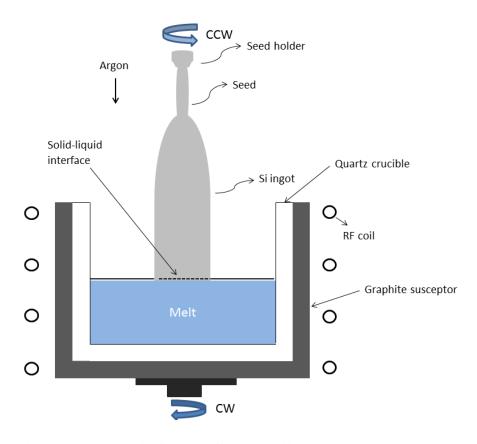

| Figure 2. 1: Schematic diagram of Czochralski crystal growth [11]9                                |

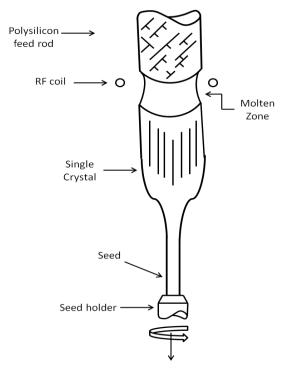

| Figure 2. 2 : Schematic diagram of Float-zone crystal growth [11]10                               |

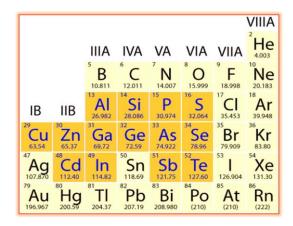

| Figure 2. 3: Place of some semiconductors on periodic table                                       |

| Figure 2. 4: Energy band diagram of electrical conduction (a), electron bonding diagram of        |

| electrical conduction (b) in intrinsic silicon after excitation                                   |

| Figure 2. 5: Energy band diagram of n-type semiconductors (a), electron bond structure of n-      |

| type semiconductors (b)                                                                           |

| Figure 2. 6: Energy band diagram of p-type semiconductors (a), electron bond structure of p-      |

| type semiconductors (b)                                                                           |

| Figure 2. 7: Simple schematic of p-n junction                                                     |

| Figure 2. 8 : Band diagram of isolated p-type and n-type semiconductor                            |

| Figure 2. 9: Band diagram of a p-n junction when the two semiconductors are in contact $\dots 16$ |

| Figure 2. 10: Solar irradiation at AMG 1.5 condition                                              |

| Figure 2. 11: I-V curve of solar cell                                                             |

| Figure 3. 1: Flow chart of production steps for n-type and p-type solar cells21                   |

| Figure 3. 2: Schematic of reflectance measurement setup                                           |

| Figure 3. 3: SEM images of bare wafer (a), 0.5min. in KOH (b), 1 min. in KOH (c) ,2 min. in       |

| KOH (d), 4 min in KOH (e), 6 min. in KOH (f)                                                      |

| Figure 3. 4: Reflection measurement results of different samples                                  |

| Figure 3. 5: Process of anisotropic etching for (10 0) oriented silicon wafer                     |

| Figure 3. 6: Reflection of incident light beam from smooth surface (a), from textured surface     |

|                                                                                                   |

| Figure 3. 7: Reflection and transmition of incident light in semiconductor                        |

| Figure 3. 8: Intensity of reflected light beam                                                    |

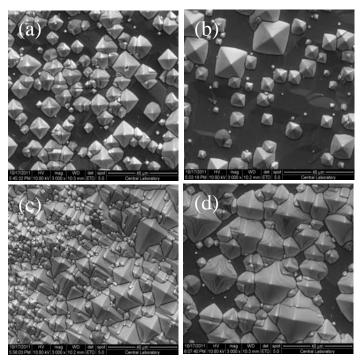

| Figure 3. 9: SEM images of samples textured in 2 wt % KOH and 10 wt % IPA solution at             |

| 75°C for 35 min. (a), 40 min. (b), 45 min. (c) ,50 min. (d)                                       |

| Figure 3. 10: SEM images of samples textured in 2 wt % KOH and 15 wt % IPA solution at            |

| 75°C for 35 min. (a), 40 min. (b), 45 min. (c) ,50 min. (d)                                       |

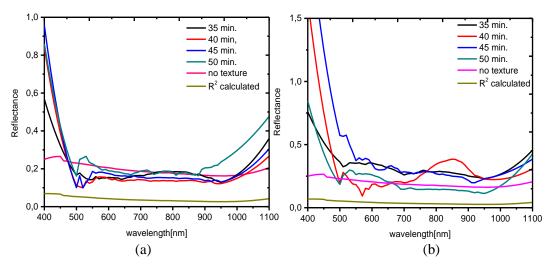

| Figure 3. 11: Reflection measurement results of samples textured in 2 wt % KOH and 10 wt          |

| % IPA solution (a) and in 2 wt % KOH and 15 wt % IPA solution (b) at 75°C for different           |

| time periods31                                                                                    |

| Figure 3. 12: SEM images of samples textured in 3 wt % KOH and 10 wt % IPA solution             | at         |

|-------------------------------------------------------------------------------------------------|------------|

| 75°C for 35 min. (a), 40 min. (b), 45 min. (c), 50 min. (d)                                     | . 31       |

| Figure 3. 13: SEM images of samples textured in 3 wt % KOH and 15 wt % IPA solution             | at         |

| 75°C for 45 min. (a), 50 min. (b)                                                               | . 32       |

| Figure 3. 14: Reflection measurement results of samples textured in 3 wt % KOH and 10 v         | wt         |

| % IPA solution (a) and in 3 wt % KOH and 15 wt % IPA solution (b) at 75°C for different         | ıt         |

| time periods                                                                                    | . 32       |

| Figure 3. 15: SEM images of samples textured in 3 wt % KOH and 10 wt % IPA solution             | at         |

| 80°C for 35 min. (a), 40 min. (b), 45 min. (c), 50 min. (d)                                     | . 33       |

| Figure 3. 16: SEM images of samples textured in 4 wt % KOH and 10 wt % IPA solution             | at         |

| 75°C for 35 min. (a), 40 min. (b), 45 min. (c) ,50 min. (d)                                     | . 34       |

| Figure 3. 17: Reflection measurement results of samples textured in 3 wt % KOH and 10 v         | wt         |

| % IPA solution at 80°C for different time periods (a) and in 4 wt % KOH and 10 wt % IPA         | A          |

| solution (b) at 75°C for different time periods                                                 | . 34       |

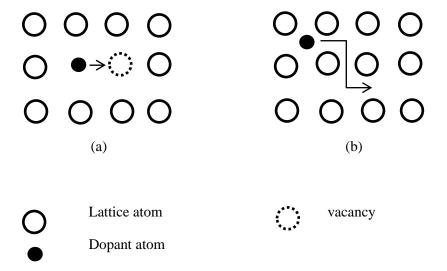

| Figure 3. 18: Atomic diffusion mechanism. (a) vacancy diffusion mechanism. (b) interstiti       | ial        |

| mechanism                                                                                       | . 36       |

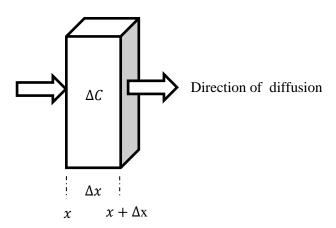

| Figure 3. 19: Diffusion along the thin plate                                                    | . 36       |

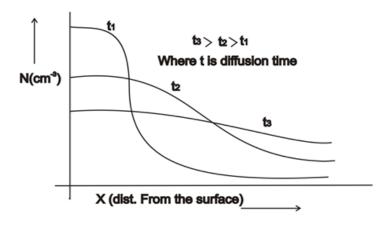

| Figure 3. 20: Concentration distribution of drive in diffusion [19]                             | . 39       |

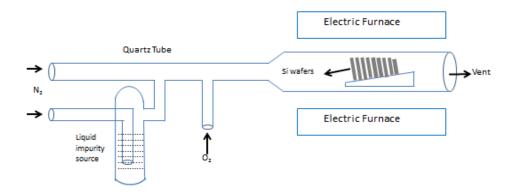

| Figure 3. 21: The schematic diagram of quartz tube furnace system for doping process            |            |

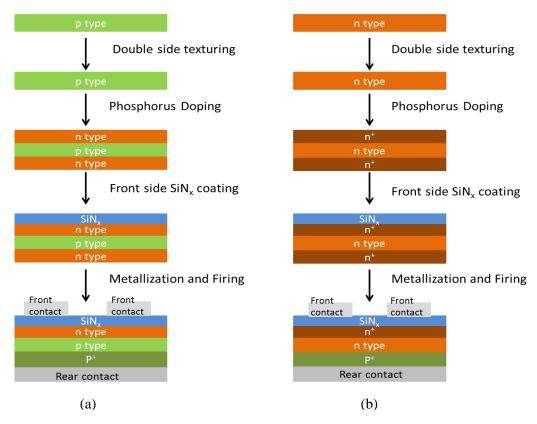

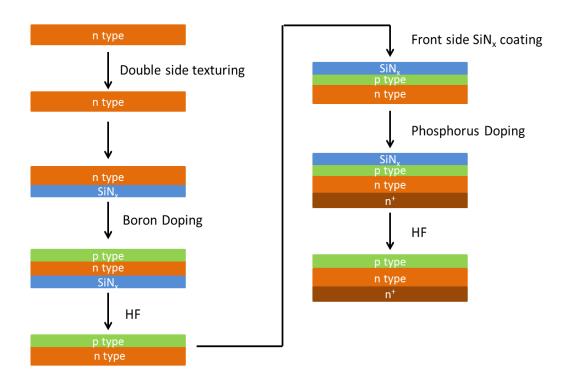

| Figure 3. 22: Process Flow of 1 <sup>st</sup> approach for p-type wafers (a), n-type wafers (b) | . 42       |

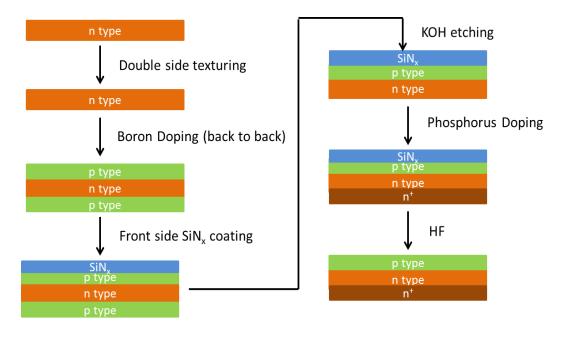

| Figure 3. 23: Process Flow of 2 <sup>nd</sup> Approach                                          | . 42       |

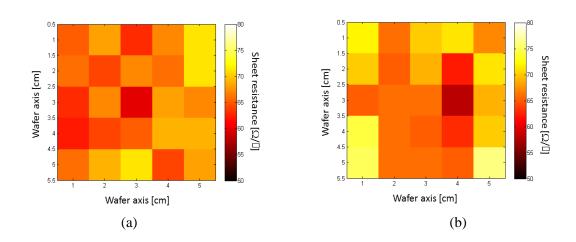

| Figure 3. 24: Sheet resistance values mapping of front side of n-type wafers (a), rear sides    | of         |

| n-type wafer (b)                                                                                | . 43       |

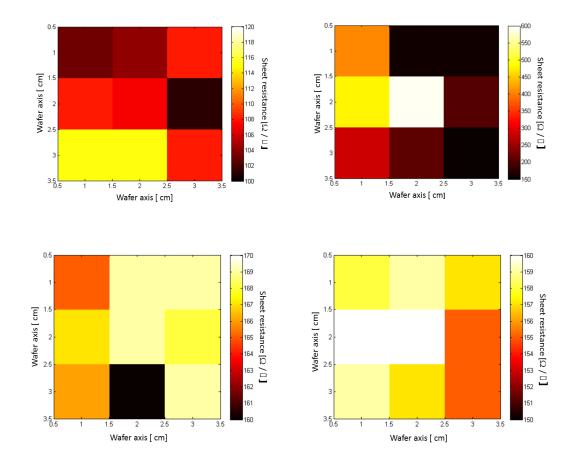

| Figure 3. 25: Sheet resistance values mapping of back sides of n-doped wafers after KOH         |            |

| solution in (a) 30 sec., (b) 60 sec., (c) 120 sec., (d) 240 sec.                                | . 44       |

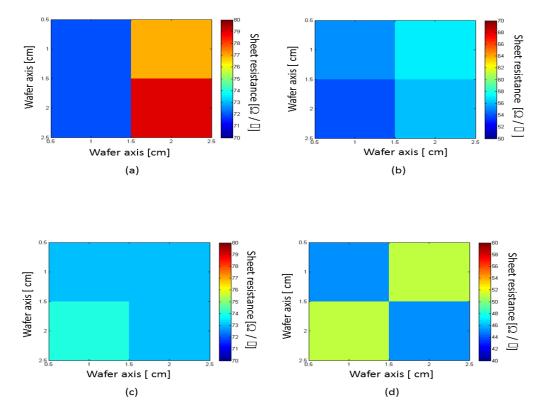

| Figure 3. 26: Sheet resistance mapping of front side (a) and rear side (b) of sample for 30     |            |

| seconds. Sheet resistance mapping of front side (a) and rear side (d) of sample for 60 seconds. | nds        |

|                                                                                                 | . 45       |

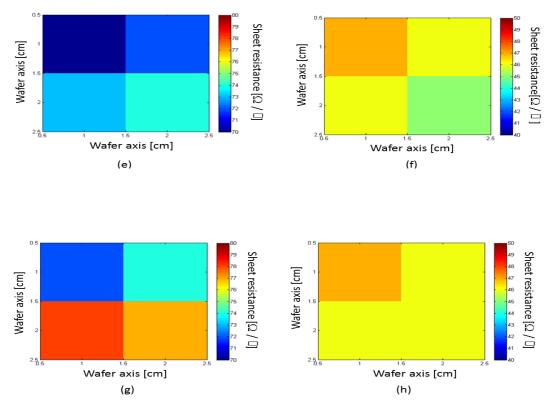

| Figure 3. 27: Sheet resistance mapping of front side (e) and rear side (f) of sample for 120    | ļ          |

| seconds. Sheet resistance mapping of front side (g) and rear side (h) of sample for 240         |            |

| seconds                                                                                         | . 46       |

| Figure 3. 28: Results of dark I-V measurement (a) before and after annealing (b)                |            |

| Figure 3. 29: Process Flow of 3 <sup>rd</sup> Approach                                          |            |

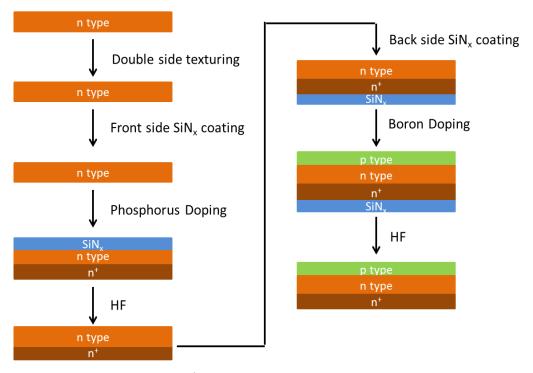

| Figure 3. 30: Process Flow of 4 <sup>th</sup> Approach                                          |            |

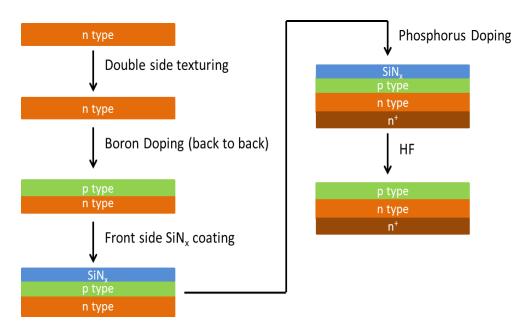

| Figure 3. 31: Process Flow of 5 <sup>th</sup> Approach                                          |            |

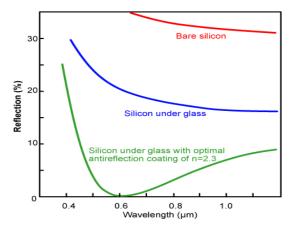

| Figure 3. 32: The reflectance graphs of bare silicon and coated by anti-reflective thin film    |            |

| [24]                                                                                            | . 51       |

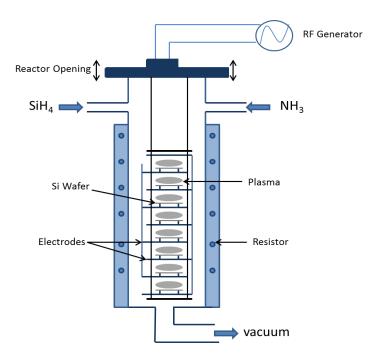

| Figure 3. 33: Schematic diagram of PECVD system.                                                |            |

| Figure 3. 34: Images of diffusion furnace and PECVD system used in GÜNAM                        | . 54       |

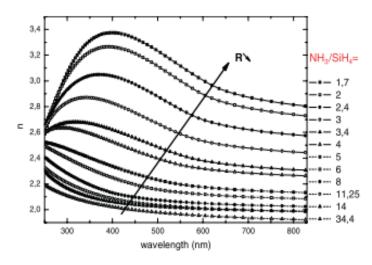

| Figure 3. 35: Dependence of refractive index of SiNx on the gas flow ratio for a given          |            |

| wavelength [25]                                                                                 |            |

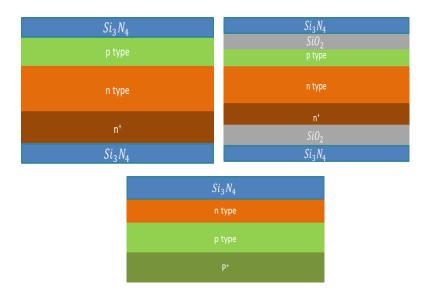

| Figure 3. 36: Cross sectional view of both n-type and p-type wafers after the anti -reflective  | <i>v</i> e |

| coating process                                                                                 |            |

| Figure 3. 37: Reflectance measurement results of p-type and n-type doped wafer                  |            |

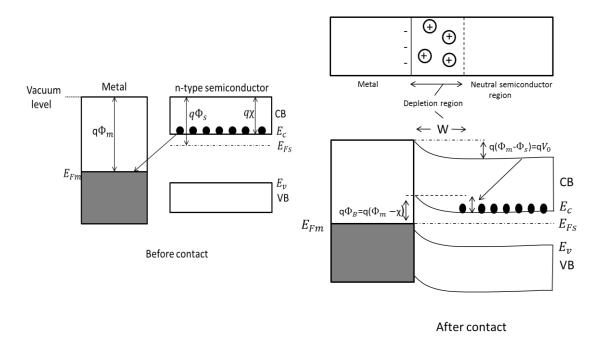

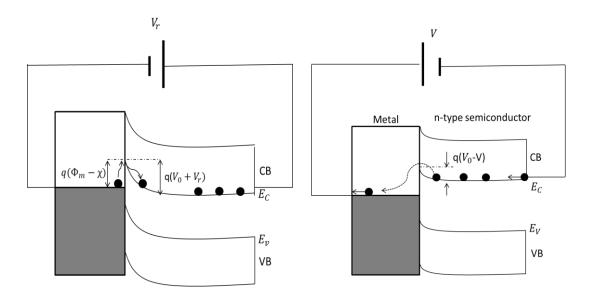

| Figure 3. 38: Schottky junction formation                                                       |            |

| Figure 3. 39: Reverse and forward biased Schottky junction                                      |            |

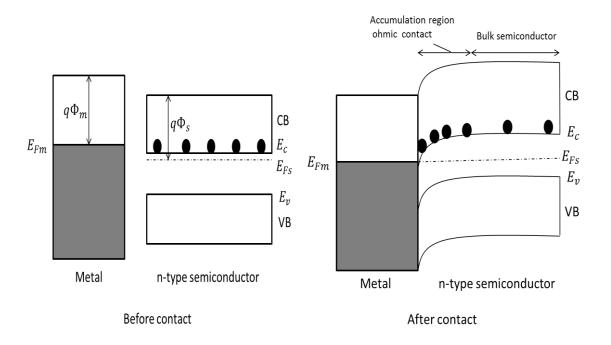

| Figure 3. 40: Ohmic contact formation                                                           | . 58       |

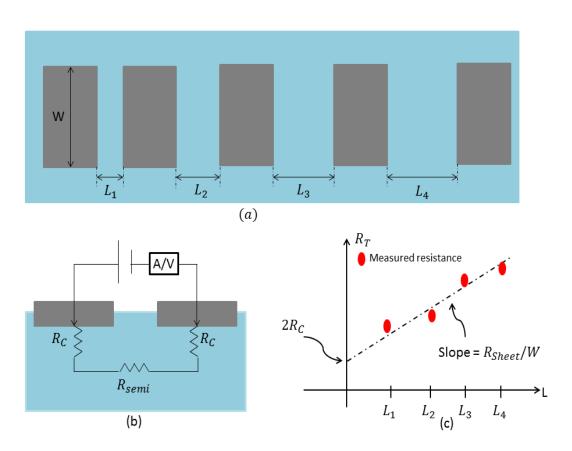

| Figure 3. 41: Top view of the TLM mask (a), cross section area of total resistance (b), curve                                     |

|-----------------------------------------------------------------------------------------------------------------------------------|

| of TLM (c)58                                                                                                                      |

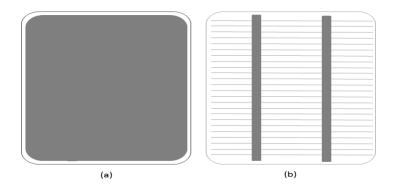

| Figure 3. 42: Aluminum mask for back side of wafer (a), silver mask for both sides of the                                         |

| wafer (b)60                                                                                                                       |

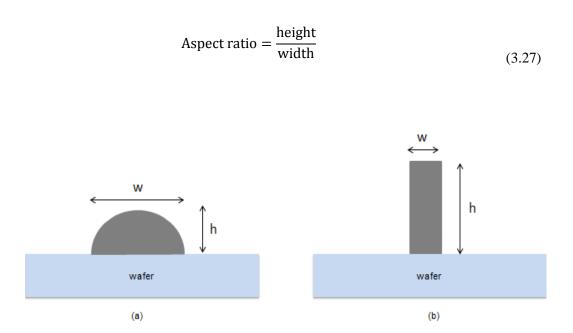

| Figure 3. 43: Cross section area of screen printed line in real case (a), in ideal case (b)61                                     |

| Figure 3. 44: Images of screen printer and firing furnace                                                                         |

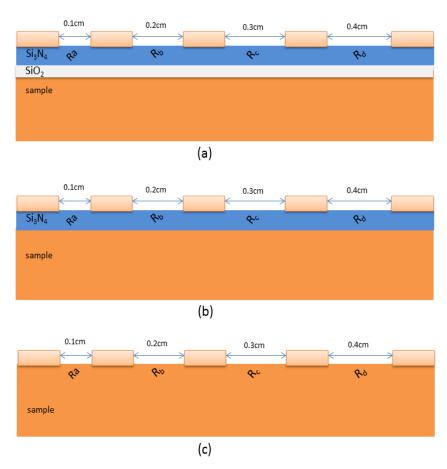

| Figure 3. 45: Design of samples for TLM measurement type 1 (a), type 2 (b), type 3 (c)63                                          |

| Figure 3. 46: Images of sample after metallization (a), and edge isolation (b)64                                                  |

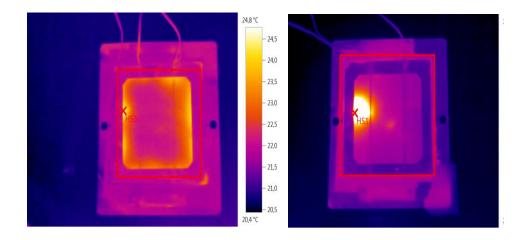

| Figure 3. 47: Thermal camera images of sample before edge isolation (a), after edge                                               |

| isolation (b)65                                                                                                                   |

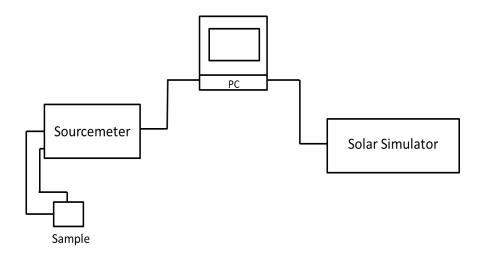

| Figure 4. 1: Schematic of I-V characterization setup                                                                              |

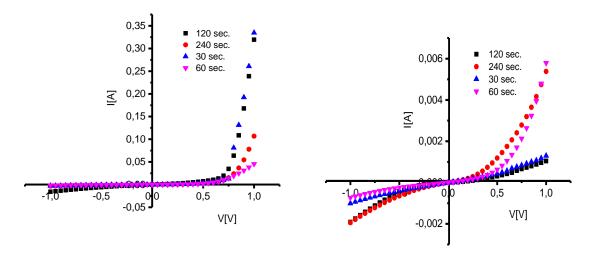

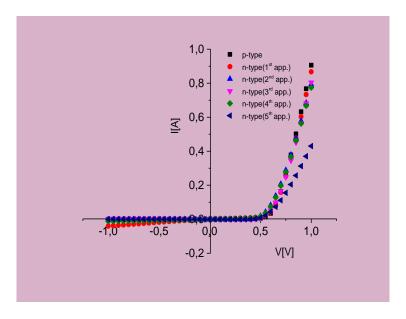

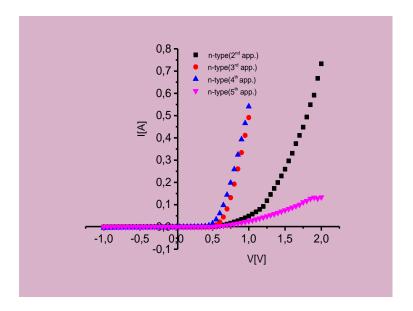

| Figure 4. 2: Results of dark I-V measurement of samples passivated with only Si <sub>3</sub> N <sub>4</sub> 68                    |

| Figure 4. 3: Results of dark I-V measurement of samples double sides passivated with stack                                        |

| layer69                                                                                                                           |

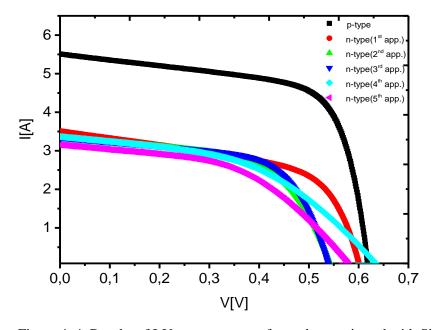

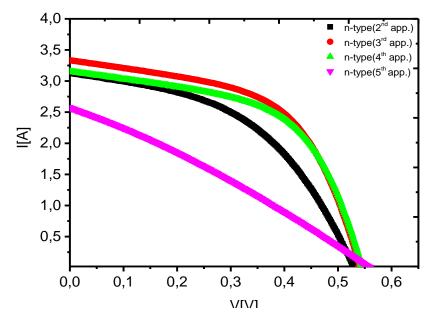

| Figure 4. 4: Results of I-V measurement of samples passivated with Si <sub>3</sub> N <sub>4</sub> 69                              |

| Figure 4. 5: Results of I-V measurement of samples double sides passivated with SiO <sub>2</sub> - Si <sub>3</sub> N <sub>4</sub> |

| 70                                                                                                                                |

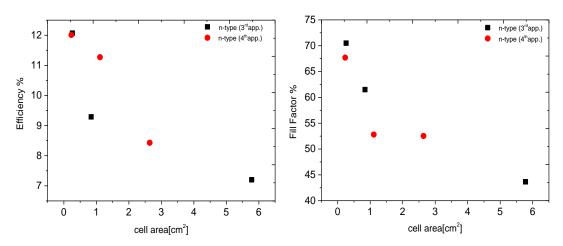

| Figure 4. 6: Effect of cell area on efficiency and fill factor                                                                    |

| Figure 4. 7: Schematic of reflectance measurement setup                                                                           |

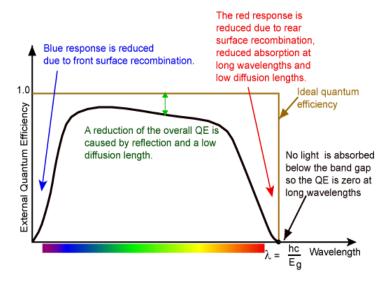

| Figure 4. 8: Quantum efficiency of ideal and real silicon solar cell [31]73                                                       |

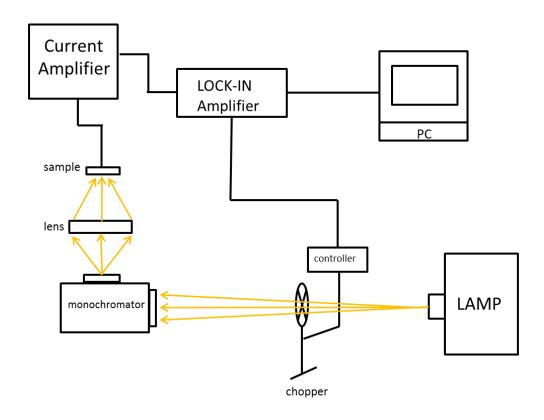

| Figure 4. 9: Schematic of quantum efficiency measurement setup74                                                                  |

| Figure 4. 10: Schematic of quantum efficiency measurement setup                                                                   |

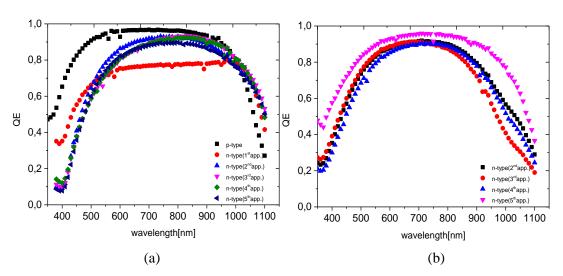

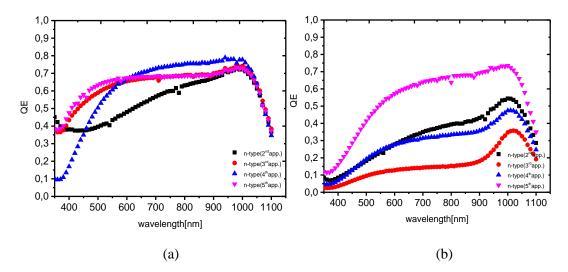

| Figure 4. 11: Results of quantum efficiency measurement of double sides passivated samples                                        |

| (a) with $Si_3N_4$ , (b) with $Si_3N_4$ - $SiO_2$                                                                                 |

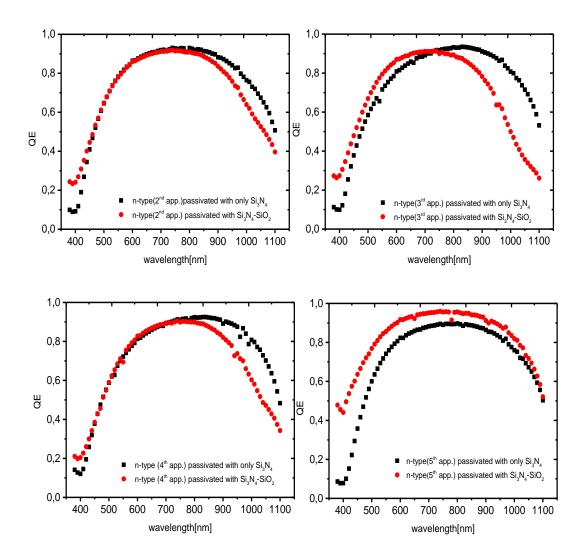

| Figure 4. 12: Comparison the quantum efficiency results between n-type samples produced                                           |

| by 2 <sup>nd</sup> , 3 <sup>rd</sup> , 4 <sup>th</sup> and 5 <sup>th</sup> approach but different passivated                      |

| Figure 4. 13: Results of quantum efficiency measurement of double sides passivated samples                                        |

| (a) with $Si_3N_4$ , (b) with $Si_3N_4$ -SiO <sub>2</sub>                                                                         |

# LIST OF ABBREVIATIONS

AM1.5G Air Mass 1.5 Global

Fz Float Zone

Cz Czochralski

E<sub>C</sub> Conduction Band Energy

E<sub>V</sub> Valance Band Energy

eV Electron Volt

KOH Potassium Hydroxide

IPA Iso Propyl Alcohol

DI water Deionized water

Si Silicon

e- Electron

h+ Hole

E field Electric field

SC Semiconductor

PECVD Plasma Enhanced Chemical Vapor

Deposition

AR Anti Reflective

BSF Back Surface Field

SEM Scanning Electron Microscope

#### **CHAPTER 1**

#### INTRODUCTION

It is a well-known fact that energy is one of the most important issues all over the world. The main source of energy is fossil fuels such as coal, oil or natural gas. However, the most important problem is that these resources are limited and they do not have sustainability in the presence of increasing energy consumption. Increasing demand also give rise to economic problems since unit price of electrical energy is also increasing. Moreover, the conventional fossil energy is detrimental to our natural life because it leads to global warming considerably due to the rate of carbon dioxide emission.

No one can deny that this problem can be tackled through renewable energy source such like solar energy, wind energy, geothermal energy, etc. However, solar energy attracts more attention among the other alternative energy resources since it is clean, abundant and accessible everywhere easily. For this reason, solar energy, in particular photovoltaic (PV) technology is considered to be a promising alternative to conventional sources. Solar energy conversion systems are proven to be a reliable means of generating electricity and heat for domestic and industrial usage.

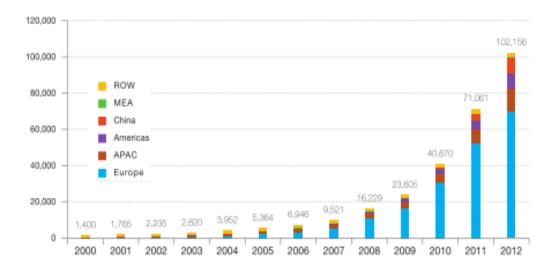

Figure 1. 1 Evolution of Global PV cumulative installed Capacity 2000-2012 (MW) [1]

Nowadays, with the lower cost and higher efficiency, PV technologies are becoming more competitive and gaining more attention especially in developed countries.

To illustrate the enhancement in the PV activities, Figure 1.1 shows the amount of installed PV systems globally. We see that the total PV power exceeded 100 GW at the end of 2012, which represents a significant amount in the power generation.

## 1.1. Historical Perspective of Photovoltaic Technology

Photovoltaic technology dates back to 19<sup>th</sup> century. In 1839, Edmund Becquerel realized the photovoltaic effect when he performed an experiment related to electrolytic cell [2, 3]. He firstly showed that materials can respond to the light by generating electric current. Then, photovoltaic effect in solid selenium was observed by William Adams and Richard Day in 1876 [2, 3]. Charles Fritts designed first photovoltaic device which was made by using two different metals and by placing selenium between the metals [4]. Then, Grohndal observed the photovoltaic effect in copper-cuprous oxide films [2, 3]. At beginning of the 1900s, Walter Schottky and Neville Mott put forward a theory related to metal-semiconductor barrier [2]. In the following years, many experiments and research were carried out.

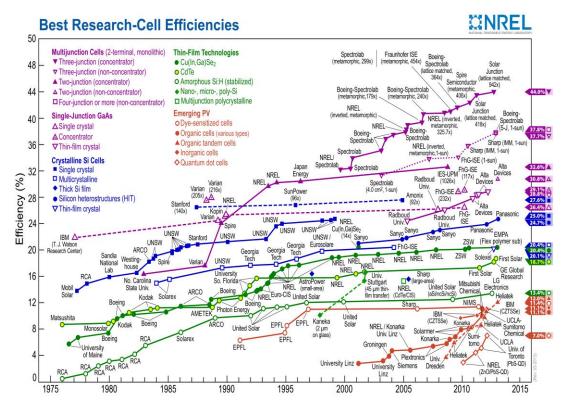

Figure 1. 2: NREL's cell efficiency graph[5]

During 1950s, formation of p-n junction was performed in silicon when the properties of silicon were discovered. Then, in 1954, the first silicon solar cell was produced by L. Pearson, C.S. Fuller and D.M. Chapin in BELL Labs.

Efficiency of that solar cell was nearly 6% [2]. In 1954, p-n junction which formed other elements was manufactured, but silicon dominated all the market technology and this case is still continuous. The number of research conducted in solar energy has been increased especially after the oil-crisis in 1973. For this reason, huge budget has been allocated by government of countries for research.

To reduce the cost and improve the efficiency, alternative materials and methods have been tried through research projects around the world. Thin film materials like amorphous silicon, organic solar cells and III-V semiconductors have been studied to obtain lower cost and/or higher efficiency in solar cells. Figure 1.2 shows the distribution of efficiencies obtained with different material and device systems.

#### 1.2. Photovoltaic Market

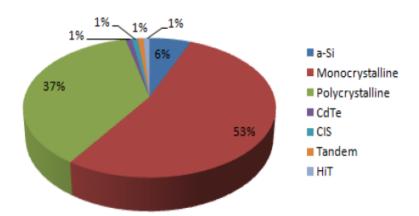

Although different photovoltaic technologies based on new material systems have been developed through the years, the oldest technology, that is, crystalline silicon technology has still prevailed in the commercial market due to its superior properties described in section 2.1. Commercial market share of different PV technologies is given Figure 1.3

Figure 1. 3: Commercial market shares of photovoltaic technologies[6]

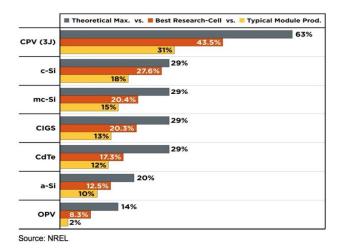

We see the share of c-Si technology is almost 90 % in today's PV market [7]. On the other hand, the level of maturity and development are of interest for the future development. Figure 1.4 compares the efficiency values achieved by the technology today and the maximum achievable values. We see that Si technology has been so developed that it has approached the theoretical limits, while for other technologies, there is a significant

difference between theoretical values and the experimental results [5]. Most of the research activities are focusing on the reduction of carrier loss after the generation.

Solar cell technologies are commonly classified as three main categories. They are called as first, second and third generation solar cells.

Figure 1. 4: Calculated and recorded solar cell efficiency [5]

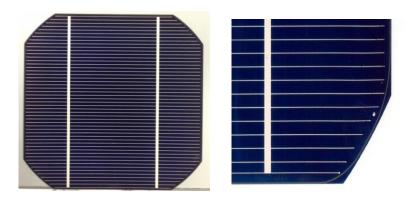

The solar cells based on crystalline Si are called first generation solar cells. It is often made of mono crystalline or multi-crystalline silicon wafer cut from the ingots grown by Czochralski and cast growth techniques, respectively. A picture of these cells is shown in Figure 1.5. When we compare mono crystalline silicon and multi-crystalline silicon solar cells we see that the former provides high efficiency because the latter has grain boundaries which cause conductivity degradation. This affects the performance of multi-crystalline silicon solar cell negatively. In mono crystal solar cells, the conduction takes place without any obstacle that leads to higher conversion efficiency. Mono crystalline silicon solar cell technology has reached 25% cell efficiency at lab level. At the same time, the improvement in the wafer growth technology, cost of crystalline silicon solar cells is being lowered, and consequently, crystalline solar cells are securing their dominant position in the commercial market.

In order to move towards more efficient systems, new ideas and approaches are being developed in recent years. One of the most important approaches is to switch from p-type based technology to n-type based solar cell systems. It is well known that n-type Si has better electronic properties due to the higher carrier life time. However, technological difficulties in the solar cell fabrication on n-type wafers have prevented them from being the major technology. As a result, in spite of its rather poor electronic properties, the whole PV industry has been organized according to the requirements of the p-type based solar cell fabrication.

Figure 1. 5: Industrial multi-crystalline solar cell and single crystalline solar cell

In recent years, some new ideas have been implemented to make n-type based cell production more feasible. This has created huge amount of attraction and resulted in increased R&D and production activities. It is even predicted that, the technology will evolve to a mature and superior level so that the PV industry will completely shift from p-type systems to n-type systems in the near future. Figure 1. 6 shows a projection of the market share for these two technologies, made by mono-Si. From this projection, we see that the market will be dominated by n-type material by mono-Si.

Figure 1. 6: Estimation of market share for p-type and n-type based solar cells [7]

This technology shift requires extensive research activities. New production steps should be designed and optimized to achieve the best conditions. In this work, we have focused on the development of solar cells based on n-type substrate.

Our work represents first attempts carried out at GÜNAM facilities. Several different routes have been followed and compared with each other. We have been able to demonstrate the feasibility of n-type solar cells.

Other technologies based on so called second generation and third generation have not been outside the scope of this study. Just to give short information. Solar cells in the form of thin films are called second generation solar cells.

They have usually lower efficiency compared to the first generation solar cells, but relatively cheaper technology [8]. Thin film systems have lost their market position due to the cost reductions in the c-Si cell technology.

A variety of new material and cell designs is called third generation solar cells. They are expected to have higher efficiencies. However, most of these new systems are still in the R&D level, and far from the industrial application. Many of these approaches have little chance for a commercial success.

#### 1.3. Summary of the thesis

The main aim of this study is to understand and optimize the fabrication steps n-type solar cells and compare it with conventional p-type solar cells. This work is expected to form the technology know-how in GÜNAM. This thesis consists of five chapters. First one is an introduction which provides general information on photovoltaic technology.

Chapter 2 presents the basic properties of wafer growth techniques, semiconductors and type of semiconductors as well as the fundamental concepts of photovoltaic technology.

Chapter 3 consists of the main experimental part of the cell production. All production steps are covered in this chapter. In addition, theory, experiment and experimental results of each process steps are also discussed in details.

In chapter 4, solar cells produced by different approaches are characterized by means of I-V measurements, quantum efficiency measurements and SunsVoc measurements. In addition, performance of these solar cells is compared her

In chapter 5, this thesis is concluded with a short summary by taking all results into consideration.

#### **CHAPTER 2**

# AN OVERVIEW OF MATERIALS AND DEVICES WITH IMPORTANCE FOR SOLAR CELL APPLICATIONS

#### 2.1. Float Zone and Czochralski Crystal Silicon Wafer Growth

Although germanium was mostly used as the semiconductor material at the beginning of the solid state devices fabrication in 1950s, after a short period of time, silicon has started to be used instead of germanium due to the superior properties of silicon such as band gap, abundance, thermally grown silicon dioxide. Therefore, silicon has become the major material in solid state devices fabrication. For example, germanium has a low band gap (0.67 eV) which leads to higher leakage current and its oxide is water soluble which is undesirable in solid state device technology and it is less abundant which affects cost of devices. Other semiconductor compounds have similar problems. In contrast to other materials, silicon has a quite suitable band gap (1.12 eV) for room temperature device applications and its oxide that grows thermally is an excellent insulator, which is highly needed for integrated circuit technology [9]. Moreover, silicon is more abundant. When taken all these important properties in to the consideration, silicon crystal is easily seen to be superior for integrated circuit production. Having this impact on the micro electronic circuit industry, the growth of high quality Si single crystal becomes an important issue both scientifically and technologically.

To obtain purified single crystal silicon, two major technologies are widely used: Czochralski growth and float zone growth. The former one is suitable for mass production while the latter one yields higher purity material with slightly higher cost.

SiO<sub>2</sub>, pure form of sand called as quartzite, is used as a raw material in order to obtain silicon crystal. It is placed in a furnace with carbon in the form of coke, coal and wood ships and a number of reactions start in the furnace at high temperature [10]. The overall reaction is given by (2.1) [10].

$$SiC (solid) + SiO_2 (solid) \rightarrow Si (solid) + SiO (gas) + CO (gas)$$

(2.1)

Silicon produced in this process is called as metallurgical grade silicon (MGS). It is not pure enough to be used in solar cells or other electronic devices due to high impurity content.

In order to purify it further, it is pulverized and is reacted with hydrogen chloride (HCl), so that trichlorosilane (SiHCl<sub>3</sub>) in gas form is obtained as follows

$$Si (solid) + 3HCl (gas) \rightarrow SiHCl_3(gas) + H_2 (gas)$$

(2.2)

Pure solid Si is then obtained by fractional distillation using H<sub>2</sub> as given in the following reaction:

$$SiHCl_3(gas) + H_2(gas) \rightarrow Si(solid) + 3HCl(gas)$$

(2.3)

This final product is called electric grade silicon (EGS). The EGS is a polycrystalline material with reduced impurity level. The amount of impurities is nearly in the parts-per-billion range (1ppb =  $5 \times 10^{13} \text{cm}^{-3}$ ) [9, 10].

The Czochralski method is based on crystallization from the melt, that is, it is solidification from the melt at the interface. The EGS is melted in a crucible which is made up of quartzite at high temperature. Then, the oriented seed crystal is placed in a seed holder. Next, oriented seed crystal is immersed into the melt and seed holder is started to rotate (counter clockwise). In the meantime, crucible is also rotated (clockwise). When the part of the seed crystal is dipped into the melt, seed is pulled out of the melt by using seed holder slowly [10]. During this process, solidification occurs at the interface as shown in the Figure 2. 1. In this way, Si ingot is formed that has same orientation with seed crystal. Pull rate is an important parameter in this technique, since it affects defect formation. Another important factor is the ambient control which is obtained by argon gas which prevents oxidation and evaporation from the melt.

Upon ingot production, wafers are cut from the ingot using rotating diamond saw or more usually using wire saw.

In this process, dopant atoms, phosphorous or boron atoms can be added into the melt in order to obtain n-type or p-type single crystal, respectively. Doping concentration is related to amount of dopant atoms added to the solution.

The Czochralski method is an effective way obtaining the single crystal wafers in large scales. However, the disadvantage of this technique is that single crystal wafers include oxygen impurities considerably since the crucible is made up of SiO<sub>2</sub>, which deteriorates the device performance. Oxygen impurities give rise to reducing the minority carrier lifetime [11]. Therefore, it results in reduction of current, voltage and efficiency directly. To get rid of this problem, float zone wafer growth technique has been developed. Using this method, Si wafers that have lower impurities (such as oxygen and carbon) concentration can be obtained.

Float zone technique is considered to be better technique in terms of the material quality. It is, however, more expensive than Czochralski technique. For this reason, Czochralski wafers dominate the commercial market today.

Figure 2. 1: Schematic diagram of Czochralski crystal growth [11]

In the float zone process which illustrated in Figure 2.2, a poly-crystal rod is heated by a RF coil to produce single crystal wafers. The rod is suspended freely without any contact with the crucible, which provides the lower contamination than Cz silicon wafer. The oriented seed is held bottom of the poly-crystal rod and RF heats the rod from bottom to the top. During the heating process, a small zone is molten when the RF passes along the rod. Impurities are disposed to staying in molten region and thus impurities are considerably removed to end of the rod. Since heating is started from the bottom which is placed oriented seed crystal, orientation of molten regions converts into the orientation of seed crystal and molten region becomes solid as a high purity single crystal. Then, by removing end part of the resultant ingot, we obtained purified single crystal ingot. To obtain further purification, melting-solidification cycle is repeated. In the final step the ingot is sliced by saw into the wafers [10, 11].

When the solar cell is produced from Fz single crystal wafer, efficiency of the cell can reach nearly 25% [12]. Fz crystal wafer has an advantage considerably when compared to Cz.

However, the price is high and the diameter of produced wafer is limited to the restriction resulting from the production technique.

Figure 2. 2 : Schematic diagram of Float-zone crystal growth [11]

# 2.2. Type of semiconductors

Two main material categories exist with respect to electrical conductivity: conductors and insulators. However, there is another material class that acts as insulators at T=0 K and with increasing temperature, they become thermally activated and act as conductors. It is a characteristic behavior in terms of electrical conductivity and this type of materials are called as semiconductors. They are important in electronic industry since their electrical properties can be controlled by doping or by thermal and optical means.

Semiconductors are called as intrinsic semiconductors if they are not doped intentionally. They are called as extrinsic semiconductors if they are doped with impurity elements which make them p-type or n-type. This property can be expressed using thermodynamical variable called Fermi Level (in the thermodynamic terminology it is called chemical potential). Fermi level is defined as the highest occupied energy level of electrons at T=0 K. If it is inside the electronic band which must be allowed, this material is defined as metal. If Fermi level is inside the forbidden gap at T=0 K, it is defined as insulator. The band which is above of the Fermi level is called conduction band, the band which is below is called valance band. The region between valance band and conduction band is called as forbidden gap which has a very important impact on industrial applications.

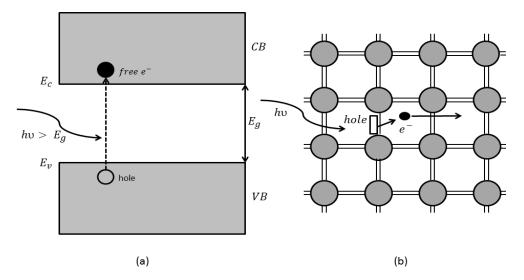

#### 2.2.1. Intrinsic Semiconductors

Intrinsic semiconductors can be interpreted with the help of band theory as mentioned above. At T=0 K, valance band is filled by electrons and conduction band is completely empty. There exists a forbidden gap called as band gap. The most familiar semiconductors are silicon and germanium from the group IVA of periodic table (Figure 2.3). Silicon is the most important semiconductor for microelectronic and solar cell applications.

Figure 2. 3: Place of some semiconductors on periodic table

Using elements of groups IIIA and VA of periodic table, compound semiconductor materials like GaAs can be synthesized More semiconductors can be obtained when using elements of IIB and VIA such as ZnS and CdS.

Since isolated silicon atoms have four valance electrons ([Ne]  $3s^2p^2$ ) when they form a crystal structure, each silicon atom is bonded covalently to others, where 4 valence electrons are shared with other 4 neighbors. This makes Si a stable and robust material. When an electron residing in the valance band is excited thermally or optically, it makes transition into the conduction band. (see Figure 2.4)

In the case of optical excitation, only photons whose energy is greater than the band energy can excite an electron to the conduction band. Any semiconductor based optical detection system including the solar cell must satisfy this condition for photo current generation.

Electrons are relatively free in the conduction band. They move around and, if a potential exists, they can be directed to the outside world to generate current. In the case of thermal generation, electrons receiving enough thermal energy can be excited to the conduction band where they can move freely. The thermal energy is provided by the lattice vibration of the atoms.

Figure 2. 4: Energy band diagram of electrical conduction (a), electron bonding diagram of electrical conduction (b) in intrinsic silicon after excitation

The conductivity of a semiconductor is determined by the free electrons and holes in the conduction and valance band, respectively. The conductivity of intrinsic semiconductor is defined as

$$\sigma = \mathbf{n}|\mathbf{e}| \ \mu_{\mathbf{e}} + \mathbf{p}|\mathbf{e}| \ \mu_{\mathbf{h}} \tag{2.4}$$

Where the p and n are the number of holes and electrons per cubic meter, respectively.  $\mu_e$  and  $\mu_h$  are the mobility of electron and hole, respectively.

However, for intrinsic semiconductors, corresponding to each free electron, holes are created and it is expressed by as

$$n = p = n_i \tag{2.5}$$

Where  $n_i$  is the carrier concentration of the intrinsic semiconductor. Thus, (2.4) becomes,

$$\sigma = n_i |e| (\mu_h + \mu_e) \tag{2.6}$$

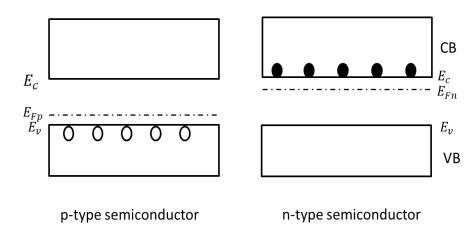

#### 2.2.2. Extrinsic Semiconductors

Semiconductor device technology is based on control conduction by chemical doping which converts an intrinsic material to extrinsic one. In an extrinsic semiconductor, the conduction is controlled by electrons and holes provided by the dopant atoms.

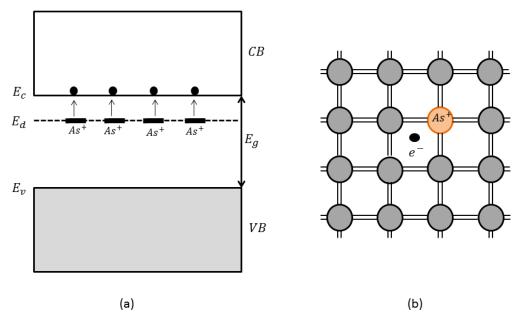

In the case of Si crystal, each atom has four valance electrons and they bond covalently to the neighboring silicon atom. If an element of group V of periodic table, such as arsenic (As), phosphorus (P) and antimony (Sb) is added as impurity atom into the silicon crystal, four valance electrons are bonded with silicon, fifth electron is left without bonding. That electron stays around the region of impurity atoms and it becomes free easily for a while since the binding energy of fifth electron is so small.

This can be expressed by perspective of band theory. Each fifth electron of impurity atoms which is bound to silicon loosely occupies energy state located forbidden band, around the conduction band. When they gain the required the energy to reach conduction band, they become free electron and jump into the conduction band. Room temperature is sufficient to excite these electrons and this makes it possible the transitions into the conduction band. This type of impurity atoms is called as donor since electrons are donated by excitations through these impurity atoms (Figure 2.5).

In the case of group V doping, since the density of free electrons in conduction band is much greater than density of holes in valance band  $(n \gg p)$ , (2.4) becomes,

$$\sigma = n|e| \mu_{e} \tag{2.7}$$

This type of materials is defined n-type semiconductor. In addition, it is clear that the majority charge carriers are electrons and minority charge carriers are holes. As for Fermi level, it is shifted upwards because donor states is close to the conduction band, but its exact position depends on temperature and concentration of impurity atoms.

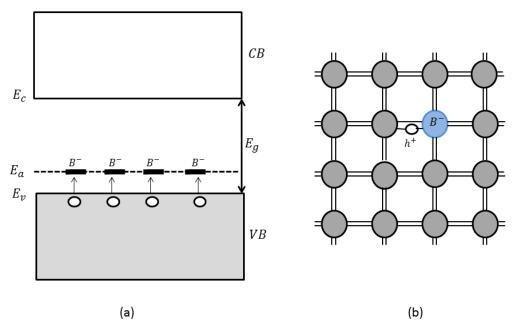

If an element of group IIIA of periodic table like boron (B) is doped into the silicon crystal, the opposite effect occurs compared to n-type semiconductors. Impurity atoms have three valence electrons at this time and they share these electrons with silicon atoms. However, one bond is deficient in terms of electron, that is, it is a hole. Electrons of adjacent atoms can displace the hole since it is bound to dopant atom, but binding energy is so small. The hole moves into the crystal from further away the impurity atom by this way. This motion can be generalized to all impurity atoms. Therefore, motion of holes is observed at most.

It can be also explained by band theory. The energy level of these type materials is between conduction band and valance band, close to valance band. The level is called acceptor state since impurity atoms is called acceptor atoms due to acting as electron acceptor. Electrons in valance band can be excited to the thermal excitation and make a transition into acceptor level rather than conduction band. Thus, missing electrons, i.e., holes, increases in the valance band.

Figure 2. 5: Energy band diagram of n-type semiconductors (a), electron bond structure of n-type semiconductors (b)

When the compare between the number of free electrons and holes, it is clear that majority charge carriers are holes and minority charge carriers are electrons. This type of materials is called p-type semiconductor (Figure 2.6)

Figure 2. 6: Energy band diagram of p-type semiconductors (a), electron bond structure of p-type semiconductors (b)

Fermi level of p-type semiconductor is the forbidden gap, but it is near the acceptor level. Its exact location is determined by temperature and concentration of acceptor atoms. In addition, for p-type material, conductivity is defined by (2.8) due to  $p \gg n$

$$\sigma = p|e|\,\mu_h\tag{2.8}$$

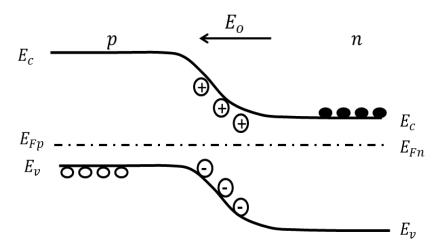

#### 2.3. P-n junction

The operation of almost all semiconductor electronic materials is based on p-n junction. It is also fundamentally important for solar cell operations.

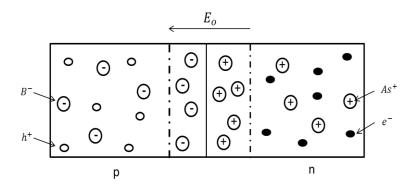

When an n-type material and p-type material are brought together, electron diffuse from n-type region to the p-type region and holes diffuse from p-type region to the n-type region, which results from the concentration gradient.

Although the regions are neutral originally, flow of charge carriers leads to formation of a region, including opposite charged ions. This region is called depletion region. It is apparent that there is internal electric field inside the depletion region from the positive ions to the negative ions, called as built in electric field.

Contrary to diffusion, drift current has always opposite direction, i.e., holes drift into the p region and electrons drift into the n region due to the built in electric field. At equilibrium, diffusion and drift current of charge carriers will be balanced, so that total net current is equal to zero. There is potential difference in p type and n type region at equilibrium. It is called as built in potential.

Figure 2. 7: Simple schematic of p-n junction

When the forward bias (positive potential to p-side compared to n-side) is applied to the junction, it disturbs the equilibrium. The applied voltage is directly dropped across the depletion region because the voltage dropped across the neutral region is negligible. Therefore, it reduces the built in potential since it affects directly built in electric field.

For this reason, diffusion current increases considerably and the number of majority carriers increases in bulk region. Therefore, net current flow increases. When the reverse bias is applied to the junction, potential at the junction increases. Therefore diffusion current is even reduced.

From the perspective of energy band diagram, when the p-n junction forms, (Figure 2.8) Fermi levels of them must be aligned at equilibrium. In addition to this, the energy bands are bent since vacuum level must be continuous (Figure 2.9).

Figure 2. 8: Band diagram of isolated p-type and n-type semiconductor

Figure 2. 9: Band diagram of a p-n junction when the two semiconductors are in contact

#### 2.4. Fundamental concepts of photovoltaic technology

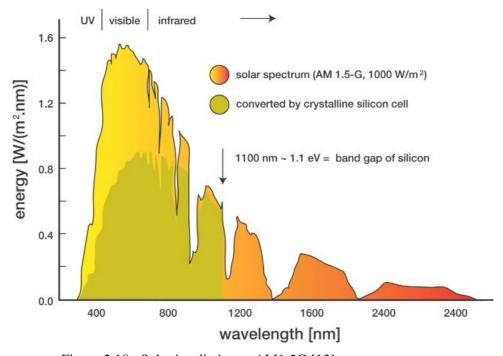

#### 2.4.1. Solar Irradiation

Outside the surface of the earth's atmosphere, the solar irradiation is 1367 W/m<sup>2</sup>. However, the real value differs slightly since distance between Earth and Sun changes because of the elliptical orbit off the Earth around the Sun. When these are taken into consideration, the average value of irradiance outside the Earth's atmosphere is determined as 1353 W/m<sup>2</sup>, which is defined as solar constant. This is not the case when the radiation passes the atmosphere. Sunlight is attenuated considerably, which can result from scattering and absorption by air molecules.

Air mass is a parameter defined as the path length which light travels through the atmosphere and it is given as

$$Air\ mass = \frac{1}{\cos \theta} \tag{2.9}$$

Where  $\theta$  is the angle between vertical axis and position of the sun. When the incoming light comes along the surface normal, the condition is called as AM0 condition, whereas it is called as AM1.5 condition for the light coming with an angle of 48°. AM1.5 condition is also named as AM1.5G where "G" stands for "global". It means that both direct and diffuse radiation is taken into account. When the spectrum of AM1.5G is normalized, incident power gives  $1000 \, \text{W/m}^2$ .

Figure 2.10: Solar irradiation at AM1.5G [13]

#### 2.4.2. Photovoltaic cell parameters

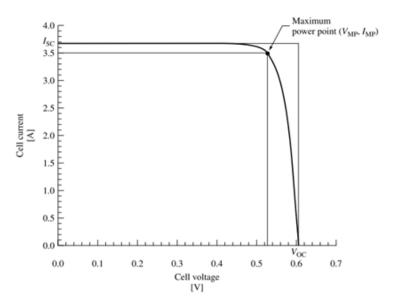

As a p-n junction diode, a solar cell displays the same behavior as a simple p-n junction diode since its mechanism is based on p-n junction. Therefore, the total current of solar cell is expressed by a diode characteristic as given by.

$$I_d = -I_{ph} + I_0 \left( e^{\frac{qV}{kT}} - 1 \right) \tag{2.10}$$

Where  $I_d$  is total current of the solar cell,  $I_0$  is the reverse saturation current,  $I_{ph}$  is the photocurrent which is generated under illumination, k is the Boltzmann constant, Vis the applied voltage and T is the temperature.

Under an illumination, I-V curve shifts in the negative voltage direction. Conventionally, I-V curve of the solar cell is characterized using 4<sup>th</sup> quadrant. I-V curve of a solar cell is given by Figure 2.11. Basic solar cell parameters that can be extracted from the I-V curve are as follows:

Figure 2. 11: I-V curve of solar cell

#### Open Circuit Voltage ( $V_{oc}$ ):

While the current flowing over the surface is zero, difference in voltage between the terminals of the cell is called open circuit voltage.  $V_{oc}$  is nearly 0.65-0.70V in high efficiency Si solar cells [14, 15]. $V_{oc}$  can be found intersection point of I-V curve with the the horizontal axis.

### **Short Circuit Current (Isc):**

While the voltage difference is zero at the terminals of the cell, the current flowing along the cell is called short circuit current.  $I_{sc}$  can be found from the intersection point of the I-V curve with the vertical axis.

#### Maximum Power Point Voltage $(V_{MP})$ :

The voltage at which the solar cell generates the maximum power is called as maximum power point voltage.  $V_{MP}$  is equal to  $V_{oc}$  in an ideal solar cell.

#### **Maximum Power Point Current (IMP):**

It is defined as the current at which the maximum power is obtained. For an ideal cell,  $I_{MP}$  is equal to  $I_{sc}$ .

#### Fill Factor (FF):

The ideal I-V curve of the solar cell must be rectangular since  $V_{MP}$  is equal to  $V_{oc}$  and  $I_{MP}$  is equal to  $I_{sc}$  for ideal cell. However, I-V curve of cell deviates from the rectangular shape due to some losses, which is characterized by another parameter called fill factor. Fill factor (FF) is defined as

$$FF = \frac{V_{MP} \times I_{MP}}{V_{oc} \times I_{sc}}$$

(2.11)

#### **Efficiency:**

The ratio of output power to input power is the definition of efficiency for a solar cell. The input power of the sunlight can be found from the light intensity multiply by surface area. For a standard measurement system, the input power is set to be 1000W/m<sup>2</sup> which corresponds to AM1.5 condition described above. Efficiency of cell can be calculated as

$$\eta = \frac{P_{out}}{1000W/m^2 \times (surface\ area)}$$

(2.12)

Where  $P_{out}$  is defined as maximum output power and  $\eta$  is efficiency of solar cell.

#### **Shunt Resistance:**

Shunt resistance is defined as resistivity against the leakage currents along the p-n junction. It is a measure of the leak current present at the junction across the device area. Shunt resistance must be high in order to prevent leakage current. It can be calculated from slope of I-V curve at V=0.

$$R_{SH} = \frac{1}{\frac{dI}{dV}}, \quad \text{at } V = 0$$

(2.13)

Low shunt resistance value affects the cell efficiency directly in negative way and it results from production steps

#### **Series Resistance:**

Series resistance can be defined the total resistance of the device. It is the sum of different resistive components like, bulk resistance of semiconductor and metal contact resistance. It is an important parameter, since series resistance affects directly solar cell performance. Higher series resistance deteriorates the performance of the cell. For ideal solar cells, series resistance is zero clearly.

# **CHAPTER 3**

# PRODUCTION STEPS OF N-TYPE AND P-TYPE Si SOLAR CELLS

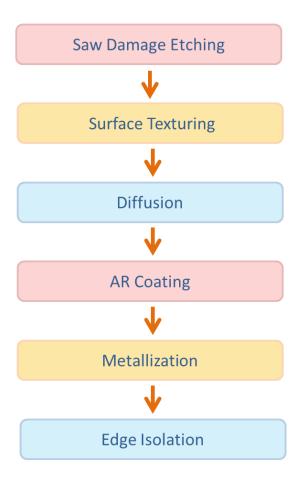

In this section, the process steps which are performed during the production of p type and n type float zone silicon wafer will be introduced. The aim of process and theory of that will be discussed in this chapter. All the process steps needed to fabricate a solar cell is shown in the flow chart below,

Figure 3. 1: Flow chart of production steps for n-type and p-type solar cells

# 3.1. Saw Damage Etching:

## **3.1.1.** Aim of Saw Damage Etching

Reducing the reflection on the surface is an essential process in order to increase the efficiency of the solar cell via reducing optical losses. The most effective way of reducing the reflection from the surface and increasing the absorption of the light is to texture the surface and coating it with an anti-reflective layer that also contributes to the electrical passivation of the surface.

It is known that initial surface morphology is not good enough due to the damages created by the wafering process which is usually done by wire sawing. This damaged surface should be cleaned and polished before any other process. Therefore, before the texturing, wafers are processed with an alkaline chemical etching called as saw damage etching. This process makes the surface of the wafer flat and ready for the further texture etching. The saw damage etching is often performed using highly concentrate potassium hydroxide (KOH) solution.

#### 3.1.2. Experiment

In this study, we used boron doped p type and phosphorous doped n type doped wafers produced by float zone technique. Wafers have (100) crystallographic direction, thickness nearly  $200\mu m$ ,  $1-5~\Omega cm$  electrical resistivity.

Saw damage etching of the as-cut silicon wafers was done by a mixture of KOH and DI water (1 unit KOH and 5 units DI). In this step, a heater and a thermocouple were used to control the temperature. A magnetic stirrer enabled us to obtain homogenous solution.

In this study, as cut wafers were dipped in the KOH solution at  $80^{\circ}$ C for 1 min., 2 min., 4min. and 6min., respectively in order to remove the surface defects. Then, wafers were cleaned in DI water and dried by  $N_2$ . We have optimized the etching process through a series of systematic solution.

#### 3.1.2.1. Reflection Measurement

Reducing reflection from the surface is a crucial for an efficient cell operation. It is important to control the effectiveness of anti-reflective layers. During the fabrication steps, the reflection of the samples is measured after each of the saw damage etching, texturing and anti-reflective thin film covering steps.

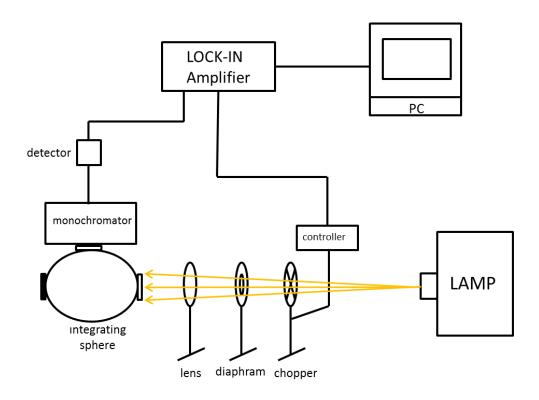

The reflection setup consists mainly of light source, chopper, integrating sphere, monochromator, diaphragm & lens, photodetector (UV enhanced Silicon) and lock-in amplifier; as can be seen below Figure 3.2.

Monochromator has input slit and output slit. Output slit of monochromator is attached to a detector and the input slit is attached to the integrating sphere. Integrating sphere is used since textured wafers have both specular and diffuse reflection. It provides to collect all of them. Chopper is placed in front of the lamp, which provides modulation of the light beam. The light beam is focused onto the reflection sample port of the integrating sphere with the help of lenses and a diaphragm. The alignment of the components is important, because the spot size should be smaller than the port size at the reflection port. This can be checked using a piece of paper. When no sample is placed, all light should exit the sphere from this sample port, which would minimize the dark signal. Dark signal should be minimized for better signal to noise ratio.

Two measurements were carried out in order to determine total reflection of sample before the reflection measurement of samples. One is performed by calibration disk. Calibration disk is a reference sample used for complete reflection. The other is done without any sample, which is called as dark measurement. Total reflection of sample is calculated by (3.1).

$$total reflection = \frac{Measured - Dark}{Calibration - Dark}$$

(3.1)

At the reflection port, the sample is placed at the angle of 8 degrees, so that the specularly reflected light does not leave the sphere from the entrance port, but strikes the inside of the sphere instead. Therefore total reflection is measured (diffuse + specular reflection).

#### 3.1.3. Results of Etching Experiments

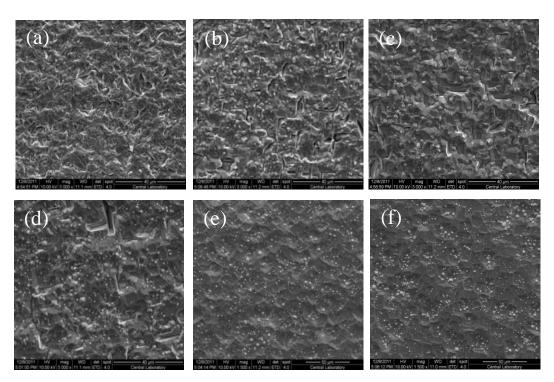

We have performed a series of experiments to determine the best surfaces for solar cell production. We studied effect of etch duration by holding the samples in the solution. The resultant surfaces were characterized using SEM and optical reflection measurements.

As seen in Figure 3.3, the surface of bare wafer has saw damage considerably. Samples held in the KOH solution for 0.5 min. and 1 min. have still porous surface so that these time periods were not enough to remove damage from the surface. Sample held in KOH solution for 2 min. has a better surface for solar cell applications despite the roughness left on the surface. Although samples held in KOH solution for 4min. and 6 min. have shiny surfaces, they are not suitable for solar cell due to reduced thickness. Thinner wafers result in reduced absorption of light and they are difficult to handle during production process.

Figure 3. 2: Schematic of reflectance measurement setup

Figure 3. 3: SEM images of bare wafer (a), 0.5min. in KOH (b), 1 min. in KOH (c) ,2 min. in KOH (d), 4 min in KOH (e), 6 min. in KOH (f)

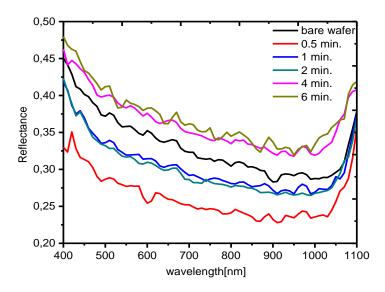

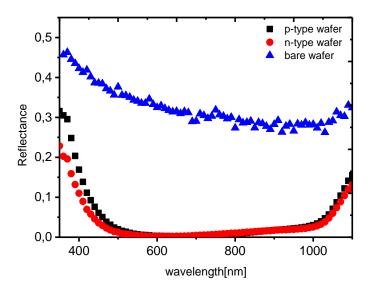

Figure 3. 4: Reflection measurement results of different samples

According to the results shown in Figure 3.4, 0.5 min KOH sample results in lowest reflection among the other samples. However, surface of this sample was not suitable for the texturing process because it needs smooth surface to properly form the pyramids. Therefore, 2 min. KOH process is determined to be optimum for our studies.

# 3.2. Surface Texturing for Lower Reflection

# 3.2.1. Theory of texturing

Reduction of the surface reflectance is of a great importance in maximizing the energy conversion efficiency by a solar cell. Reducing reflection will enhance the absorption and creation of electron-hole pairs in the active region of the solar cell, and thus improve the conversion efficiency. One of the techniques that reduce the reflection is to texture the surface of the cell in such a way that the interaction of the light beam with the surface is increased. In principle, texturing should enhance the current output of the solar cell substantially. Therefore, texturing is an important process that should be carried out during the solar cell fabrication.

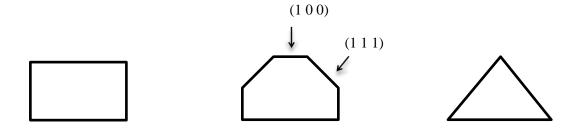

The aim of texturing is to create a new surface morphology on the silicon wafer that provides multiple light interactions with the cell surface. For single crystalline and wafer-based solar cells, it can be achieved by anisotropic etching using an alkali solution which forms pyramidal shapes on the surface of the silicon wafer. These pyramids are formed randomly on the surface of the silicon due to the etch rate differences of KOH solution for different crystal orientation.

Potassium hydroxide (KOH) has been used to make three dimensional shapes on Si surface and bulk. It is the major chemical etchant material of microelectromechanical systems (MEMS) technology. KOH is highly anisotropic with the extremely low etch rate for (111) plane. When applied to a Si wafer having an initial surface orientation of (100), the surface will ultimately be covered with pyramids having 111 surfaces only. In order to improve the quality of the surface, KOH is used with with isopropyl alcohol (IPA) and deionized water (DI) solution.

Anisotropic etching of the silicon in that solution occurs by means of the following mechanism [16].

$$SI + 4OH^{-} \rightarrow Si(OH)_{4} + 4e^{-}$$

(3.2)

In this process, etch rate of potassium hydroxide on the (100) and (111) plane is of determining role. During the texturing process, (1 0 0) oriented mono-crystalline wafer is etched in a mixture of KOH, IPA and water with a very high rate until all surfaces become (111) plane. In this way, pyramids on the surface of the wafer are formed as illustrated in Figure 3.5.

Etch rate of KOH solution for silicon substrate;

etch rate

$$(100)$$

plane/etch rate  $(111)$  plane =  $600/1$

Figure 3. 5: Process of anisotropic etching for (10 0) oriented silicon wafer

The shape of the new surface contributes to increasing the optical length of the light as shown in Figure 3.6. As can be seen in Figure 3.6, the number of reflection on the surface of the wafer and the generation of electron-hole pairs are increased dramatically in this way.

Figure 3. 6: Reflection of incident light beam from smooth surface (a), from textured surface

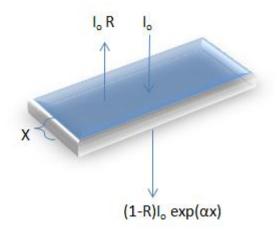

Figure 3. 7: Reflection and transmition of incident light in semiconductor

The amount of optical gain by surface texturing can be calculated as follows: When a beam of photons having an energy E and intensity  $I_o$  enter the material and travels a thickness x, (Figure 3.7) the amount of light absorbed by the material is determined by Beer-Lambert law:

$$\frac{dI}{dx} = -\alpha I \tag{3.3}$$

Where  $\alpha$  is the absorption coefficient. The solution of this equation is found from

$$I(x) = I(0)e^{-\int \alpha dx}$$

(3.4)

For uniform  $\alpha$ ; the equation becomes,

$$I(x) = I(0)e^{-\alpha x} \tag{3.5}$$

For this reason, it can be said that the total reflectivity of the surface is reduced from IR to IR<sup>2</sup> by pyramidal structure formed after the texturing process (0<R<1) as shown in Figure 3.8.

Figure 3. 10: Intensity of reflected light beam

#### 3.2.2. Experimental Procedures

In this step, saw damage etched wafers have been used as sample. On the contrary saw damage etching process, the solution has been prepared as dilute solution relatively.

Texturing of the silicon wafers were done within a 20 liter tank by mixing KOH, DI water and IPA. In this process, thermocouple, heater and magnetic stirrer are used for the control of temperature, setting the desired temperature value and obtaining homogeneous mixture, respectively.

The mixture ratio of KOH, DI water, IPA in the solution, the etch duration and the temperature are all crucially important in reaching the best condition on the surface.

We studied and optimized the solution composition. For this purpose we varied the process parameters as summarized in the table below.

We see that a large number of experiments have been carried out in this experiment. In choosing the process parameters listed in Table 3.1, we analyzed the data available in the literature and considered the physical-chemical properties of the solution. For instance, we know that the IPA is not effective when the temperature is above its boiling point (82.5°C). We also know that KOH solution does not work at temperatures below 70°C. Form the data available in the literature, the concentration of KOH and IPA should not exceed %4 and %15 respectively [17].

Table 3. 1: Variables of texturing process

| Variables                 | Lower Limit | Upper Limit |

|---------------------------|-------------|-------------|

| KOH concentration (wt %)  | 2           | 4           |

| IPA concentration (wt %)  | 10          | 15          |

| Time (min)                | 35          | 50          |

| Solution temperature (°C) | 75          | 80          |

Wafers were first exposed to 1:20 HF: DI solution in order to eliminate the natural oxide on the surface of them, then they were rinsed by DI. Then, they were immersed in to the etch tank for the desired period of time. After all of these processes, they were cleaned by DI again and dried by N<sub>2</sub>. During the experiments, speed of mechanical stirrer was constant at 220 rpm.

#### 3.2.3. Results of Texturing Experiments

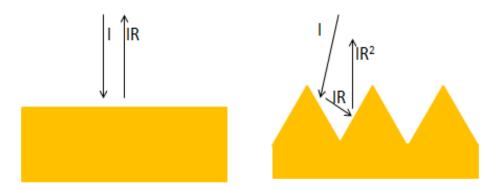

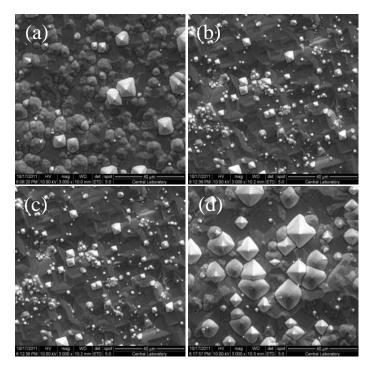

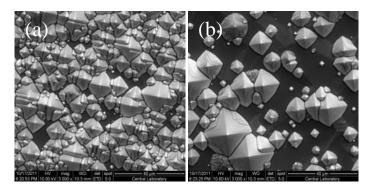

Figure 3.9 shows SEM images of the process, including 2 wt % KOH and 10 wt % IPA at 75°C for 35 min., 40min., 45 min., 50 min. as seen in the Figure 3.9, 35 minutes is not enough for formation of pyramids since surface is just started for this duration. Pyramids start to be formed at 40 minutes and 45 minutes, but the reflection from the surface is still far from the desired conditions for these samples. As for 50 minutes, pyramids formed on the surface, but their distribution is not homogenous.

Figure 3.10 shows SEM images of the process, including 2 wt % KOH and 15 wt % IPA at 75°C for 35 min., 40min., 45 min.,50 min. We see from these figures that increasing the amount of IPA is worsening the pyramid formation.

Figure 3. 11: SEM images of samples textured in 2 wt % KOH and 10 wt % IPA solution at 75°C for 35 min. (a), 40 min. (b), 45 min. (c) ,50 min. (d)

Figure 3. 10: SEM images of samples textured in 2 wt % KOH and 15 wt % IPA solution at 75°C for 35 min. (a), 40 min. (b), 45 min. (c) ,50 min. (d)

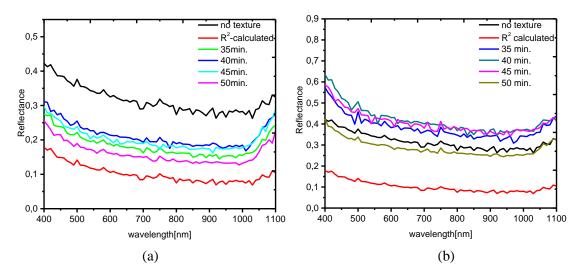

Figure 3.11: Reflection measurement results of samples textured in 2 wt % KOH and 10 wt % IPA solution (a) and in 2 wt % KOH and 15 wt % IPA solution (b) at 75°C for different time periods.

As seen the Figure 3.11, solutions, including 2 wt % KOH-10 wt % 10 IPA and 2 wt % KOH and 15 % IPA do not provide good results in terms of reflection. Samples which belong to both solutions are far away from expected result.

Figure 3. 12: SEM images of samples textured in 3 wt % KOH and 10 wt % IPA solution at 75°C for 35 min. (a), 40 min. (b), 45 min. (c), 50 min. (d)

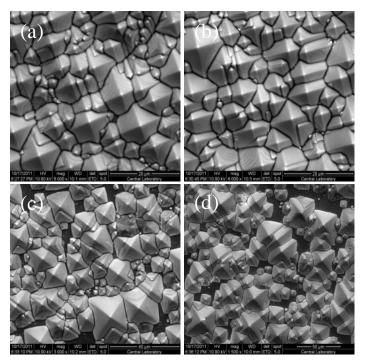

Figure 3.12 shows SEM images of the process, including 3 wt % KOH and 10 wt % IPA at 75°C for 35 min., 40min., 45 min., 50 min. It is apparent that 35 minutes and 40 minutes are not enough to form shape like pyramids. Pyramids started to be formed at 45 minutes along the whole surface.

Figure 3.13 shows that higher rate of IPA in solution deteriorates the surface quality compared to results of Figure 3.10. It is observed that pyramids could not start to form in solution, including 3 wt % KOH and 15 wt % IPA at 75°C for 45 min. and 50 min.

Figure 3. 13 : SEM images of samples textured in 3 wt % KOH and 15 wt % IPA solution at 75°C for 45 min. (a), 50 min. (b)

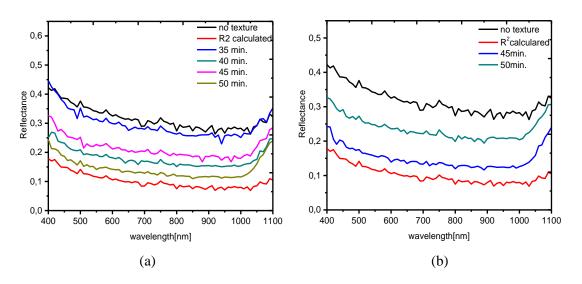

Figure 3. 14: Reflection measurement results of samples textured in 3 wt % KOH and 10 wt % IPA solution (a) and in 3 wt % KOH and 15 wt % IPA solution (b) at 75°C for different time periods.

In Figure 3.14, better results have been obtained in terms of reducing reflection when the etch-time was increased. However, when the amount of IPA in solution was increased, reflection from the surface increased since surface of the wafer has lost homogeneity. According to these results, it is concluded that the amount of IPA has affected directly surface morphology and the shape of pyramids.

Figure 3.15 shows SEM images of the process, including 3 wt % KOH and 10 wt % IPA at 80°C for 35 min., 40min., 45 min., 50 min. It is clear that pyramids started to grow on top of each other at 35 min. and 45 min. since reaction occurs faster due to the increased temperature. As for 45 min. and 50 min., pyramidal shapes on the surface could not be preserved. Therefore, increase in temperature affects quality of the surface negatively.

Figure 3. 15: SEM images of samples textured in 3 wt % KOH and 10 wt % IPA solution at 80°C for 35 min. (a), 40 min. (b), 45 min. (c), 50 min. (d)

Figure 3.16 shows SEM images of the process, including 4 wt % KOH and 10 wt % IPA at 75°C for 35 min., 40min., 45 min., 50 min. It can be expressed that solution behaves aggressively because pyramidal shapes on the surface were annihilated by solution after the 45 minutes. On the contrary to this, pyramids could not be formed on the whole surface by that solution at 35 and 40 minutes.

According to Figure 3.17a, increasing process temperature increased the deviation from the  $R^2$ . Similarly as seen Figure 3.17b, increasing KOH concentration also increased the deviation from  $R^2$ . is the theoretical limit of surface reflectance

Figure 3.16: SEM images of samples textured in 4 wt % KOH and 10 wt % IPA solution at 75°C for 35 min. (a), 40 min. (b), 45 min. (c),50 min. (d)

Taking all SEM and Reflection measurement results into account, it could be said that optimum process temperature is 75°C and optimum KOH concentration is between 3-4 wt % with optimum IPA concentration is 10 wt %. Optimum etch time is found to be 45 minutes.