# TRUE-TIME DELAY STRUCTURES FOR MICROWAVE BEAMFORMING NETWORKS IN S-BAND PHASED ARRAYS

### A THESIS SUBMITTED TO THE GRADUATE SCHOOL OF NATURAL AND APPLIED SCIENCES OF MIDDLE EAST TECHNICAL UNIVERSITY

BY KAAN TEMİR

IN PARTIAL FULLFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE IN ELECTRICAL AND ELECTRONICS ENGINEERING

JANUARY 2013

#### Approval of the thesis:

### TRUE-TIME DELAY STRUCTURES FOR MICROWAVE BEAMFORMING NETWORKS IN S-BAND PHASED ARRAYS

submitted by Kaan TEMIR in partial fulfillment of the requirements for the degree of Master of Science in Electrical and Electronics Engineering Department, Middle East Technical University by,

| Prof. Dr. Canan Özgen<br>Dean, Graduate School of <b>Natural and Applied Sciences</b> |  |

|---------------------------------------------------------------------------------------|--|

| Dean, Graduate School of <b>Natural and Applied Sciences</b>                          |  |

| Prof. Dr. İsmet Erkmen                                                                |  |

| Head of Department, Electrical and Electronics Eng.                                   |  |

| Assoc. Prof. Dr. Şimşek Demir                                                         |  |

| Supervisor, Electrical and Electronics Eng. Dept.,METU                                |  |

| Examining Committee Members:                                                          |  |

| Prof. Dr. Canan TOKER                                                                 |  |

| Electrical and Electronics Eng. Dept., METU                                           |  |

| Assoc. Prof. Dr. Şimşek DEMİR                                                         |  |

| Electrical and Electronics Eng. Dept., METU                                           |  |

| Prof. Dr. Gönül Turhan SAYAN                                                          |  |

| Electrical and Electronics Eng. Dept., METU                                           |  |

| Prof. Dr. Özlem Aydın ÇİVİ                                                            |  |

| Electrical and Electronics Eng. Dept., METU                                           |  |

| M.Sc. Eser ERKEK                                                                      |  |

| REHIS/TTD-MBM, ASELSAN INC.                                                           |  |

|                                                                                       |  |

**Date:** 31.01.2013

I hereby declare that all information in this document has been obtained and presented in accordance with academic rules and ethical conduct. I also declare that, as required by these rules and conduct, I have fully cited and referenced all material and results that are not original to this work.

Name, Last name: Ka

Kaan TEMİR

Signature :

# ABSTRACT

#### TRUE-TIME DELAY STRUCTURES FOR MICROWAVE BEAMFORMING NETWORKS IN S-BAND PHASED ARRAYS

Temir, Kaan M. Sc. Department of Electrical and Electronics Engineering Supervisor: Assoc. Prof. Dr. Şimşek Demir January 2013, 97 pages

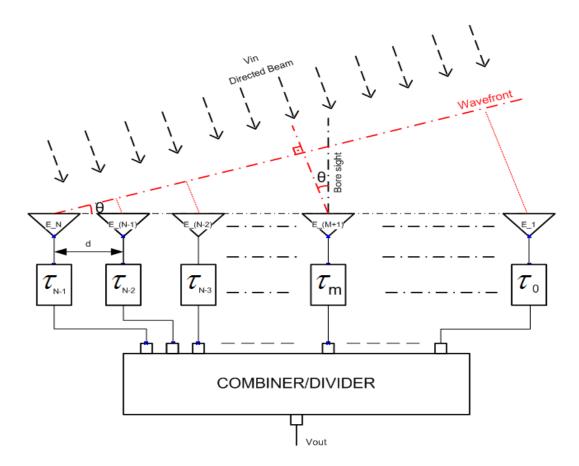

True time delay networks are one of the most critical structures of wideband phased-array antenna systems which are frequently used in self-protection and electronic warfare applications. In order to direct the main beam of a wideband phased-array antenna to the desired direction; phase values, which are linearly dependent to frequency, are essential. Due to the phase characteristics of the true-time delay networks, beam squint problems for broadband phased array systems are minimized.

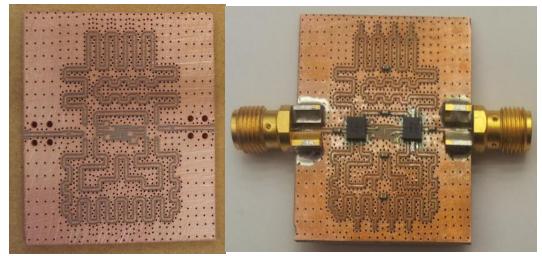

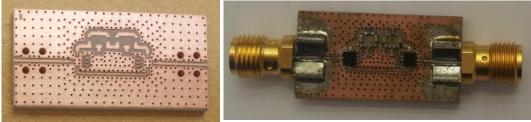

In this thesis, different types of true-time delay structures are investigated for wideband phased array applications and a tunable S-band true-time delay network having delay over 1ns with high resolution is developed, designed, fabricated and measured. Lower-cost, smaller occupied area, digital/analog control mechanism and ease of implementation are the other features of the developed network.

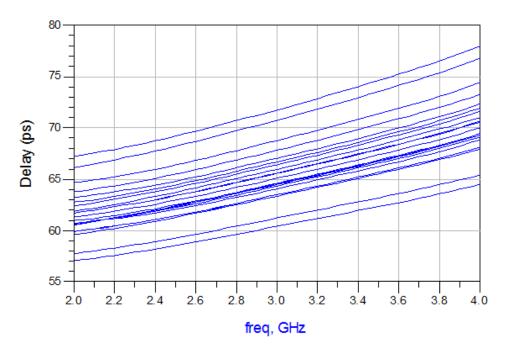

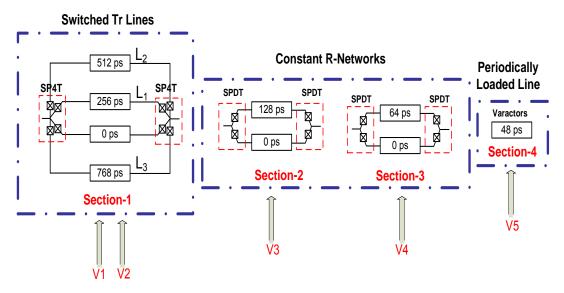

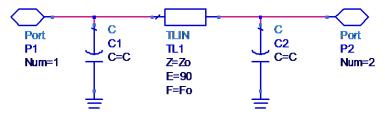

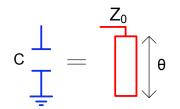

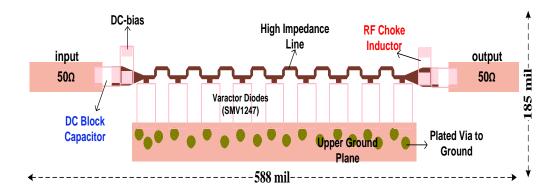

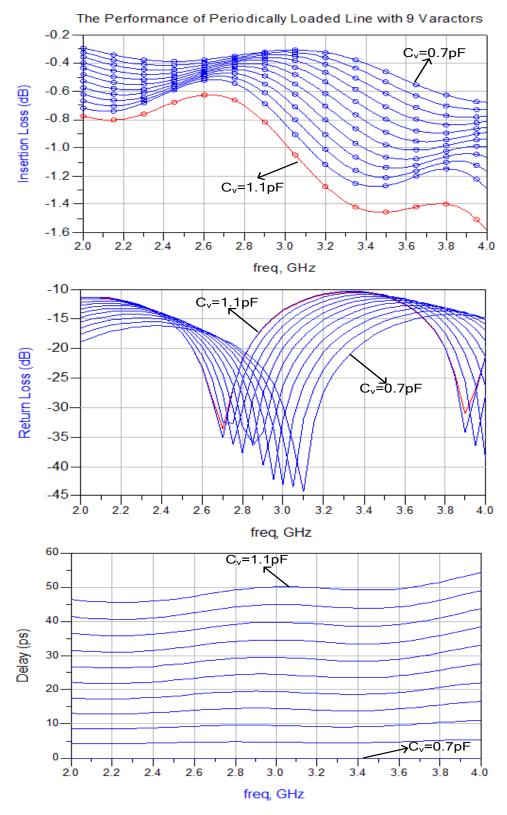

High delay values with high resolutions for wideband operation are achieved through the combination of several techniques; therefore the desired S-band TTD network is constructed with the synthesis of switched-transmission lines, constant-R networks and periodically-loaded transmission lines. Higher delay states are realized by the switched-transmission lines technique, while the method of constant R-network is used for the intermediate delay states. To increase the tuning flexibility, smaller delay states are accomplished by analog-voltage controlled periodically loaded transmission lines.

A step-by-step procedure is followed during the design process of the S-band true time delay network. Firstly, each method used in the TTD network is analyzed in detail and developed for PCB implementation and the use of COTS components. Then, the designed structures are verified via linear and EM simulations performed by ADS2011<sup>®</sup>. After that, the effects of production tolerances are examined to optimize each design for S-band operations. Moreover, the designed structures are fabricated by using PCB technology and measured. Finally, a software code is developed in MATLAB to generate the overall cascaded network with the help of measured data.

Keywords: Beam Squint, Delay, Phase Delay, True-Time Delay, Wideband Phased-Array.

#### S-BANT FAZLI DİZİLERDE MİKRODALGA HUZME YÖNLENDİRME YAPILARI İÇİN GERÇEK ZAMAN GECİKME YAPILARI

Temir, Kaan Yüksek Lisans, Elektrik ve Elektronik Mühendisliği Bölümü Tez Yöneticisi: Doç. Dr. Şimşek Demir Ocak 2013, 97 sayfa

Zaman gecikme yapıları kendini koruma ve elektronik harp uygulamalarında yaygın olarak kullanılan geniş bant fazlı dizi anten sistemlerinin en önemli yapılarından bir tanesidir. Fazlı dizilerde ana huzmeyi istenen yöne yönlendirmek için frekansla doğru orantılı faz değerleri gereklidir. Zaman gecikme yapılarının faz karakteristiği geniş bantlı fazlı dizi sistemlerde yaşanan huzme sapması problemlerini en aza indirgemektedir.

Bu tez çalışmasında, geniş bantlı fazlı dizi uygulamaları için çeşitli zaman gecikme yapıları araştırılmış ve S-bandında çalışan, yüksek çözünürlüklü, 1ns üzerinde toplam gecikmeye sahip, ayarlanabilir bir zaman gecikme yapısı geliştirilmiş, tasarlanmış, üretilmiş ve ölçülmüştür. Geliştirilen yapının diğer özellikleri düşük maliyetli olması, küçük boyuta sahip olması, dijital/analog kontrol edilebilmesi ve kolay bir şekilde gerçeklenmesidir.

Geniş bantta, yüksek çözünürlüğe sahip yüksek gecikme değerleri ancak birçok tekniğin bir arada kullanılması yoluyla gerçekleştirilebilir. Bu sebeple, S-bantta tasarlanan TTD yapısı iletim hatlarının anahtarlanması, sabit empedans devreleri ve periyodik olarak yüklenen iletim hatlarının sentezlenmesi ile oluşturulmuştur. Orta seviye gecikme değerleri için sabit empedans devreleri metodu kullanılırken, yüksek gecikme değerleri anahtarlanabilir iletim hatları tekniği ile gerçeklenmiştir. Ayarlama esnekliğini arttırmak için, düşük gecikme durumları analog-voltaj kontrollü periyodik olarak yüklenen iletim hatları kullanılarak başarılmıştır.

Tasarım kısmında, S-bandındaki gerçek zaman gecikme yapısı adım adım geliştirilmiştir. İlk olarak tasarımda kullanılan her bir metot detaylı bir şekilde analiz edilmiş, bu yapılar baskı devre tekniği ve piyasadaki malzemeler kullanılarak üretilmek üzere geliştirilmiştir. Sonraki aşamada tasarlanan yapılar ADS2011<sup>®</sup> kullanılarak lineer ve elektromanyetik benzetimlerle doğrulanmıştır. Ardından, üretimden kaynaklanabilecek toleransların yapılara etkisi araştırılmış ve her bir yapı S-bandında çalışabilmesi için optimize edilmiştir. Tasarlanan yapılar baskı devre tekniği ile üretilmiş ve ölçülmüştür. Son olarak, elde edilen ölçüm sonuçları kullanılarak MATLAB yardımıyla art arda bağlanan TTD yapısı oluşturulmuştur.

Anahtar Kelimeler: Faz Gecikmesi, Gecikme, Geniş Bant Fazlı Dizi, Gerçek Zaman Gecikmesi, Huzme Sapması.

# ÖZ

# **ACKNOWLEDGEMENTS**

I would like to express my sincere gratitude to my adviser, Assoc. Prof. Dr. Şimşek Demir, for his guidance, patience, support and technical suggestions throughout the study. I would also like to thank Prof. Dr. Canan Toker, Prof. Dr. Gönül Turhan Sayan, Prof. Dr. Özlem Aydın Çivi and Mr. Eser Erkek being in my jury and sharing their opinions.

I would like to express my gratitude to Mr. H.Aydın Yahşi for proposing this topic to me and Mr. Murat Sencer Akyüz for providing every support throughout the development of the conducted studies.

I am grateful to ASELSAN A.Ş. for the financial and technical opportunities provided for the completion of this thesis.

I would also like to express my sincere appreciation for Egemen Yıldırım, Kadir İşeri, Damla Duygu Tekbaş, Çağdaş Gücün, Erinç Gücün and Kamil Karaciğer for their valuable friendship, motivation and help.

I would like to thank TÜBİTAK for providing financial support during the study.

Finally, I would like to thank to Tuğçe Serbez for being with me in every moment of this work and giving me the strength and courage to finish it.

# TABLE OF CONTENTS

| ABSTRACT                                                                               | v    |

|----------------------------------------------------------------------------------------|------|

| ÖZ                                                                                     | vi   |

| ACKNOWLEDGEMENTS                                                                       | vii  |

| TABLE OF CONTENTS                                                                      | viii |

| LIST OF TABLES                                                                         | x    |

| LIST OF FIGURES                                                                        | xi   |

| LIST OF SYMBOLS                                                                        | xiii |

| CHAPTERS                                                                               |      |

| 1.INTRODUCTION                                                                         | 1    |

| 1.1 Preface                                                                            | 1    |

| 1.2 A Brief Review of Developments in TTD Networks                                     | 2    |

| 1.3 Thesis Outline                                                                     | 5    |

| 2.FUNDAMENTALS OF TIME DELAY NETWORKS                                                  | 7    |

| 2.1 Brief Explanation of Time Delay for Phased Array Systems                           | 7    |

| 2.2 Types of Variable TTD Networks                                                     | 11   |

| 2.2.1 Methodologies for TTD Generation                                                 | 11   |

| 2.2.1.a Manipulating The Wave Velocity                                                 |      |

| 2.2.1.b Manipulating the Propagation Distance                                          |      |

| 2.2.2 Control Mechanism for Variable TTD Networks                                      | 18   |

| 2.3 Design Parameters of TTD Networks and Their Effects in PAA Systems                 |      |

| 2.3.1 Operating Frequency and Bandwidth                                                |      |

| 2.3.2 Insertion Loss over Frequency                                                    |      |

| 2.3.3 Return Loss over Frequency                                                       |      |

| 2.3.4 Total Delay Time and Number of Bits                                              |      |

| 2.3.5 Time Delay Variation over Frequency and RMS Delay Error                          |      |

| 2.3.6 Loss Flatness over Frequency                                                     |      |

| 2.3.7 Amplitude Imbalance                                                              |      |

| 2.3.8 Capacity of Power Handling                                                       |      |

| 2.3.9 Tuning Speed and Rise/Fall Time                                                  |      |

| 2.3.10 Size and Power Consumption                                                      |      |

| <ul><li>2.3.11 Cost and Complexity</li><li>2.3.12 Environmental Requirements</li></ul> |      |

| 3.DESIGN OF A WIDEBAND TRUE-TIME DELAY NETWORK                                         |      |

|                                                                                        |      |

| 3.1 Design Requirements for Desired TTD Network                                        |      |

| 3.2 The Types of Transmission Lines and Production Technology Process                  |      |

| 3.3 Frequently Used Topologies and Linear Simulations                                  |      |

| 3.3.2 Switched-Reflection Lines Network                                                                                       |                            |  |

|-------------------------------------------------------------------------------------------------------------------------------|----------------------------|--|

| 3.3.3 Periodically Loaded Transmission Lines Network                                                                          |                            |  |

| 3.3.4 Loaded Reflection Lines Network                                                                                         | 34                         |  |

| 3.3.5 Constant-R Network                                                                                                      | 35                         |  |

| 3.4 Analysis and Design for Desired TTD Network                                                                               | 39                         |  |

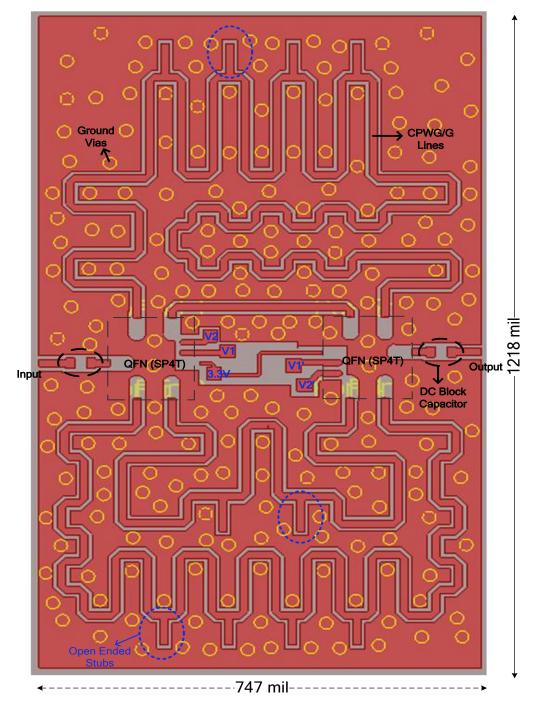

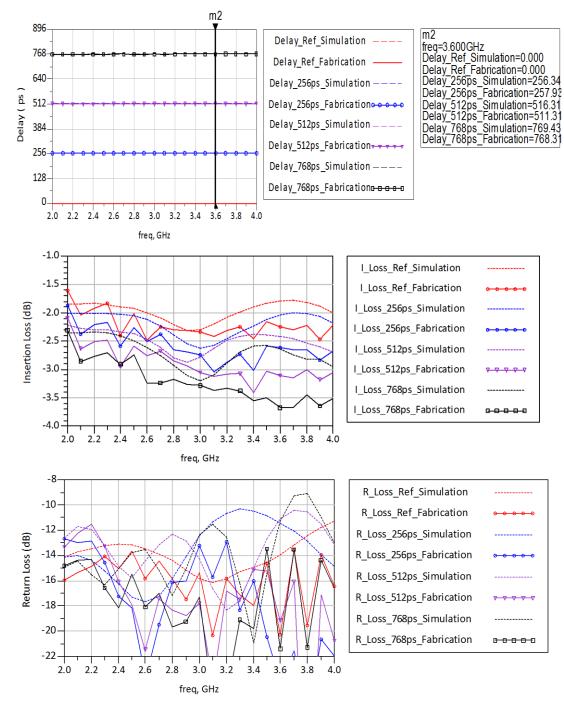

| 3.4.1 TTD Design Using Switched-Transmission Lines                                                                            | 39                         |  |

| 3.4.1.a Selection of the Substrate                                                                                            | 39                         |  |

| 3.4.1.b Selection of the Switching Elements and Configuration                                                                 | 40                         |  |

| 3.4.1.c Choosing the Reference Line Length                                                                                    | 46                         |  |

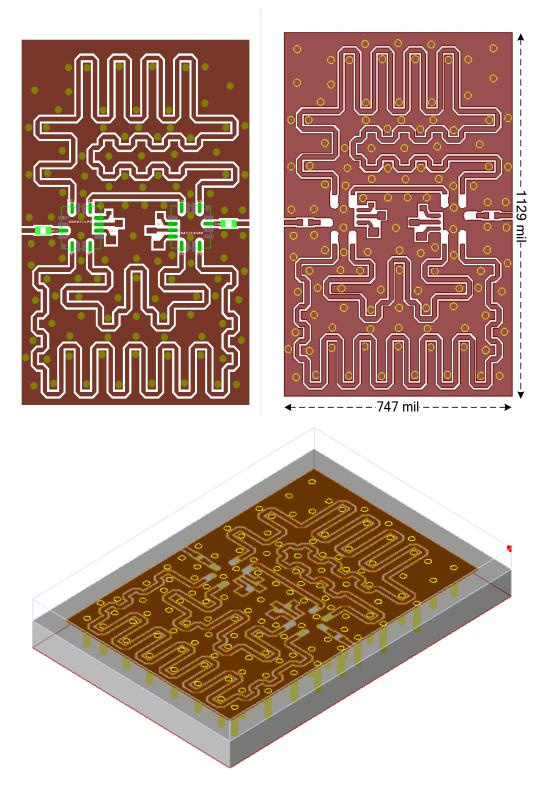

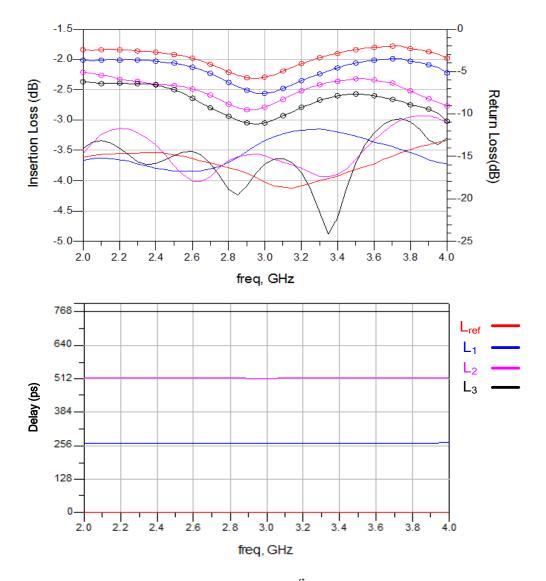

| 3.4.1.d Drawings of Each Line and Synthesis of the Layouts                                                                    | 47                         |  |

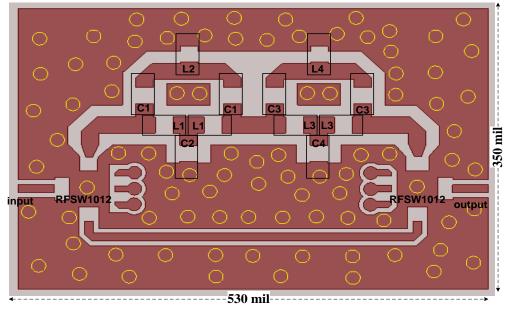

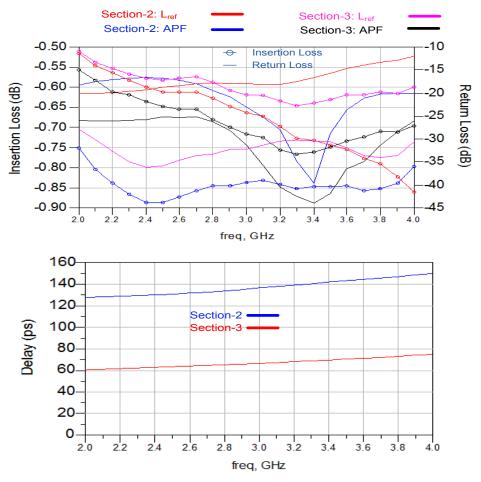

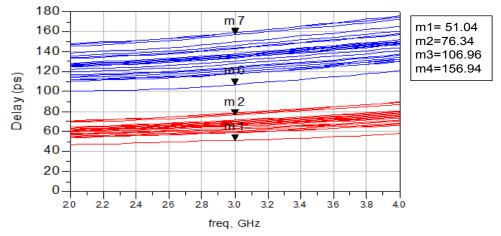

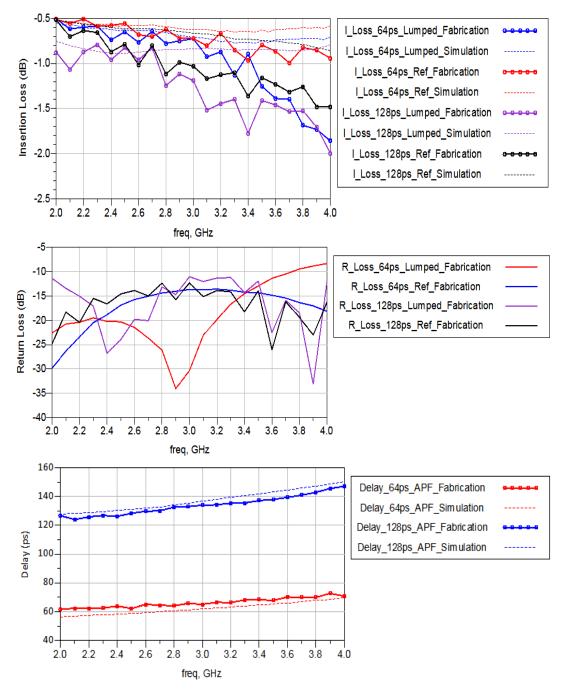

| 3.4.2 TTD Design Using Periodically Capacitive Loaded Transmission Lines                                                      | 58                         |  |

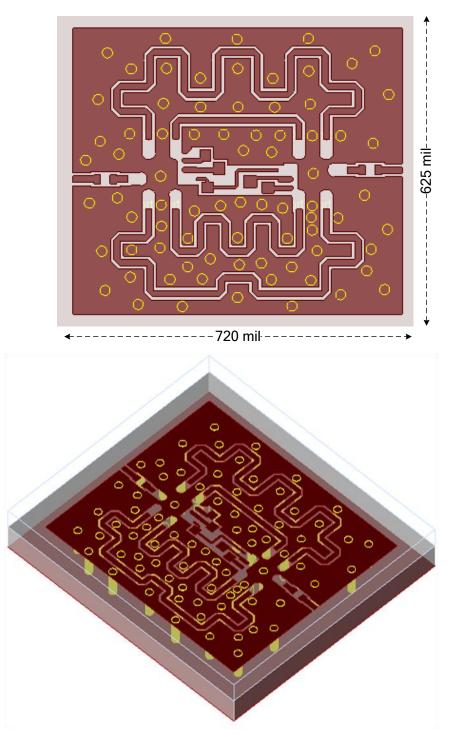

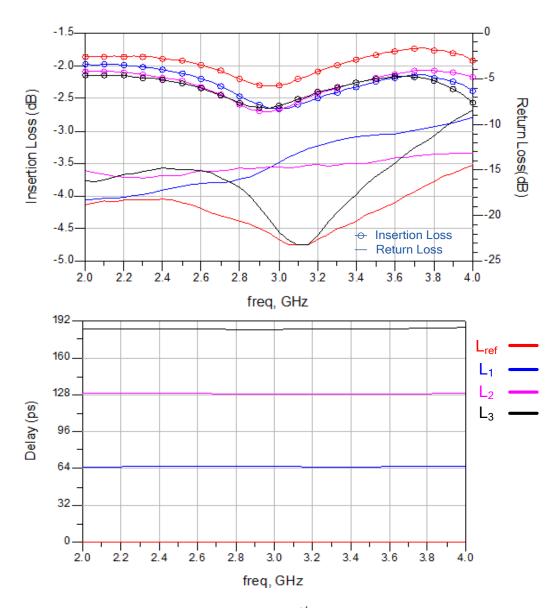

| 3.4.3 TTD Design Using Constant R-Network                                                                                     | 61                         |  |

|                                                                                                                               |                            |  |

| 4.PRODUCTION OF THE DESIGNED TTD NETWORK AND MEASUREMENTS                                                                     | 67                         |  |

| 4.PRODUCTION OF THE DESIGNED TTD NETWORK AND MEASUREMENTS                                                                     |                            |  |

|                                                                                                                               | 68                         |  |

| 4.1 Design of the TTD Network Sections                                                                                        | 68<br>77                   |  |

| <ul><li>4.1 Design of the TTD Network Sections</li><li>4.2 Fabrication and Measurement of the Each Designed Section</li></ul> | 68<br>77<br>81             |  |

| <ul> <li>4.1 Design of the TTD Network Sections</li></ul>                                                                     | 68<br>77<br>81<br>83       |  |

| <ul> <li>4.1 Design of the TTD Network Sections</li></ul>                                                                     | 68<br>77<br>81<br>83       |  |

| <ul> <li>4.1 Design of the TTD Network Sections</li></ul>                                                                     | 68<br>77<br>81<br>83<br>85 |  |

# LIST OF TABLES

## TABLES

| Table 3-1: The Requirements for the Desired TTD Network                                              | . 26 |

|------------------------------------------------------------------------------------------------------|------|

| Table 3-2: The Comparison of Different Production Technologies                                       | . 26 |

| Table 3-3: The Comparison of Different Transmission Line Types                                       | . 27 |

| Table 3-4: Properties of the Substrates with High Dielectric Constant                                |      |

| Table 3- 5: Commercially Available Switches in Market                                                | . 42 |

| Table 3-6: Widths of Transmission Lines for 50mil RO3210                                             |      |

| Table 3-7: CPWG/G Line Lengths for SP4T Switched Lines TTD Network                                   |      |

| Table 3-8: The results of the MSB for SP4T Switched Lines                                            |      |

| Table 3-9: The results of the 2 <sup>nd</sup> bit for SP4T Switched Lines                            |      |

| Table 3-10: The results of the 3 <sup>rd</sup> bit for SP4T Switched Lines                           | . 57 |

| Table 3-11: Capacitance Range vs Characteristic Impedances in Periodically Loaded Lines              | . 58 |

| Table 3-12: SMD Varactor Diode Products for S-band TTD Design                                        |      |

| Table 3-13: SMD Inductors of COILCRAFT for Lower Inductance                                          | . 64 |

| Table 3-14: Conductor Widths for 50Ω CPWG/G Lines                                                    |      |

| Table 4-1: Control Voltages for Desired TTD Network                                                  |      |

| Table 4-2: Delay Reduction Caused By RO3210 $\epsilon_r$ Tolerance in Section-1                      | . 68 |

| Table 4-3: Simulation Results for Section-1                                                          |      |

| Table 4-4: Coilcraft RF Chip Inductors@3GHz                                                          | . 72 |

| Table 4-5: AVX 0402 Package Accu-P Series Capacitors                                                 | . 72 |

| Table 4-6: Selected SMD Components for the Designs of Section-2 and Section-3                        |      |

| Table 4-7: Simulation Results for Section-2 and Section-3                                            | . 74 |

| Table 4-8: Simulation Results for Section-4                                                          | . 76 |

| Table 4-9: Different Arrangements of the Designed Sections for Cascaded Layout                       | . 81 |

| Table A-1: Delay Values for T-section Mutually Coupled Inductors                                     |      |

| Table A-2: Q values for 2 <sup>nd</sup> Order APF Satisfying Flat Delay over at Least an Octave Band | . 92 |

# **LIST OF FIGURES**

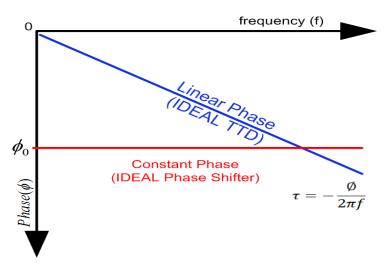

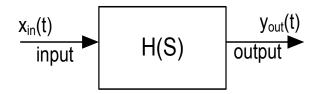

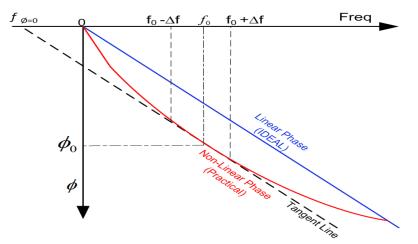

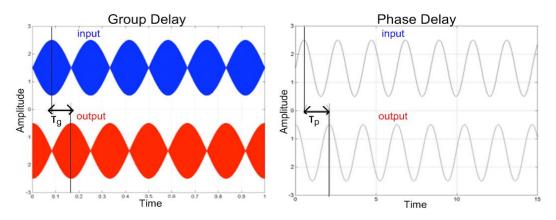

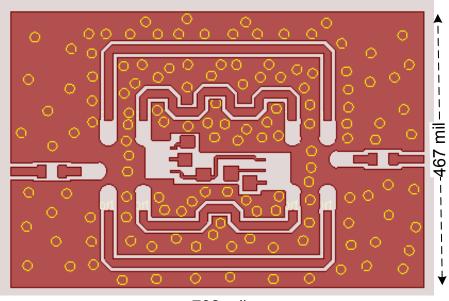

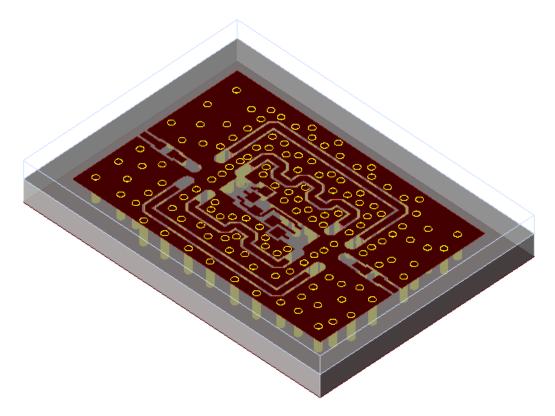

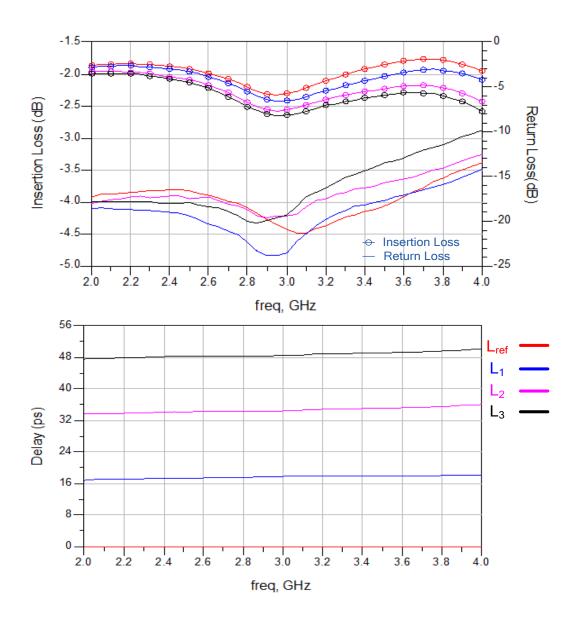

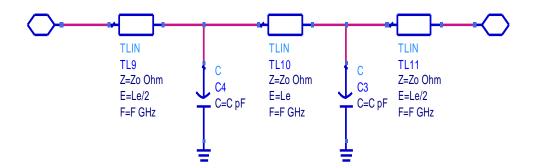

| Figure 2-1 Comparison of Ideal Phase Shifter and TTD Network.       7         Figure 2-2 General Two Port TTD Network.       8         Figure 2-3 Phase Performance of Group Delay and Phase Delay       9         Figure 2-4 Comparison of Group Delay and Phase Delay       9         Figure 2-4 Comparison of Group Delay and Phase Delay       9         Figure 2-5 Wideband PAA System Architecture       10         Figure 2-7 Varying Dielectric of a Medium       12         Figure 2-10 Arging Dielectric of a Medium       12         Figure 2-10 Cruit Representation of a Directional Coupler       13         Figure 2-10 Reflection Type TTD Network with Varying Loads       15         Figure 2-11 Betr-Smard Electrical Trombone Line Structure       17         Figure 2-13 Conventional Switched-Line TTD Network       17         Figure 2-14 Switched-Lines in a Coupler as TTD Network       17         Figure 2-15 Block Diagram of an Active PAA Transceiver       20         Figure 3-2 Comparison of SP4T and SP2T Switch Configurations for Switched-Lines       28         Figure 3-3 Representation of the Switched-Transmission Lines       30         Figure 3-4 Response of 6-Bit SP4T Switched-Transmission Lines       30         Figure 3-5 Representation of the NDL Unit Section       33         Figure 3-10 Response of the Unit Section for Loaded Reflection Lines TTD Network       32                                                                                                                                                                                                                                                                                    | FIGURES                                                                                |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|----|

| Figure 2-2 General Two Port TTD Network.       8         Figure 2-2 Comparison of Group Delay and Phase Delay       9         Figure 2-4 Comparison of Group Delay and Phase Delay       9         Figure 2-4 Comparison of Group Delay and Phase Delay       9         Figure 2-4 Varying Dielectric of a Medium       12         Figure 2-4 Varying Dielectric of a Medium       12         Figure 2-1 Varying Dielectric of a Medium       13         Figure 2-10 Reflection Type TTD Network with Varying Loads       15         Figure 2-11 Path-Shared Electrical Trombone Line Structure       16         Figure 2-12 Conventional Switched-Tine TTD Network       17         Figure 2-13 Block Diagram of an Active PAA Transceiver       20         Figure 3-12 Comparison of SP4T and SP2T Switch Configurations for Switched-Lines       28         Figure 3-2 Comparison of SP4T and SP2T Switched-Transmission Lines       30         Figure 3-3 Response of 6-Bit SP4T Switched-Reflection Lines TTD Network       31         Figure 3-4 Response of 6-Bit SP4T Switched-Reflection Lines TTD Network       32         Figure 3-5 Representation of the Switched-Reflection Lines TTD Network       32         Figure 3-6 Response of 6-Bit SystTSwitched-Reflection Lines TTD Network       32         Figure 3-10 Response of the Unit Section for Loaded Reflection Lines Network       33         Figure 3-10 Response                                                                                                                                                                                                                                                                            | Figure 2-1 Comparison of Ideal Phase Shifter and TTD Network                           | 7  |

| Figure 2-3 Phase Performance of Group Delay and Phase Delay       9         Figure 2-5 Wideband PAA System Architecture       10         Figure 2-5 Wideband PAA System Architecture       10         Figure 2-5 Varying Signal-Ground Separation       12         Figure 2-7 Varying Dielectric of a Medium       12         Figure 2-8 Varying Capacitive Loading of Transmission Line       13         Figure 2-9 Circuit Representation of a Directional Coupler       14         Figure 2-10 Reflection Type TTD Network with Varying Loads       15         Figure 2-11 Subschemetal Electrical Trombone Line Structure       16         Figure 2-12 Subschemetal Electrical Trombone Line Structure       17         Figure 2-13 Conventional Switched-Line TTD Network       17         Figure 2-14 Switched-Lines in a Coupler as TTD Network       17         Figure 2-15 Block Diagram of an Active PAA Transceiver       20         Figure 3-1 TTD Design Flow Chart       25         Figure 3-3 Response of 6-Bit SPDT Switched-Transmission Lines       39         Figure 3-4 Response of 6-Bit SPDT Switched-Reflection Lines TTD Network       31         Figure 3-7 Sample Layout of 4-bit Switched-Reflection Lines TTD Network       32         Figure 3-8 Simple Representation of the NulLU unit Section       33         Figure 3-10 Response of 6-Bit APF TTD Network       35                                                                                                                                                                                                                                                                                                               |                                                                                        |    |

| Figure 2-4 Comparison of Group Delay and Phase Delay       9         Figure 2-5 Wideband PAA System Architecture       10         Figure 2-6 Varying Signal-Ground Separation       12         Figure 2-7 Varying Dielectric of a Medium       12         Figure 2-7 Varying Dielectric of a Medium       12         Figure 2-8 Varying Capacitive Loading of Transmission Line       13         Figure 2-10 Reflection Type TTD Network with Varying Loads       15         Figure 2-11 Path-Shared Electrical Trombone Line Structure       16         Figure 2-12 Electromechanical Trombone Line Structure       17         Figure 2-13 Conventional Switched–Line TTD Network       17         Figure 2-14 Switched–Lines in a Coupler as TTD Network       18         Figure 3-1 TTD Design Flow Chart       25         Figure 3-1 TTD Design Flow Chart       25         Figure 3-2 Comparison of SP4T and SP2T Switch Configurations for Switched-Lines       28         Figure 3-3 Response of 6-Bit SP1T Switched-Reflection Lines TTD Network       31         Figure 3-4 Response of 6-Bit Switched-Reflection Lines TTD Network       32         Figure 3-7 Sample Layout of 4-bit Switched-Reflection Lines TD Network       32         Figure 3-10 Response of the Unit Section for Loaded Reflection Lines Network       33         Figure 3-11 Delay Response of the Unit Section for Loaded Reflection Lines Network <td></td> <td></td>                                                                                                                                                                                                                                                          |                                                                                        |    |

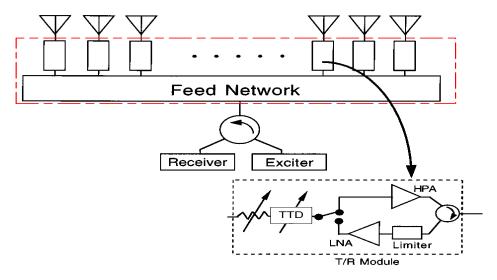

| Figure 2-5 Wideband PAA System Architecture       10         Figure 2-7 Varying Digloal-Ground Separation       12         Figure 2-7 Varying Dielectric of a Medium       12         Figure 2-7 Varying Dielectric of a Medium       13         Figure 2-10 Reflection Type TTD Network with Varying Loads       15         Figure 2-11 Path-Shared Electrical Trombone Line Structure       16         Figure 2-12 Electromechanical Trombone Line Structure       17         Figure 2-13 Conventional System Archive PAA Transceiver       20         Figure 2-14 Switched-Lines in a Coupler as TTD Network       17         Figure 2-15 Block Diagram of an Active PAA Transceiver       20         Figure 3-1 TTD Design Flow Chart       25         Figure 3-3 Response of 6-Bit SPDT Switched-Transmission Lines       29         Figure 3-4 Response of 6-Bit SPAT Switched-Reflection Lines TTD Network       31         Figure 3-5 Representation of the Switched-Reflection Lines TTD Network       32         Figure 3-7 Sample Layout of 4-bit Switched-Reflection Lines TTD Network       32         Figure 3-10 Response of the Unit Section for Loaded Reflection Lines Network       33         Figure 3-10 Response of the Loaded Reflection Lines Network       35         Figure 3-11 Delay Response of the Loaded Reflection Lines Network       35         Figure 3-12 Nodified T-Section Coupled Inductors for 2 <sup></sup>                                                                                                                                                                                                                                                                |                                                                                        |    |

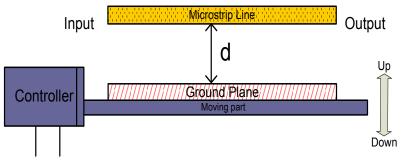

| Figure 2-6 Varying Signal-Ground Separation       12         Figure 2-7 Varying Dielectric of a Medium       12         Figure 2-8 Varying Capacitive Loading of Transmission Line       13         Figure 2-9 Circuit Representation of a Directional Coupler       14         Figure 2-10 Reflection Type TTD Network with Varying Loads       15         Figure 2-11 Path-Shared Electrical Trombone Line Structure       16         Figure 2-12 Electromechanical Trombone Line Structure       17         Figure 2-13 Conventional Switched-Line TD Network       17         Figure 3-1 TD Design Flow Chart       20         Figure 3-1 TD Design Flow Chart       25         Figure 3-2 Comparison of SP4T and SP2T Switch Configurations for Switched-Lines       28         Figure 3-3 Response of 6-Bit SPDT Switched-Transmission Lines       20         Figure 3-4 Response of 6-Bit SWitched-Reflection Lines TD Network       31         Figure 3-5 Representation of the Switched-Reflection Lines TD Network       32         Figure 3-7 Sample Layout of 4-bit Switched-Reflection Lines TD Network       32         Figure 3-11 Delay Response of the Unit Section for Loaded Reflection Lines Network       33         Figure 3-13 Modified T-Section Coupled Inductors for 1 <sup>ed</sup> order APF Network       35         Figure 3-14 The Response of the Unit Cell for APF Network       36         Figure 3-15 The Respon                                                                                                                                                                                                                                                                 |                                                                                        |    |

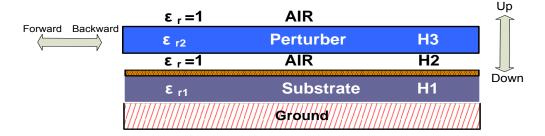

| Figure 2-7 Varying Dielectric of a Medium12Figure 2-8 Varying Capacitive Loading of Transmission Line13Figure 2-9 Circuit Representation of a Directional Coupler14Figure 2-10 Reflection Type TTD Network with Varying Loads15Figure 2-11 Path-Shared Electrical Trombone Line Structure16Figure 2-12 Electromechanical Tombone Line Structure17Figure 2-13 Conventional Switched-Line TTD Network18Figure 2-14 Switched-Lines in a Coupler as TTD Network18Figure 2-15 Block Diagram of an Active PAA Transceiver20Figure 3-2 Comparison of SP4T and SP2T Switch Configurations for Switched-Lines28Figure 3-3 Response of 6-Bit SP4T Switched-Transmission Lines29Figure 3-4 Response of 6-Bit SP4T Switched-Transmission Lines30Figure 3-5 Representation of the Switched-Reflection Lines TTD Network31Figure 3-6 Response of 6-Bit SP4T Switched-Reflection Lines TTD Network32Figure 3-7 Sample Layout of 4-bit Switched-Reflection Lines TTD Network32Figure 3-8 Simple Representation of the NLDL Unit Section33Figure 3-10 Response of the Unit Section for Loaded Reflection Lines Network34Figure 3-13 Modified T-Section Coupled Inductors for 2 <sup>nd</sup> order APF Network35Figure 3-15 The Response of the Unit Cell for APF Network36Figure 3-15 The Response of G-Bit SP11 Switched-Transmission Lines Network41Figure 3-15 The Response of G-Bit SP11 Switched 2 <sup>nd</sup> order APF Network36Figure 3-15 The Response of He Unit Cell for APF Network36Figure 3-15 The Response of G                                                                                                                                                                                                    |                                                                                        |    |

| Figure 2-8 Varying Capacitive Loading of Transmission Line       13         Figure 2-9 Circuit Representation of a Directional Coupler       14         Figure 2-10 Reflection Type TTD Network with Varying Loads.       15         Figure 2-11 Path-Shared Electrical Trombone Line Structure       17         Figure 2-12 Electromechanical Trombone Line Structure       17         Figure 2-14 Switched-Lines in a Coupler as TTD Network       17         Figure 2-15 Block Diagram of an Active PAA Transceiver       20         Figure 3-1 TTD Design Flow Chart       25         Figure 3-3 Response of 6-Bit SPDT Switched-Transmission Lines       29         Figure 3-5 Representation of the Switched-Reflection Lines TTD Network       31         Figure 3-7 Sample Layout of 4-bit Switched-Reflection Lines TTD Network       32         Figure 3-7 Sample Layout of 4-bit Switched-Reflection Lines TTD Network       32         Figure 3-10 Response of 6-Bit Periodically Loaded Lines TTD Network       32         Figure 3-11 Delay Response of the Unit Section for Loaded Reflection Lines Network       33         Figure 3-12 T-Section Coupled Inductors for 1 <sup>nd</sup> order APF Network       35         Figure 3-14 The Response of the Unit Section for Loaded Reflection Lines Network       36         Figure 3-14 The Response of G-Bit APF TTD Network       36         Figure 3-14 The Response of the Unit Cell for APF Network       <                                                                                                                                                                                                                                   |                                                                                        |    |

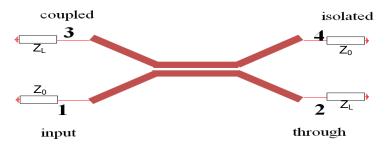

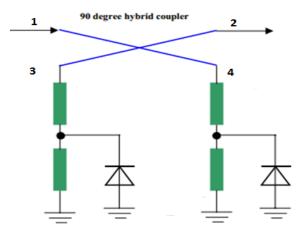

| Figure 2-9 Circuit Representation of a Directional Coupler14Figure 2-10 Reflection Type TTD Network with Varying Loads15Figure 2-11 Path-Shared Electrical Trombone Line Structure16Figure 2-13 Conventional Switched-Line TTD Network17Figure 2-13 Conventional Switched-Line TTD Network17Figure 2-15 Block Diagram of an Active PAA Transceiver20Figure 3-1 TTD Design Flow Chart25Figure 3-2 Comparison of SP4T and SP2T Switch Configurations for Switched-Lines28Figure 3-3 Representation of the Switched-Transmission Lines29Figure 3-4 Response of 6-Bit SPDT Switched-Transmission Lines30Figure 3-5 Representation of the Switched-Reflection Lines TTD Network31Figure 3-6 Response of 6-Bit Switched-Reflection Lines TTD Network32Figure 3-7 Sample Layout of 4-bit Switched-Reflection Lines TTD Network32Figure 3-8 Simple Representation of the NLDL Unit Section33Figure 3-10 Response of 6-Bit Periodically Loaded Lines TTD Network34Figure 3-11 Delay Response of the Unit Section for Loaded Reflection Lines Network35Figure 3-12 T-Section Coupled Inductors for 1 <sup>st</sup> order APF Network35Figure 3-13 Modified T-Section Coupled Inductors for 1 <sup>st</sup> order APF Network36Figure 3-14 The Response of the Self-Switched Pathed-Transmission Lines Network34Figure 3-13 Potters of Switch Isolation for Switched-Transmission Lines Network36Figure 3-14 The Response of the Unit Section for Loaded Reflection Lines Network35Figure 3-15 The Response of G-Bit APF TD Network36 <td></td> <td></td>                                                                                                                                                                      |                                                                                        |    |

| Figure 2-10 Reflection Type TTD Network with Varying Loads.15Figure 2-11 Path-Shared Electrical Trombone Line Structure16Figure 2-12 Conventional Switched–Line TTD Network17Figure 2-13 Conventional Switched–Line TTD Network17Figure 2-14 Switched–Lines in a Coupler as TTD Network18Figure 2-15 Block Diagram of an Active PAA Transceiver20Figure 3-1 TTD Design Flow Chart25Figure 3-2 Comparison of SP4T and SP2T Switch Configurations for Switched-Lines28Figure 3-3 Response of 6-Bit SPDT Switched-Transmission Lines29Figure 3-4 Response of 6-Bit SPDT Switched-Transmission Lines30Figure 3-5 Representation of the Switched-Reflection Lines TTD Network31Figure 3-7 Sample Layout of 4-bit Switched-Reflection Lines TTD Network32Figure 3-8 Simple Representation of the NLDL Unit Section33Figure 3-10 Response of 6-Bit Periodically Loaded Lines TTD Network33Figure 3-11 Delay Response of the Unit Section for Loaded Reflection Lines Network34Figure 3-12 T-Section Coupled Inductors for 2 <sup>nd</sup> order APF Network35Figure 3-13 Modified T-Section Coupled Inductors for 2 <sup>nd</sup> order APF Network37Figure 3-14 The Response of G-Bit Switched 2 <sup>nd</sup> order APF Network37Figure 3-15 The Response of G-Bit APF TD Network37Figure 3-16 The Schematic of the Self-Switched 2 <sup>nd</sup> order APF Network37Figure 3-17 The Effects of Switch Isolation for Switched-Transmission Lines Network34Figure 3-18 Pin Descriptions and Truth Table for HMC241LP3 and SKY13384-350LF.42 <td< td=""><td></td><td></td></td<>                                                                                                                                           |                                                                                        |    |

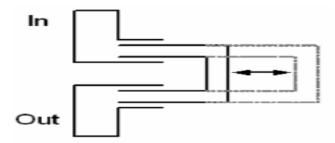

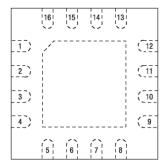

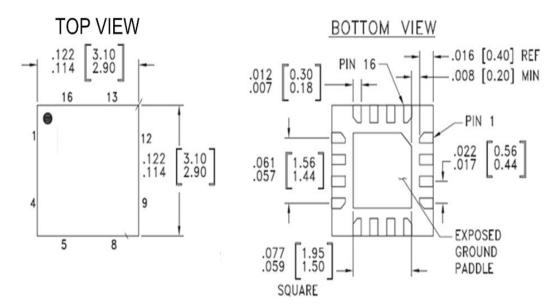

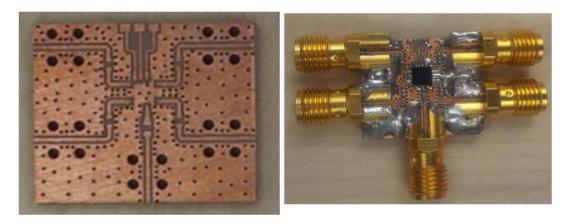

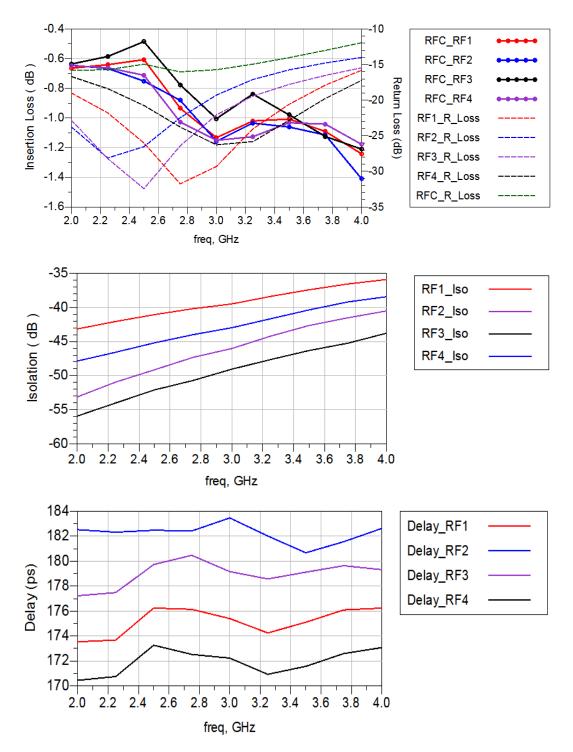

| Figure 2-11 Path-Shared Electrical Trombone Line Structure16Figure 2-12 Electromechanical Trombone Line Structure17Figure 2-13 Conventional Switched–Line TTD Network17Figure 2-14 Switched–Lines in a Coupler as TTD Network18Figure 2-15 Block Diagram of an Active PAA Transceiver20Figure 3-1 TTD Design Flow Chart25Figure 3-2 Comparison of SP4T and SP2T Switch Configurations for Switched-Lines28Figure 3-3 Response of 6-Bit SPDT Switched-Transmission Lines29Figure 3-4 Response of 6-Bit SPT Switched-Reflection Lines TTD Network31Figure 3-5 Representation of the Switched-Reflection Lines TTD Network32Figure 3-7 Sample Layout of 4-bit Switched-Reflection Lines TTD Network32Figure 3-7 Sample Layout of 4-bit Switched-Reflection Lines TTD Network33Figure 3-9 Response of 6-Bit Periodically Loaded Lines TTD Network33Figure 3-10 Response of the Unit Section for Loaded Reflection Lines Network35Figure 3-11 Delay Response of the Loaded Reflection Lines Network35Figure 3-13 Modified T-Section Coupled Inductors for 2 <sup>nd</sup> order APF Network36Figure 3-15 The Response of 6-Bit APF TTD Network37Figure 3-15 The Response of 6-Bit APF TTD Network38Figure 3-16 The Schematic of the Self-Switched 2 <sup>nd</sup> order APF Network41Figure 3-17 The Effects of Switch Isolation for Switched-Transmission Lines Network41Figure 3-18 Pin Descriptions and Truth Table for HMC241LP3 and SKY13384-350LF.42Figure 3-19 Outline Drawings of QFN (16pin, 3x3mm) Package [Dimensions in mm]                                                                                                                                                                                  |                                                                                        |    |

| Figure 2-12 Electromechanical Trombone Line Structure17Figure 2-13 Conventional Switched–Line TD Network17Figure 2-14 Switched–Lines in a Coupler as TD Network18Figure 2-15 Block Diagram of an Active PAA Transceiver20Figure 3-1 TTD Design Flow Chart25Figure 3-2 Comparison of SP4T and SP2T Switch Configurations for Switched-Lines28Figure 3-3 Response of 6-Bit SPDT Switched-Transmission Lines29Figure 3-4 Response of 6-Bit SPAT Switched-Reflection Lines TTD Network31Figure 3-6 Response of 6-Bit SWitched-Reflection Lines TTD Network32Figure 3-7 Sample Layout of 4-bit Switched-Reflection Lines TTD Network32Figure 3-9 Response of 6-Bit Periodically Loaded Lines TTD Network33Figure 3-9 Response of 6-Bit Periodically Loaded Lines TD Network33Figure 3-10 Response of the Unit Section for Loaded Reflection Lines Network34Figure 3-11 Delay Response of the Londed Reflection Lines Network35Figure 3-12 T-Section Coupled Inductors for 1 <sup>ed</sup> order APF Network36Figure 3-14 The Response of G-Bit APF TTD Network37Figure 3-15 The Response of G-Bit APF TTD Network37Figure 3-16 The Schematic of the Self-Switched 2 <sup>nd</sup> order APF Network37Figure 3-17 The Effects of Switch Isolation for Switched-Transmission Lines Network41Figure 3-18 Pin Descriptions and Truth Table for HMC241LP3 and SKY13384-350LF42Figure 3-21 Measurements of SKY13384-350LF on RO321044Figure 3-22 Measurements of SHAT 30 ARD321045Figure 3-24 Off-Path Resonance Forbidden                                                                                                                                                                                                     |                                                                                        |    |

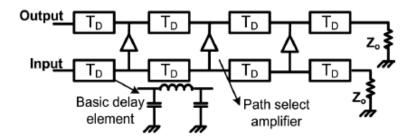

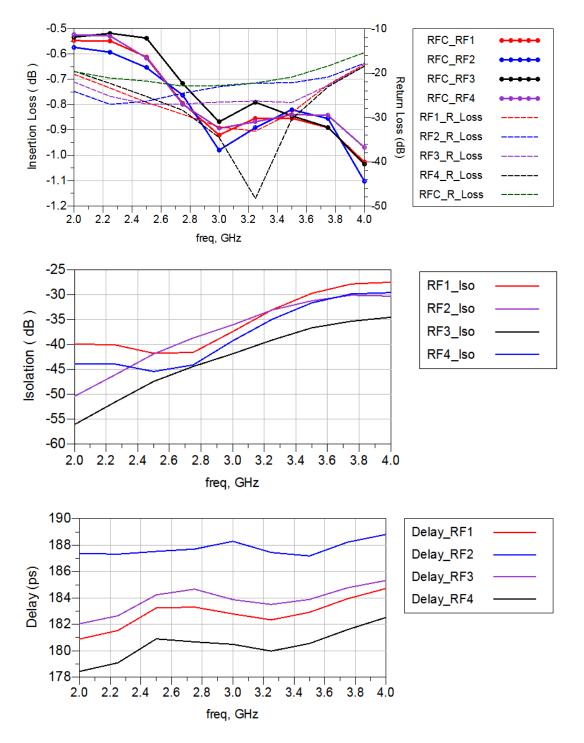

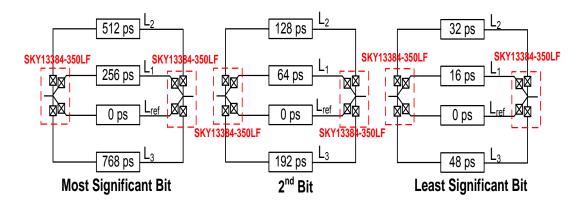

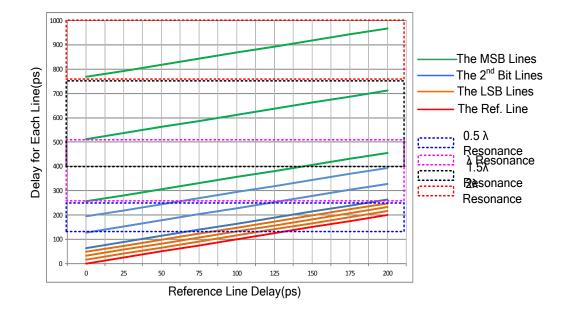

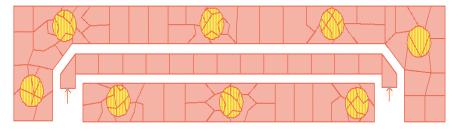

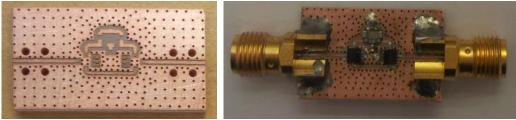

| Figure 2-13 Conventional Switched–Line TTD Network17Figure 2-14 Switched–Lines in a Coupler as TTD Network.18Figure 2-15 Block Diagram of an Active PAA Transceiver20Figure 3-1 TTD Design Flow Chart25Figure 3-2 Comparison of SP4T and SP2T Switch Configurations for Switched-Lines28Figure 3-3 Response of 6-Bit SPDT Switched-Transmission Lines29Figure 3-4 Response of 6-Bit SPAT Switched-Transmission Lines29Figure 3-5 Representation of the Switched-Reflection Lines TTD Network31Figure 3-6 Response of 6-Bit Switched-Reflection Lines TTD Network32Figure 3-7 Sample Layout of 4-bit Switched-Reflection Lines TTD Network32Figure 3-8 Simple Representation of the NLDL Unit Section33Figure 3-10 Response of the Unit Section for Loaded Reflection Lines Network34Figure 3-11 Delay Response of the Loaded Reflection Lines Network35Figure 3-12 T-Section Coupled Inductors for 1 <sup>rd</sup> order APF Network35Figure 3-13 Modified T-Section Coupled Inductors for 2 <sup>nd</sup> order APF Network37Figure 3-15 The Response of the Unit Cell for APF Network37Figure 3-16 The Schematic of the Self-Switched 2 <sup>nd</sup> order APF Circuit.39Figure 3-17 The Effects of Switch Isolation for Switched-Transmission Lines Network41Figure 3-20 RO3210 Demo-Board for SP4T Switch Measurements43Figure 3-21 Measurements of MKC13384-350LF on RO321044Figure 3-22 Measurements of HMC241LP3 on RO321044Figure 3-24 Off-Path Resonance Forbidden Zones for the Reference Lines of SP4T47Figure                                                                                                                                                                                          |                                                                                        |    |

| Figure 2-14 Switched–Lines in a Coupler as TTD Network.18Figure 2-15 Block Diagram of an Active PAA Transceiver20Figure 3-1 TTD Design Flow Chart25Figure 3-2 Comparison of SP4T and SP2T Switch Configurations for Switched-Lines28Figure 3-3 Response of 6-Bit SPDT Switched-Transmission Lines29Figure 3-4 Response of 6-Bit SP4T Switched-Transmission Lines30Figure 3-5 Representation of the Switched-Reflection Lines TTD Network.31Figure 3-6 Response of 6-Bit Switched-Reflection Lines TTD Network.32Figure 3-7 Sample Layout of 4-bit Switched-Reflection Lines TTD Network.32Figure 3-9 Response of 6-Bit Periodically Loaded Lines TTD Network.33Figure 3-10 Response of the Unit Section for Loaded Reflection Lines Network34Figure 3-11 Delay Response of the Unit Section for Cloaded Reflection Lines Network35Figure 3-12 T-Section Coupled Inductors for 2 <sup>nd</sup> order APF Network.35Figure 3-13 Modified T-Section Coupled Inductors for 2 <sup>nd</sup> order APF Network37Figure 3-15 The Response of G-Bit APF TD Network38Figure 3-16 The Schematic of the Self-Switched 2 <sup>nd</sup> order APF Circuit.39Figure 3-17 The Effects of Switch Isolation for Switched-Transmission Lines Network41Figure 3-20 RO3210 Demo-Board for SP4T Switched Areansmission Lines Network41Figure 3-21 Measurements of SKY13384-350LF on RO321044Figure 3-22 Measurements of HMC241LP3 on RO321044Figure 3-23 The Schematic of the Self-Switched-Transmission Lines TTD Network46Figure 3-24 Off-Path Resonace Forbidden Zones                                                                                                                                                                |                                                                                        |    |

| Figure 2-15 Block Diagram of an Active PAA Transceiver20Figure 3-1 TTD Design Flow Chart25Figure 3-2 Comparison of SP4T and SP2T Switch Configurations for Switched-Lines28Figure 3-3 Response of 6-Bit SP1T Switched-Transmission Lines30Figure 3-5 Representation of the Switched-Reflection Lines TTD Network31Figure 3-6 Response of 6-Bit Switched-Reflection Lines TTD Network32Figure 3-7 Sample Layout of 4-bit Switched-Reflection Lines TTD Network32Figure 3-8 Simple Representation of the NLDL Unit Section33Figure 3-9 Response of 6-Bit Periodically Loaded Lines TTD Network33Figure 3-10 Response of the Unit Section for Loaded Reflection Lines Network35Figure 3-11 Delay Response of the Loaded Reflection Lines Network35Figure 3-12 T-Section Coupled Inductors for 1 <sup>st</sup> order APF Network36Figure 3-13 Modified T-Section Coupled Inductors for 2 <sup>nd</sup> order APF Network37Figure 3-15 The Response of 6-Bit APF TTD Network38Figure 3-16 The Schematic of the Self-Switched 2 <sup>nd</sup> order APF Circuit39Figure 3-17 The Effects of Switch Isolation for Switched-Transmission Lines Network41Figure 3-20 RO3210 Demo-Board for SPAT Switch Measurements43Figure 3-21 Measurements of SKY13384-350LF42Figure 3-22 Layout of the Reference Line for the 1 <sup>st</sup> Bit48Figure 3-24 Off-Path Resonance Forbidden Zones for the Reference Lines of SPAT47Figure 3-25 Layout of the Reference Line for the 1 <sup>st</sup> Bit49Figure 3-26 EM Results of L <sub>1</sub> for the 1 <sup>st</sup> Bit49Figure 3                                                                                                                                                  |                                                                                        |    |

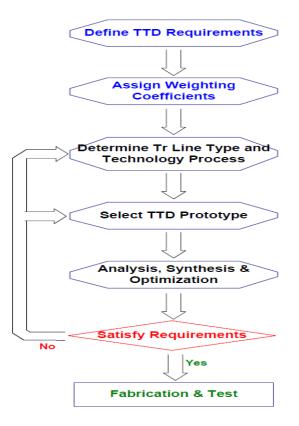

| Figure 3-1 TTD Design Flow Chart25Figure 3-2 Comparison of SP4T and SP2T Switch Configurations for Switched-Lines.28Figure 3-3 Response of 6-Bit SPDT Switched-Transmission Lines.29Figure 3-4 Response of 6-Bit SP4T Switched-Reflection Lines TTD Network.30Figure 3-5 Representation of the Switched-Reflection Lines TTD Network.32Figure 3-6 Response of 6-Bit Switched-Reflection Lines TTD Network.32Figure 3-7 Sample Layout of 4-bit Switched-Reflection Lines TTD Network.32Figure 3-8 Simple Representation of the NLDL Unit Section33Figure 3-10 Response of 6-Bit Periodically Loaded Lines TTD Network.33Figure 3-11 Delay Response of the Unit Section for Loaded Reflection Lines Network35Figure 3-12 T-Section Coupled Inductors for 1 <sup>st</sup> order APF Network.35Figure 3-13 Modified T-Section Coupled Inductors for 2 <sup>nd</sup> order APF Network37Figure 3-14 The Response of 6-Bit APF TD Network37Figure 3-15 The Response of 6-Bit Switched 2 <sup>nd</sup> order APF Network37Figure 3-16 The Schematic of the Self-Switched 2 <sup>nd</sup> order APF Network37Figure 3-17 The Effects of Switch Isolation for Switched-Transmission Lines Network41Figure 3-19 Dutine Drawings of QFN (16pin, 3x3mm) Package [Dimensions in mm]43Figure 3-20 RO3210 Demo-Board for SP4T Switch Measurements43Figure 3-21 Measurements of SKY13384-350LF on RO321044Figure 3-22 Apout of the Lift or the 1 <sup>st</sup> Bit48Figure 3-24 Off-Path Resonance Forbidden Zones for the Reference Lines of SP4T47Figure 3-25 Layout of the Reference L                                                                                                                                           |                                                                                        |    |

| Figure 3-2 Comparison of SP4T and SP2T Switch Configurations for Switched-Lines.28Figure 3-3 Response of 6-Bit SPDT Switched-Transmission Lines.29Figure 3-4 Response of 6-Bit SP4T Switched-Transmission Lines30Figure 3-5 Representation of the Switched-Reflection Lines TTD Network.31Figure 3-6 Response of 6-Bit Switched-Reflection Lines TTD Network.32Figure 3-7 Sample Layout of 4-bit Switched-Reflection Lines TTD Network.32Figure 3-8 Simple Representation of the NLDL Unit Section33Figure 3-10 Response of 6-Bit Periodically Loaded Lines TTD Network.34Figure 3-11 Delay Response of the Unit Section for Loaded Reflection Lines Network35Figure 3-11 Delay Response of the Unit Cell for APF Network35Figure 3-13 Modified T-Section Coupled Inductors for 2 <sup>nd</sup> order APF Network36Figure 3-14 The Response of the Self-Switched 2 <sup>nd</sup> order APF Network37Figure 3-15 The Response of 6-Bit APF TTD Network37Figure 3-16 The Schematic of the Self-Switched 2 <sup>nd</sup> order APF Circuit39Figure 3-17 The Effects of Switch Isolation for Switched-Transmission Lines Network41Figure 3-18 Pin Descriptions and Truth Table for HMC241LP3 and SKY13384-350LF.42Figure 3-20 RO3210 Demo-Board for SP4T Switch Reasurements43Figure 3-21 Measurements of SKY13384-350LF on RO321044Figure 3-22 Measurements of HMC241LP3 on RO321044Figure 3-24 Off-Path Resonance Forbidden Zones for the Reference Lines of SP4T47Figure 3-25 Layout of the Reference Line for the 1 <sup>st</sup> Bit49Figure 3-26 EM Results o                                                                                                                                                     |                                                                                        |    |

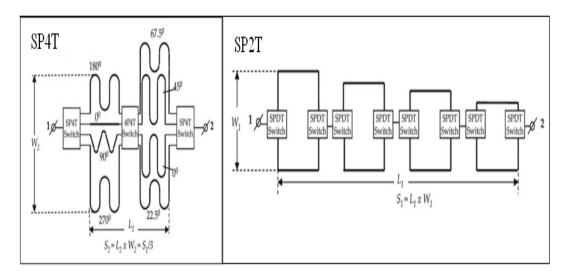

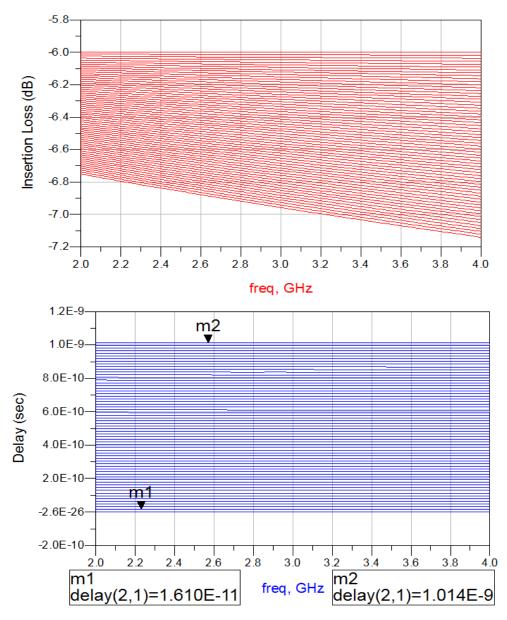

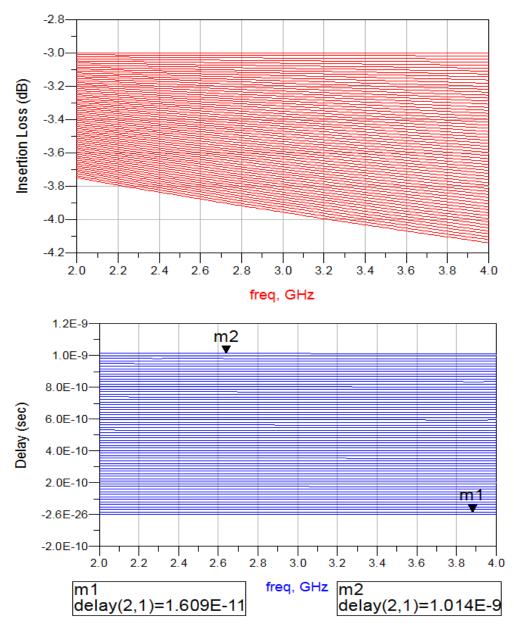

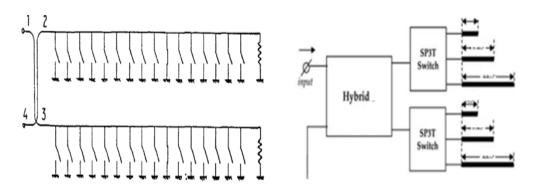

| Figure 3-3 Response of 6-Bit SPDT Switched-Transmission Lines29Figure 3-4 Response of 6-Bit SP4T Switched-Reflection Lines TTD Network31Figure 3-5 Representation of the Switched-Reflection Lines TTD Network32Figure 3-7 Sample Layout of 4-bit Switched-Reflection Lines TTD Network32Figure 3-8 Simple Representation of the NLDL Unit Section33Figure 3-9 Response of 6-Bit Periodically Loaded Lines TTD Network33Figure 3-10 Response of the Unit Section for Loaded Reflection Lines Network34Figure 3-11 Delay Response of the Loaded Reflection Lines Network35Figure 3-12 T-Section Coupled Inductors for 2 <sup>nd</sup> order APF Network35Figure 3-13 Modified T-Section Coupled Inductors for 2 <sup>nd</sup> order APF Network37Figure 3-14 The Response of the Unit Cell for APF Network37Figure 3-15 The Response of 6-Bit APF TTD Network38Figure 3-16 The Schematic of the Self-Switched 2 <sup>nd</sup> order APF Circuit39Figure 3-17 The Effects of Switch Isolation for Switched-Transmission Lines Network41Figure 3-19 Outline Drawings of QFN (16pin, 3x3mm) Package [Dimensions in mm]43Figure 3-21 Measurements of SKY13384-350LF on RO321044Figure 3-22 Measurements of HMC241LP3 on RO321044Figure 3-24 Coff-Path Resonance Forbidden Zones for the Reference Lines of SP4T47Figure 3-25 Layout of the Reference Line for the 1 <sup>st</sup> Bit48Figure 3-26 EM Results of L <sub>1</sub> for the 1 <sup>st</sup> Bit49Figure 3-29 Layout of the L <sub>2</sub> for the 1 <sup>st</sup> Bit50Figure 3-20 EM Results of L <sub>2</sub> for the 1 <sup>st</sup> Bit50                                                                                                                | Figure 3-2 Comparison of SP4T and SP2T Switch Configurations for Switched-Lines        | 28 |

| Figure 3-4 Response of 6-Bit SP4T Switched-Transmission Lines30Figure 3-5 Representation of the Switched-Reflection Lines TTD Network.31Figure 3-6 Response of 6-Bit Switched-Reflection Lines TTD Network.32Figure 3-7 Sample Layout of 4-bit Switched-Reflection Lines TTD Network.33Figure 3-8 Simple Representation of the NLDL Unit Section33Figure 3-10 Response of 6-Bit Periodically Loaded Lines TTD Network.34Figure 3-10 Response of the Unit Section for Loaded Reflection Lines Network34Figure 3-11 Delay Response of the Loaded Reflection Lines Network35Figure 3-12 T-Section Coupled Inductors for 1 <sup>st</sup> order APF Network.35Figure 3-13 Modified T-Section Coupled Inductors for 2 <sup>nd</sup> order APF Network36Figure 3-15 The Response of the Unit Cell for APF Network37Figure 3-16 The Schematic of the Self-Switched 2 <sup>nd</sup> order APF Circuit.39Figure 3-17 The Effects of Switch Isolation for Switched-Transmission Lines Network41Figure 3-19 Outline Drawings of QFN (16pin, 3x3mm) Package [Dimensions in mm].43Figure 3-21 Measurements of SKY13384-350LF.42Figure 3-22 Measurements of HMC241LP3 on RO321044Figure 3-23 The Schematic of Hom C241LP3 on RO321044Figure 3-24 Off-Path Resonance Forbidden Zones for the Reference Lines of SP4T47Figure 3-24 Layout of the L <sub>1</sub> for the 1 <sup>st</sup> Bit.48Figure 3-24 EM Results of L <sub>1</sub> for the 1 <sup>st</sup> Bit.49Figure 3-28 EM Results of L <sub>1</sub> for the 1 <sup>st</sup> Bit.49Figure 3-29 Layout of the L <sub>2</sub> for the 1 <sup>st</sup> Bit.50Figure 3                                                                                                          |                                                                                        |    |

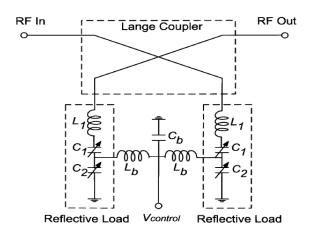

| Figure 3-5 Representation of the Switched-Reflection Lines TTD Network.31Figure 3-6 Response of 6-Bit Switched-Reflection Lines TTD Network.32Figure 3-7 Sample Layout of 4-bit Switched-Reflection Lines TTD Network.32Figure 3-8 Simple Representation of the NLDL Unit Section33Figure 3-9 Response of 6-Bit Periodically Loaded Lines TTD Network.33Figure 3-10 Response of the Unit Section for Loaded Reflection Lines Network34Figure 3-11 Delay Response of the Loaded Reflection Lines Network35Figure 3-12 T-Section Coupled Inductors for 1 <sup>st</sup> order APF Network.35Figure 3-13 Modified T-Section Coupled Inductors for 2 <sup>nd</sup> order APF Network36Figure 3-14 The Response of the Unit Cell for APF Network37Figure 3-15 The Response of 6-Bit APF TTD Network38Figure 3-16 The Schematic of the Self-Switched 2 <sup>nd</sup> order APF Circuit39Figure 3-17 The Effects of Switch Isolation for Switched-Transmission Lines Network41Figure 3-19 Outline Drawings of QFN (16pin, 3x3mm) Package [Dimensions in mm]43Figure 3-20 RO3210 Demo-Board for SP4T Switch Measurements43Figure 3-21 Measurements of SKY13384-350LF on RO321044Figure 3-22 Measurements of Forbidden Zones for the Reference Lines of SP4T47Figure 3-24 Off-Path Resonance Forbidden Zones for the Reference Lines of SP4T47Figure 3-25 Layout of the Reference Line for the 1 <sup>st</sup> Bit48Figure 3-26 EM Results of L <sub>1</sub> for the 1 <sup>st</sup> Bit49Figure 3-28 EM Results of L <sub>2</sub> for the 1 <sup>st</sup> Bit50Figure 3-31 Layout of the L <sub>2</sub> for the 1 <sup>st</sup> Bit<                                                                                         |                                                                                        |    |

| Figure 3-6 Response of 6-Bit Switched-Reflection Lines TTD Network.32Figure 3-7 Sample Layout of 4-bit Switched-Reflection Lines TTD Network.32Figure 3-8 Simple Representation of the NLDL Unit Section33Figure 3-9 Response of 6-Bit Periodically Loaded Lines TTD Network.33Figure 3-10 Response of the Unit Section for Loaded Reflection Lines Network34Figure 3-11 Delay Response of the Loaded Reflection Lines Network35Figure 3-12 T-Section Coupled Inductors for 1 <sup>st</sup> order APF Network.35Figure 3-13 Modified T-Section Coupled Inductors for 2 <sup>nd</sup> order APF Network37Figure 3-14 The Response of the Unit Cell for APF Network37Figure 3-15 The Response of 6-Bit APF TTD Network38Figure 3-16 The Schematic of the Self-Switched 2 <sup>nd</sup> order APF Circuit39Figure 3-17 The Effects of Switch Isolation for Switched-Transmission Lines Network41Figure 3-19 Outline Drawings of QFN (16pin, 3x3mm) Package [Dimensions in mm]43Figure 3-21 Measurements of SKY13384-350LF on R0321044Figure 3-22 Measurements of SKY13384-350LF on R0321044Figure 3-24 Off-Path Resonance Forbidden Zones for the Reference Lines of SP4T47Figure 3-25 Layout of the Reference Line for the 1 <sup>st</sup> Bit48Figure 3-26 EM Results of L <sub>1</sub> for the 1 <sup>st</sup> Bit49Figure 3-28 EM Results of L <sub>1</sub> for the 1 <sup>st</sup> Bit50Figure 3-30 EM Results of L <sub>2</sub> for the 1 <sup>st</sup> Bit50Figure 3-31 Layout of the L <sub>2</sub> for the 1 <sup>st</sup> Bit50Figure 3-32 EM Results of L <sub>2</sub> for the 1 <sup>st</sup> Bit50 <tr <tr="">Figure 3-32 EM Resul</tr>                                                                   |                                                                                        |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                        |    |

| Figure 3-7 Sample Layout of 4-bit Switched-Reflection Lines TTD Network.32Figure 3-8 Simple Representation of the NLDL Unit Section33Figure 3-9 Response of 6-Bit Periodically Loaded Lines TTD Network.33Figure 3-10 Response of the Unit Section for Loaded Reflection Lines Network34Figure 3-11 Delay Response of the Loaded Reflection Lines Network.35Figure 3-12 T-Section Coupled Inductors for 1 <sup>st</sup> order APF Network.35Figure 3-13 Modified T-Section Coupled Inductors for 2 <sup>nd</sup> order APF Network.36Figure 3-14 The Response of the Unit Cell for APF Network37Figure 3-15 The Response of 6-Bit APF TTD Network38Figure 3-16 The Schematic of the Self-Switched 2 <sup>nd</sup> order APF Circuit.39Figure 3-17 The Effects of Switch Isolation for Switched-Transmission Lines Network41Figure 3-19 Outline Drawings of QFN (16pin, 3x3mm) Package [Dimensions in mm]43Figure 3-20 RO3210 Demo-Board for SP4T Switch Measurements43Figure 3-23 The Schematic of 6-Bits Switched-Transmission Lines TTD Network46Figure 3-24 Off-Path Resonance Forbidden Zones for the Reference Lines of SP4T47Figure 3-23 The Schematic of 6-Bits Switched-Transmission Lines TTD Network46Figure 3-24 Off-Path Resonance Forbidden Zones for the Reference Lines of SP4T47Figure 3-24 Off-Path Resonance Forbidden Zones for the Reference Lines of SP4T47Figure 3-25 Layout of the Reference Line for the 1 <sup>st</sup> Bit48Figure 3-26 EM Results of L <sub>1</sub> for the 1 <sup>st</sup> Bit49Figure 3-27 Layout of the L <sub>2</sub> for the 1 <sup>st</sup> Bit50Figur                                                                                                             |                                                                                        |    |

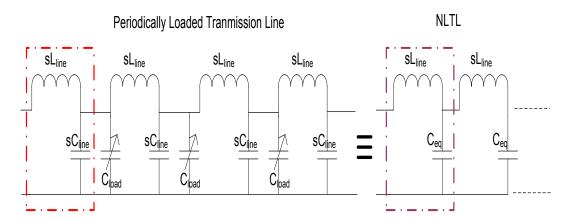

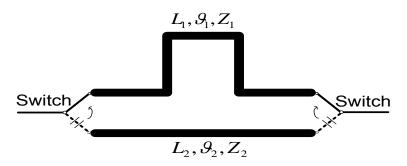

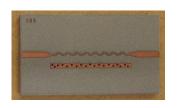

| Figure 3-8 Simple Representation of the NLDL Unit Section33Figure 3-9 Response of 6-Bit Periodically Loaded Lines TTD Network33Figure 3-10 Response of the Unit Section for Loaded Reflection Lines Network34Figure 3-11 Delay Response of the Loaded Reflection Lines Network35Figure 3-12 T-Section Coupled Inductors for 1 <sup>st</sup> order APF Network35Figure 3-13 Modified T-Section Coupled Inductors for 2 <sup>nd</sup> order APF Network36Figure 3-14 The Response of the Unit Cell for APF Network37Figure 3-15 The Response of 6-Bit APF TTD Network38Figure 3-16 The Schematic of the Self-Switched 2 <sup>nd</sup> order APF Circuit39Figure 3-17 The Effects of Switch Isolation for Switched-Transmission Lines Network41Figure 3-19 Outline Drawings of QFN (16pin, 3x3mm) Package [Dimensions in mm]43Figure 3-20 RO3210 Demo-Board for SP4T Switch Measurements43Figure 3-22 Measurements of SKY13384-350LF on RO321044Figure 3-23 The Schematic of 6-Bits Switched-Transmission Lines TD Network46Figure 3-24 Off-Path Resonance Forbidden Zones for the Reference Lines of SP4T47Figure 3-25 Layout of the Reference Line for the 1 <sup>st</sup> Bit48Figure 3-26 EM Results of L <sub>1</sub> for the 1 <sup>st</sup> Bit49Figure 3-28 EM Results of L <sub>1</sub> for the 1 <sup>st</sup> Bit49Figure 3-29 Layout of the L <sub>2</sub> for the 1 <sup>st</sup> Bit50Figure 3-30 EM Results of L <sub>2</sub> for the 1 <sup>st</sup> Bit50Figure 3-32 EM Results of L <sub>2</sub> for the 1 <sup>st</sup> Bit50Figure 3-32 EM Results of L <sub>2</sub> for the 1 <sup>st</sup> Bit50Figure 3-32 EM Results of L <sub>2</sub> for the 1 <sup></sup>                                   |                                                                                        |    |

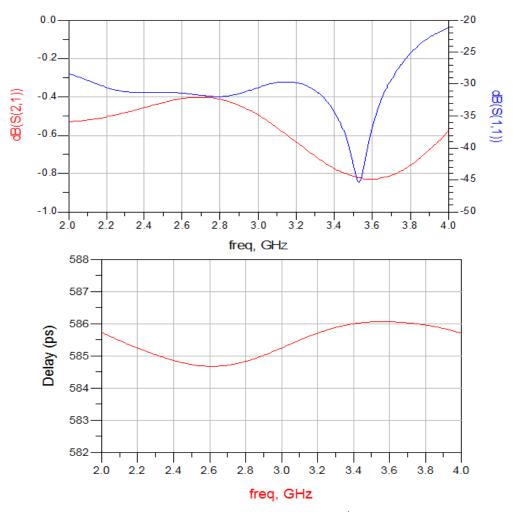

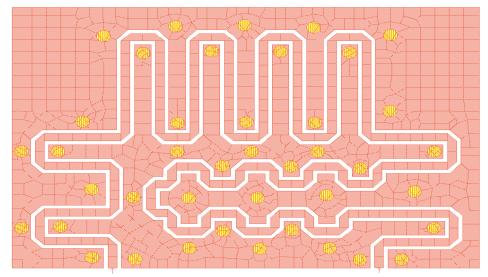

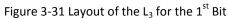

| Figure 3-9 Response of 6-Bit Periodically Loaded Lines TTD Network33Figure 3-10 Response of the Unit Section for Loaded Reflection Lines Network34Figure 3-11 Delay Response of the Loaded Reflection Lines Network35Figure 3-12 T-Section Coupled Inductors for 1 <sup>st</sup> order APF Network35Figure 3-13 Modified T-Section Coupled Inductors for 2 <sup>nd</sup> order APF Network36Figure 3-14 The Response of the Unit Cell for APF Network37Figure 3-15 The Response of 6-Bit APF TTD Network38Figure 3-16 The Schematic of the Self-Switched 2 <sup>nd</sup> order APF Circuit38Figure 3-17 The Effects of Switch Isolation for Switched-Transmission Lines Network41Figure 3-19 Outline Drawings of QFN (16pin, 3x3mm) Package [Dimensions in mm]43Figure 3-20 RO3210 Demo-Board for SP4T Switch Measurements43Figure 3-23 The Schematic of 6-Bits Switched-Transmission Lines TTD Network44Figure 3-24 Off-Path Resonance Forbidden Zones for the Reference Lines of SP4T47Figure 3-25 Layout of the Reference Line for the 1 <sup>st</sup> Bit48Figure 3-26 EM Results of L <sub>1</sub> for the 1 <sup>st</sup> Bit49Figure 3-28 EM Results of L <sub>1</sub> for the 1 <sup>st</sup> Bit50Figure 3-20 EM Results of L <sub>2</sub> for the 1 <sup>st</sup> Bit50Figure 3-28 EM Results of L <sub>2</sub> for the 1 <sup>st</sup> Bit50Figure 3-24 EM Results of L <sub>2</sub> for the 1 <sup>st</sup> Bit50Figure 3-26 EM Results of L <sub>2</sub> for the 1 <sup>st</sup> Bit50Figure 3-27 Layout of the L <sub>1</sub> for the 1 <sup>st</sup> Bit50Figure 3-30 EM Results of L <sub>2</sub> for the 1 <sup>st</sup> Bit50Figure 3-31 Layout of the L <sub>3</sub> for the 1 <sup>st</sup> Bit |                                                                                        |    |

| Figure 3-10 Response of the Unit Section for Loaded Reflection Lines Network34Figure 3-11 Delay Response of the Loaded Reflection Lines Network35Figure 3-12 T-Section Coupled Inductors for $1^{st}$ order APF Network35Figure 3-13 Modified T-Section Coupled Inductors for $2^{nd}$ order APF Network36Figure 3-14 The Response of the Unit Cell for APF Network37Figure 3-15 The Response of 6-Bit APF TTD Network38Figure 3-16 The Schematic of the Self-Switched $2^{nd}$ order APF Circuit39Figure 3-17 The Effects of Switch Isolation for Switched-Transmission Lines Network41Figure 3-18 Pin Descriptions and Truth Table for HMC241LP3 and SKY13384-350LF42Figure 3-19 Outline Drawings of QFN (16pin, 3x3mm) Package [Dimensions in mm]43Figure 3-20 RO3210 Demo-Board for SP4T Switch Measurements43Figure 3-21 Measurements of HMC241LP3 on RO321044Figure 3-22 Measurements of HMC241LP3 on RO321045Figure 3-24 Off-Path Resonance Forbidden Zones for the Reference Lines of SP4T47Figure 3-25 Layout of the Reference Line for the $1^{st}$ Bit48Figure 3-26 EM Results of L1 for the $1^{st}$ Bit49Figure 3-29 Layout of the L2 for the $1^{st}$ Bit49Figure 3-29 Layout of the L2 for the $1^{st}$ Bit50Figure 3-30 EM Results of L2 for the $1^{st}$ Bit50Figure 3-31 Layout of the L3 for the $1^{st}$ Bit50Figure 3-32 EM Results of L3 for the $1^{st}$ Bit51                                                                                                                                                                                                                                                                                                                               |                                                                                        |    |

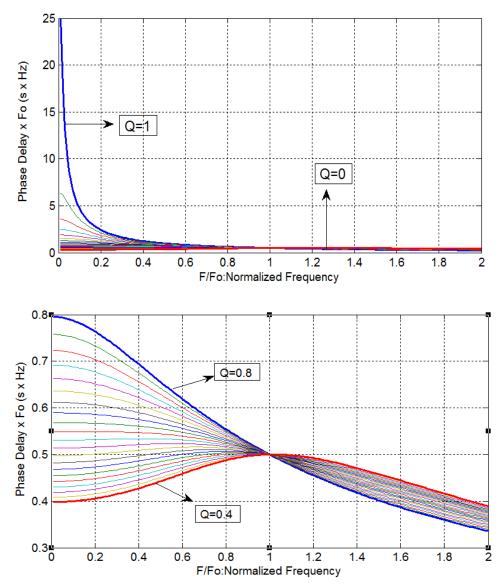

| Figure 3-11 Delay Response of the Loaded Reflection Lines Network35Figure 3-12 T-Section Coupled Inductors for 1st order APF Network35Figure 3-13 Modified T-Section Coupled Inductors for 2nd order APF Network36Figure 3-14 The Response of the Unit Cell for APF Network37Figure 3-15 The Response of 6-Bit APF TTD Network38Figure 3-16 The Schematic of the Self-Switched 2nd order APF Circuit39Figure 3-17 The Effects of Switch Isolation for Switched-Transmission Lines Network41Figure 3-18 Pin Descriptions and Truth Table for HMC241LP3 and SKY13384-350LF.42Figure 3-19 Outline Drawings of QFN (16pin, 3x3mm) Package [Dimensions in mm]43Figure 3-20 RO3210 Demo-Board for SP4T Switch Measurements43Figure 3-21 Measurements of SKY13384-350LF on RO321044Figure 3-22 Measurements of HMC241LP3 on RO321045Figure 3-24 Off-Path Resonance Forbidden Zones for the Reference Lines of SP4T47Figure 3-25 Layout of the Reference Line for the 1st Bit48Figure 3-26 EM Results of L <sub>1</sub> for the 1st Bit49Figure 3-28 EM Results of L <sub>1</sub> for the 1st Bit49Figure 3-29 Layout of the L <sub>2</sub> for the 1st Bit50Figure 3-30 EM Results of L <sub>2</sub> for the 1st Bit50Figure 3-31 Expound of the L <sub>3</sub> for the 1st Bit50Figure 3-32 EM Results of L <sub>2</sub> for the 1st Bit50Figure 3-34 EM Results of L <sub>2</sub> for the 1st Bit50Figure 3-34 EM Results of L <sub>2</sub> for the 1st Bit50Figure 3-34 EM Results of L <sub>2</sub> for the 1st Bit50Figure 3-34 EM Results of L <sub>2</sub> for the 1                                                                                                                                                |                                                                                        |    |

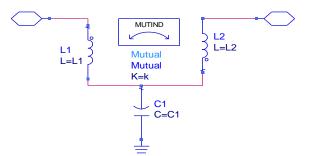

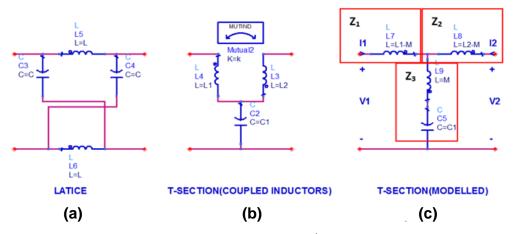

| Figure 3-12 T-Section Coupled Inductors for 1st order APF Network35Figure 3-13 Modified T-Section Coupled Inductors for $2^{nd}$ order APF Network36Figure 3-14 The Response of the Unit Cell for APF Network37Figure 3-15 The Response of 6-Bit APF TTD Network38Figure 3-16 The Schematic of the Self-Switched $2^{nd}$ order APF Circuit39Figure 3-17 The Effects of Switch Isolation for Switched-Transmission Lines Network41Figure 3-18 Pin Descriptions and Truth Table for HMC241LP3 and SKY13384-350LF.42Figure 3-19 Outline Drawings of QFN (16pin, 3x3mm) Package [Dimensions in mm]43Figure 3-20 RO3210 Demo-Board for SP4T Switch Measurements43Figure 3-21 Measurements of SKY13384-350LF on RO321044Figure 3-22 Measurements of HMC241LP3 on RO321045Figure 3-23 The Schematic of 6-Bits Switched-Transmission Lines TTD Network46Figure 3-24 Off-Path Resonance Forbidden Zones for the Reference Lines of SP4T47Figure 3-25 Layout of the Reference Line for the 1st Bit48Figure 3-27 Layout of the L1 for the 1st Bit49Figure 3-28 EM Results of L1 for the 1st Bit49Figure 3-29 Layout of the L2 for the 1st Bit50Figure 3-30 EM Results of L2 for the 1st Bit50Figure 3-31 Layout of the L3 for the 1st Bit50Figure 3-32 EM Results of L3 for the 1st Bit51                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                        |    |

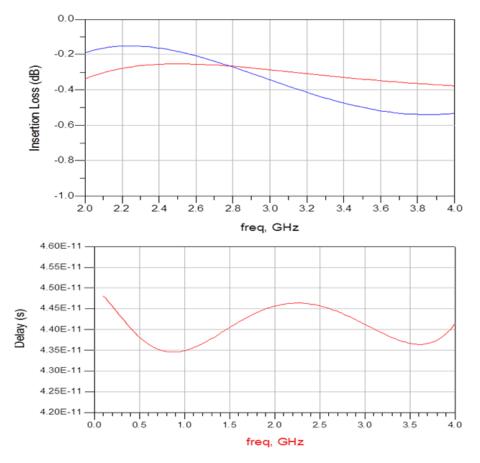

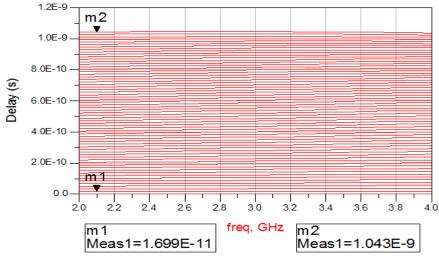

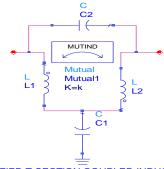

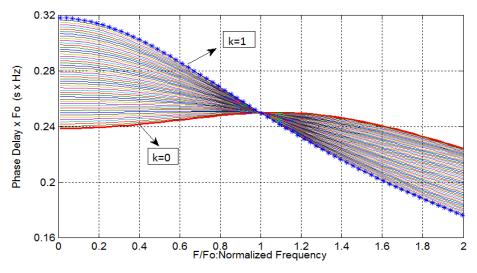

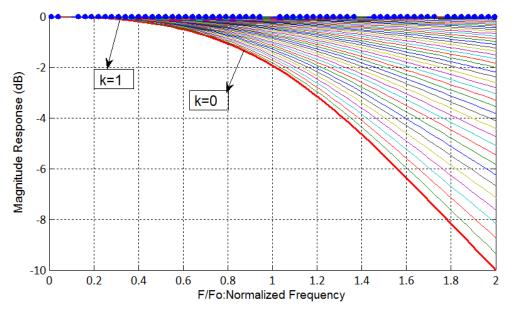

| Figure 3-14 The Response of the Unit Cell for APF Network37Figure 3-15 The Response of 6-Bit APF TTD Network38Figure 3-16 The Schematic of the Self-Switched $2^{nd}$ order APF Circuit39Figure 3-17 The Effects of Switch Isolation for Switched-Transmission Lines Network41Figure 3-18 Pin Descriptions and Truth Table for HMC241LP3 and SKY13384-350LF.42Figure 3-19 Outline Drawings of QFN (16pin, 3x3mm) Package [Dimensions in mm]43Figure 3-20 RO3210 Demo-Board for SP4T Switch Measurements43Figure 3-21 Measurements of SKY13384-350LF on RO321044Figure 3-22 Measurements of HMC241LP3 on RO321045Figure 3-23 The Schematic of 6-Bits Switched-Transmission Lines TTD Network46Figure 3-24 Off-Path Resonance Forbidden Zones for the Reference Lines of SP4T47Figure 3-25 Layout of the Reference Line for the 1 <sup>st</sup> Bit48Figure 3-26 EM Results of the Reference Line for the 1 <sup>st</sup> Bit49Figure 3-28 EM Results of L <sub>1</sub> for the 1 <sup>st</sup> Bit49Figure 3-29 Layout of the L <sub>2</sub> for the 1 <sup>st</sup> Bit50Figure 3-30 EM Results of L <sub>2</sub> for the 1 <sup>st</sup> Bit50Figure 3-31 Layout of the L <sub>3</sub> for the 1 <sup>st</sup> Bit51Figure 3-32 EM Results of L <sub>2</sub> for the 1 <sup>st</sup> Bit51Figure 3-32 EM Results of L <sub>3</sub> for the 1 <sup>st</sup> Bit51                                                                                                                                                                                                                                                                                                                                                   |                                                                                        |    |

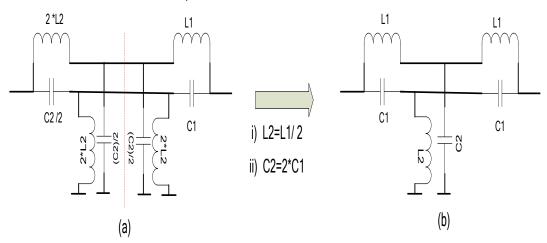

| Figure 3-14 The Response of the Unit Cell for APF Network37Figure 3-15 The Response of 6-Bit APF TTD Network38Figure 3-16 The Schematic of the Self-Switched $2^{nd}$ order APF Circuit39Figure 3-17 The Effects of Switch Isolation for Switched-Transmission Lines Network41Figure 3-18 Pin Descriptions and Truth Table for HMC241LP3 and SKY13384-350LF.42Figure 3-19 Outline Drawings of QFN (16pin, 3x3mm) Package [Dimensions in mm]43Figure 3-20 RO3210 Demo-Board for SP4T Switch Measurements43Figure 3-21 Measurements of SKY13384-350LF on RO321044Figure 3-22 Measurements of HMC241LP3 on RO321045Figure 3-23 The Schematic of 6-Bits Switched-Transmission Lines TTD Network46Figure 3-24 Off-Path Resonance Forbidden Zones for the Reference Lines of SP4T47Figure 3-25 Layout of the Reference Line for the 1 <sup>st</sup> Bit48Figure 3-26 EM Results of the Reference Line for the 1 <sup>st</sup> Bit49Figure 3-28 EM Results of L <sub>1</sub> for the 1 <sup>st</sup> Bit49Figure 3-29 Layout of the L <sub>2</sub> for the 1 <sup>st</sup> Bit50Figure 3-30 EM Results of L <sub>2</sub> for the 1 <sup>st</sup> Bit50Figure 3-31 Layout of the L <sub>3</sub> for the 1 <sup>st</sup> Bit51Figure 3-32 EM Results of L <sub>2</sub> for the 1 <sup>st</sup> Bit51Figure 3-32 EM Results of L <sub>3</sub> for the 1 <sup>st</sup> Bit51                                                                                                                                                                                                                                                                                                                                                   | Figure 3-13 Modified T-Section Coupled Inductors for 2 <sup>nd</sup> order APF Network | 36 |

| Figure 3-16 The Schematic of the Self-Switched 2nd order APF Circuit39Figure 3-17 The Effects of Switch Isolation for Switched-Transmission Lines Network41Figure 3-18 Pin Descriptions and Truth Table for HMC241LP3 and SKY13384-350LF.42Figure 3-19 Outline Drawings of QFN (16pin, 3x3mm) Package [Dimensions in mm].43Figure 3-20 RO3210 Demo-Board for SP4T Switch Measurements.43Figure 3-21 Measurements of SKY13384-350LF on RO321044Figure 3-22 Measurements of HMC241LP3 on RO321045Figure 3-23 The Schematic of 6-Bits Switched-Transmission Lines TTD Network46Figure 3-24 Off-Path Resonance Forbidden Zones for the Reference Lines of SP4T47Figure 3-26 EM Results of the Reference Line for the 1st Bit48Figure 3-27 Layout of the L1 for the 1st Bit49Figure 3-28 EM Results of L1 for the 1st Bit49Figure 3-29 Layout of the L2 for the 1st Bit50Figure 3-30 EM Results of L2 for the 1st Bit50Figure 3-30 EM Results of L2 for the 1st Bit51Figure 3-31 Layout of the L3 for the 1st Bit51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -                                                                                      |    |

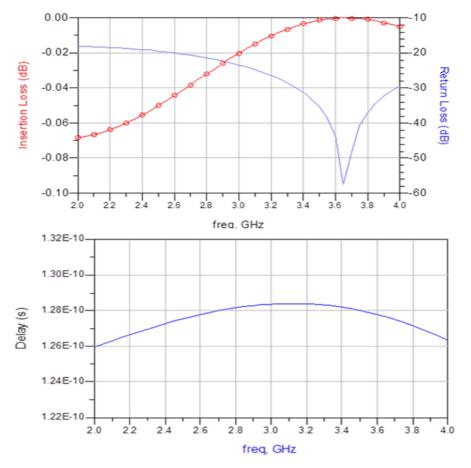

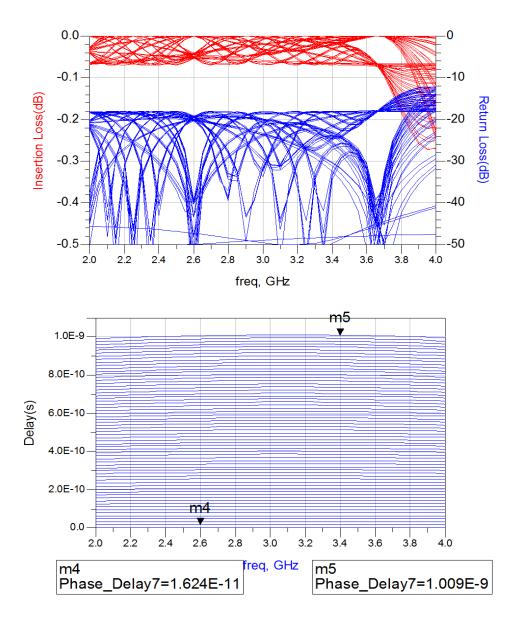

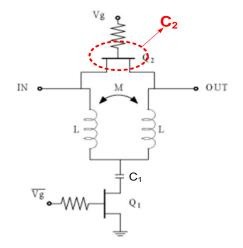

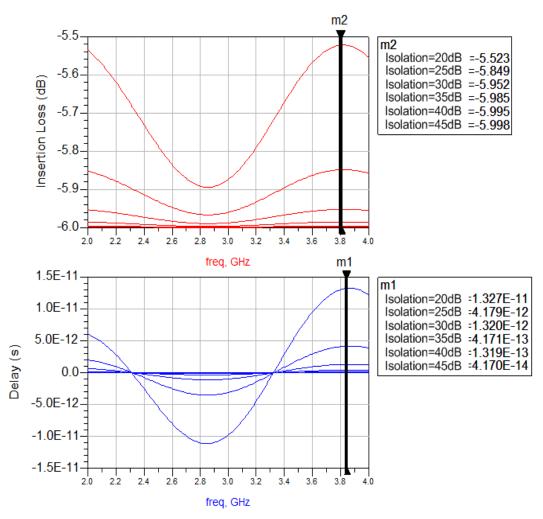

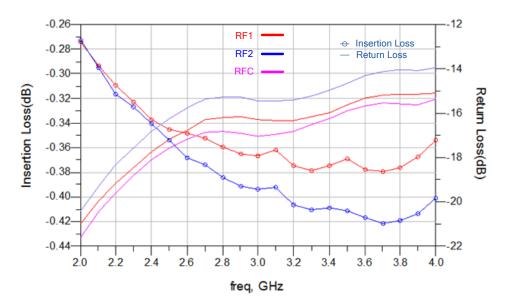

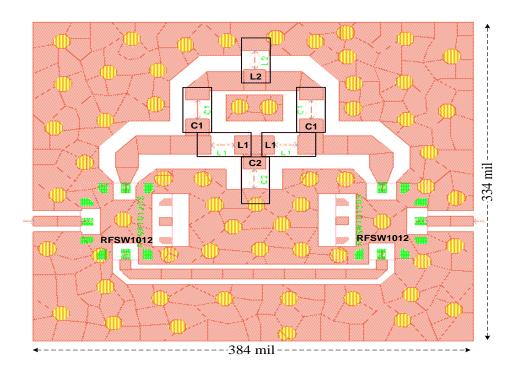

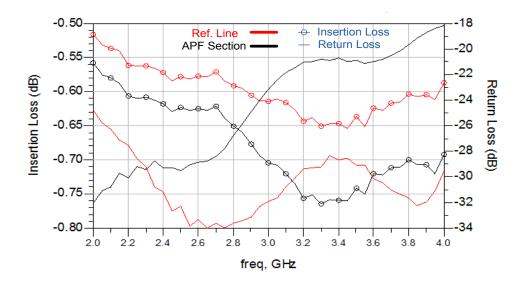

| Figure 3-16 The Schematic of the Self-Switched $2^{nd}$ order APF Circuit39Figure 3-17 The Effects of Switch Isolation for Switched-Transmission Lines Network41Figure 3-18 Pin Descriptions and Truth Table for HMC241LP3 and SKY13384-350LF.42Figure 3-19 Outline Drawings of QFN (16pin, 3x3mm) Package [Dimensions in mm]43Figure 3-20 RO3210 Demo-Board for SP4T Switch Measurements43Figure 3-21 Measurements of SKY13384-350LF on RO321044Figure 3-22 Measurements of HMC241LP3 on RO321045Figure 3-23 The Schematic of 6-Bits Switched-Transmission Lines TTD Network46Figure 3-24 Off-Path Resonance Forbidden Zones for the Reference Lines of SP4T47Figure 3-26 EM Results of the Reference Line for the $1^{st}$ Bit48Figure 3-27 Layout of the L1 for the $1^{st}$ Bit49Figure 3-28 EM Results of L1 for the $1^{st}$ Bit49Figure 3-29 Layout of the L2 for the $1^{st}$ Bit50Figure 3-30 EM Results of L2 for the $1^{st}$ Bit50Figure 3-31 Layout of the L3 for the $1^{st}$ Bit51Figure 3-32 EM Results of L3 for the $1^{st}$ Bit51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Figure 3-15 The Response of 6-Bit APF TTD Network                                      | 38 |

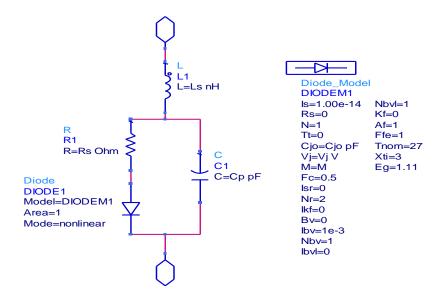

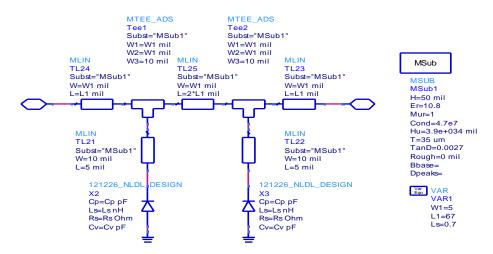

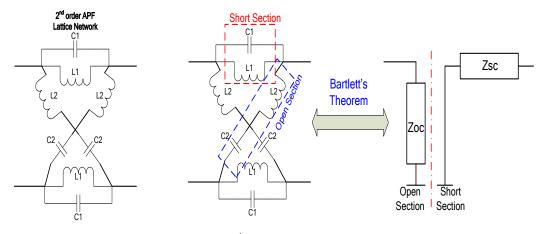

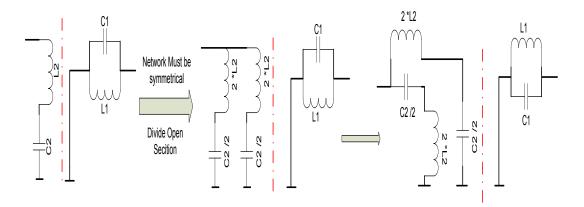

| Figure 3-18 Pin Descriptions and Truth Table for HMC241LP3 and SKY13384-350LF.42Figure 3-19 Outline Drawings of QFN (16pin, 3x3mm) Package [Dimensions in mm].43Figure 3-20 RO3210 Demo-Board for SP4T Switch Measurements43Figure 3-21 Measurements of SKY13384-350LF on RO321044Figure 3-22 Measurements of HMC241LP3 on RO321045Figure 3-23 The Schematic of 6-Bits Switched-Transmission Lines TTD Network46Figure 3-24 Off-Path Resonance Forbidden Zones for the Reference Lines of SP4T47Figure 3-25 Layout of the Reference Line for the 1 <sup>st</sup> Bit48Figure 3-26 EM Results of the Reference Line for the 1 <sup>st</sup> Bit49Figure 3-28 EM Results of L1 for the 1 <sup>st</sup> Bit49Figure 3-29 Layout of the L2 for the 1 <sup>st</sup> Bit50Figure 3-30 EM Results of L2 for the 1 <sup>st</sup> Bit50Figure 3-31 Layout of the L3 for the 1 <sup>st</sup> Bit51Figure 3-32 EM Results of L3 for the 1 <sup>st</sup> Bit51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Figure 3-16 The Schematic of the Self-Switched 2 <sup>nd</sup> order APF Circuit       | 39 |