#### PROTOTYPE DEVELOPMENT AND VERIFICATION OF AN IP LOOKUP ENGINE ON FPGA

#### A THESIS SUBMITTED TO THE GRADUATE SCHOOL OF NATURAL AND APPLIED SCIENCES OF MIDDLE EAST TECHNICAL UNIVERSITY

BY

AKIN ÖZKANER

IN PARTIAL FULLFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE IN ELECTRICAL AND ELECTRONICS ENGINEERING

FEBRUARY 2012

#### APPROVAL OF THE THESIS:

#### PROTOTYPE DEVELOPMENT AND VERIFICATION FOR AN IP LOOKUP ENGINE ON FPGAS PERFORMANCE STUDY

submitted by AKIN ÖZKANER in partial fulfillment of the requirements for the degree of Master of Science in Electrical and Electronics Engineering Department, Middle East Technical University by,

| Prof. Dr. Canan Özgen                                       |            |

|-------------------------------------------------------------|------------|

| Dean, Graduate School of Natural and Applied Sciences       |            |

| Prof. Dr. İsmet Erkmen                                      |            |

| Head of Department, Electrical and Electronics Engineering  | ng         |

| Assoc. Prof. Dr. Cüneyt F. Bazlamaçcı                       |            |

| Supervisor, Electrical and Electronics Engineering Dept.,   | METU       |

| Examining Committee Members:                                |            |

| Prof. Dr. Semih Bilgen                                      |            |

| Electrical and Electronics Engineering Dept., METU          |            |

| Assoc. Prof. Dr. Cüneyt F. Bazlamaçcı                       |            |

| Electrical and Electronics Engineering Dept., METU          |            |

| Prof. Dr. Gözde B. Akar                                     |            |

| Electrical and Electronics Engineering Dept., METU          |            |

| Assoc. Prof. Dr. Ş. Ece Schmidt                             |            |

| Electrical and Electronics Engineering Dept., METU          |            |

| Dr. Oğuzhan Erdem                                           |            |

| Electrical and Electronics Engineering Dept., Atatürk Univ. |            |

| Date:                                                       | 08.02.2012 |

I hereby declare that all information in this document has been obtained and presented in accordance with academic rules and ethical conduct. I also declare that, as required by these rules and conduct, I have fully cited and referenced all material and results that are not original to this work.

> Name, Last name : Akın Özkaner Signature :

## ABSTRACT

# PROTOTYPE DEVELOPMENT AND VERIFICATION FOR AN IP LOOKUP ENGINE ON FPGAS PERFORMANCE STUDY

Özkaner, Akın

M. S., Department of Electrical and Electronics Engineering Supervisor: Assoc. Prof. Dr. Cüneyt F. Bazlamaçcı

#### February 2012, 117 pages

The increasing use of the internet demands more powerful routers with higher speed, less power consumption and less physical space occupation. IP lookup operation is one of the major concerns in today's routers for providing such attributes. To accomplish IP lookup on routers, hardware or software based solutions can be used. In this thesis, an SRAM based pipelined architecture proposed earlier for ASIC implementation is re-designed and implemented on an FPGA in the form of a BRAM based pipelined 8x8 torus architecture using Xilinx ISE and simulated and verified using Modelsim Simulator. Some necessary modifications and improvements for FPGA implementation are carried out. The results of our experiments, which are performed for a real router lookup table and a real time traffic load with various optimizations, are also presented. Our study and design effort demonstrates the feasibility of the FPGA implementation of the proposed technique, of course with a considerable performance penalty.

Keywords : IP lookup, FPGA, routers.

# ÖΖ

#### FPGA ÜZERİNDE IP TARAMA MOTORU PROTOTİP GELİŞTİRMESİ VE DOĞRULAMASI

#### Özkaner, Akın

Yüksek Lisans, Elektrik Elektronik Mühendisliği Bölümü Tez Yöneticisi : Doç. Dr. Cüneyt F. Bazlamaçcı

#### Şubat 2012, 117 sayfa

Artan internet kullanımı; yüksek hızda çalışan, güç tüketimi düşük olan ve fiziksel olarak az yer kaplayan daha etkili ağ yönlendiricilerinin kullanımını gerektirmektedir. Bu özelliklere sahip ağ yönlendiricileri için en önemli unsurlardan birisi de IP arama işlemidir. Ağ yönlendiriciler üzerinde IP arama işlevini gerçekleştirmek amacıyla yazılım veya donanım temelli çözümler kullanılabilmektedir. Bu tez çalışması, boru hattı davranışlı SRAM tabanlı ASIC model için daha önce önerilmiş bir çalışmanın yeniden tasarlanarak FPGA donanım yapısında gerçeklenmesini içermektedir. Tez kapsamında, boru hattı davranışlı BRAM tabanlı 8x8 torus mimarinin Xilinx ISE ile tasarımı ve Modelsim Simulator ile benzetimi gerçekleştirilmiştir. FPGA tasarımına yönelik bazı iyileştirmeler ve gerekli değişiklikler yapılmıştır. Gerçek yönlendirici arama tabloları ve gerçek zamanlı ağ trafiği ile çeşitli en iyileştirmeler ve denemeler de gerçekleştirilmiş ve sonuçları sunulmuştur. Çalışmamız ve tasarım çabamız daha önce önerilmiş tekniğin, elbette belirgin bir başarım kaybı karşılığında, FPGA gerçeklemesinin de mümkün olduğunu göstermektedir.

Anahtar Kelimeler: IP arama, IP tarama, ağ yönlendiricisi, FPGA üzerinde IP tarama

To My Family

## ACKNOWLEDGEMENTS

I would like to express my sincere gratitude to my supervisor Assoc. Prof. Dr. Cüneyt F. Bazlamaçcı for his guidance, advice, criticism, encouragement, endless patience and insight throughout the completion of the thesis.

I wish to thank my company ASELSAN A.Ş for giving me the opportunity of continuing my thesis study and supporting me in my efforts to get the Master of Science degree.

I would like to express my appreciation to all my friends and colleagues for their contributions to my thesis with their continuous guidance, advice, encouragement and for expanding my horizons.

Finally, my family. No word can suffice to express how I am grateful to my parents but at least I can mention my sincere gratitude to them for their unwavering support, continual confidence and endless and gratis love. I also wish to thank my wife for her support on my thesis.

# **TABLE OF CONTENTS**

| ABSTRACT                                                         | IV   |

|------------------------------------------------------------------|------|

| ÖZ                                                               | V    |

| ACKNOWLEDGEMENTS                                                 | VII  |

| LIST OF ABBREVIATIONS                                            | XIII |

| CHAPTER 1 INTRODUCTION                                           | 1    |

| 1.1 BACKGROUND                                                   | 1    |

| 1.1.1 Network Topology                                           | 3    |

| 1.1.2 Router Architecture                                        | 5    |

| 1.1.3 IP Lookup                                                  | 6    |

| 1.2 MOTIVATION                                                   | 6    |

| 1.3 CONTRIBUTIONS                                                | 7    |

| 1.4 OUTLINE                                                      | 8    |

| CHAPTER 2 IP LOOKUP APPROACHES                                   | 9    |

| 2.1 SOFTWARE BASED SOLUTIONS                                     | 9    |

| 2.2 HARDWARE BASED SOLUTIONS                                     | 11   |

| 2.2.1 SRAM Based Solutions                                       | 12   |

| 2.2.2 T-CAM Based Solutions                                      | 13   |

| CHAPTER 3 ARRAY DESIGN FOR TRIE BASED IP LOOKUP AND UPDATE       | 15   |

| 3.1 INTRODUCTION                                                 | 15   |

| 3.2 MOTIVATION                                                   | 16   |

| 3.3 ARRAY ARCHITECTURE FOR FAST IP LOOKUP WITH UPDATE CAPABILITY | 16   |

| 3.3.1 IP Lookup Process                                          | 19   |

| 3.3.2 IP Lookup Table Update and Propagate Process               | 21   |

| 3.3.3 Processing Element                                         | 22   |

| 3.3.4 Selector Unit                                              | 27   |

| 3.3.5 Contention Resolver                                        | 28   |

| 3.3.6 Congestion Control Unit                                    | 28   |

| 3.3.7 Ram Data Loader                                            | 29   |

| CHAPTER 4 FPGA IMPLEMENTATION OF THE ARRAY ARCHITECTURE FOR F.   | AST  |

| IP LOOKUP WITH UPDATE CAPABILITY                                 | 30   |

| 4.1 PROCESSING ELEMENT                                           | 30   |

| 4.1.1 Design                 |     |

|------------------------------|-----|

| 4.1.2 Simulation             |     |

| 4.2 SELECTOR UNIT            |     |

| 4.2.1 Design                 |     |

| 4.2.2 Simulation             | 50  |

| 4.3 CONTENTION RESOLVER      |     |

| 4.3.1 Design                 |     |

| 4.3.2 Simulation             | 56  |

| 4.4 CONGESTION CONTROL UNIT  | 61  |

| 4.4.1 Design                 | 61  |

| 4.4.2 Simulation             |     |

| 4.5 RAM DATA LOADER          |     |

| 4.5.1 Design                 | 65  |

| 4.5.2 Simulation             | 67  |

| 4.6 SYSTEM INTEGRATION       | 69  |

| 4.6.1 Design                 | 69  |

| 4.6.2 Simulation             | 74  |

| 4.7 PERFORMANCE EVALUATION   |     |

| 4.7.1 Speedup and Throughput |     |

| 4.7.2 Latency                |     |

| 4.8 OPTIMIZATION             |     |

| CHAPTER 5 CONCLUSION         |     |

| REFERENCES                   |     |

| APPENDIX A                   | 95  |

| APPENDIX B                   |     |

| APPENDIX C                   | 109 |

# **LIST OF FIGURES**

| Figure 1-1 Example Forwarding Table                                 |    |

|---------------------------------------------------------------------|----|

| Figure 2-1 A Prefix Table and Corresponding Binary Trie             | 10 |

| Figure 2-2 The Leaf Pushed Version of the Binary Trie in Figure 2-1 | 11 |

| Figure 2-3 TCAM                                                     | 14 |

| Figure 3-1 A 4x4 Systolic Array                                     | 17 |

| Figure 3-2 4x4 Torus                                                | 17 |

| Figure 3-3 4x4 SAFIL Architecture [6]                               |    |

| Figure 3-4 SAFIL Frame                                              | 19 |

| Figure 3-5 Propagation of a SAFIL frame during lookup               | 20 |

| Figure 3-6 SAFIL Update Frame                                       |    |

| Figure 3-7 Block Diagram of the Processing Element (PE)             | 22 |

| Figure 3-8 Flowchart of Data Processing in PE                       | 24 |

| Figure 3-9 Detailed Block Diagram of a PE (Lookup Process)          |    |

| Figure 3-10 Block Diagram of a PE (Update Process)                  |    |

| Figure 3-11 Block Diagram of a PE's Propagate Process               |    |

| Figure 4-1 FIFO Input and Output Signals                            |    |

| Figure 4-2 IP Core Menu for Block RAM Generation                    |    |

| Figure 4-3 Data Flow Manager Schematic View                         |    |

| Figure 4-4 Processing Element                                       |    |

| Figure 4-5 Simulation Results for PE in Scenario 1                  |    |

| Figure 4-6 Simulation Results for PE in Scenario 2                  | 39 |

| Figure 4-7 Simulation Results for PE in Scenario 3                  | 41 |

| Figure 4-8 Simulation Results for PE in Scenario 4                  |    |

| Figure 4-9 Simulation Results for PE in Scenario 5                  | 46 |

| Figure 4-10 Selector Unit Input and Output Signals                  |    |

| Figure 4-11 Simulation Results for SU in Scenario 1                 | 51 |

| Figure 4-12 Block Diagram of CR                                     | 52 |

| Figure 4-13 Block Diagram of Transition from CR to PE               | 54 |

| Figure 4-14 Contention Resolver Input and Output Signals                | 55 |

|-------------------------------------------------------------------------|----|

| Figure 4-15 Simulation Results for CR in Scenario 1                     | 59 |

| Figure 4-16 Simulation Results for CR in Scenario 1 (continued)         | 60 |

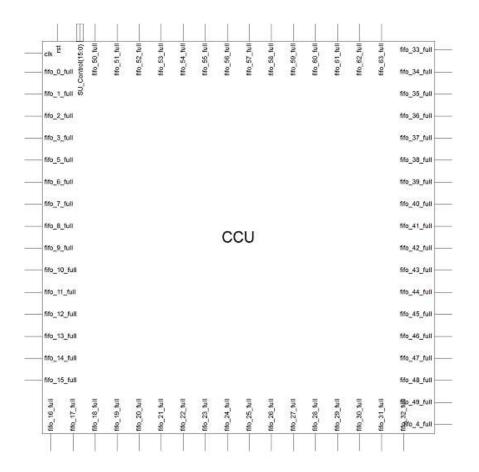

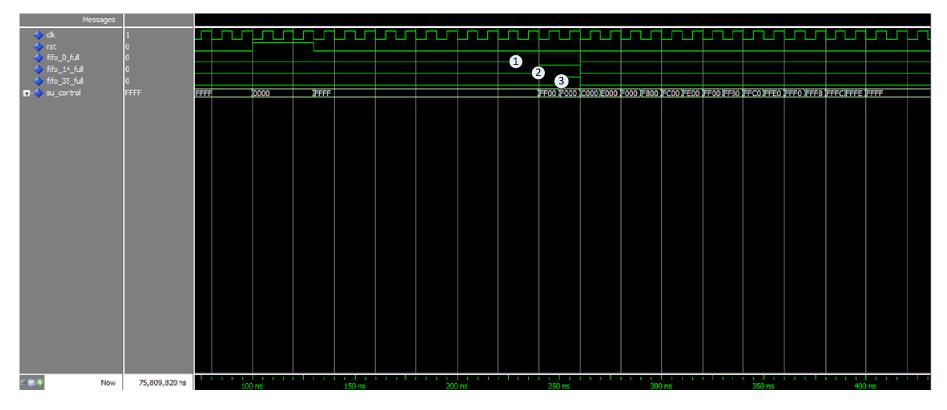

| Figure 4-17 Congestion Controller Unit Input and Output Signals         | 61 |

| Figure 4-18 Simulation Results for CCU in Scenario 1                    | 64 |

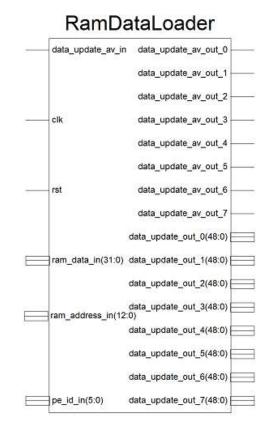

| Figure 4-19 RDL Unit Input and Output Signals                           | 66 |

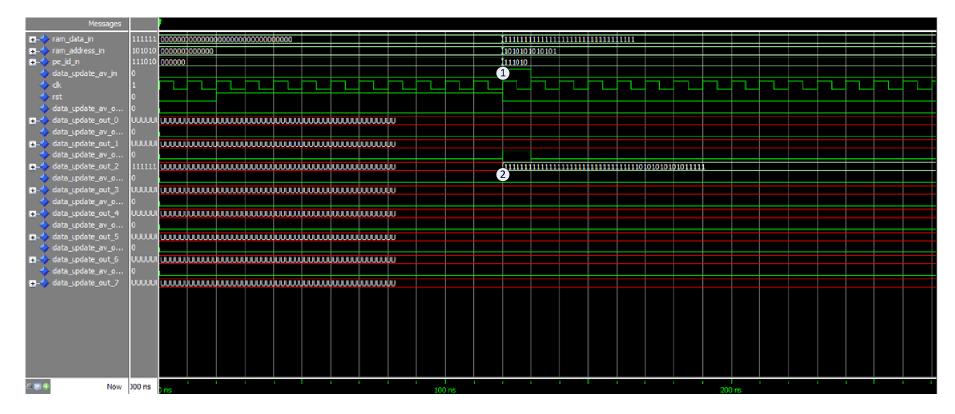

| Figure 4-20 Simulation Results for RDL in Scenario 1                    | 68 |

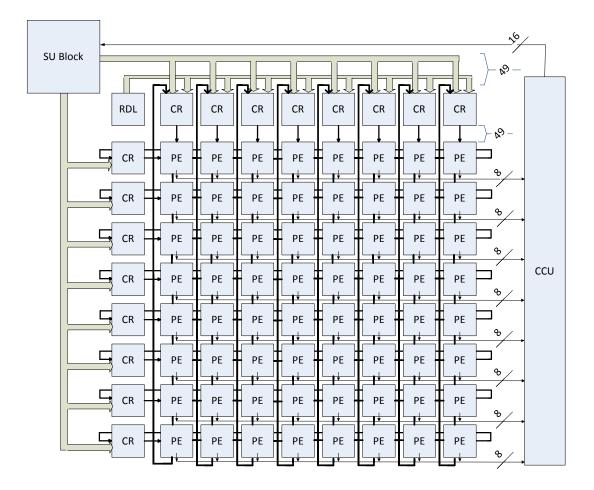

| Figure 4-21 8x8 SAFIL System                                            | 70 |

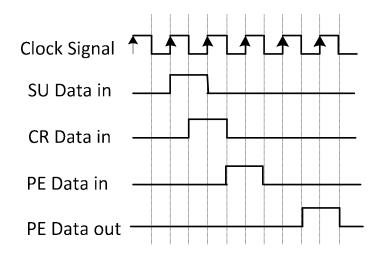

| Figure 4-22 Timing Diagram for the Whole System                         | 71 |

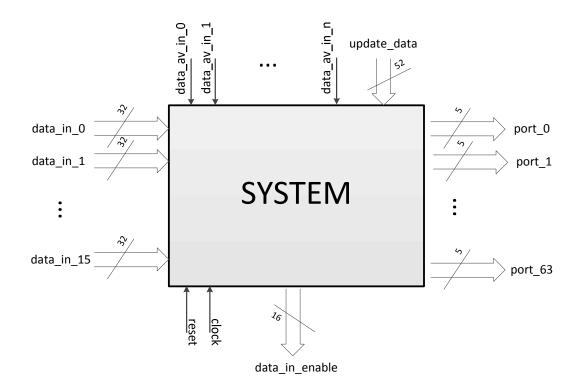

| Figure 4-23 System Input and Output Signals                             | 72 |

| Figure 4-24 Data Adapter                                                |    |

| Figure 4-25 The Binary View of "file_data.in"                           |    |

| Figure 4-26 The Binary View of "traffic.in"                             | 77 |

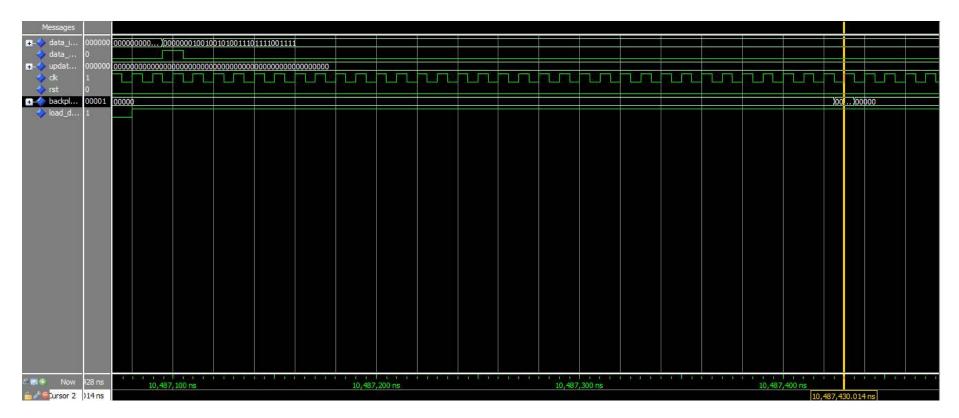

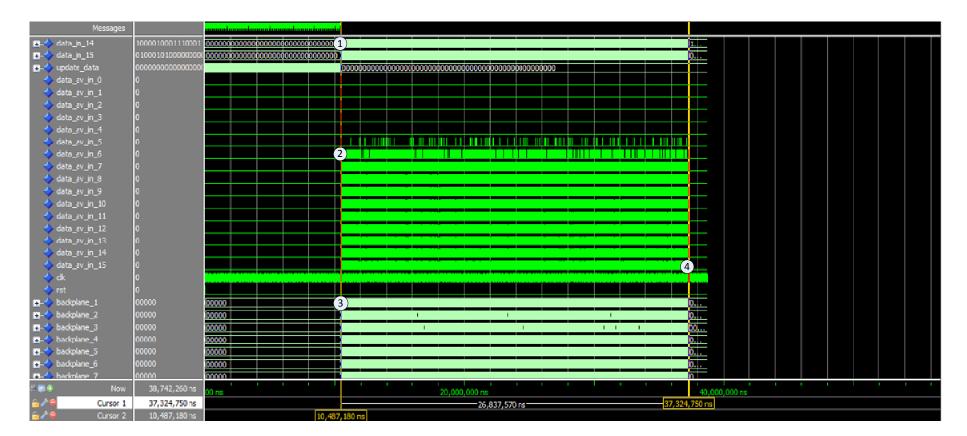

| Figure 4-27 Simulation Results for the System in Scenario 1             | 80 |

| Figure 4-28 Simulation Results for the System in Scenario 1 (continued) | 81 |

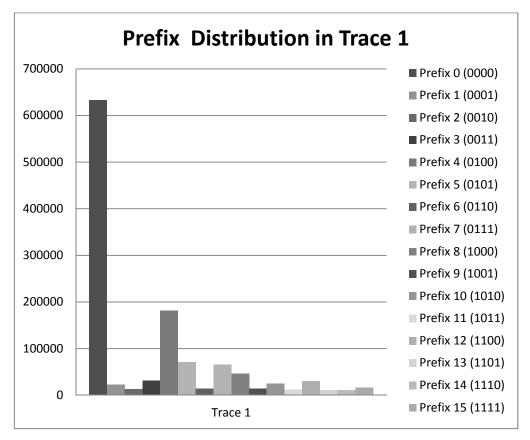

| Figure 4-29 Trace 1 Distribution                                        | 82 |

| Figure 4-30 Port Results of Trace 1                                     | 83 |

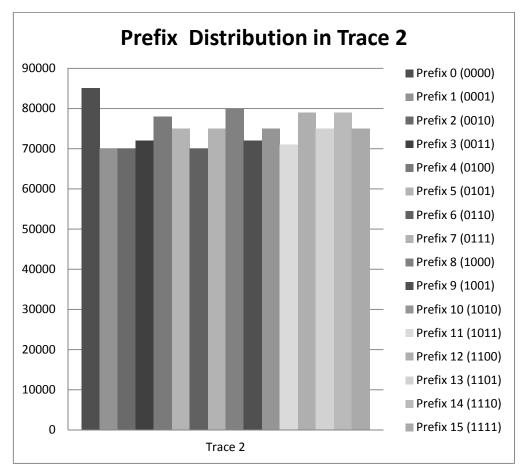

| Figure 4-31 Trace 2 Distribution                                        | 84 |

| Figure 4-32 Trace 1 Simulation Results                                  | 85 |

| Figure 4-33 Trace 2 Simulation Results                                  | 86 |

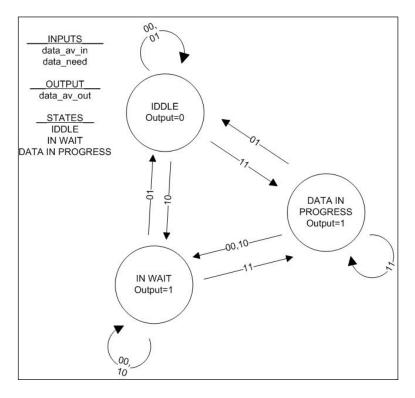

| Figure 4-34 State Diagram for Our Modified CR                           | 90 |

| Figure 4-35 Block Diagram of the Modified System                        | 90 |

# LIST OF TABLES

| Table 4-1 FIFO Signal Descriptions.                                      | 32 |

|--------------------------------------------------------------------------|----|

| Table 4-2 PE Signal Descriptions                                         | 35 |

| Table 4-3 Initial Partitioning Conversion                                | 47 |

| Table 4-4 SU Signal Descriptions                                         | 49 |

| Table 4-5 CR Signal Descriptions                                         | 54 |

| Table 4-6 CCU Signal Descriptions                                        | 62 |

| Table 4-7 RDL Signal Descriptions                                        | 66 |

| Table 4-8    The System Signal Descriptions                              | 72 |

| Table 4-9 Design Requirements                                            | 73 |

| Table 4-10 Attributes of Some Xilinx Family Members                      | 73 |

| Table 4-11 Feasibility of SAFIL Implementations on Xilinx Family Members | 74 |

| Table 4-12 Effect of Threshold Level on Performance                      | 88 |

| Table 4-13 Effects of Removing FIFOs from CRs on Performance             | 90 |

# LIST OF ABBREVIATIONS

| BRAM  | Block RAM                                      |

|-------|------------------------------------------------|

| CAM   | Content Addressable Memory                     |

| CAMP  | Circular, Adaptive and Monotonic Pipeline      |

| CIDR  | Classless Inter Domain Routing                 |

| CCU   | Congestion Controller Unit                     |

| CR    | Contention Resolver                            |

| IP    | Internet Protocol                              |

| ISP   | Internet Service Provider                      |

| LPM   | Longest Prefix Matching                        |

| PE    | Processing Element                             |

| POLP  | Parallel Optimized Linear Pipeline             |

| RDL   | RAM Data Loader                                |

| SAFIL | Systolic Array Architecture for Fast IP Lookup |

| SU    | Selector Unit                                  |

| TCAM  | Ternary Content Addressable Memory             |

# **CHAPTER 1**

# **INTRODUCTION**

In the developing environment of high performance IP networks, it is expected that local and wide area backbones, enterprise networks, and ISPs will use multigigabit and even terabit networking technologies, where IP routers will be used not only to interconnect backbone segments but also to act as points of attachments to high performance wide area links.

#### **1.1 BACKGROUND**

The primary role of IP routers is to forward packets to their final destination address. For this purpose, a router must decide for each incoming packet where to send it next. In other words, the forwarding decision consists of finding the address of the next-hop router and the output port through which the packet should be sent. This information is stored in a lookup table that the router computes based on the information gathered by routing protocols. To consult the lookup table, the router uses the incoming packet's destination address as a key and this process is called *address lookup*. Once the forwarding information is retrieved, the router can transfer the packet from the incoming link to the appropriate outgoing link, in a process called switching.

The rapid growth of the Internet has stressed its routing system. While the link rates have kept pace with the increasing traffic, it has been difficult for the packet processing capacity of routers to keep up with the increased data rates of the link.

#### The Classful Addressing Scheme

When Internet addressing was initially designed, a simple address allocation scheme was defined, which is known today as the classful addressing scheme.

In IP version 4, IP addresses are 32 bit long and, when broken up into 4 groups of 8 bits, are normally represented as four decimal numbers separated by dots. The IP address scheme initially used a simple two-level hierarchy, with networks at the top level and hosts at the bottom level. This hierarchy is reflected in the fact that an IP address consists of two parts, a network part and a host part. The network part identifies the network to which a host is attached and thus all hosts attached to the same network agree in the network part of their IP addresses.

Since the network part corresponds to the first bits of the IP address, it is called the address prefix. We will write prefixes as bit strings of up to 32 bits in IPv4 followed by a "\*". For example, prefix 1000001001010110\* represents all  $2^{16}$  addresses that begin with the bit pattern 1000001001010110. Alternatively, prefixes can be indicated using the dotted-decimal notation, so the same prefix can be written as 130.86/16, where the number after the slash indicates the length of the prefix.

With a two-level hierarchy, IP routers forward packets based only on the network part, until packets reach the destination network. As a result, a forwarding table only needs to store a single entry to forward packets to all the hosts attached to the same network. This technique is called address aggregation and allows using prefixes to represent a group of addresses. Each entry in a forwarding table contains a prefix (Figure 1-1). So, finding the forwarding information requires searching for the prefix in the forwarding table that matches the corresponding bits of the destination address.

| Destination Address<br>Prefix | Next-hop       | Output<br>interface |

|-------------------------------|----------------|---------------------|

| 24.40.32/20                   | 192.41.177.148 | 2                   |

| 130.86/16                     | 192.41.177.181 | 6                   |

| 208.12.16/20                  | 192.41.177.241 | 4                   |

| 208.12.21/24                  | 192.41.177.196 | 1                   |

| 167.24.103/24                 | 192.41.177.3   | 4                   |

Figure 1-1 Example Forwarding Table

#### **1.1.1 Network Topology**

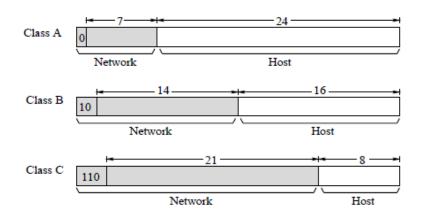

Basically, three different sizes of networks were defined in the classful addressing scheme, identified by a class name: class A, B, and C. Size of networks was determined by the number of bits used to represent the network part and the host part. Thus networks of class A, B or C consisted in an 8, 16 or 24-bit network part and a corresponding 24, 16 or 8-bit host part (Figure 1-2).

Figure 1-2 Classful Addressing Scheme

With this scheme there were very few class A networks and their addressing space represented 50% of the total IPv4 address space  $(2^{31} \text{ addresses out of a total of } 2^{32})$ . There were 16,384  $(2^{14})$  class B networks with a maximum of 65,536 hosts per network and 2,097,152  $(2^{21})$  class C networks with up to 256 hosts. This allocation scheme worked well in the early days of the Internet. However, the continuous growth of the number of hosts and networks has made apparent two problems with this classful addressing architecture. First, with only three different network sizes to

choose, the address space was not used efficiently and the IP address space was getting exhausted very rapidly, even though only a small fraction of the addresses allocated were actually in use.

#### The CIDR Addressing Scheme

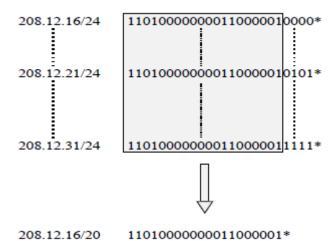

To allow for a more efficient use of the IP address space and to slow down the growth of the backbone forwarding tables, a new scheme called Classless Interdomain Routing or CIDR was introduced.

In the classful addressing scheme, only 3 different prefix lengths are allowed: 8, 16 and 24 corresponding to the classes A, B and C, respectively. CIDR makes more efficient use of the IP address space by allowing a finer granularity in the prefix lengths. With CIDR, prefixes can be of arbitrary length rather than constraining them to be 8, 16 or 24 bits long.

Figure 1-3 Address Aggregation in CIDR Acheme

#### **1.1.2 Router Architecture**

The popularity of the Internet has caused the traffic on the Internet to grow drastically every year for the last several years. It has also spurred the emergence of many ISPs. To sustain growth, ISPs need to provide new differentiated services, e.g., tiered service, support for multimedia applications, etc. The routers in the ISPs' networks play a critical role in providing these services. IP traffic in private enterprise networks has also been growing rapidly for some time. These networks face significant bandwidth challenges as new application types, especially desktop applications uniting voice, video, and data traffic need to be delivered on the network infrastructure. This growth in IP traffic is beginning to stress the traditional processor-based design of current-day routers and as a result has created new challenges for router design.

Routers have traditionally been implemented purely in software. Because of the software implementation, the performance of a router was limited by the performance of the processor executing the protocol code. To achieve wire-speed routing, high-performance processors together with large memories were required. This translated into higher cost. Thus, while software-based wire-speed routing was possible at low-speeds, for example, with 10 megabits per second (Mbps) ports, or with a relatively smaller number of 100 Mbps ports, the processing costs and

architectural implications make it difficult to achieve wire-speed routing at higher speeds using software-based processing.

Fortunately, many changes in technology (both networking and silicon) have changed the landscape for implementing high-speed routers. Silicon capability has improved to the point where highly complex systems can be built on a single integrated circuit. The use of 0.35  $\mu$ m and smaller silicon geometries enables application specific integrated circuit implementations of millions gate-equivalents. Embedded memory and microprocessors are available in addition to high-density logic. This makes it possible to build single-chip, low-cost routing solutions that incorporate both hardware and software as needed for best overall performance.

#### 1.1.3 IP Lookup

Due to the rapid growth of traffic in the Internet, backbone links of several Gigabit/sec are commonly deployed. To handle Gigabit/sec traffic rates, the backbone routers must be able to forward millions of packets per second on each of their ports. Fast IP address lookup in the routers, which uses the packets destination address to determine for each packet the next hop, is therefore crucial to achieve the packet forwarding rates required.

#### **1.2 MOTIVATION**

In hardware based IP Lookup solutions for network routers, there are two main categories. These are namely ternary content addressable memory (TCAM) based and random access memory (RAM) based solutions. RAM based solutions include dynamic or static random access memories (DRAM or SRAM) or Block RAM (BRAM) in FPGA or ASIC. Each prefix can be stored in a TCAM with not only using 0's or 1's but also using don't care values. A seach key (i.e. IP address) is compared to all entries cycle and only one matched result, which is the longest matching prefix, appears at the output in one clock cycle. Therefore, TCAM based solutions have been popular for implementing lookup functions in core routers [1]. However, they have high cost and high power consumption as major drawbacks in

addition to their unsuitability in adopting to new addressing and routing protocols [2, 3].

On the other hand, RAM based solutions offer higher memory access speeds, lower power consumption and higher density. To implement RAM based IP lookup architectures, generally tree type data structures for finding LPM are used and the trees are traversed appropriately during a search. However, multiple memory accesses may be needed to search an IP addresses in such structures. For improving the throughput, various pipelined architectures have been proposed [4, 5] the main idea being the storage of a lookup table (represented for example as a binary tree) of a router on seperate and multiple memory elements. When an IP search is in progress in a pipeline, another incoming search key can be admitted into the system. Although the throughput is improved in pipelined solutions, straightforward mapping of the tree on the pipeline stages makes an unbalanced memory distribution inevitable. One of the possible solutions to unbalanced memory problem was proposed earlier using two dimensional, parallel, intersecting, circular and variable length pipelines [6,26]. Our implementation within the scope of this thesis provides minor modifications on the work of [6] to adapt it to be implemented in an FPGA rather than an ASIC.

In [6], nothing was mentioned abour initializing RAM contents for each stage of the pipeline and hence we also proposed loading and updating of RAM contents in each processing element described in Section 4.1.

## **1.3 CONTRIBUTIONS**

- We re-designed and adopted an existing SRAM based pipelined architecture, named SAFIL [6] for FPGA implementation.

- We added load and update attributes to SAFIL.

- We utilized FIFOs in CRs in SAFIL to prevent possible head of line blocking.

- We augmented SAFIL by designing a data flow manager (DFM) module in each PE to manage different type of incoming SAFIL frames.

- We implemented and simulated the modified SAFIL structure in the form of a BRAM based pipelined 8x8 torus architecture on an FPGA using Xilinx ISE and Modelsim Simulator.

## **1.4 OUTLINE**

The rest of the thesis is organized as follows. Chapter 2 covers the background and related work for IP lookup approaches. Our array design for trie-based IP lookup and update is discussed in Chapter 3. Chapter 4 introduces the proposed IP lokup architecture and its implementation on FPGA. Finally, Chapter 5 summarizes and concludes our work.

## **CHAPTER 2**

# **IP LOOKUP APPROACHES**

In modern IP routers, Internet Protocol (IP) lookup forms a bottleneck in packet forwarding because the lookup speed cannot catch up with the increase in link bandwidth. To deal with this problem, various software and hardware based solutions have been proposed for over 20 years. In this chapter, a brief overview of prior work on IP lookup solutions will be presented.

#### **2.1 SOFTWARE BASED SOLUTIONS**

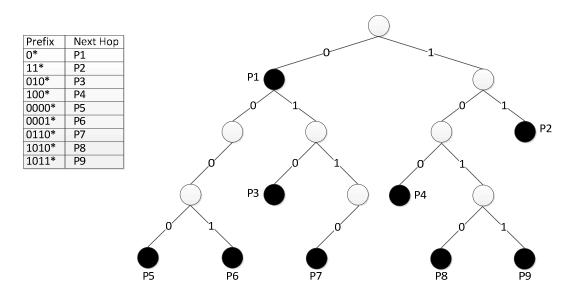

In IP lookup, the simplest and most popular data structure is *binary trie*. Each node in trie contains two pointers, the left-child pointer and the right-child pointer. Moreover if a trie node contains a valid prefix (corresponding to a routing table entry), then a next hop information (port number) associated with that prefix is also stored in a trie node. Figure 2-1 illustrates a sample prefix table and its corresponding binary trie.

In the rest of this text, the following terms are used:

- *Prefix node* is any trie node that corresponds to a valid prefix (marked as black)

- *Leaf prefix node* is a leaf node which is a valid prefix node (black leaf)

In a trie data structure, a node does not hold any prefix explicitly but the path from the root to another node corresponds to a prefix implicitly.

Figure 2-1 A Prefix Table and Corresponding Binary Trie

Any search operation begins with the root node. According to the bits of the IP address, operation continues traversing the trie from parent to child nodes. If following bit of IP address is "0", search continues towards left child node, otherwise right child node. While traversing, port result is updated if a valid node is encountered. Search operation terminates if a null child node or a leaf node is reached. The last matched prefix is selected as the longest matched prefix. For instance, a search key starting with 1010 will match the leaf prefix node whose next hop is P8 according to longest prefix mathing (LPM) rule in Figure 2-1. Update operations such as prefix insertion, deletion and route changes are easy to implement in a binary trie structure. On the other hand, search operation in a binary trie needs 32 memory accesses for IPv4 and 128 memory accesses for IPv6 in the worst case and hence lookup time gets longer.

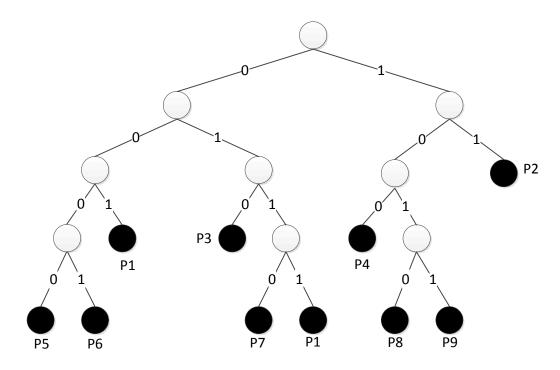

When all the prefix nodes are pushed to leaves, then a binary trie is called a leafpushed binary trie [7]. In a leaf-pushed binary trie, a non-leaf node contains only pointers to its children and the leaf node contains only a next hop information associated with the corresponding prefix. Figure 2-2 shows the leaf-pushed version of the binary trie in Figure 2-1.

Figure 2-2 The Leaf Pushed Version of the Binary Trie in Figure 2-1

Software based IP lookup solutions are generally based on algorithms that use binary trie. These software approaches are scalable but slow to work in line speeds [8]. To accelarate software based lookup, various solutions were proposed. The search time and the memory performance of a binary trie can be increased with *path compression technique*, which was first proposed by [9]. With this method, any node of a trie can be omitted if it has only one child node to make the path from root node to leaf node shorten. In order to keep the record of removed internal nodes, each node must store a skip value and bit string. The skip value stores the number of bits to be skipped on the path. The bit string stores missing bits from the last skip operation.

#### **2.2 HARDWARE BASED SOLUTIONS**

Altgough software based solutions are simple and scalable, they are slow to work in line speeds [8]. To improve performance and especially the throughput, various hardware based solutions were proposed using either SRAM or TCAM based memory technologies. And recently, ASIC or FPGA based solutions have also appeared in the literature [10, 11, 12, 13, 14].

#### **2.2.1 SRAM Based Solutions**

Single SRAM based IP lookup solutions are in need of multiple memory accesses during the tree traversal for finding the matched port result. To increase the throughput, various SRAM based pipelined solutions have been proposed. A binary trie can be implemented in an SRAM based pipelined architecture using multiple static random access memory elements. Each stage in binary trie is represented by an SRAM block. Therefore, the number of stages should be equal to the SRAM blocks utilized. The number of memory accesses is then determined by the average depth of the trie that stores a part or all of the routing table. Each search operation can access a seperate memory block only once during a search if each stage of the binary trie is utilized seperately. During a search that checks whether an IP address matches a prefix or not, a new incoming search request must wait for the on-going lookup operation to finish up.

IP lookup in binary tries need multiple memory accesses in order to find LPM node. In a pipelined architectures, the trie is mapped onto the stages of the pipelines. The trie traversal is then performed on these separate and multiple memory elements (SRAMs) through the pipeline. Enough memory stages exist and no stage is accessed more than once during a search in a conventional one dimensional pipeline architecture. Although throughput is improved using a pipeline, an ordinary mapping of the binary trie onto the pipeline stages results in unbalanced memory utilization. Unbalanced trie node distribution over pipeline stages decreases the overall performance of the architecture. Various different solutions have been proposed to address the memory balancing problem [4, 5, 15, 16].

In [4], a ring pipeline architecture, which allows search to start from any pipeline stage, is proposed. This approach is based on dividing the binary trie into subtries and choosing each subtrie starting point to a different pipeline stage to create a balanced pipeline. In this approach, there are two different data path. First one is for finding the starting pipeline stage and the second one is for lookup operation. The matched port result propagates to the final pipeline stage to appear at the output. The throughput of the described Baboescu et al. architecture is 0,5 lookups per clock cycle.

In [5], the previous method is improved with an approach called Circular, Adaptive and Monotonic Pipeline (CAMP). Apart from previous approach, at any pipeline stage, there are two different input and one output stage. In this architecture, maximum 0,8 lookups per clock cycle are possible.

The throughput of pipelined architectures can be improved by using multiple pipelines. Jiang et al. [12] proposed the first parallel multipipeline architecture Parallel Optimized Linear Pipeline (POLP) in which each pipeline can operate concurrently to increase the speed up rate. POLP is improved further in later studies. For example a bidirectional linear pipeline is introduced in [17]. To improve POLP power effciency, a hybrid SRAM/TCAM selector unit is also proposed in [18] and [19], the aim being shortening pipeline lengths by introducing hybrid partitioning schemes.

#### 2.2.2 T-CAM Based Solutions

Binary CAM is the simplest type of CAM which uses data search words consisting entirely of 1s and 0s. Ternary CAM (TCAM) allows a third state of "Don't Care" bits in the stored dataword, thus adding flexibility to the search. For example, a ternary CAM might have a stored word of "10XX0" which will match any of the four search words "10000", "10010", "10100", or "10110". The added search flexibility comes at an additional cost over binary CAM as the internal memory cell must now encode three possible states instead of the two of binary CAM. This additional state is typically implemented by adding a mask bit ("care" or "don't care" bit) to every memory cell. TCAM is more powerful because don't cares may act as wildcards during a search and hence LPM can be solved naturally in one cycle [20].

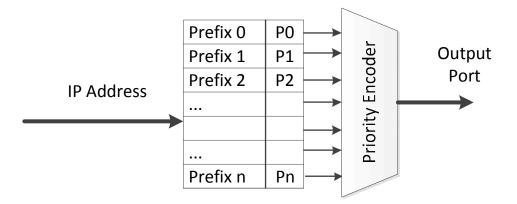

As shown in Figure 2-3, in TCAM architectures, prefixes are stored in sorted order based on prefix lengths. When a search key (i.e. an IP address) is admitted into conventional TCAM, incoming bits are distributed to all the entries. The matched entries activate outputs that are fed into a priority encoder. If more than one outputs

are activated, the priority encoder decides which entry is LPM and outputs the longest matching one.

Figure 2-3 TCAM

Although TCAM-based solutions are straightforward and famous, they are expensive, power consuming, and offer little scalability and adaptability to new addressing and routing protocols [2, 3, 21, 22]. While a search is in progress, in which every memory block of the entries are used in active state, TCAM modules consumes high power. Moreover, updating a memory cell may require multiple entry moves, which means that long updating progress may be needed. Additionally, low scalability may arise in the case of changing the order in the priority encoder when updating the contents of the memory cells.

# **CHAPTER 3**

# ARRAY DESIGN FOR TRIE BASED IP LOOKUP AND UPDATE

#### **3.1 INTRODUCTION**

SRAM based IP lookup solutions are in need of multiple memory accesses to traverse the tree to perform a single search request. Since only one memory access is allowed during a lookup process for an IP address, a new incoming lookup request should wait until previous search is completed. Several researchers have explored various SRAM based pipelined architectures to improve the througput [4,5].

In these architectures, only a single pipeline stage is used for mapping a binary trie. This single pipeline stage is composed of multiple connected sub blocks that represent a node in the trie. Each sub block utilizes an SRAM unit to store node information. Each new search request starts in the boundary sub block and proceed until the LPM node is encountered.

An SRAM based multi pipeline [13, 15, 16, 18, 19] approach improves the throughput considerably by using parallel non-intersecting and costant length pipelines having m different sub blocks that contains SRAM units. Each sub block is connected to each other with n pipelines.

In this chapter, we review and present a Block RAM based array architecture for fast IP lookup with update functionality, which is a slightly modified version of [6].

#### **3.2 MOTIVATION**

In this thesis, we implement a two dimensional multiple pipelined architecture proposed in [6] that has parallel, circular search capabilities on intersecting and variable length pipelines.

In our implementation, we added FIFOs to the system to prevent head of line blocking in Contention Resolvers and a Ram Data Loader module to load or update RAM contents of the system. We also modified the PE architecture slightly to adapt it to Xilinx FPGAs and used BRAMs instead of separate SRAMs.

# **3.3 ARRAY ARCHITECTURE for FAST IP LOOKUP WITH UPDATE CAPABILITY**

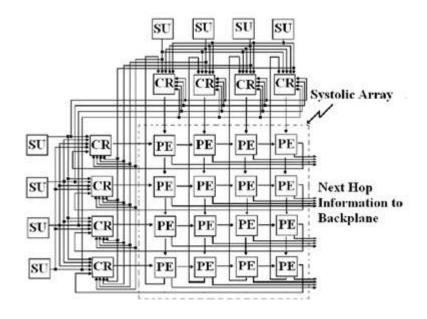

SRAM based array architecture for fast IP lookup (SAFIL) is composed of specially designed processing elements (PEs) that are connected like a 2D torus topology but is operated like a systolic array to benefit from multi-pipeline parallelism [6]. In the following, the systolic array like structure and 2D torus network topology are explained briefly:

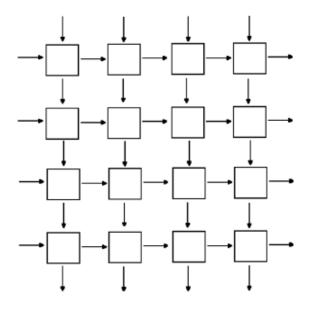

<u>Systolic array</u>: A *systolic array* is a pipe network arrangement of processing units called cells. It is a specialized form of parallel computing, where cells (i.e. processors), compute data and store it independently of each other. Each processing element inputs data from one or more neighbors (e.g. North and West) and processes it. The output of the process is given to the neighbors in the opposite direction (e.g. South and East). The task of one cell can be summarized as receive, compute and transmit. The communication with the outside world occurs only at boundary cells. The processing elements share the information with their neighbors after performing the needed operations on the data. Figure 3-1 demonstrates an example of 4x4 systolic array architecture. The systolic arrays have attractive

properties such as synchronization, modularity, regularity, locality, finite connection, parallel pipelining and modular extendibility [6].

Figure 3-1 A 4x4 Systolic Array

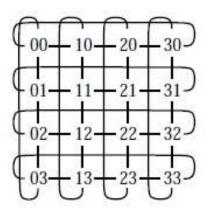

<u>2D-torus</u>: 2D torus is a *k-ary* 2-*cube* network where  $k \ge 3$ . A *k-ary n*-cube network where *n* is the dimension of the cube and *k* is the radix, is a well-known topology used in communication networks and high performance computing architectures. It consists of  $N = k^n$  nodes arranged in *n*-dimensions, with *k*-nodes per dimension. Figure 3-2 illustrates 4-*ary* 2-*cube* network or 4 x 4 torus.

Figure 3-2 4x4 Torus

The topology in SAFIL is like a *k-ary* 2-*cube*; in particular a 2D torus, where  $k \ge 3$ , in which the wrap-around connections are not between PEs but rather between a PE and a contention resolver (CR) (Figure 3-3). As a result, SAFIL can be regarded as an array of PEs that are connected in a 2D torus topology and is operated like a systolic array to benefit from multi-pipeline parallelism for trie-based IP lookup.

Figure 3-3 4x4 SAFIL Architecture [6]

In a systolic array in general;

*i*) a PE is similar to a central processing unit except for a program counter,

ii) the operations are synchronous and transport-triggered,

*iii*) the communication with the outside world occurs only at the array boundary,

*iv*) there exist structured data parallelism, strict flows along rows/columns and interaction of data streams at the PEs.

SAFIL is not exactly a systolic array since it has the above (i)-(iii) characteristics but not (iv) [6].

#### **3.3.1 IP Lookup Process**

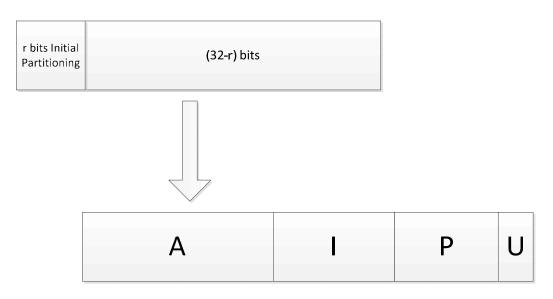

An IP Lookup Process starts at an available Selector Unit (SU). The searched IP address arrives at input side of SU to start a new search operation. Then this SU, using initial r bits of the IP address, finds the input stage PE and the memory address of the corresponding subtrie root in this PE. Then a SAFIL Frame is constructed as shown in Figure 3-4.

Figure 3-4 SAFIL Frame

A SAFIL Frame consists of the following four fields:

- A-field holds the least significant (32-*r*) bits of the IP address being searched (most significant *r* bits are to be used for initial partitioning).

- I-field is a pointer to the Block RAM in PE.

- P-field holds the search result that the IP packet will use to reach to the next router

- U-field holds the type of the frame (IP Lookup or IP Update).

Since more than one search requests may arrive at an input stage PE, in this case contention occurs. The contention resolver (CR) is used to get a SAFIL frame that

contains the IP address to be processed into the system. When contention occurs, only one of the contented packets is selected and the others are put on hold using a suitable strategy. Each SU is connected to every other CR. Number of SUs is a design choice and defines the maximum number of search requests that can be admitted to the system simultaneously. The endpoints of each row and column are connected to their corresponding CRs. Hence a pipeline corresponding to a branch in prefix tree can be mapped onto the array of PEs by wrapping it around the corresponding row or column. If a circulating search exists, other search requests from SUs are accepted by CR into "inside FIFOs". The backplane obtains the search result from any of the PEs.

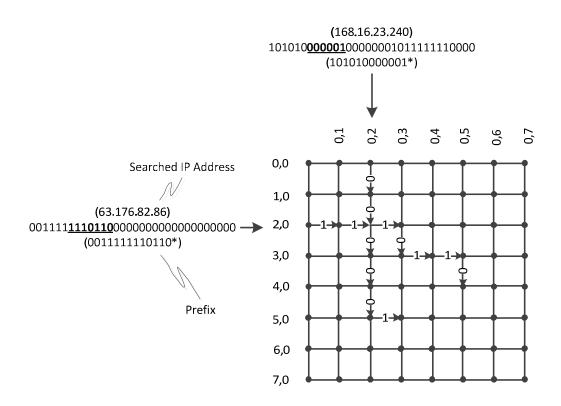

Figure 3-5 Propagation of a SAFIL frame during lookup

Figure 3-5 illustrates the lookup process for two different addresses on an 8x8 SAFIL system assuming an initial stride for partitioning as r = 8. These two search keys are assumed to enter into the system at the same time. While search key is traversing through each PE, SAFIL frame is updated and mapped to one of the child node according to MSB of it. If the stored prefix node is valid, the port number field

in the traversing SAFIL frame is updated. At the end of the search operation, port number is output to the backplane.

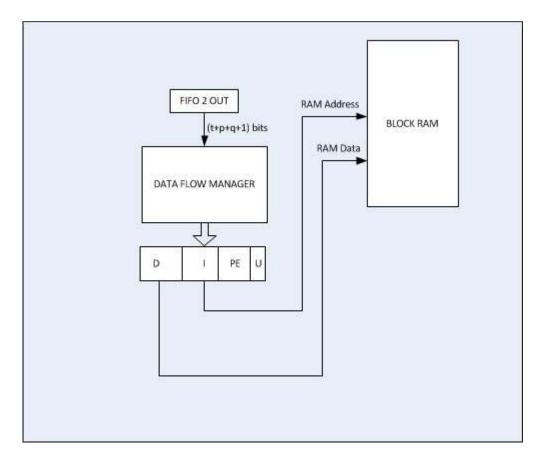

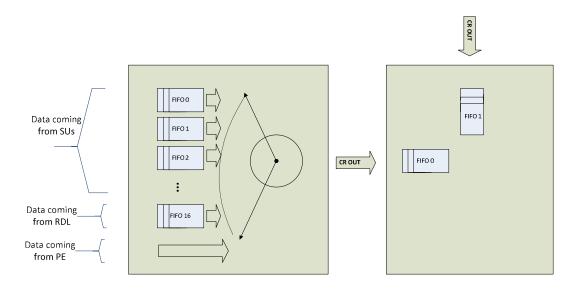

### 3.3.2 IP Lookup Table Update and Propagate Process

A binary trie is initially partitioned into several disjoint subtries. These subtries are then mapped on SAFIL starting from the input stage PE (to which CRs ans SUs are connected). The Block RAM contents of each PE is loaded by Ram Data Loader by constructing SAFIL Update Frames. This unit is connected to all CRs located in the northern side of the structure.

A SAFIL Update Frame (shown in Figure 3-6) consists of four fields, namely *m*-bit ram data (D), *p*-bit Block RAM index (I), *n*-bit PE ID code (PE) and 1-bit frame type (U). D-field holds *p*-bit Block RAM data that will be updated, I-field holds Block RAM Address, PE-field holds the identification code of the PE and U-field is the type of the frame (if SAFIL Update Frame U='1' otherwise U='0').

Figure 3-6 SAFIL Update Frame

An update process begins at Ram Data Loader (RDL) by constructing SAFIL update frame. This frame comes to the corresponding column (one of northern side CRs). Since each PE in one column has a unique ID, only one ID of the update packet will match the destination PE ID. The update packet propagates along with the column until the mached ID's are encountered. The propagation of the update packet between the PEs is named as "propagation process". If matching occurs in any PE, this is named as "update process".

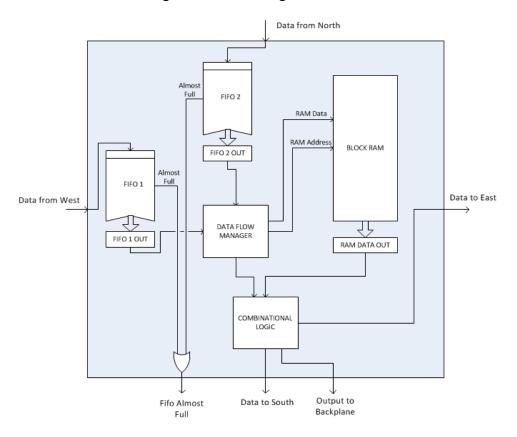

## **3.3.3 Processing Element**

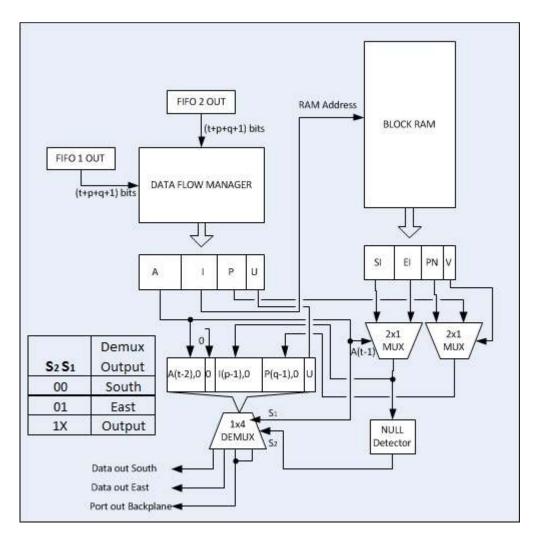

A PE consists of two FIFO queue blocks, a Block RAM, a Data Flow Manager and additional combinational logic as shown in Figure 3-7.

Figure 3-7 Block Diagram of the Processing Element (PE)

Each block in the PE is explained below:

<u>FIFO Block</u>: This block is used for buffering data coming from west or north side of the PE.

Block RAM: This memory element is used to store trie nodes.

<u>Data Flow Manager</u>: This unit is used for managing the data flow coming into PE. It manages two FIFOs using a Round Robin Scheduler by enabling only one of the FIFOs at each cycle. It also decides whether the incoming frame is a SAFIL Frame or a SAFIL Update Frame. Then, according to frame type, it starts one of either lookup, update or propagate processes.

<u>Combinational Logic</u>: This logic is used for deciding whether the IP address searched encounter an LPM or not in the current node of the trie (LPM node: there

is a valid prefix and a match in the current node). With this decision, this logic can modify the SAFIL Frame and put this frame at the output (either south or east) or send the result (i.e., output port information) to the backplane.

A SAFIL Frame consists of four fields, namely *t*-bit address (A), *p*-bit Block RAM index (I), *q*-bit port number (P) and 1-bit frame type (U). A-field holds the least significant *t*-bits of the IP address being searched (most significant (32-*t*) bits are to be used for initial partitioning, I-field is a pointer to the Block RAM in PE, P-field holds the search result that the IP packet will use to reach to the next router and U-field is the type of the frame. (if SAFIL Frame U='0', otherwise U='1')

In addition to the (t+p+q+1)-bits wide data bus connection, a single bit data available (DAV) signal between two neighboring PEs is also used. Each Block RAM unit stores (2p+q+1) bits in each entry, having two p-bit fields of south (SI) and east (EI) Block RAM indices, a q-bit port number (PN) field and a valid (V) bit (indicating whether the current trie node is a prefix or an intermediate node). A PE modifies the P-field in SAFIL frame if the current node is a valid prefix node. A SAFIL frame carries the latest longest matched port number through each traversed PE not to backtrack from the last stage when a search terminates.

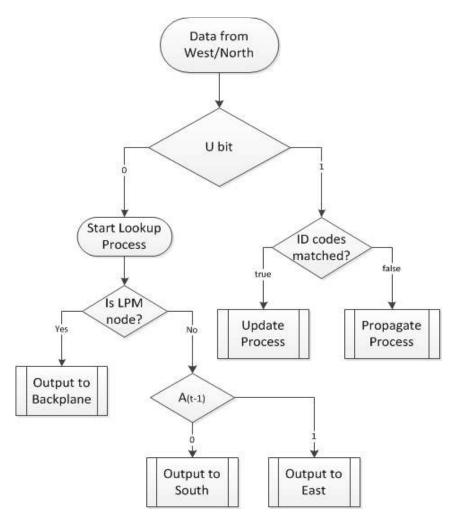

Each PE's behavioral structure is shown in Figure 3-8. In each two clock cycle, a PE functions as follows:

- i. SAFIL/SAFIL Update Frame arrives from northern or western input ports

- ii. Data Flow Manager finds the Frame type:

- iii. If the frame is a SAFIL Frame, Combinational Logic decides if the current node is an LPM node or not.

- a. If LPM node, q-bits wide port result is output to backplane by using the information read with a single access from Block RAM.

- b. If not, Combinational Logic modifies the frame by using the information read with a single access from Block RAM and this modified frame is guided to one of eastward or southward output ports.

If the frame is a SAFIL Update Frame, Data Flow Manager modifies the data row of the relevant Block RAM.

Figure 3-8 Flowchart of Data Processing in PE

Figure 3-9 Detailed Block Diagram of a PE (Lookup Process)

Figure 3-9 presents the block diagram of a Processing Element in SAFIL for lookup process.

Figure 3-10 Block Diagram of a PE (Update Process)

Figure 3-10 presents the block diagram of a Processing Element in SAFIL for update process.

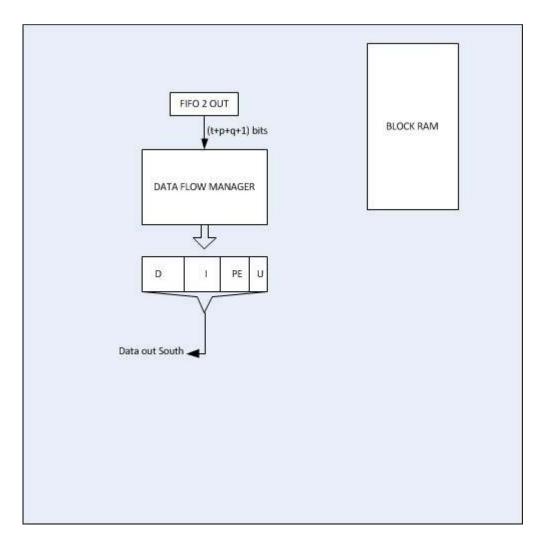

Figure 3-11 Block Diagram of a PE's Propagate Process

Figure 3-11 gives the block diagram of a SAFIL Processing Element's propagate process.

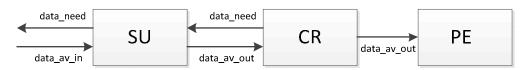

# 3.3.4 Selector Unit

This unit is used for initial partitioning and constructing SAFIL Frames. Selector Unit is a combinational logic that inputs the destination IP address and processes its initial *r*-bits (r is used for initial partitioning and was discussed in Section 3.3.1). SU functions as follows:

- i. It finds the input stage PE by checking the initial r-bits of the IP address.

- ii. It constructs the SAFIL Frame by adding the memory address of the root node of the corresponding subtrie.

iii. It puts the constructed SAFIL Frame on its output port.

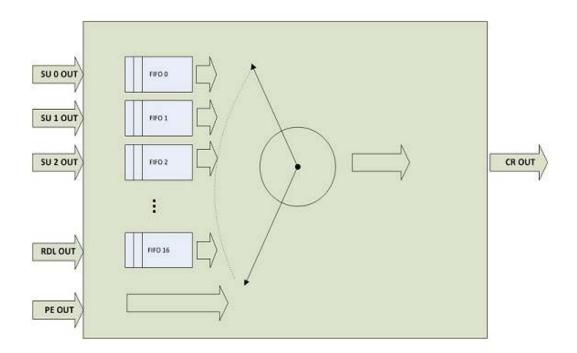

## **3.3.5** Contention Resolver

This unit is used for buffering and arranging incoming data from different SU's and wrapped around eastern and southern PE's. Since more than one search request may arrive at an input stage PE, there is a need for a mechanism in order to accept an IP address into the system to be searched. Therefore, only one search operation will be accepted by a Contention Resolver. When contention occurs, only one of the contented packets is selected and routed to the connected PE while the others being stored in FIFO's in each Contention Resolver.

Since more than one packet may arrive at each CR in one cycle, we implemented a FIFO block in each port in a CR to accept incoming data. Since more than one packet want to leave CR at the same time, there is also a need for arranging these packets. A suitable strategy, such as Round Robin for example, can be employed for this operation.

CR functions as follows:

- i. SAFIL Frames or SAFIL Update Frames arrives at the input of the CR.

- ii. At each input port, receiving data enters the corresponding FIFO.

- iii. CR enables one of the FIFOs for taking data to the output port.

## **3.3.6 Congestion Control Unit**

This unit is designed and used to prevent possible FIFO overflow in any PE. Since FIFO's in each PE have limited size, packet loss due to queue overflow is always possible. Using a simple congestion control mechanism, one can control the incoming traffic rate by activating or deactivating the input ports if any of the FIFO's is almost full. A one bit connection from each PE's queue to congestion control unit (CCU) is sufficient for this purpose. One possible congestion control algorithm in activating and deactivating the SU's is additive increase multiplicative

decrease strategy. If the FIFO queue usage exceeds the predefined threshold value, then half of the SUs are deactivated to decrease the load at the input of the whole system. SUs to be deactivated can be chosen arbitrarily because each SU may receive packets from the input queue and has direct connections to each CR. If there is no congestion, number of active SUs are increased by one at each cycle.

CCU functions as follows:

- i. If one of the FIFO's in any PE reaches to predefined threshold value, one bit *almost full signal* becomes logic '1'.

- ii. CCU deactivates SUs with multiplicative decrease strategy. For example, if *n* SU's are active at some time and one of the FIFO's is almost full, CCU deactivates half of the SU's not to accept a search key (IP Address) anymore having *n*/2 active SUs for the next cycle.

- iii. CCU activates SUs with additive increase strategy. For example, if n SU's are active at some and none of the FIFO's are almost full, CCU activates one of the inactive SUs making a total of n+1 SU's are active.

## 3.3.7 Ram Data Loader

This unit is used for loading and updating the contents of the Block RAM's inside each PE. Each load or update operation starts at Ram Data Loader (RDL). RDL examines the incoming packet and finds the column, which contains the PE that will be updated. Then, RDL constructs SAFIL Update Frame and sends it to CR of the corresponding column. As was explained in Section 3.3.2, SAFIL Update Frame travels through this column until the ID of the PE and Frame matches. If such a match occurs, the selected PE content will be updated.

Since the update process can be performed while lookup processes are running, the system can be modified without being stopped, which is very beneficial.

# **CHAPTER 4**

# FPGA IMPLEMENTATION OF THE ARRAY ARCHITECTURE FOR FAST IP LOOKUP WITH UPDATE CAPABILITY

Our Block RAM based array implementation of SAFIL is composed of 8x8 specially designed processing elements (PEs) that are connected like a 2D torus topology, buffered CRs that connects all SUs to corresponding PE, Ram Data Loader that is used for loading and updating RAM content and finally CCU that is used to regulate the incoming traffic. In this chapter, all of these blocks and sub modules will be explained and detailed including design and simulation studies.

## **4.1 PROCESSING ELEMENT**

A PE consists of two FIFO blocks, a Block RAM, a Data Flow Manager and additional combinational logic. The 49 bit input port of each PE is connected to west and north neighbors. The 49 bit output port of each PE is connected to east and south neighbors. Each PE is also connected to Congestion Control Unit (CCU) by one bit data line.

## 4.1.1 Design

The PE unit is composed of blocks and sub-units explained below:

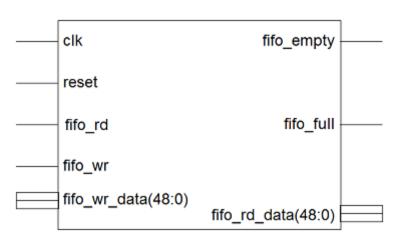

<u>FIFO Block:</u> This block is used for buffering data coming from western or northern sides of the PE.

FIFOs are implemented using distributed RAM's on FPGA. To achieve a high speed IP lookup process, FIFO Blocks are designed with "first word fall through" attribute. With this, data written to an empty FIFO appears on the read port at the same clock cycle.

To avoid data overflow in FIFO, *fifo\_full* output signal is used for warning CCU to reduce incoming traffic rate. To do this, FIFO Block asserts this almost full signal to high when FIFO memory usage reaches the predefined threshold level.

Since SAFIL Frame and SAFIL Update Frame are 49 bits wide, FIFO width is 49 bits and depth can be choosen as a result of some optimization trials. In our design, FIFO depth was selected as 1024.

FIFO

The schematic view of FIFO is given in Figure 4-1.

Figure 4-1 FIFO Input and Output Signals

Each in and out signals of FIFO are described in Table 4-1.

| Signal Name  | Signal<br>Type | Signal<br>Length | Signal Description                                                                                                                                               |

|--------------|----------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| rst          | In             | 1 bit            | Reset signal is used in order to set all<br>configuration registers to zero (low) and to<br>bring the FIFO module into a state that is<br>ready to receive data. |

| clk          | In             | 1 bit            | The clock signal is used in order to synchronize FIFO with other modules                                                                                         |

| fifo_rd      | In             | 1 bit            | The read enable signal                                                                                                                                           |

| fifo_wr      | In             | 1 bit            | The write enable signal                                                                                                                                          |

| fifo_wr_data | In             | 49 bits          | Data written to FIFO                                                                                                                                             |

| fifo_empty   | Out            | 1 bit            | Indication signal of fifo empty                                                                                                                                  |

| fifo_full    | Out            | 1 bit            | Indication signal of fifo is almost full                                                                                                                         |

| fifo_rd_data | Out            | 49 bits          | Output data of FIFO                                                                                                                                              |

Table 4-1 FIFO Signal Descriptions

The VHDL source code for designing FIFO is given in Appendix A.

Block RAM: This memory element is used to store trie nodes.

Each Block RAM has 32 bits width and  $2^{13} = 8192$  bits depth. Total memory size for one PE is 8k x 32 = 256 kbits. Since the whole system consists of 64 PEs, total memory size is 64 x 256 kbits = 16,777,216 mbits  $\approx$  2 MByte.

Block RAM's were generated with IP CORE in Xilinx ISE as shown in Figure 4-2.

| Symbol Ø×<br>Aconsult 250<br>Block Memory Generator<br>Component Name ram<br>Memory Type Single Port RAM<br>Clocking Options<br>Comman Clock<br>ECC Options<br>ECC Type NeECC<br>Write Enable<br>Byte Size 0 bits<br>Algorithm<br>Defines the algorithm used to concatenate the block RAM primitives. See the datasheet for<br>more information.<br>Minimum Area<br>Low Power<br>Fixed Primitives<br>Primitike (Write Port A) : Bic2<br>Actual Primitive(S) Used : 16bo2, 8oc2                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ocuments View                                                                                      |                                                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|------------------------------------------------------------|

| ACDERA[12:0]       Bindpit op         BINdpit op       Sampan         Bits       Algorithm         Bits       Algorithm         Define information.       Wintermation.         Immather of Block RAM primitives. See the datasheet for more information.         Immather of Block RAM primitives (any ip)       Fixed Primitives         Primitive (Write Port A) :       Block | Symbol đ                                                                                           | Logic RE Block Memory Generator                            |

| ADDRA(12.3)       BOUTS(3)         BINA(12.3)       SECCTYPE         BINA(12.3)       SECTYPE         BINA(13.3)       SECTYPE         BINA(13.3)       SECTYPE         BINA(13.3)       SECTYPE                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                    | Memory Type Single Port RAM  Clocking Options Common Clock |

| Defines the algorithm used to concatenate the block RAM primitives. See the datasheet for more information.   Minimum Area  C Low Power  Fixed Primitives  Primitive (Write Port A) : Block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | EINA(31:0)<br>ENA →→<br>SEOCIA → → SEITERSI<br>WEA(2:0) → → CETTERSI<br>RECK. → → REACORECCI (1:0) | ECC Type No ECC -                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Handbard and                                                                                       |                                                            |

Figure 4-2 IP Core Menu for Block RAM Generation

Data Flow Manager (DFM): This unit is used for managing the data flow coming into PE. It manages two FIFOs with respect to a round robin schedule by enabling only one FIFO at each cycle. It also checks if the incoming frame is a SAFIL Frame or a SAFIL Update Frame and then it starts either lookup, update or propagate processes according to frame type.

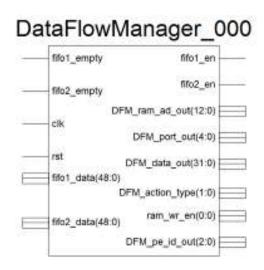

The schematic view of Data Flow Manager is given in Figure 4-3.

Figure 4-3 Data Flow Manager Schematic View

The VHDL source code for designing DFM is given in Appendix B.

<u>Combinational Logic</u>: This logic is used for deciding whether the IP address searched hits an LPM node or not. With this decision, the logic can modify the SAFIL Frame and directs it to output (either south or east) or send the output port information to backplane.

Combinational Logic inputs the outputs of the DFM.

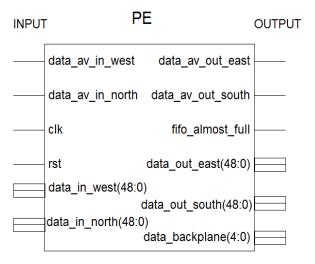

All of these blocks and sub modules form the PE, whose input and output signals are illustrated in Figure 4-4 Processing Element

Each in and out signals of PE are described in Table 4-2 and the VHDL source code for designing PE is given in Appendix C.

Figure 4-4 Processing Element

| Signal Name       | Signal<br>Type | Signal<br>Length | Signal Description                                                                                                                                                  |

|-------------------|----------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| rst               | In             | 1 bit            | Reset signal is used in order to set all<br>configuration registers to zero (low) and<br>to bring the PE module into a state that<br>is ready to receive data.      |

| clk               | In             | 1 bit            | The clock signal is used in order to<br>synchronize different parts of the PE<br>module (cycling at a rate less than the<br>worst-case internal propagation delays) |

| data_av_in_west   | In             | 1 bit            | The available signal of data from west                                                                                                                              |

| data_in_west      | In             | 49 bits          | The data coming from west side of the PE                                                                                                                            |

| data_av_in_north  | In             | 1 bit            | The available signal of data from north                                                                                                                             |

| data _in_north    | In             | 49 bits          | The data coming from north side of the PE                                                                                                                           |

| data_av_out_east  | Out            | 1 bit            | The available signal of data to east                                                                                                                                |

| data_out_east     | Out            | 49 bits          | The data going out to east side of the PE                                                                                                                           |

| data_av_out_south | Out            | 1 bit            | The available signal of data to south                                                                                                                               |

| data_out_south    | Out            | 49 bits          | The data going out to south side of the PE                                                                                                                          |

| data_backplane    | Out            | 5 bits           | The search result (port number) of the IP address looked up                                                                                                         |

| fifo_almost_full  | Out            | 1 bit            | The signal indicating one of FIFOs in the PE is almost full                                                                                                         |

## 4.1.2 Simulation

## **SCENARIO 1**

**Aim:** To show and verify southern and eastern port outputs for simultaneously applied predefined input data from northern and western sides of the PE. (Lookup Process)

#### **Test Code:**

Pre-Statement: Initially, reset input is set to "high" for 3 clock cycles. After reset state, data from west and north is sent to the input ports consecutively. Since the input data is of type SAFIL Frame, U-field is '0'. The Block RAM data content in 0000000000001 address is hex 000800EB binary 0000000000001 ( 000000000011 10101 1). According to this scenario, the node that refers to tested PE is an intermediate node. Therefore, there shouldn't be any backplane output. Since  $A_{t-1} = 0$  for the data from west, the southern available output should be high for one clock cycle after some delay. Since  $A_{t-1} = 1$  for the data from north, the eastern available output should be high for one clock cycle after some delay.

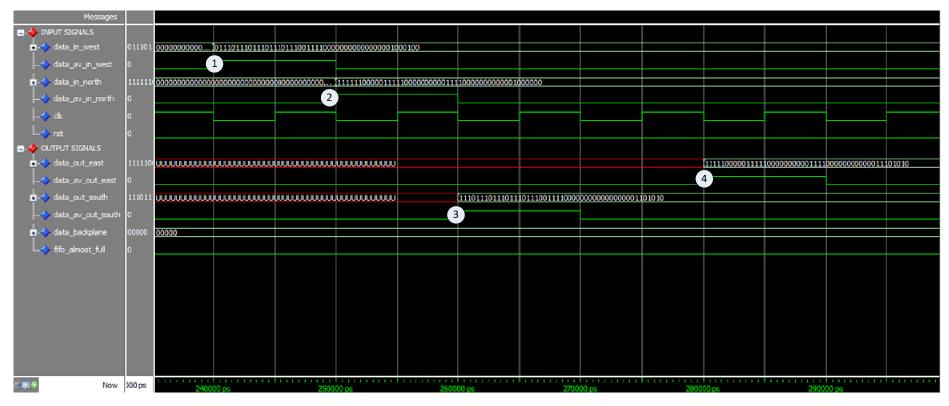

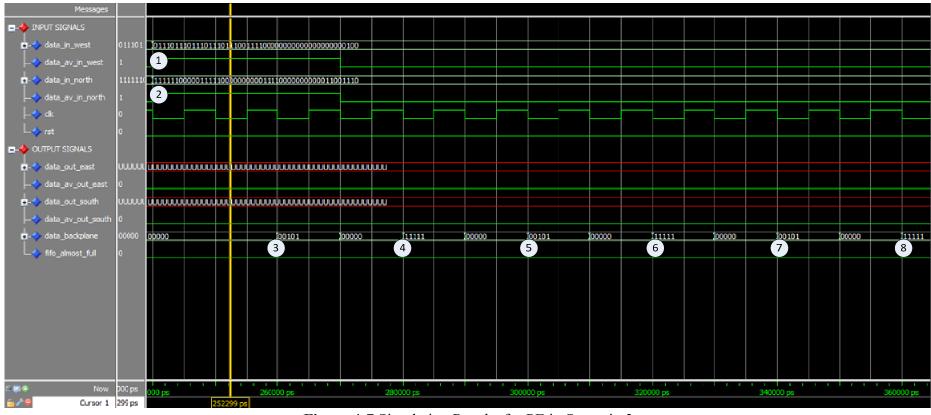

Figure 4-5 Simulation Results for PE in Scenario 1

The result of the simulation is given in **Figure 4-5**. In this scenario, *data\_av\_in\_west* appears at label 1 and *data\_av\_in\_north* appears at label 2. Since the input data is in the form of intermediate node data, at labels 3 and 4, *data\_av\_out\_south* and *data\_av\_out\_east* are activated after 2 clock cycles.

#### **SCENARIO 2**

**Aim:** To show and verify southern and eastern port outputs for simultaneously applied predefined input data from northern and western sides of the PE and Round-Robin Scheduler inside the DFM of the PE. (Lookup Process)

#### **Test Code:**

**Pre-Statement:** Initially, reset input is set to "high" for 3 clock cycles. After reset state, data from west and north is sent to the input ports <u>concurrently</u> for 3 clock cycles. Since the input data is of type SAFIL Frame, U-field is '0'. The Block RAM data content in 000000000100 address is hex F4FFFFFF

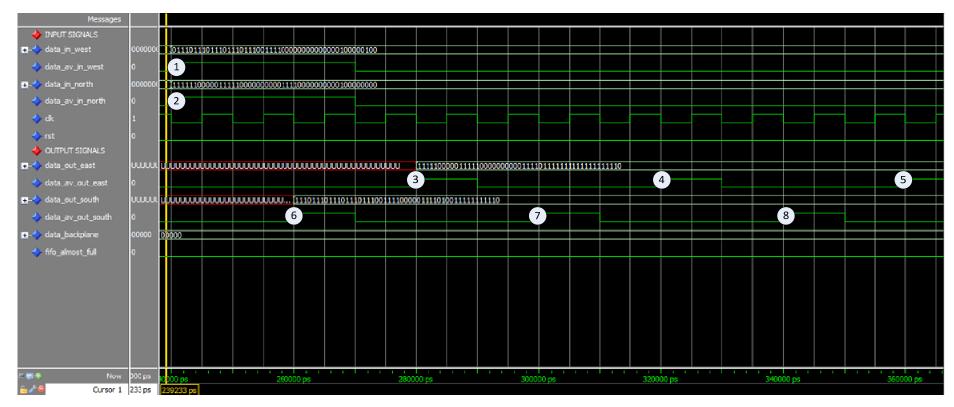

Figure 4-6 Simulation Results for PE in Scenario 2

The result of the simulation is given in **Figure 4-6**. In this scenario, *data\_av\_in\_west* and *data\_av\_in\_north* appear at labels 1 and 2 during 3 clock cycles. Since the input data is in the form of intermediate node data, at labels 3, 4, 5, 6, 7, 8; *data\_av\_out\_south* and *data\_av\_out\_east* are activated by the Round Robin Scheduler.

#### **SCENARIO 3**

**Aim:** To show and verify backplane outputs for simultaneously applied predefined input data from northern and western sides of the PE (Lookup Process)

## **Test Code:**

Figure 4-7 Simulation Results for PE in Scenario 3

The result of the simulation is given in **Figure 4-7**. In this scenario, *data\_av\_in\_west* and *data\_av\_in\_north* appear at labels 1 and 2. Since the input data is in form of longest prefix node data, at labels 3, 4, 5, 6, 7 and 8 *data\_backplane* output is activated.

#### **SCENARIO 4**

**Aim:** To show and verify southern output for predefined input data applied from northern side of the PE for IP update process (Propagate Process)

## **Test Code:**

**Pre-Statement:** Initially, reset input is set to "high" for 3 clock cycles. After reset state, data from north is sent to the input port for 3 clock cycles. Since the input data is of type SAFIL Update Frame, U-field is '1'. Therefore, PE decides which process (Update or Propagate) to run. In this case, propagate process should run because PE ID and ID of the incoming SAFIL Update Frame does not match. Therefore, there exists data at the southern output port.

Figure 4-8 Simulation Results for PE in Scenario 4

The result of the simulation is given in **Figure 4-8**. In this scenario, *data\_av\_in\_north* appears at label 1. Since the input data is in form of propagate process data, at labels 2, and, 4 *data av out south* output is activated.

#### SCENARIO 5

**Aim:** To verify and show that Block RAM data contents can be loaded/updated via the update process (Update Process).

#### **Test Code:**

```

wait for 100 ns;

rst<='1';

wait for clk period*3;

rst <= '0';

wait for clk period*10;

data av in west \leq 0';

data av in north \leq 0';

wait for clk period;

data in west <= '1' & x"EEEE7800040";

data av in west \leq 1';

wait for clk period;

data av in west \leq = 0';

wait for clk period;

data in north \leq = '1' \& x''FFFFFFE0011'';

data av in north \leq = '1';

wait for clk period;

data av in north \leq = 0';

wait for clk period;

data in west \leq 1' \& x'' EEEEE7800040'';

data av in west \leq 1';

wait for clk period;

data av in west \leq 0';

```

**Pre-Statement:** Initially, reset input is set to "high" for 3 clock cycles. After reset state, data from west is sent to the input port for 3 clock cycles. First, a SAFIL Frame arrives at the western side of the PE. After 2 clock cycles, a SAFIL Update Frame appears in the Northen side. Since the input data is of type SAFIL Update

Frame, U-field is '1'. Therefore, PE decide which process (Update or Propagate) to run. In this case, update process should run because PE ID and ID of the incoming SAFIL Update Frame match. Finally, the same SAFIL Frame appears again at the western side of the PE to observe that the same SAFIL Frame provides a different SAFIL Frame output after ram update process.

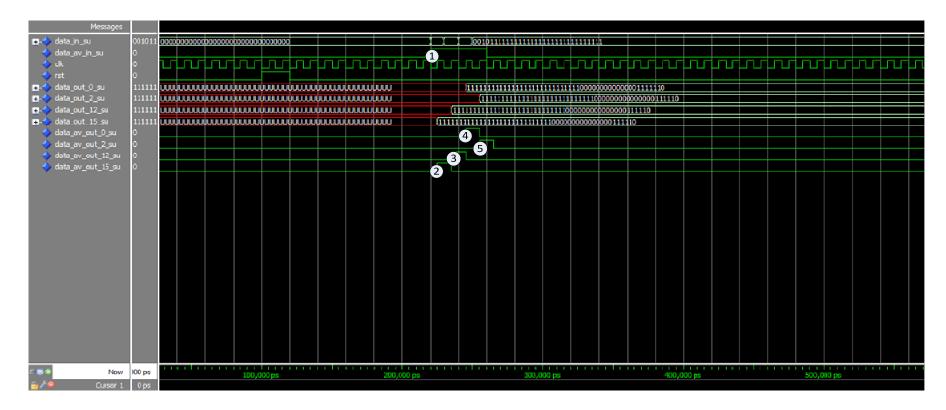

Figure 4-9 Simulation Results for PE in Scenario 5

The result of the simulation is given in **Figure 4-9**. In this scenario, *data\_av\_in\_west* appears for a lookup process at label 1. Then, *data\_av\_in\_north appears* for an update process at label 3. Then, *data\_av\_in\_west* appears for a lookup process again at label 2. Before the update process is completed, the corresponding output for *data\_out\_east* is activated at label 4. After the update process is completed, the corresponding output for *data\_out\_east* is activated at label 5.

# **4.2 SELECTOR UNIT**

This unit is designed and used for initial partitioning and for constructing SAFIL Frames.

## 4.2.1 Design

Just a 4x16 line decoder is sufficient for initial partitioning (Table 4-3). Using leftmost 4-bits of the key IP address, the search is directed to the corresponding CR and PE.

| Initial 4 Bit | <b>Output Port of SU</b> |

|---------------|--------------------------|

| 0000          | 0                        |

| 0001          | 1                        |

| 0010          | 2                        |

| 0011          | 3                        |

| 0100          | 4                        |

| 0101          | 5                        |

| 0110          | 6                        |

| 0111          | 7                        |

| 1000          | 8                        |

| 1001          | 9                        |

| 1010          | 10                       |

| 1011          | 11                       |

| 1100          | 12                       |

| 1101          | 13                       |

| 1110          | 14                       |

| 1111          | 15                       |

Table 4-3 Initial Partitioning Conversion

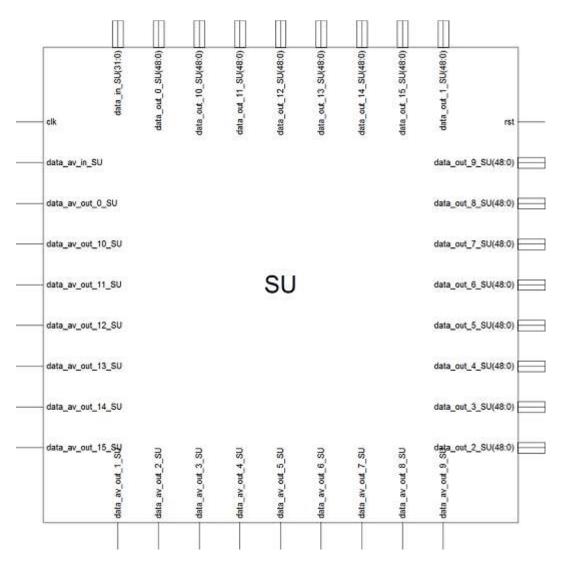

The 32-bit input port of each SU is connected to incoming traffic port, i.e. the IP address to be searched. The output ports of each SU are connected to all of the CR's input ports.

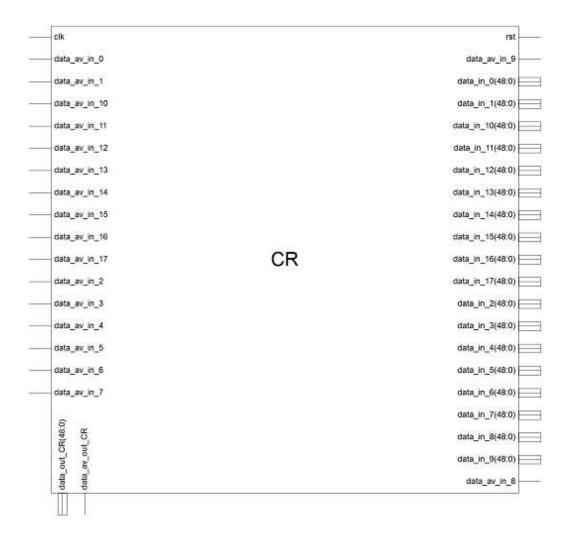

The schematic view of SU is given in Figure 4-10.

Figure 4-10 Selector Unit Input and Output Signals

In and out signals of SU are described in Table 4-4.

| Signal Name      | Signal<br>Type | Signal<br>Length | Signal Description                                                                                                                                            |

|------------------|----------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| rst              | In             | 1 bit            | Reset signal is used in order to set all<br>configuration registers to zero (low) and to<br>bring the SU module into a state that is<br>ready to receive data |

| clk              | In             | 1 bit            | The clock signal is used in order to synchronize SU with other modules                                                                                        |

| data_av_in_SU    | In             | 1 bit            | The available signal of data incoming to SU                                                                                                                   |

| data_in_SU       | In             | 32 bits          | The data incoming to SU                                                                                                                                       |

| data_av_out_X_SU | Out            | 1 bit            | The available signal of data outgoing from SU X                                                                                                               |

| data _out_X_SU   | Out            | 49 bits          | The data outgoing from SU X                                                                                                                                   |

Table 4-4 SU Signal Descriptions

In each falling edge of a cycle, SU checks data available input. If data is available, SU gets the 32-bit wide IP Address into the block. After initial partitioning stage, SU finds the input stage CR and constructs the SAFIL Frame while outputing it at the corresponding output port .

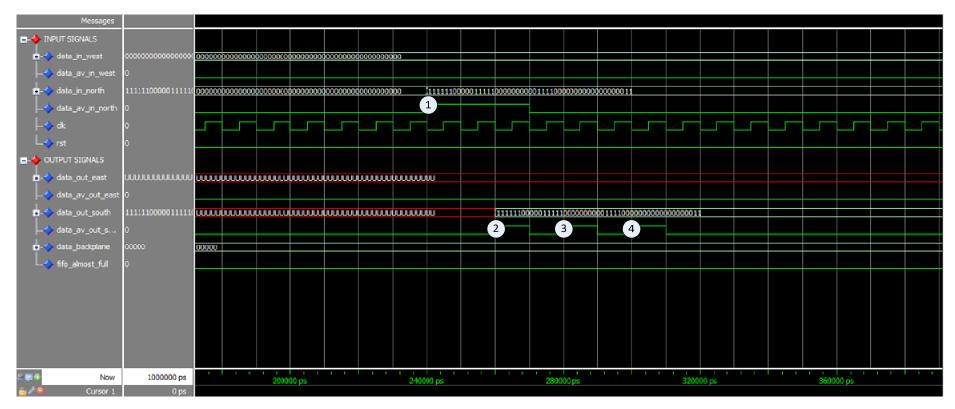

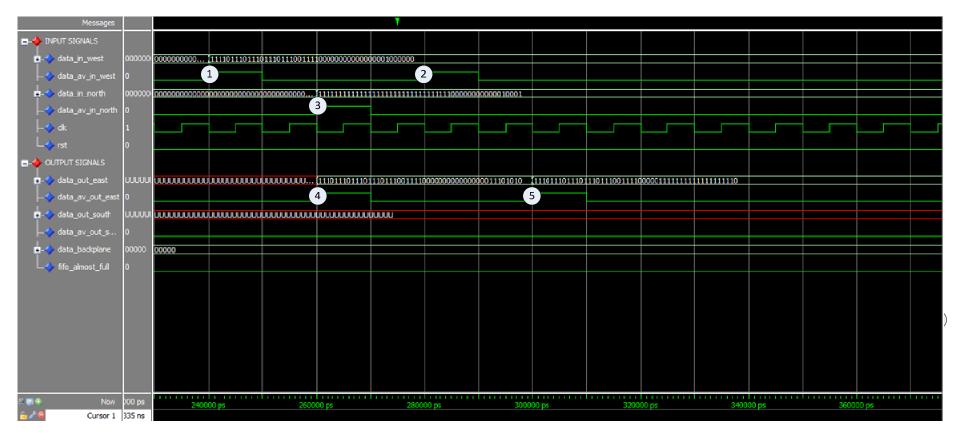

## 4.2.2 Simulation

#### **SCENARIO 1**

Aim: To show and verify that SU constructs SAFIL Frame and outputs it on the corresponding output port.

## **Test Code:**

wait for 100 ns;  $rst \le '1'$ ; wait for clk\_period\*3;  $rst \le '0'$ ; wait for clk\_period\*10; data\_av\_in\_SU <= '1'; data\_in\_SU <= x"ffffffff"; wait for clk\_period; data\_in\_SU <= x"cffffffff"; wait for clk\_period; data\_in\_SU <= x"0ffffffff"; wait for clk\_period; data\_in\_SU <= x"2ffffffff"; wait for clk\_period; data\_in\_SU <= x"2ffffffff"; wait for clk\_period; data\_av\_in\_SU <= '0';