# INVESTIGATION OF DC BUS CURRENT HARMONICS IN TWO AND THREE LEVEL THREE-PHASE INVERTERS

# A THESIS SUBMITTED TO THE GRADUATE SCHOOL OF NATURAL AND APPLIED SCIENCES OF MIDDLE EAST TECHNICAL UNIVERSITY

$\mathbf{B}\mathbf{Y}$

# UFUK AYHAN

## IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE IN ELECTRICAL AND ELECTRONICS ENGINEERING

FEBRUARY 2012

Approval of the thesis:

# INVESTIGATION OF DC BUS CURRENT HARMONICS IN TWO AND THREE LEVEL THREE-PHASE INVERTERS

submitted by UFUK AYHAN in partial fulfillment of the requirements for the degree of Master of Science in Electrical and Electronics Engineering Department, Middle East Technical University by,

| Prof. Dr. Canan Özgen<br>Dean, Graduate School of <b>Natural and Applied Sciences</b>                 |            |

|-------------------------------------------------------------------------------------------------------|------------|

| Prof. Dr. İsmet Erkmen<br>Head of Department, <b>Electrical and Electronics Engineering</b>           |            |

| Assoc. Prof. Dr. Ahmet M. Hava<br>Supervisor, <b>Electrical and Electronics Engineering Dept.</b> , M | ETU        |

| Examining Committee Members:                                                                          |            |

| Prof. Dr. Muammer Ermiş<br>Electrical and Electronics Engineering Dept., METU                         |            |

| Assoc. Prof. Dr. Ahmet M. Hava<br>Electrical and Electronics Engineering Dept., METU                  |            |

| Prof. Dr. Arif Ertaş<br>Electrical and Electronics Engineering Dept., METU                            |            |

| Prof. Dr. Kemal Leblebicioğlu<br>Electrical and Electronics Engineering Dept., METU                   |            |

| Emre Ün, M.Sc.<br>ASELSAN                                                                             |            |

| Date:                                                                                                 | 09/02/2012 |

I hereby declare that all information in this document has been obtained and presented in accordance with academic rules and ethical conduct. I also declare that, as required by these rules and conduct, I have fully cited and referenced all material and results that are not original to this work.

Name, Last name : Ufuk Ayhan

Signature :

#### ABSTRACT

## INVESTIGATION OF DC BUS CURRENT HARMONICS IN TWO AND THREE LEVEL THREE-PHASE INVERTERS

Ayhan, Ufuk M.Sc., Department of Electrical and Electronics Engineering Supervisor: Assoc. Prof. Dr. Ahmet M. Hava

February 2012, 134 pages

Within scope of this work, double-fourier analysis method of rapid calculation and detailed simulation method, which are used to investigate DC bus current harmonics in two level and three level three-phase inverters systematically, will be emphasized and two methods will be compared via applying different modulation techniques. In addition, DC bus currents will be investigated visually for various working conditions and modulation methods. After that, analysis methods will be applied and harmonic spectrums will be determined. After all, it will be showed that calculated harmonic spectrums could be treated as unified harmonics around certain frequencies and these unified harmonics could be reached easily via looking at predetermined table. Moreover, it will also be showed that unified harmonic values could be used to determine harmonic current components that are necessary for sizing DC bus capacitor and could be used in various inverter analysis.

Keywords: fourier, dc bus, current harmonics, inverter, PWM, unified harmonics

# İKİ VE ÜÇ SEVİYELİ ÜÇ FAZLI EVİRİCİLERDE DC BARA AKIMI HARMONİKLERİNİN İNCELENMESİ

Ayhan, Ufuk Yüksek Lisans, Elektrik ve Elektronik Mühendisliği Bölümü Tez Yöneticisi: Doç. Dr. Ahmet M. Hava

#### Şubat 2012, 134 sayfa

Bu çalışmada, iki ve üç seviyeli üç fazlı eviricilerde DC bara akım harmoniklerinin sistematik bir şekilde incelenmesi için kullanılan ayrıntılı benzetim yöntemi ve hızlı hesap yöntemi olan çift-fourier analitik yöntemi ele alınıp çeşitli modülasyon yöntemleri uygulanarak iki yaklaşım değerlendirilip karşılaştırılacaktır. Çalışmada DC bara akımları çeşitli çalışma koşulları ve modülasyon yöntemleri için görsel olarak incelenecek, ardından analiz yöntemleri uygulanacak ve harmonik spektrumları belirlenecektir. Daha sonra, hesaplanan harmonik spektrumların, belli frekans bölgelerinde birleştirilmiş olarak ele alınabileceği ve önceden oluşturulan tablo ile birleştirilmiş harmonik değerlerine kolayca ulaşılabileceği; birleştirilmiş harmonik değerlerinin, DC bara kondansatörü boyutlandırmada gerekli olan harmonik akımı bileşenlerini belirlemekte ve çeşitli evirici analizlerinde kullanılabileceği gösterilecektir.

Anahtar Kelimeler: fourier, da bara, akım harmonikleri, evirici, DGM, birleştirilmiş harmonik

## ÖZ

To My Family And to the memory of my grandfather, Memiş Çakıllı

#### ACKNOWLEDGEMENTS

I express my sincerest thanks to my supervisor, Dr. Ahmet M. Hava, for his guidance, support, encouragement, and valuable contributions throughout my graduate education.

I would like to express my deepest gratitude to my mother, Gülay Ayhan, my father, İsmail Ayhan, and my older brother, Barış Ayhan for their support.

I would like to thank my research groupmates Nebi Onur Çetin, Özgür Bulut, Ziya Özkan, Volkan Aban and all my friends for their help and support. Also, I would like to thank Emre Ün for his critique and review of my thesis work.

I wish to thank to the staff of Electrical and Electronics Engineering Department and Graduate School of Natural and Applied Sciences for their help throughout my graduate study.

Moreover, I wish to thank to Tübitak-Sage for the encouragement and support about following master and doctoral programs while working.

# **TABLE OF CONTENTS**

| ABSTRACT          | iv   |

|-------------------|------|

| ÖZ                | v    |

| ACKNOWLEDGEMENTS  | vii  |

| TABLE OF CONTENTS | viii |

| LIST OF FIGURES   | xi   |

| LIST OF TABLES    | xx   |

# CHAPTERS

| 1. | INTRODUCTION                                                                | 1    |

|----|-----------------------------------------------------------------------------|------|

|    | 1.1. Three-Phase Voltage Source Inverters as Applied to AC Motor Drives and | d    |

|    | PWM Rectifiers                                                              | 1    |

|    | 1.2. PWM Techniques                                                         | 4    |

|    | 1.3. High Frequency Effects of PWM Operation                                | 5    |

|    | 1.4. Scope of the Thesis                                                    | 7    |

|    |                                                                             |      |

| 2. | TOPOLOGIES AND BASIC APPLICATIONS                                           | 9    |

|    | 2.1. Introduction                                                           | 9    |

|    | 2.2. PWM Rectifier                                                          | 9    |

|    | 2.3. PWM Inverter                                                           | . 10 |

|    | 2.4. PWM Rectifier Cascaded with PWM Inverter                               | . 11 |

|    | 2.5. Diode / Thyristor Rectifier Cascaded with PWM Inverter                 | . 13 |

|    |                                                                             |      |

| 3. | ANALYSIS AND CHARACTERIZATION OF DC BUS RIPPLE                              |      |

#

| 3.1. Introduction                                                  | 17 |

|--------------------------------------------------------------------|----|

| 3.2. Dc Bus Current Ripple of VSI                                  | 18 |

| 3.2.1. Microscopic View                                            | 18 |

| 3.2.2. Spectral Content                                            | 21 |

| 3.2.3. Total RMS Value                                             | 24 |

| 3.3. Ripple Current Spectral analysis                              | 25 |

| 3.4. The Equivalent Centered Harmonic Approach                     | 30 |

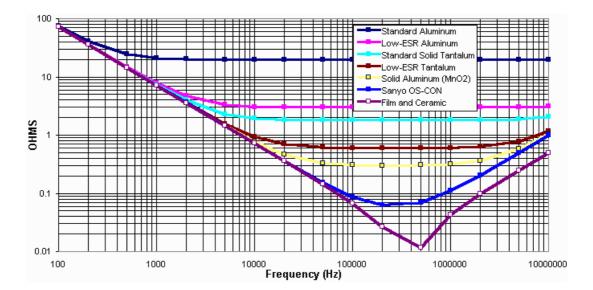

| 4. POWER ELECTRONIC CAPACITORS                                     | 34 |

| 4.1. Introduction                                                  | 34 |

| 4.2. Terminology and Loss Mechanisms in Capacitors                 | 38 |

| 4.3. Electrolytic and Film Capacitors in DC Link Applications      | 39 |

| 5. TOPOLOGIES, APPLICATIONS, INVERTER DESIGN AND                   |    |

| PERFORMANCE EVALUATION                                             | 45 |

| 5.1. Introduction                                                  | 45 |

| 5.2. PWM Method Selection                                          | 47 |

| 5.3. Review and Design of Dc Bus Capacitors for Inverters          | 48 |

| 5.4. Design Examples                                               | 55 |

| 5.4.1. PWM Rectifier Design Example                                | 55 |

| 5.4.2. PWM Rectifier Cascaded with PWM Inverter Design Example     | 56 |

| 5.4.2.1. Transformerless UPS System Case                           | 56 |

| 5.4.2.2. Regenerative Motor Drive with Active Front End Case       | 57 |

| 5.4.3. Diode/Thyristor Rectifier Cascaded with PWM Inverter Design |    |

| Example                                                            | 58 |

| 5.5. Comparing Theoric Calculations and System Simulation Results  | 60 |

| 5.5.1. Comparison for Typical Application I                        | 62 |

| 5.5.2. Comparison for Typical Application II                       | 66 |

| 5.5.3. Comparison for Typical Application III                      | 71 |

| 5.6. Output Current Harmonic of Two Level VSI                      | 77 |

| 6. | EXP  | PERIMENTAL RESULTS                         | . 82 |

|----|------|--------------------------------------------|------|

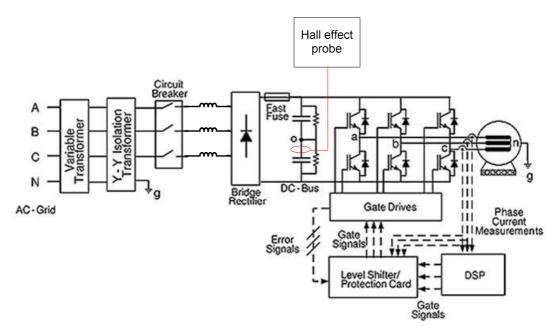

|    | 6.1. | Introduction                               | . 82 |

|    | 6.2. | No Load Induction Motor Experiment Results | . 85 |

|    | 6.3. | RL Load Experiment Results                 | .93  |

|    |      |                                            |      |

# 7. BASIC INVESTIGATION OF THREE PHASE THREE LEVEL PWM VSI 105

| REFERENCES                                 | 119 |

|--------------------------------------------|-----|

| APPENDIX                                   |     |

| A. MATLAB CODE FOR DOUBLE FOURIER ANALYSIS |     |

# LIST OF FIGURES

# FIGURES

| 1.1 The dc bus current and its average and ripple components in the three phase                |  |  |

|------------------------------------------------------------------------------------------------|--|--|

| two-level VSI topology2                                                                        |  |  |

| 1.2 Main application types                                                                     |  |  |

| 1.3 Two-level three-phase inverter popular PWM methods; the high frequency                     |  |  |

| carrier waves (left) and the modulation waves (right)4                                         |  |  |

| 2.1 PWM rectifier topology and the current distribution10                                      |  |  |

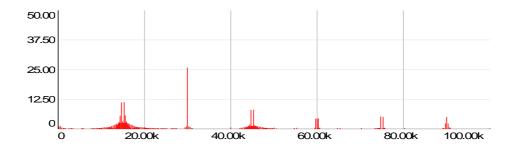

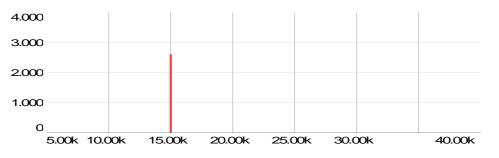

| 2.2 Harmonic spectrum of dc link current $I_{dc}$ for a working condition of NSPWM,            |  |  |

| $M_i = 0.7,  \phi = 0^\circ,  f_c = 15 \text{kHz}  (12.5 \text{A/div},  20 \text{kHz/div})$ 10 |  |  |

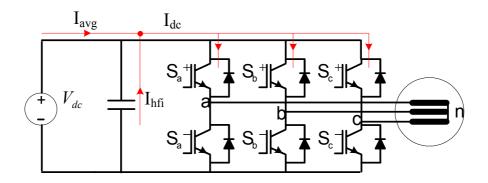

| 2.3 PWM VS Inverter topology and current distribution with 3Ø motor load 11                    |  |  |

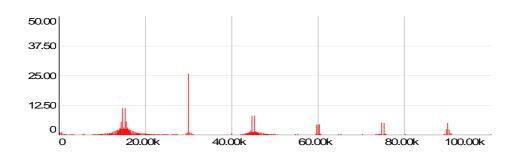

| 2.4 Harmonic spectrum of dc link current $I_{dc}$ for a working condition of NSPWM,            |  |  |

| $M_i = 0.7,  \phi = 0^\circ,  (12.5 A/div,  20 kHz/div) \dots 11$                              |  |  |

| 2.5 Back to back inverter topology and the current distribution                                |  |  |

| 2.6 Harmonic spectrum of dc link capacitor current $I_{hf}$ for rectifier working              |  |  |

| condition of NSPWM, $M_i = 0.7$ , $\phi = 0^\circ$ , and inverter working condition of         |  |  |

| SVPWM, $M_i = 0.7$ , $\phi = 0^\circ$ , (12.5A/div, 20kHz/div)13                               |  |  |

| 2.7 Harmonic spectrum of dc link capacitor current $I_{hf}$ for rectifier working              |  |  |

| condition of NSPWM, $M_i = 0.7$ , $\phi = 0^\circ$ , $f_c = 15$ kHz and inverter working       |  |  |

| condition of SVPWM, $M_i = 0.7$ , $\phi = 0^\circ$ , $f_c = 10$ kHz, (12.5A/div, 20kHz/div) 13 |  |  |

| 2.8 Diode / thyristor rectifier cascaded with PWM inverter                                     |  |  |

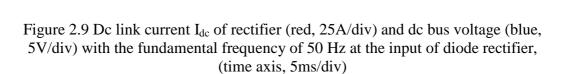

| 2.9 Dc link current $I_{dc}$ of rectifier (red, 25A/div) and dc bus voltage (blue, 5V/div)     |  |  |

| with the fundamental frequency of 50 Hz at the input of diode rectifier, (time                 |  |  |

| axis, 5ms/div)14                                                                               |  |  |

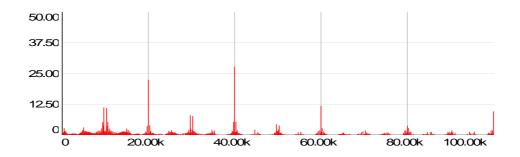

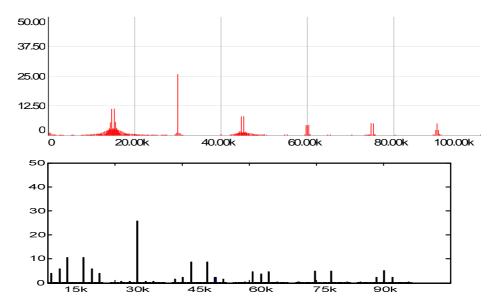

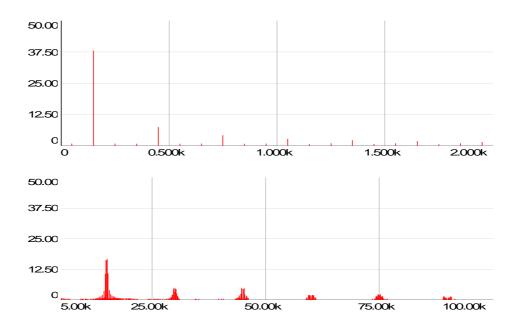

| 2.10 Low frequency (top) and high frequency (bottom) harmonic spectrum of $I_{dc}$ of |

|---------------------------------------------------------------------------------------|

| rectifier with 34 kW output power and inverter working condition of NSPWM,            |

| $M_i = 0.7,  \phi = 0^\circ,  (12.5 \text{A/div},  16.67 \text{kHz/div})  15$         |

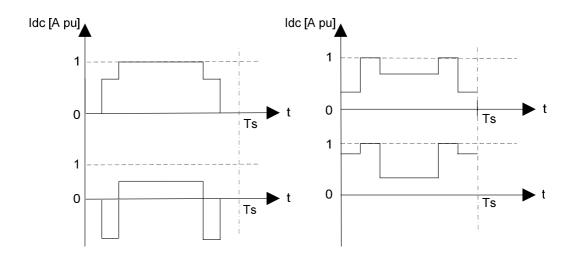

| 3.2 Inverter microscopic dc bus currents in a PWM period for continuous PWM                               |

|-----------------------------------------------------------------------------------------------------------|

| methods; Left: SVPWM (M <sub>i</sub> =0.7, top: $\phi = 0^{\circ}$ , bottom $\phi = 90^{\circ}$ ), Right: |

| AZSPWM1 (M <sub>i</sub> =0.7, top: $\phi = 0^{\circ}$ , bottom $\phi = 90^{\circ}$ )                      |

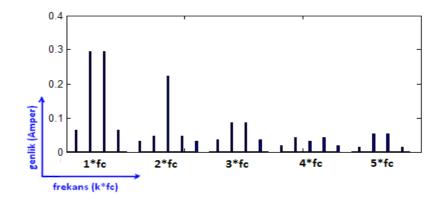

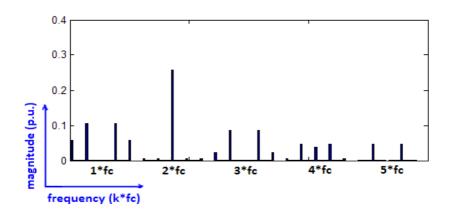

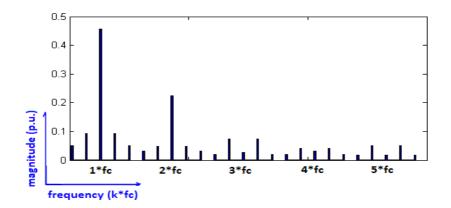

3.4 Ripple current spectrum (0.1A-pu/div), SVPWM,  $M_i$ =0,3,  $\phi$  = 0°,  $I_{om}$ =100 A.22

- 3.5 Ripple current spectrum (0.1A-pu/div), AZSPWM1,  $M_i=0,3$ ,  $\phi = 0^\circ$ ,  $I_{om}=100$  A

- 3.6 Ripple current spectrum (0.1A-pu/div), DPWM1,  $M_i$ =0,7,  $\phi$  = 0°,  $I_{om}$ =100A..22

- 3.7 Ripple current spectrum (0.1A-pu/div), DPWM1,  $M_i$ =0,7,  $\phi$  = 30°,  $I_{om}$ =100A 23

- 3.8 Ripple current spectrum (0.1A-pu/div), NSPWM,  $M_i$ =0,7,  $\phi$  = 0°,  $I_{om}$ =100 A.23

- 3.9 Ripple current spectrum, (0.1A-pu/div), NSPWM,  $M_i=0.7$ ,  $\phi = 30^\circ$ ,  $I_{om}=100$  A.

- 3.10 RMS ripple current characteristics,  $K_{dc} = f(M_i, \cos \varphi)$  for various PWM methods

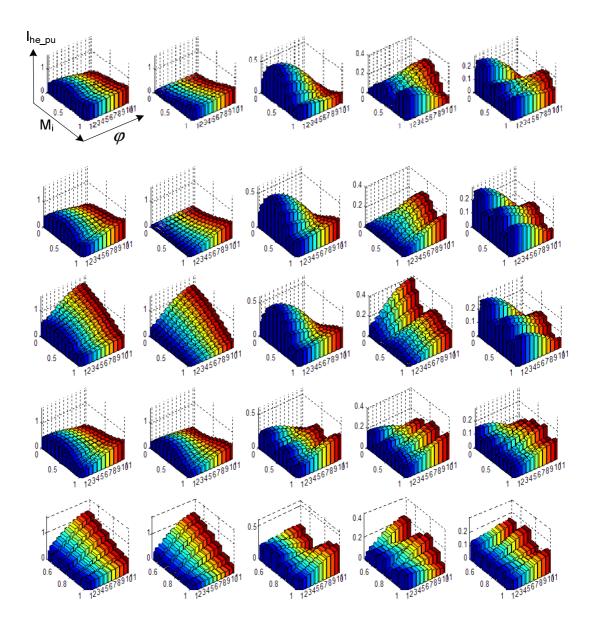

- 3.14 The normalized rms and normalized equivalent centered dc bus current harmonics. From top to bottom: SPWM, SVPWM, AZSPWM1, DPWM1,

| NSPWM. From left to right: normalized rms value (scaled with $\sqrt{2}$ ), first            |

|---------------------------------------------------------------------------------------------|

| centered harmonic peak value (m=1), second centered harmonic peak value                     |

| (m=2), third centered harmonic peak value (m=3), fourth centered harmonic                   |

| peak value (m=4). $M_i$ axis: 0.1 to 0.9 in 0.1 increments, and $\phi$ axis: 0° to 90° in   |

| 9° increments                                                                               |

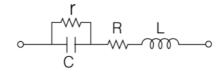

| 4.1 Capacitor equivalent circuit model [17]35                                               |

| 4.2 Geometrical definition of DF [17]                                                       |

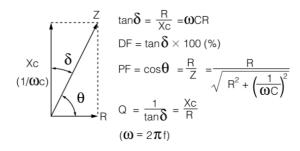

| 4.3 Usage of different kinds of capacitors over capacitance and voltage rating plane        |

| [19]                                                                                        |

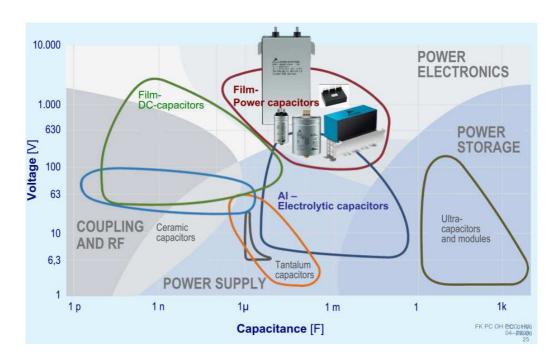

| 4.4 Impedance graph of different kinds of capacitors. Inductance of electrolytic            |

| capacitors is taken as 0.016 $\mu$ H and ESR is assumed as constant with frequency          |

| [18]                                                                                        |

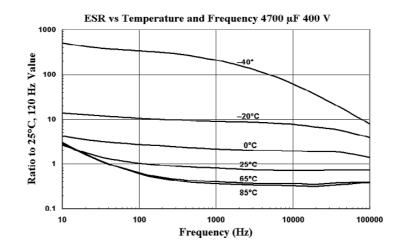

| 4.5 ESR of Aluminum Electrolytic Capacitor with ESR:23m $\Omega$ @ 120 Hz, 25°C40           |

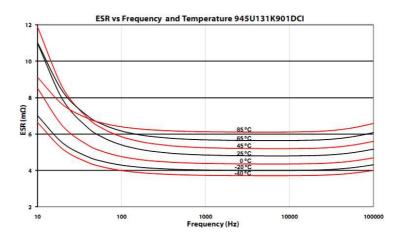

| 4.6 ESR of film capacitor [25]40                                                            |

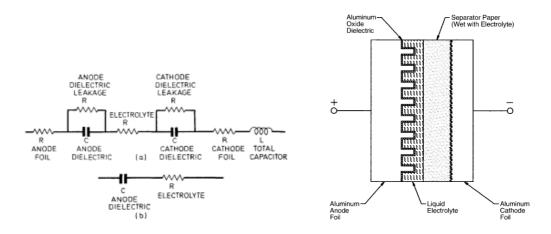

| 4.7 (a) Complete internal circuit of electrolytic capacitor (b) Simplified circuit at       |

| low frequencies [22]. The internal layer structure of aluminum electrolytic                 |

| capacitor [23]41                                                                            |

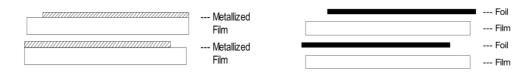

| 4.8 Metallized film technology and foil film technology [24]41                              |

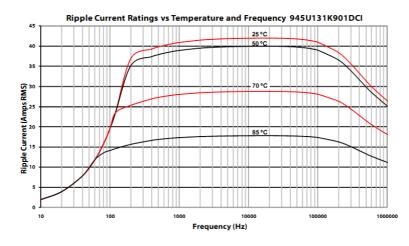

| 4.9 Ripple current rating of film capacitor with the ratings: $130\mu$ F, $900V$ [25]42     |

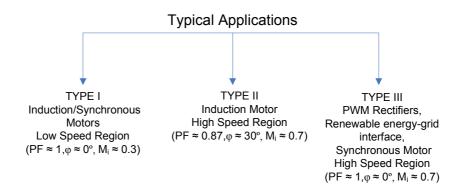

| 5.1 PWM inverter applications and typical operating points                                  |

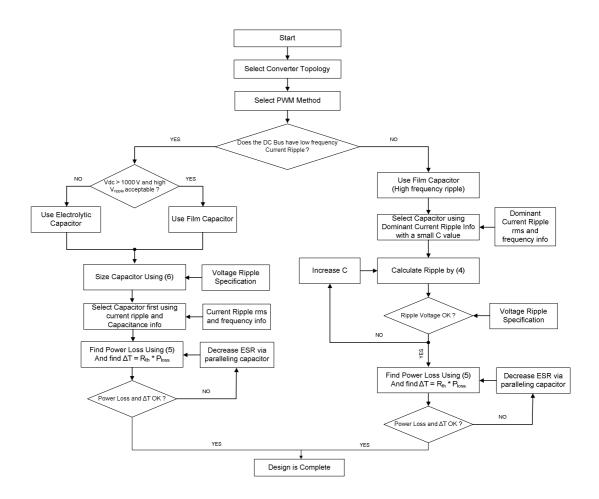

| 5.2 Dc bus capacitor sizing flow chart                                                      |

| 5.3 Dc bus capacitor branch                                                                 |

| 5.4 Rectifier circuit (top) and phasor diagram (bottom) for lagging power factor            |

| operation61                                                                                 |

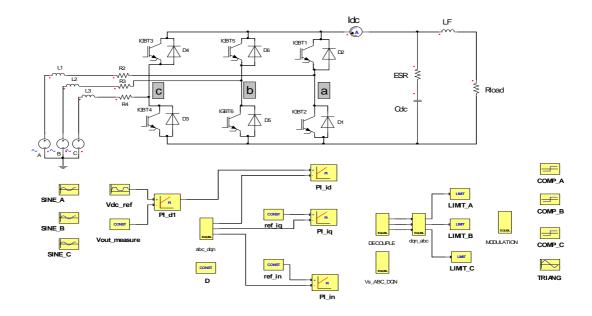

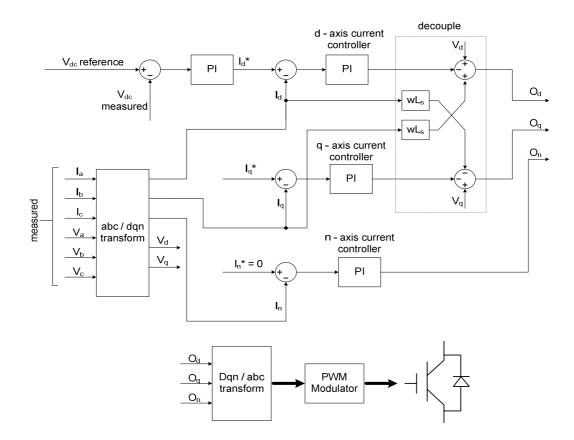

| 5.5 Three-wire two-level voltage source rectifier used to simulate R-L-E system 61          |

| 5.6 Three wire two level voltage source rectifier control block diagram                     |

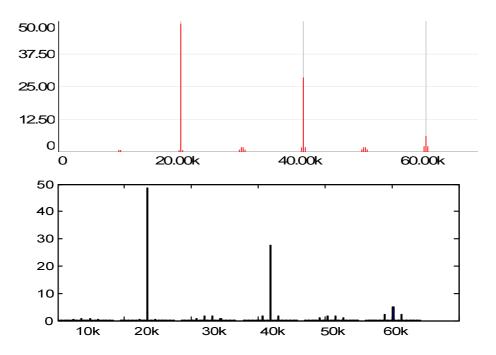

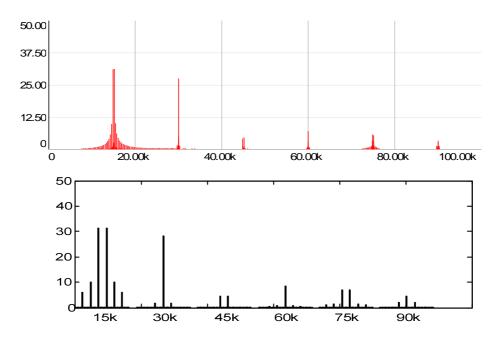

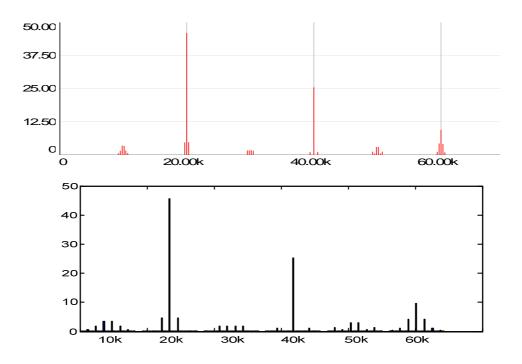

| 5.7 $I_{hf}$ spectrum from simulation fft (top, 12.5A/div, 20kHz/div) and $I_{hf}$ spectrum |

| from matlab analysis (bottom, 10A/div) for SVPWM64                                          |

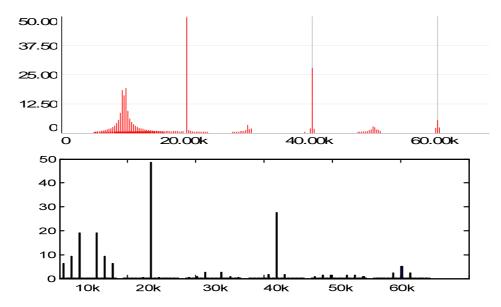

| 5.8 $I_{hf}$ spectrum from simulation fft (top, 12.5A/div, 20kHz/div) and $I_{hf}$ spectrum |

| from matlab analysis (bottom, 10A/div, 10kHz/div) for AZSPWM164                             |

| 5.9 $I_{hf}$ spectrum from simulation fft (top, 12.5A/div, 20kHz/div) and $I_{hf}$ spectrum          |

|------------------------------------------------------------------------------------------------------|

| from matlab analysis (bottom, 10A/div, 15kHz/div) for DPWM165                                        |

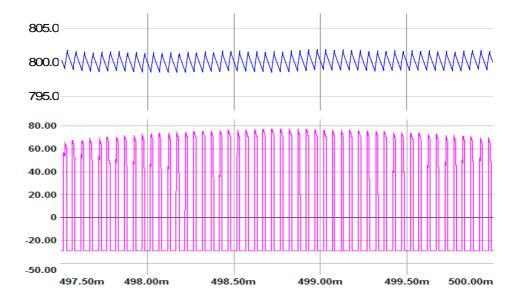

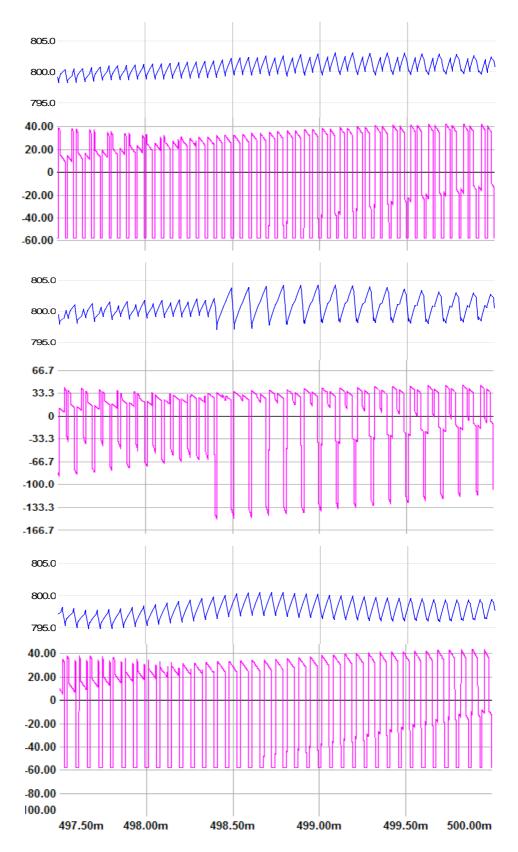

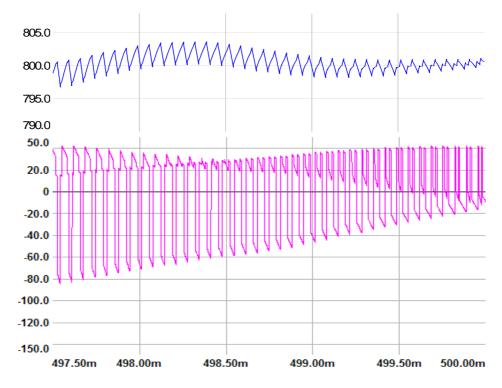

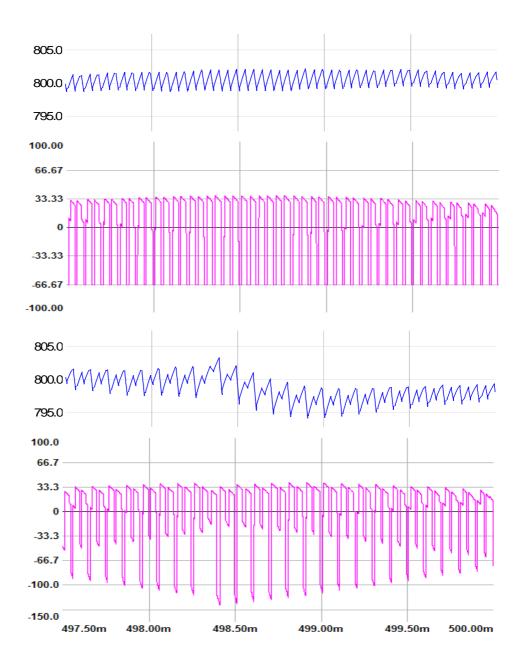

| 5.10 DC bus capacitor voltage waveform (blue, 5V/div) and the $I_{hf}$ current                       |

| waveform (pink, 20A/div), time axis (0.5mS/div) for SVPWM65                                          |

| 5.11 DC bus capacitor voltage waveform (blue, 5V/div) and the $I_{hf}$ current                       |

| waveform (pink, 20A/div), time axis (0.5mS/div) for AZSPWM1, DPWM1                                   |

| respectively from top to bottom                                                                      |

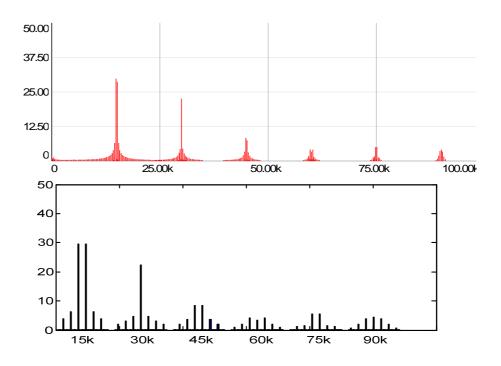

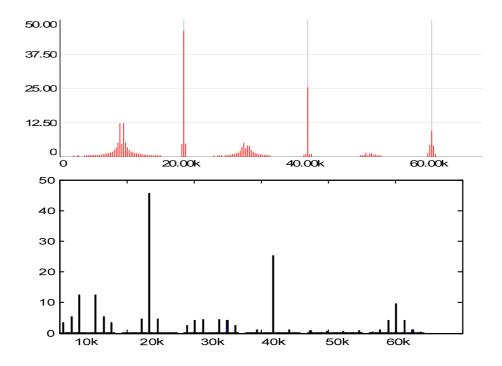

| 5.12 $I_{hf}$ spectrum from simulation fft (top, 12.5A/div, 20kHz/div) and $I_{hf}$ spectrum         |

| from matlab analysis (bottom, 10A/div, 10kHz/div) for SVPWM68                                        |

| 5.13 $I_{hf}$ spectrum from simulation fft (top, 12.5A/div, 20kHz/div) and $I_{hf}$ spectrum         |

| from matlab analysis (bottom, 10A/div, 10kHz/div) for AZSPWM168                                      |

| 5.14 $I_{hf}$ spectrum from simulation fft (top, 12.5A/div, 25kHz/div) and $I_{hf} spectrum$         |

| from matlab analysis (bottom, 10A/div, 15kHz/div) for DPWM169                                        |

| 5.15 $I_{\rm hf}$ spectrum from simulation fft (top, 12.5A/div, 20kHz/div) and $I_{\rm hf}$ spectrum |

| from matlab analysis (bottom, 10A/div, 15kHz/div) for NSPWM69                                        |

| 5.16 DC bus capacitor voltage waveform (blue, 5V/div) and the $I_{hf}  current$                      |

| waveform (pink, 20A/div, 33.3A/div), time axis (0.5mS/div) for SVPWM,                                |

| AZSPWM1, DPWM1 respectively from top to bottom70                                                     |

| 5.17 DC bus capacitor voltage waveform (blue, 5V/div) and the $I_{hf}  current$                      |

| waveform (pink, 20A/div), time axis (0.5mS/div) for NSPWM71                                          |

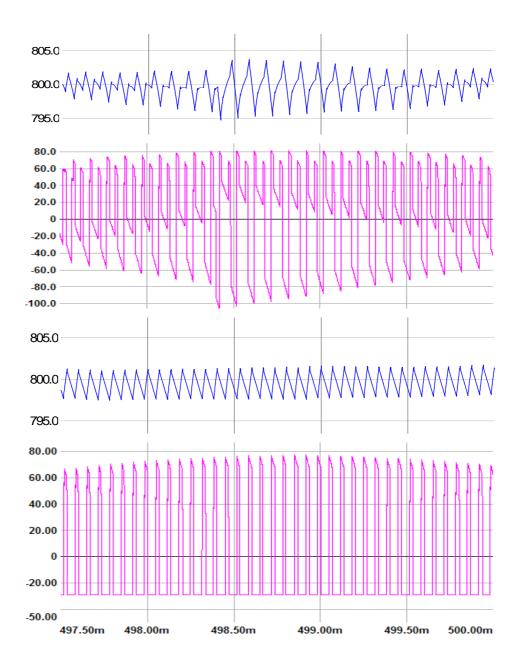

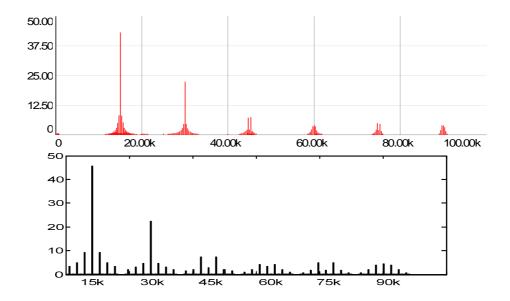

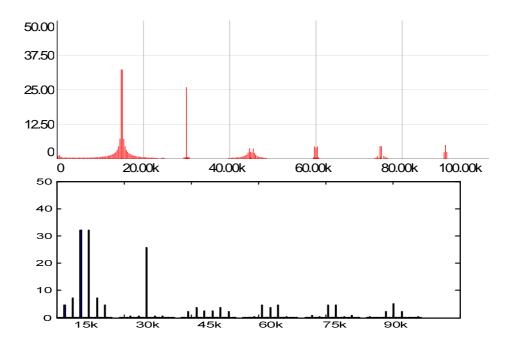

| 5.18 $I_{hf}$ spectrum from simulation fft (top, 12.5A/div, 20kHz/div) and $I_{hf} spectrum$         |

| from matlab analysis (bottom, 10A/div, 10kHz/div) for SVPWM73                                        |

| 5.19 $I_{hf}$ spectrum from simulation fft (top, 12.5A/div, 20kHz/div) and $I_{hf}$ spectrum         |

| from matlab analysis (bottom, 10A/div, 10kHz/div) for AZSPWM173                                      |

| 5.20 $I_{hf}$ spectrum from simulation fft (top, 12.5A/div, 20kHz/div) and $I_{hf}$ spectrum         |

| from matlab analysis (bottom, 10A/div, 15kHz/div) for DPWM174                                        |

| 5.21 $I_{hf}$ spectrum from simulation fft (top, 12.5A/div, 20kHz/div) and $I_{hf}$ spectrum         |

| from matlab analysis (bottom, 10A/div, 15kHz/div) for NSPWM74                                        |

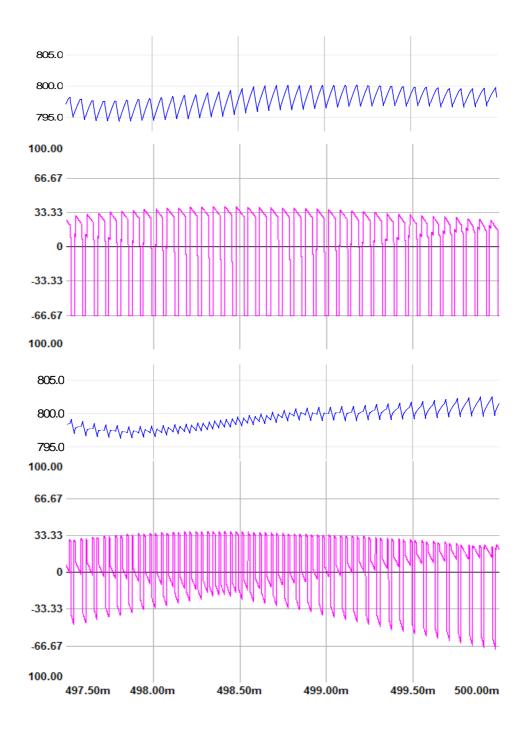

| 5.22 DC bus capacitor voltage waveform (blue, 5V/div) and the $I_{hf}  \text{current}$               |

| waveform (pink, 33.3A/div), time axis (0.5mS/div) for SVPWM, AZSPWM1,                                |

| respectively from top to bottom75                                                                    |

|                                                                                                      |

| 5.23 DC bus capacitor voltage waveform (blue, 5V/div) and the $I_{hf}$ current                |

|-----------------------------------------------------------------------------------------------|

| waveform (pink, 33.3A/div), time axis (0.5mS/div) for DPWM1, NSPWM,                           |

| respectively from top to bottom76                                                             |

| 5.24 Two level 3 wire inverter with low pass filter (R-L) outputs                             |

| 5.25 A phase output voltage (Va) and a phase output current (Ia) waveforms for                |

| φ=0                                                                                           |

| 5.26 Output current waveform for SVPWM                                                        |

| 5.27 High frequency harmonic spectrum of output current ( $I_a$ ) for SVPWM,                  |

| (0.5A/div, 5kHz/div)79                                                                        |

| 5.28 Output current waveform for DPWM1, (50A/div, 10ms/div)79                                 |

| 5.29 High frequency harmonic spectrum of output current ( $I_a$ ) for DPWM1,                  |

| (0.5A/div, 10kHz/div)                                                                         |

| 5.30 Output current waveform for AZSPWM, (50A/div, 10ms/div)80                                |

| 5.31 High frequency harmonic spectrum of output current (Ia) for AZSPWM,                      |

| (1A/div, 10kHz/div)                                                                           |

| 5.32 Output current waveform for NSPWM, (50A/div, 10ms/div)80                                 |

| 5.33 High frequency harmonic spectrum of output current $(I_a)$ for NSPWM,                    |

| (1A/div, 5kHz/div)                                                                            |

| 6.1 The motor drive system of experimental work                                               |

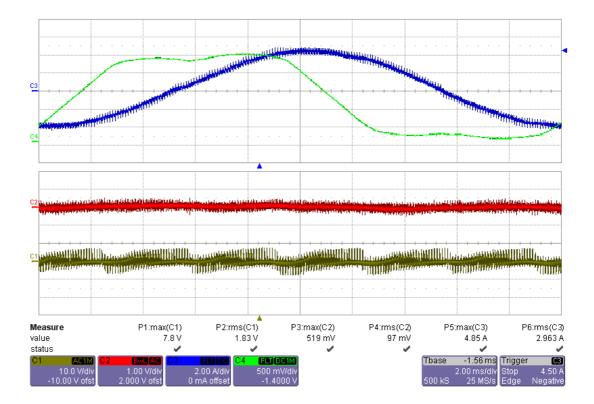

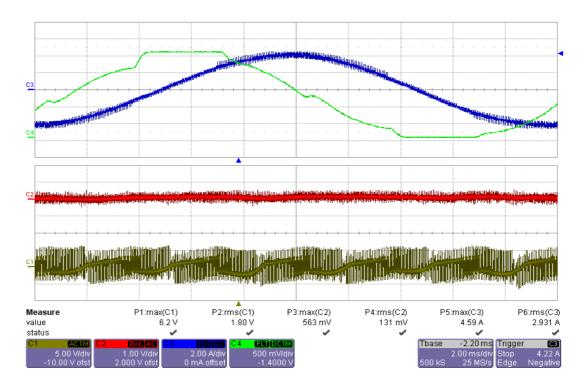

| 6.2 Modulation waveform (green, 0.5V/div), output current waveform                            |

| (blue, 2A/div), dc bus voltage (red, ac coupled, $1V/div$ ) and $I_{hf}$ current              |

| (brown, 10A/div), time axis (2ms/div) for SVPWM, $M_i$ =0.8, $f_c$ =10 kHz85                  |

| 6.3 Modulation waveform (green, 0.5V/div), output current waveform                            |

| (blue, 2A/div), dc bus voltage (red, ac coupled, $1V/div$ ) and $I_{hf}$ current              |

| (brown, 5A/div), time axis (2ms/div) for AZSPWM1, $M_i$ =0.8, $f_c$ =10 kHz86                 |

| 6.4 Modulation waveform (green, 0.5V/div), output current waveform                            |

| (blue, 2A/div), dc bus voltage (red, ac coupled, $1V/div$ ) and $I_{hf}$ current              |

| (brown, 5A/div), time axis (2ms/div) for DPWM1, M <sub>i</sub> =0.8, f <sub>c</sub> =15 kHz86 |

| 6.5 Modulation waveform (green, 0.5V/div), output current waveform                            |

| (blue, 2A/div), dc bus voltage (red, ac coupled, 1V/div) and I <sub>hf</sub> current          |

| (brown, 5A/div), time axis (2ms/div) for NSPWM, $M_i=0.8$ , $f_c=15$ kHz87                    |

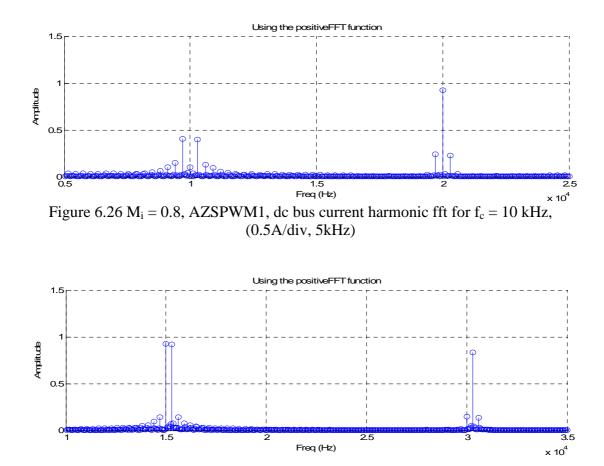

| 6.6 $M_i$ = 0.8, SVPWM, dc bus current harmonic fft for $f_c$ = 10 kHz,<br>(0.5A/div, 10kHz/div)                                                                                                                                                                        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $6.7 \text{ M}_{i} = 0.8, \text{ SVPWM}, \text{ dc bus current harmonic fft for } f_{c} = 10 \text{ kHz},$ $(0.5 \text{A/div}, 5 \text{kHz/div}) \dots 88$                                                                                                              |

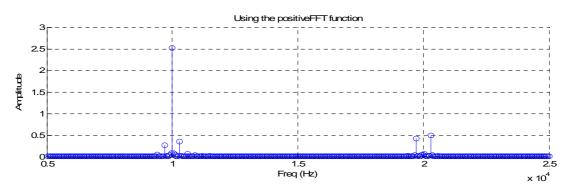

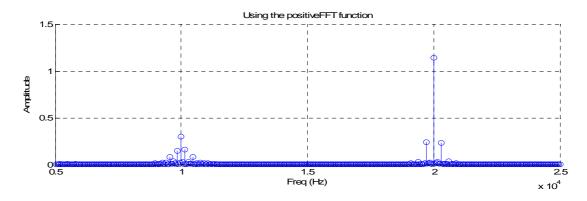

| $6.8 \text{ M}_{i} = 0.8, \text{ AZSPWM1, dc bus current harmonic fft for } f_{c} = 10 \text{ kHz,}$ $(0.5 \text{A/div}, 5 \text{kHz/div}) \dots 88$                                                                                                                    |

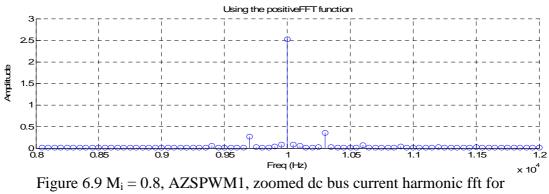

| 6.9 $M_i = 0.8$ , AZSPWM1, zoomed dc bus current harmonic fft for<br>$f_c = 10$ kHz, (0.5A/div, 0.5kHz/div)                                                                                                                                                             |

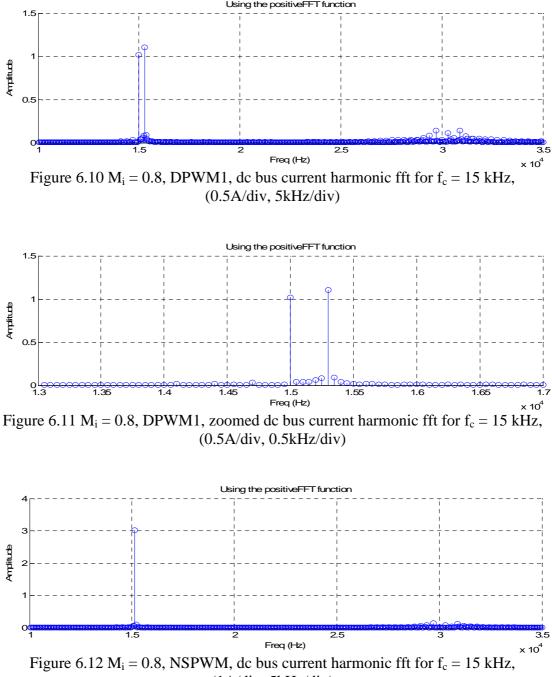

| $6.10 \text{ M}_{i} = 0.8$ , DPWM1, dc bus current harmonic fft for $f_{c} = 15 \text{ kHz}$ ,<br>( $0.5 \text{A/div}$ , $5 \text{kHz/div}$ )                                                                                                                           |

| $6.11 \text{ M}_{i} = 0.8, \text{ DPWM1, zoomed dc bus current harmonic fft for } f_{c} = 15 \text{ kHz,}$ $(0.5 \text{A/div}, 0.5 \text{kHz/div}) \dots 89$                                                                                                            |

| $6.12 \text{ M}_{i} = 0.8, \text{NSPWM}, \text{ dc bus current harmonic fft for } f_{c} = 15 \text{ kHz},$ $(1\text{A/div}, 5\text{kHz/div}) \dots 89$                                                                                                                  |

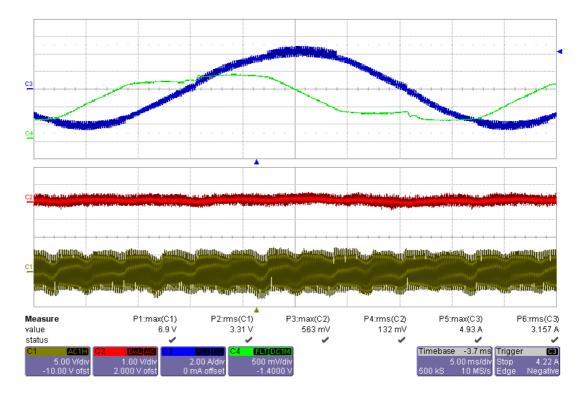

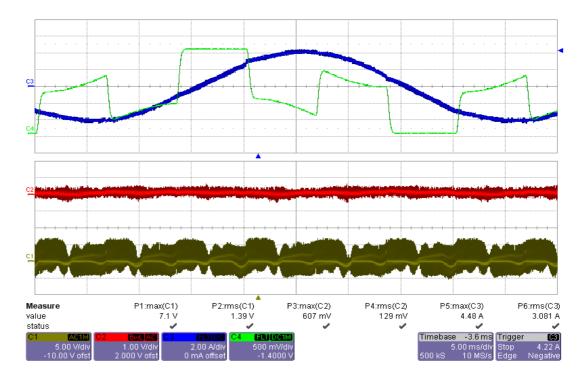

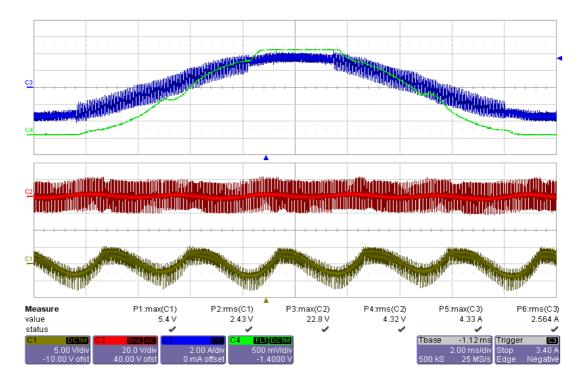

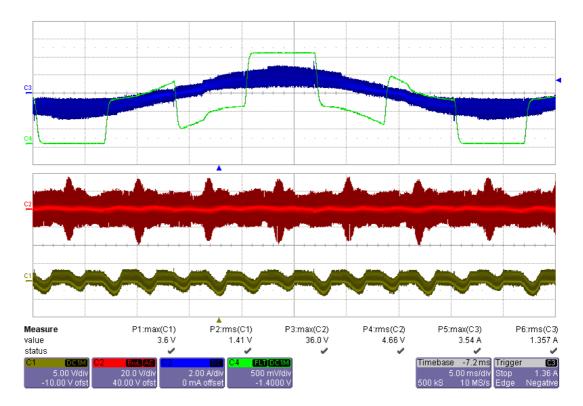

| <ul> <li>6.13 Modulation waveform (green, 0.5V/div), output current waveform (blue, 2A/div), dc bus voltage (red, ac coupled, 1V/div) and I<sub>hf</sub> current (brown, 5A/div), time axis (5ms/div) for SVPWM, M<sub>i</sub>=0.4, f<sub>c</sub>=10 kHz90</li> </ul>   |

| <ul> <li>6.14 Modulation waveform (green, 0.5V/div), output current waveform (blue, 2A/div), dc bus voltage (red, ac coupled, 1V/div) and I<sub>hf</sub> current (brown, 5A/div), time axis (5ms/div) for AZSPWM1, M<sub>i</sub>=0.4, f<sub>c</sub>=10 kHz91</li> </ul> |

| <ul> <li>6.15 Modulation waveform (green, 0.5V/div), output current waveform (blue, 2A/div), dc bus voltage (red, ac coupled, 1V/div) and I<sub>hf</sub> current (brown, 5A/div), time axis (5ms/div) for DPWM1, M<sub>i</sub>=0.4, f<sub>c</sub>=15 kHz91</li> </ul>   |

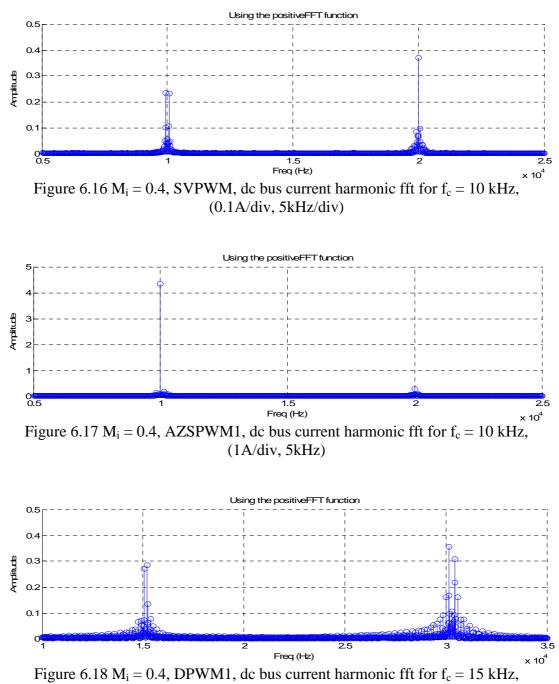

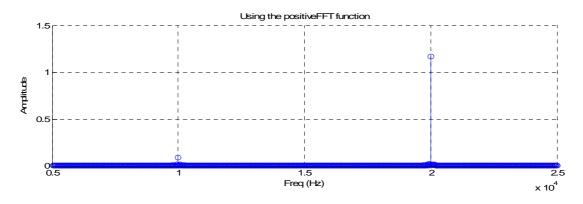

| $6.16\ M_i = 0.4,\ SVPWM,\ dc\ bus\ current\ harmonic\ fft\ for\ f_c = 10\ kHz,$ $(0.1A/div,\ 5kHz/div) \ldots 92$                                                                                                                                                      |

| 6.17 $M_i = 0.4$ , AZSPWM1, dc bus current harmonic fft for $f_c = 10$ kHz,<br>(1A/div, 5kHz)                                                                                                                                                                           |

| $6.18 \text{ M}_{i} = 0.4, \text{ DPWM1, dc bus current harmonic fft for } f_{c} = 15 \text{ kHz,}$ $(0.1 \text{A/div, 5kHz/div}) \dots 92$                                                                                                                             |

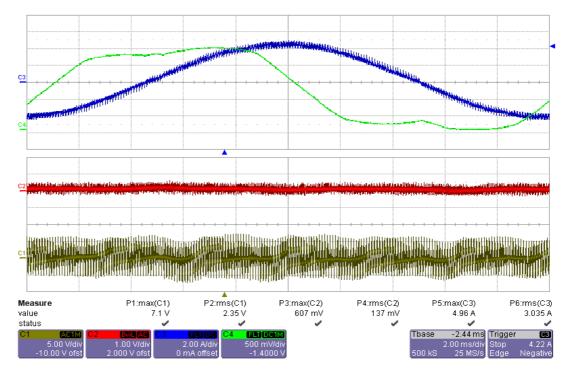

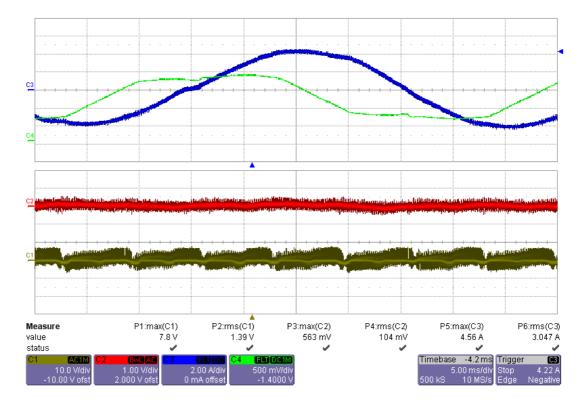

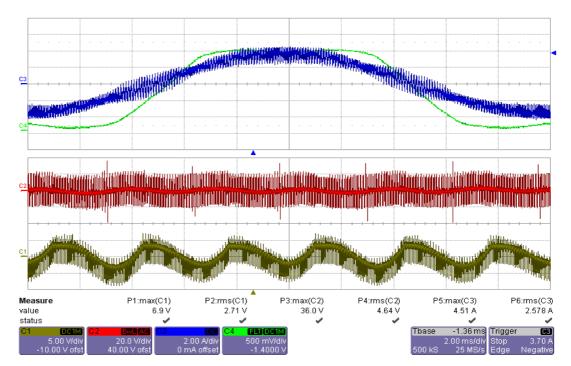

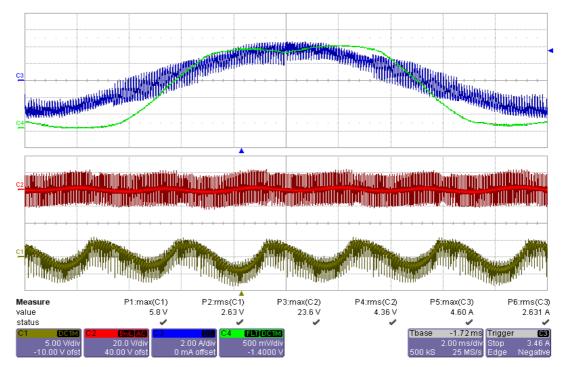

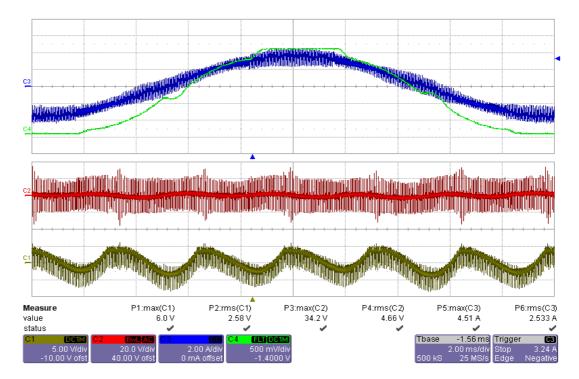

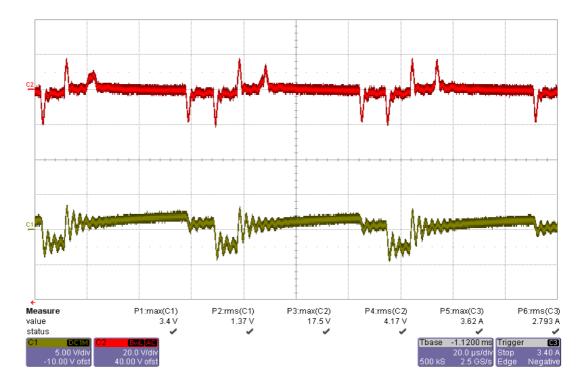

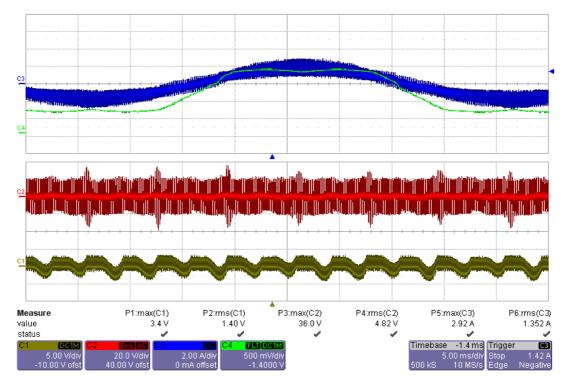

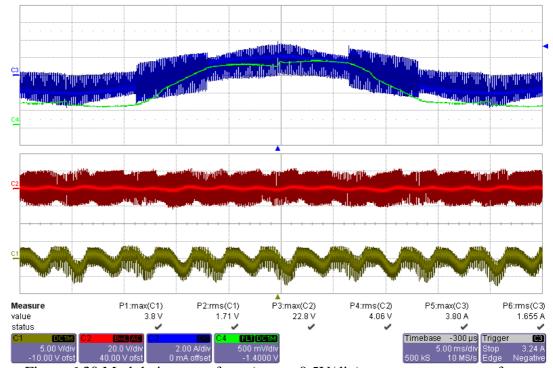

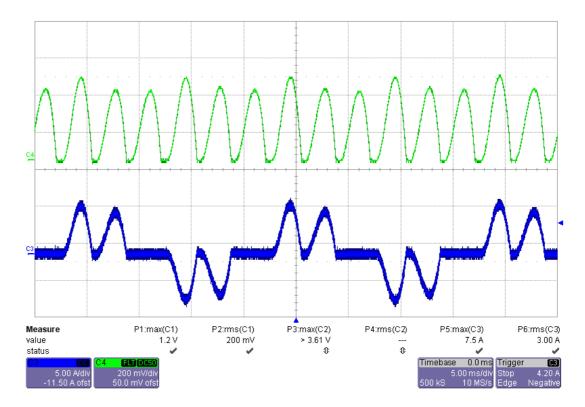

| 6.19 Modulation waveform (green, 0.5V/div), output current waveform                           |

|-----------------------------------------------------------------------------------------------|

| (blue, 2A/div), dc bus voltage (red, ac coupled, 20V/div) and $I_{hf}$ current                |

| (brown, 5A/div), time axis (2ms/div) for SVPWM, M <sub>i</sub> =0.8, f <sub>c</sub> =10 kHz93 |

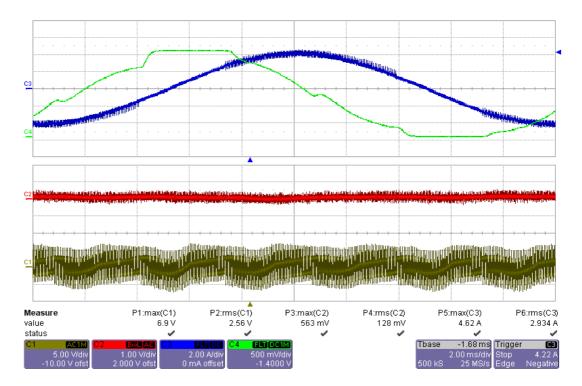

6.20 Modulation waveform (green, 0.5V/div), output current waveform (blue, 2A/div), dc bus voltage (red, ac coupled, 20V/div) and I<sub>hf</sub> current (brown, 5A/div), time axis (2ms/div) for AZSPWM1, M<sub>i</sub>=0.8, f<sub>c</sub>=10 kHz....94

| 6.21 Modulation waveform (green, 0.5V/div), output current waveform                           |

|-----------------------------------------------------------------------------------------------|

| (blue, 2A/div), dc bus voltage (red, ac coupled, 20V/div) and $I_{hf}current$                 |

| (brown, 5A/div), time axis (2ms/div) for DPWM1, M <sub>i</sub> =0.8, f <sub>c</sub> =15 kHz94 |

6.22 Modulation waveform (green, 0.5V/div), output current waveform (blue, 2A/div), dc bus voltage (red, ac coupled, 20V/div) and I<sub>hf</sub> current (brown, 5A/div), time axis (2ms/div) for NSPWM, M<sub>i</sub>=0.8, f<sub>c</sub>=15 kHz .......95

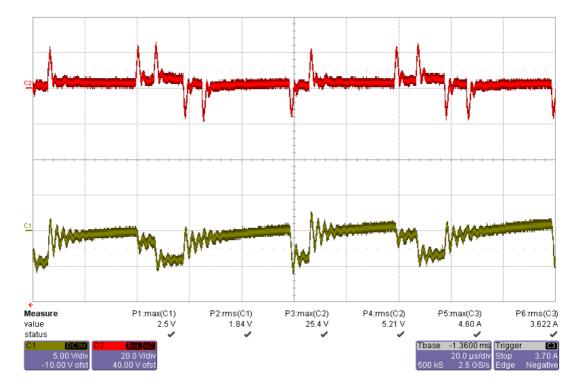

6.23 Zoomed in I<sub>hf</sub> current waveform (green, 5A/div), dc bus current waveform (red, 20V/div), time axis(20 $\mu$ s/div) for SVPWM M<sub>i</sub> = 0.8, f<sub>c</sub> = 10kHz ......95

| 6.24 Zoomed in I <sub>hf</sub> current waveform (green, 5A/div), dc bus current waveform            |

|-----------------------------------------------------------------------------------------------------|

| (red, 20V/div), time axis(20 $\mu$ s/div) for DPWM1, M <sub>i</sub> = 0.8, f <sub>c</sub> = 15kHz96 |

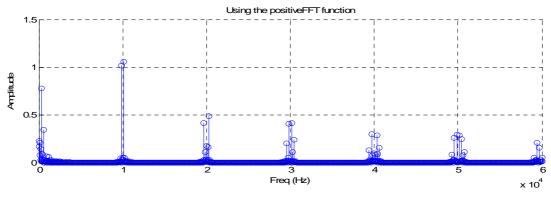

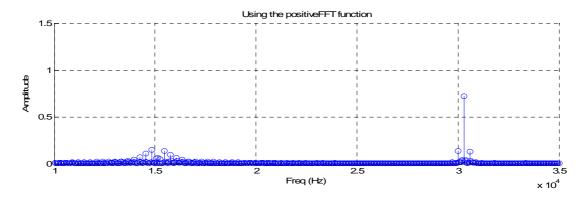

- $6.25 \text{ M}_{i} = 0.8, \text{ SVPWM, dc bus current harmonic fft for } f_{c} = 10 \text{ kHz,}$   $(0.5 \text{A/div}, 5 \text{kHz}) \dots 97$

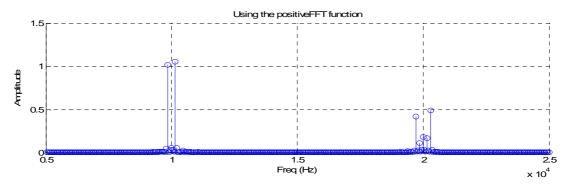

- 6.27  $M_i = 0.8$ , DPWM1, dc bus current harmonic fft for  $f_c = 15$  kHz, (0.5A/div, 5kHz) ......97

- 6.29 Modulation waveform (green, 0.5V/div), output current waveform (blue, 2A/div), dc bus voltage (red, ac coupled, 20V/div) and I<sub>hf</sub> current (brown, 5A/div), time axis (5ms/div) for SVPWM, M<sub>i</sub>=0.4, f<sub>c</sub>=10 kHz .......99

- 6.30 Modulation waveform (green, 0.5V/div), output current waveform (blue, 2A/div), dc bus voltage (red, ac coupled, 20V/div) and I<sub>hf</sub> current (brown, 5A/div), time axis (5ms/div) for AZSPWM1, M<sub>i</sub>=0.4, f<sub>c</sub>=10 kHz....99

| 6.31 Modulation waveform (green, 0.5V/div), output current waveform                                |

|----------------------------------------------------------------------------------------------------|

| (blue, 2A/div), dc bus voltage (red, ac coupled, 20V/div) and I <sub>hf</sub> current              |

| (brown, 5A/div), time axis (5ms/div) for DPWM1, $M_i=0.4$ , $f_c=15$ kHz100                        |

| 6.32 $M_i = 0.4$ , SVPWM, dc bus current harmonic fft for $f_c = 10$ kHz,                          |

| (0.5A/div, 5kHz)                                                                                   |

| $6.33 \text{ M}_{i} = 0.4$ , AZSPWM1, dc bus current harmonic fft for $f_{c} = 10 \text{ kHz}$ ,   |

| (0.5A/div, 5kHz)                                                                                   |

| 6.34 $M_i = 0.4$ , DPWM1, dc bus current harmonic fft for $f_c = 15$ kHz,                          |

| (0.5A/div, 5kHz)101                                                                                |

| 6.35 No load motor diode rectifier AC input current (blue, 1A/div), DC output                      |

| current (green, 0.8A/div), (5ms/div), $M_i = 0.8$                                                  |

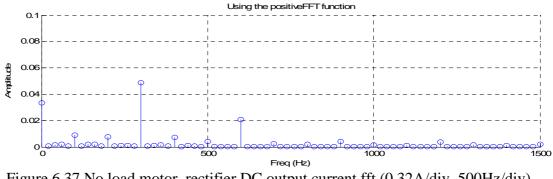

| 6.36 No load motor rectifier AC input current fft (0.05A/div, 500Hz/div), $M_i = 0.8$              |

|                                                                                                    |

| 6.37 No load motor rectifier DC output current fft (0.32A/div, 500Hz/div), $M_i = 0.8$             |

|                                                                                                    |

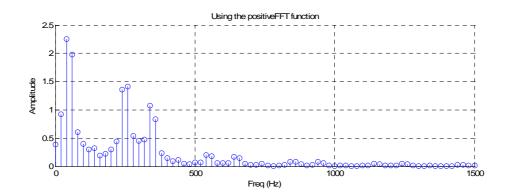

| 6.38 RL load diode rectifier AC input current (blue, 5A/div), DC output current                    |

| (green, 3.2A/div), (5ms/div), $M_i = 0.8$                                                          |

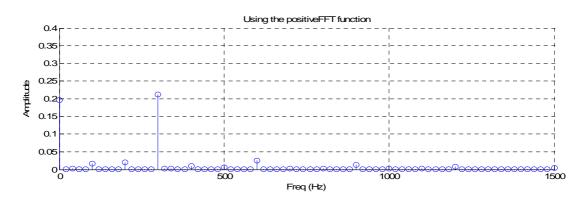

| 6.39 RL load rectifier AC input current fft (0.5A/div, 500Hz/div), $M_i = 0.8 \dots 104$           |

| 6.40 RL load rectifier DC output current fft (0.8A/div, 500Hz/div), $M_i = 0.8 \dots 104$          |

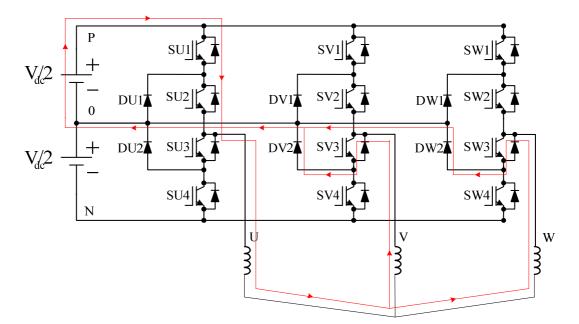

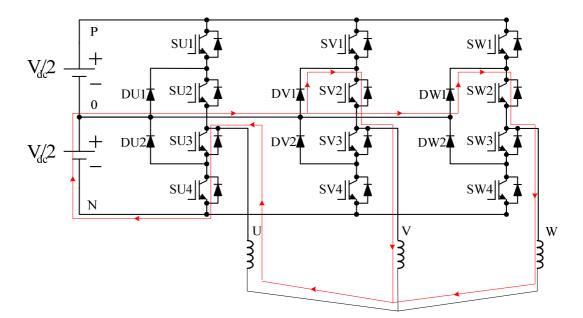

| 7.1 3L inverter topology and current circulation path in a switching state106                      |

| 7.2 3L inverter topology and current circulation path in a switching state107                      |

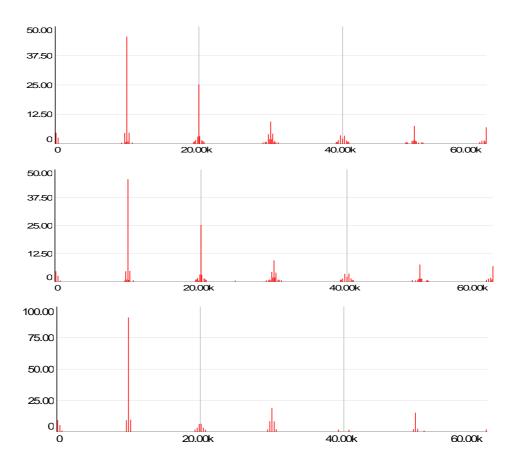

| 7.3 From top to bottom: $I_{dc_P}$ (V <sub>dc</sub> /2 rail current) harmonic spectrum (12.5A/div, |

| 20kHz/div), $I_{dc_N}$ (-V <sub>dc</sub> /2 rail current) harmonic spectrum                        |

| (12.5A/div, 20kHz/div), and the $I_{dc_O}$ (neutral wire current) harmonic spectrum                |

| (25A/div, 20kHz/div)108                                                                            |

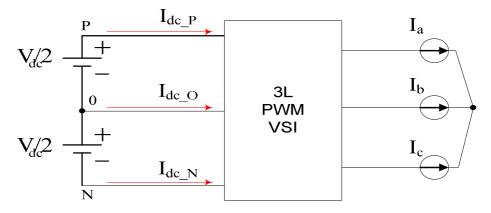

| 7.4 Dc bus current notations for 3L PWM VSI108                                                     |

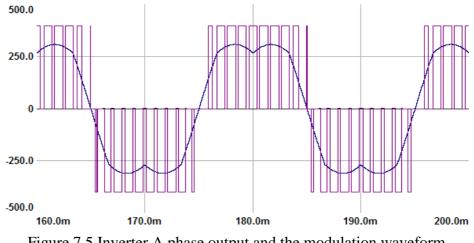

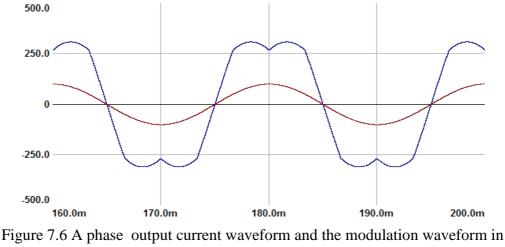

| 7.5 Inverter A phase output and the modulation waveform                                            |

| 7.6 A phase output current waveform and the modulation waveform in phase109                        |

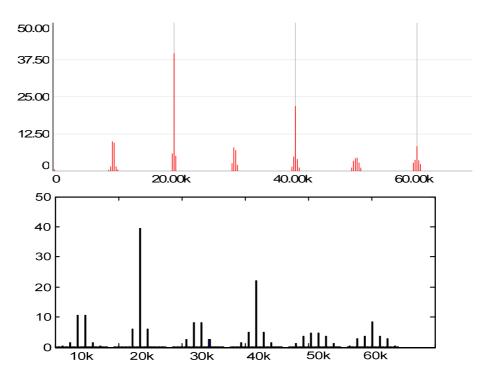

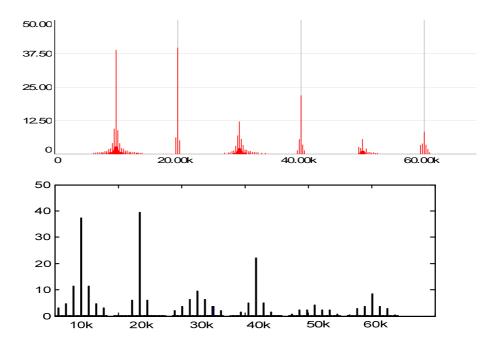

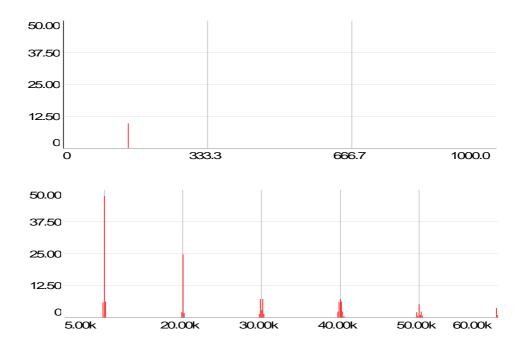

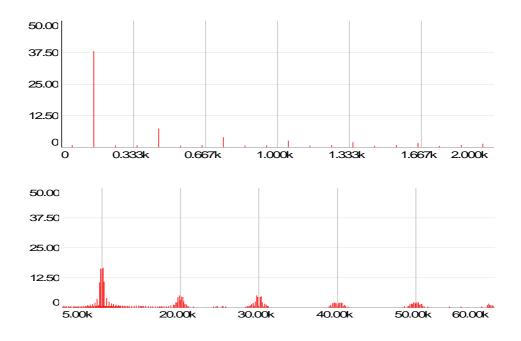

| 7.7 SPWM ripple current spectrum, low frequency harmonics (top, 12.5A/div,                         |

| 333Hz/div), high frequency harmonics (bottom, 12.5A/div, 10kHz/div),                               |

| $(M_i=0,3, \phi = 0^\circ, I_{om}=100 \text{ A})$ 110                                              |

|                                                                                                    |

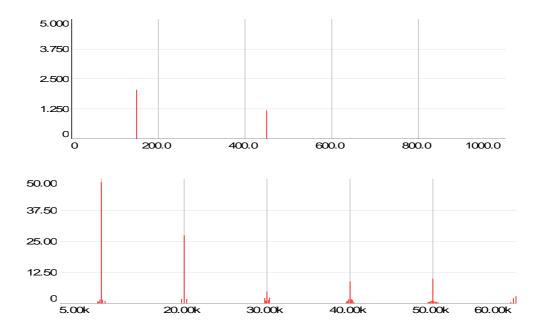

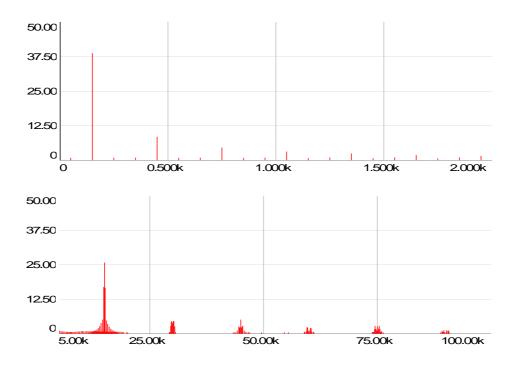

| 7.8 SVPWM ripple current spectrum, low frequency harmonics (top, 1.25A/div, 200Hz/div), high frequency harmonics (bottom, 12.5A/div, 10kHz/div), $(M_i=0,3, \phi = 0^\circ, I_{om}=100 \text{ A})$                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

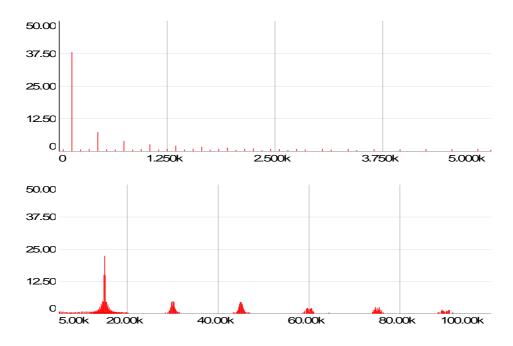

| <ul> <li>7.9 AZSPWM1 ripple current spectrum, low frequency harmonics</li> <li>(top, 12.5A/div, 333Hz/div), high frequency harmonics (bottom, 12.5A/div, 10kHz/div), (M<sub>i</sub>=0,3, φ = 0°, I<sub>om</sub>=100 A)</li></ul>    |

| 7.10 DPWM1 ripple current spectrum, low frequency harmonics<br>(top, 12.5A/div, 500Hz/div), high frequency harmonics (bottom, 12.5A/div, 25kHz/div), ( $M_i$ =0,7, $\phi = 0^\circ$ , $I_{om}$ =100 A)111                           |

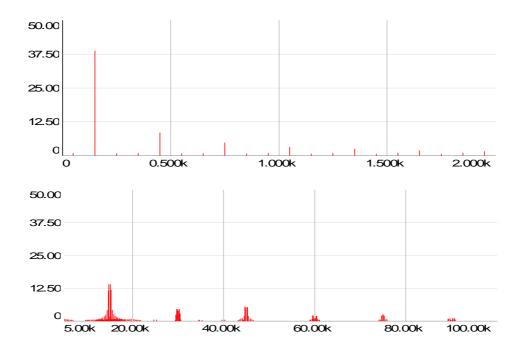

| <ul> <li>7.11 DPWM1 ripple current spectrum, low frequency harmonics</li> <li>(top, 12.5A/div, 1.25kHz/div), high frequency harmonics (bottom, 12.5A/div, 20kHz/div), (M<sub>i</sub>=0,7, φ = 30°, I<sub>om</sub>=100 A)</li></ul>  |

| 7.12 NSPWM ripple current spectrum, low frequency harmonics<br>(top, 12.5A/div, 20kHz/div), high frequency harmonics (bottom, 12.5A/div,<br>20kHz), (Mi=0,7, $\phi = 0^{\circ}$ , Iom=100 A                                         |

| <ul> <li>7.13 NSPWM ripple current spectrum, low frequency harmonics<br/>(top, 12.5A/div, 500Hz/div), high frequency harmonics<br/>(bottom, 12.5A/div, 25kHz/div), (M<sub>i</sub>=0,7, φ = 30°, I<sub>om</sub>=100 A)113</li> </ul> |

| 7.14 PD carrier waveforms: carrier for positive cycle of modulation waveform<br>(green ) and carrier for negative cycle of modulation waveform (blue)                                                                               |

| <ul> <li>7.15 Inner Integral calculation domains (grey region) for normal triangular carrier</li> <li>(left) and reverse triangular carrier (right) for positive cycle of modulation</li> <li>signal</li></ul>                      |

| <ul><li>7.16 Inner Integral calculation domains (grey region) for normal triangular carrier (left) and reverse triangular carrier (right) for negative cycle of modulation signal</li></ul>                                         |

# LIST OF TABLES

# TABLES

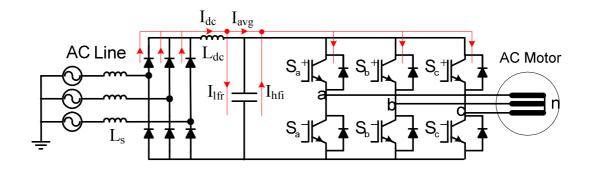

| 2.1 3-phase diode rectifier side simulation parameters               | 14  |

|----------------------------------------------------------------------|-----|

| 2.2 Dc bus current frequency spectrum comparison                     | 15  |

| 4.1 Comparison of capacitors [20]                                    | 36  |

| 4.2 ESR % ratio to ESR at 25 °C for aluminum electrolytic capacitors | 40  |

| 5.1 Rms and dominant harmonics of I <sub>hf</sub> of PWM methods     | 47  |

| 5.2 Transformerless UPS system operating points                      | 56  |

| 5.3 Regenerative motor drive with active front end                   | 58  |

| 5.4 Parameters of diode rectifier                                    | 59  |

| 5.5 Motor drive application operating points                         | 59  |

| 5.6 Simulation circuit parameters for typical application I          | 63  |

| 5.7 Simulation circuit parameters for typical application II.        | 67  |

| 5.8 Simulation circuit parameters for typical application III.       | 72  |

| 5.9 Parameters for inverter                                          | 78  |

| 6.1 Parameters for the motor drive system                            | 83  |

| 6.2 Operating points for the experimental data                       | 84  |

| 7.1 3L PWM VSI simulation parameters                                 | 105 |

#### **CHAPTER 1**

## **INTRODUCTION**

# 1.1 Three-Phase Voltage Source Inverters as Applied to AC Motor Drives and PWM Rectifiers

Different kinds of electrical energy sources like renewable energy sources, turbine driven AC generators exist. The distribution system is constructed to deliver this energy to the end user like factory, households, and so on. However, electrical energy must be conditioned in terms of voltage and current to such a degree that can be used by the end user. An example of this process is the conversion between DC sources (renewable energy sources) and AC sources (AC generators and AC distribution system) in order to construct a interconnected system or to drive AC driven machines (industrial motors like induction machine etc.) using DC source. Power electronic conversion devices have been invented for these purposes. Moreover, these power converter circuits improve the system efficiency, controllability and reliability.

There are many types of power converters today and VSI (voltage source inverter) is the mostly used one among them in a range of kilowatt to megawatt and it is used in different applications like industrial, military, and general purpose.

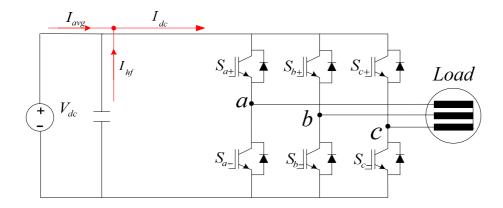

Figure 1.1 The dc bus current and its average and ripple components in the three phase two-level VSI topology

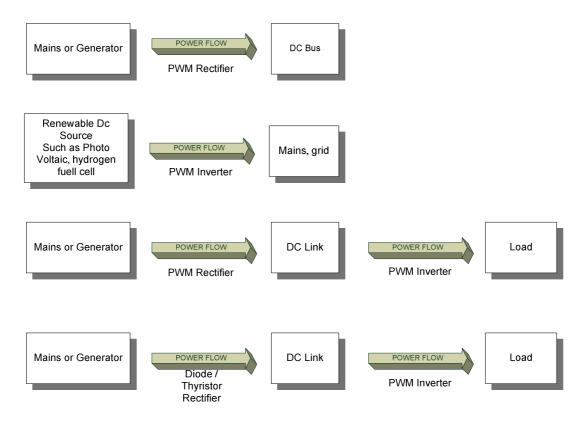

There are different conversion topologies and these can be grouped as four main types. In one application, AC voltage is converted directly to DC voltage and this process is called rectification. In order to minimize the harmonic current injected to the AC source (mains), and to sink sinusoidal current with desired low THD (total harmonic distortion) and with high power factor, the pulse width modulated (PWM) VSI is widely used and this process is shown at first row in Figure 1.2. Another application is the interfacing between renewable sources like photo voltaic panel, hydrogen fuel cell, and end user like residentals, factories or more generally the power system grid. In this interfacing process, the PWM VSI is used to inject very low THD and unity power factor sinusoidal current to the grid. Third application is the conversion from AC voltage to DC voltage via PWM rectifier and reconversion of DC voltage to AC voltage via PWM inverter. This type of application is used in regenerative drives and active filters that need dynamic circulation of energy back and forth through the switches of power converter. Elevator drive system, active power filtering system and UPS system are some examples for the use of this application. Last application is again an AC-DC-AC conversion but with the difference of rectifier stage. In this type, AC-DC conversion is done via diode / thyristor rectifier and used mostly in industrial AC motor drive with the dynamic control of magnitude and frequency of the output AC voltage.

Figure 1.2 Main application types

As seen from the topologies of main application types, the key element of such energy conversion systems is the PWM VSI.

In DC – AC conversion process of the PWM-VSI, the switches are switched at a frequency over 10-20 times of fundamental frequency in order to yield a sinusoidal output voltage or current after a low pass filtering process via LC circuit at the output. Moreover, in applications where there is no neutral return wire like industrial motor drive, some third harmonic patterns are inserted to the pure sinusoidal reference signal (modulation wave) and the magnitude of the pure sinusoidal output voltage per phase is increased as a result of the line to line cancellation of third harmonic voltages. This results in a better usage of DC Bus voltage that is limited. For this purpose and for other technical constraints, different modulation techniques have been invented.

#### **1.2 PWM Techniques**

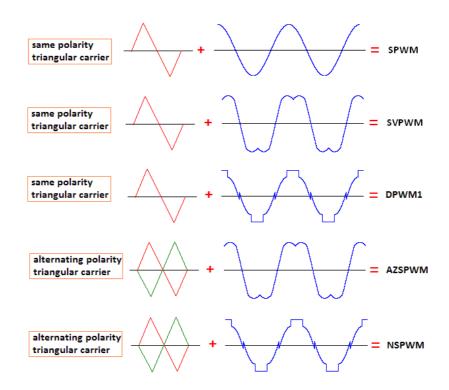

Among the various PWM methods existing, the following methods are popular due to their simplicity and performance advantages; sinusoidal PWM (SPWM), space vector PWM (SVPWM), discontinuous PWM (DPWM1) [1], active zero state PWM (AZSPWM1) [2], and near state PWM (NSPWM) [3]. The benefit of SPWM and SVPWM is low ripple at low M<sub>i</sub>, DPWM1 benefits with low ripple and low loss at high M<sub>i</sub>, and AZSPWM1 benefits with low common mode voltage and NSPWM benefits with both low common mode voltage and low losses at high M<sub>i</sub> [4]. While SPWM, SVPWM and DPWM1 employ a common carrier (triangle), AZSPWM1 and NSPWM employ alternating polarity triangles for each phase [5]. All these methods are easy to implement with modern inverter control chips with advanced PWM generation units. The modulation waves of these methods and the associated carrier signals are shown in Figure 1.3.

Figure 1.3 Two-level three-phase inverter popular PWM methods; the high frequency carrier waves (left) and the modulation waves (right)

#### **1.3 High Frequency Effects of PWM Operation**

PWM operation of the VSI effects the input side and the output side of the inverter system via injecting current harmonics at high frequency (carrier frequency and integer multiple of carrier frequency). The output of the inverter is composed of rectangular voltage pulses of which the low pass filtered value is the desired sinusoidal voltage or current. The input side (dc bus side) of the inverter sinks rectangular high frequency currents which must be filtered via dc bus capacitor.

In three-phase inverters, with PWM operation, the inverter input current (dc bus current,  $I_{dc}$  in Figure 1.1) consists of high frequency rectangular pulses. The average value  $I_{avg}$  comes from the supply, while the harmonic content (ripple current)  $I_{hf}$  is bypassed through the dc bus capacitor (filter capacitor). The ripple current frequency spectrum is at the carrier frequency (and its sidebands) and its multiples (and their sidebands). The dc bus PWM ripple current and its spectra depend on the modulation index  $M_i$ , PWM method, the load (output) current magnitude ( $I_{om}$ ), and the load power factor angle ( $\phi$ ) (or power factor PF=cos( $\phi$ )) [1], [2], [6], [7]-[9]. The dc bus current and its spectra affect the drive performance, thus influence the inverter design both from the dc bus voltage ripple and the dc bus capacitor losses (due to the capacitor equivalent series resistor (ESR) and/or dielectric losses) perspective. Thus, it is important to obtain the detailed dc bus ripple current characteristics for an effective inverter design.

The analysis of the dc bus current ripple has been previously investigated by means of rms ripple value [1], [2], [6] and by means of spectral component calculations [7]-[9] for various PWM methods. The rms ripple value obtained via closed form formulas is easy to use, yet it hides the spectral information, which is necessary in analysis and design. The spectral analysis could be conducted by means of detailed computer simulations (labor and computation intensive with case specific results) or by means of analytical methods, for example the double Fourier integral approach (more general, less computations, but requires math skills) [8]-[9]. While literature based on both rms and spectral methods provide various aspects of the dc

bus current ripple characteristics, comparison based on PWM methods and operating conditions ( $M_i$ ,  $\phi$ ,  $I_{om}$ ), understanding of the dominant frequency range in terms of ripple and losses, etc. is lacking.

The prime purpose of the dc bus current ripple analysis is the dc bus capacitor design and PWM method selection. However, this analysis by itself is not sufficient to complete the inverter design process. In various inverter applications, different capacitor types are used and each capacitor technology exhibits different ripple and loss attributes and involves different design rules. Thus, the utilization of the dc bus current ripple and spectrum analysis results requires that the capacitor technology is taken into account. For example, electrolytic and film capacitors have different loss mechanisms and different behavior. Therefore, for each type of application a different capacitor type and different design rules should be considered. For this purpose a basic dc bus capacitor technology classification and design issues should be discussed to guide a proper design. The capacitor suppliers/manufacturers usually provide capacitor operating condition data and give empirical design methods for the design engineer [10]-[15]. There is no clear understanding and a rigorous guide to the inverter design in terms of dc bus capacitor ripple and losses. Based on the above discussions it becomes obvious, a clear understanding of the dc bus ripple current characteristics and capacitor design study involves very detailed case by case study for each application.

This thesis work provides an analysis method and graphic tools to overcome these difficulties. In addition to the dc bus current ripple analysis, it also provides a fundamental review of the power electronic capacitor technologies (focused on inverter applications) which is required in the design. Combining the ripple current analysis and the capacitor technology information, it applies the approach to specific examples to be used in inverter design. It yields the information on correct PWM method and correct capacitor sizing, and then correct and simple dc bus capacitor performance prediction for a given application.

#### **1.4 Scope of The Thesis**

This thesis mainly focuses on the harmonic spectrum analysis of dc bus current of two level VSI at different operating conditions and under various modulation methods. The thesis evaluates the harmonic spectrum microscopically and globally, and then provides frequency-local spectral information (termed as the centered harmonic) that is useful and simple for dc bus ripple performance evaluation.

The second contribution involves a 3D harmonic analysis graph that can be used as a quick design guide which gives dc bus current harmonic spectrum up to the fourth integer multiple of switching frequency over various modulation index and output power factor operating points for all five types of modulation methods. With the help of this graphic, the choice of appropriate PWM method for a specific inverter application becomes easily visible. Likewise, performance evaluation with simple calculations becomes possible.

The final contribution of the thesis is the algorithm for the selection of dc bus capacitor for different applications and an estimation of the ripple over dc bus voltage.

In the 2<sup>nd</sup> chapter, a summary of different application topologies using the PWM-VSI will be given.

In the 3<sup>rd</sup> chapter, dc bus current ripple of VSI will be thoroughly studied; ripple current characteristics depending on the operating point and PWM technique utilized will be examined. The microscopic (per PWM cycle), the rms, and spectral components will be discussed for various PWM method and operating conditions. The double Fourier analysis approach will be briefly reviewed and utilized to generate the spectral data. Then the equivalent centered harmonic approach will be proposed and its results will be demonstrated. After the introduction of the method, the design stage will be elaborated on. Moreover, PWM methods in terms of dc bus ripple performance will be compared.

In the 4<sup>th</sup> chapter, power electronic capacitors are reviewed and the film and electrolytic capacitors suitable for PWM-VSI application are investigated in detail.

In the 5<sup>th</sup> chapter, different design examples are introduced on application basis. After that, a rectifier system simulation results are demonstrated and they are compared with analytical calculation results. Moreover, output current harmonic is studied with some simulation examples.

In the  $6^{th}$  chapter, experimental results for dc bus current spectra for various loads and operating conditions will be evaluated and compared with the calculation based methods.

In the 7<sup>th</sup> chapter, DC Bus current harmonic spectrum calculation of three level inverters will be briefly discussed as an extension of the developed technique to more advanced inverter topologies.

In the 8<sup>th</sup> chapter, all the work will be summed up and future work recommended.

#### **CHAPTER 2**

### TOPOLOGIES AND BASIC APPLICATIONS

#### **2.1 Introduction**

PWM VSIs are widely used in energy conversion applications with their high efficiency and low distortion characteristics. They are used as rectifier, inverter or both of them depending on the desired direction of power flow for the given application. Moreover, PWM VSIs can be used as the inverter side of rectifier / inverter cascaded system that contains diode / thyristor rectifier stage that interfaces the dc link with the mains.

As mentioned in Chapter 1, application types can be grouped in four main types in which the circulation path and magnitude – frequency relation of high frequency dc bus current differ. The mentioned three-phase power conversion topologies and their dc bus current characteristics will be explained in the following sections. In the simulations of these topologies, the peak of the sinusoidal input or output current of PWM converter side of these topologies is 100A per phase.

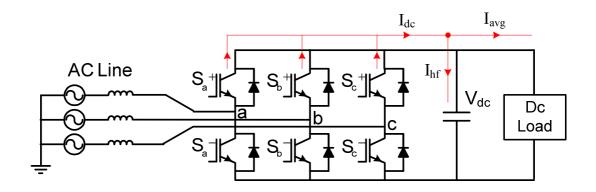

## 2.2 PWM Rectifier

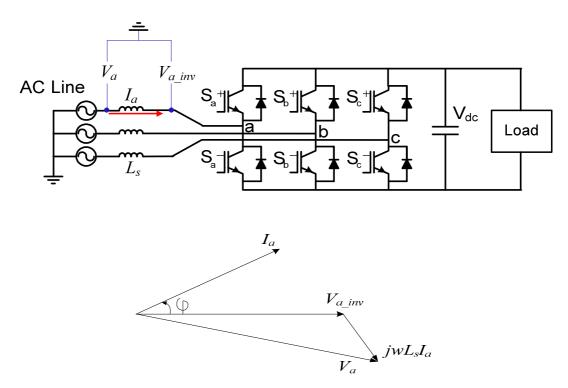

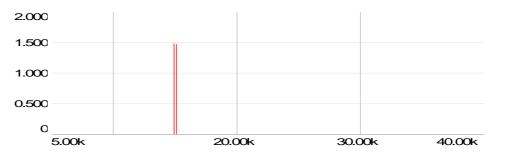

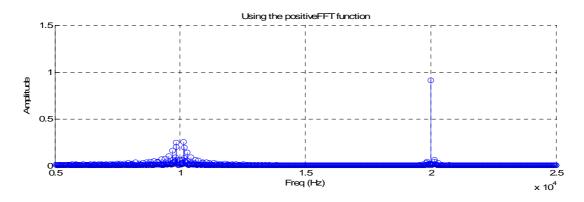

PWM rectifiers are increasingly utilized in applications with constant dc bus voltage requirement, typically feed passive loads. PWM rectifiers have the same  $I_{dc}$  harmonic characteristics with the PWM inverters, however, they have some differences such as the usage of freewheeling diodes of inverter switches and the direction of power flow which is from AC side to DC side. High frequency

component of dc link current  $(I_{hf})$  circulates between switches and the dc bus capacitor as seen in Figure 2.1 and the harmonic spectrum of  $I_{dc}$  is seen in Figure 2.2 for a given operating condition in which the dominant current harmonic is located at double  $f_s$  (30 kHz). The magnitude of the spectrum decreases with the increasing frequency.

Figure 2.1 PWM rectifier topology and the current distribution

Figure 2.2 Harmonic spectrum of dc link current  $I_{dc}$  for a working condition of NSPWM,  $M_i = 0.7$ ,  $\phi = 0^\circ$ ,  $f_c=15$ kHz, (12.5A/div, 20kHz/div)

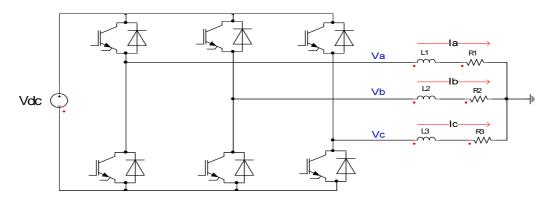

### 2.3 PWM Inverter

PWM Inverters are mostly used in motor drive, interfacing between regenerative sources and mains, and other AC supply applications with their capability of power flow from DC side to AC side. Actually their topology are same with rectifier, however, inverter controller drives six switches (Sx+, Sx-, x = a,b,c) in such a way

that all inverter legs act as buck converter and pumps AC current to the load after a low pass filtering stage of LC filter.  $I_{hf}$  circulates between dc bus capacitor and the inverter switches. A sample of harmonic spectrum of  $I_{dc}$  is seen in Figure 2.4 for a given operating condition. The only difference of inverter is the direction of power flow and the usage of semiconductor devices (the usage of freewheeling diode is lower than rectifier application) compared with the rectifier application. The dc bus current harmonic spectrum is same as in the rectifier. The spectral analysis in chapter 3 is based on this inverter structure.

Figure 2.3 PWM VS Inverter topology and current distribution with 3Ø motor load

Figure 2.4 Harmonic spectrum of dc link current  $I_{dc}$  for a working condition of NSPWM,  $M_i = 0.7$ ,  $\phi = 0^\circ$ ,  $f_c=15$ kHz (12.5A/div, 20kHz/div)

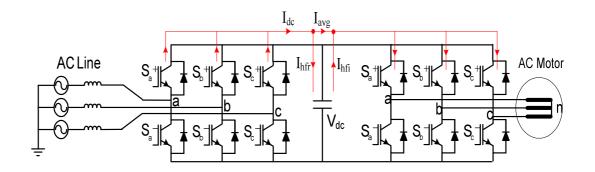

## 2.4 PWM Rectifier Cascaded with PWM Inverter

In UPS (uninterruptible power source) applications and in motor drive applications that includes regenerative characteristics where power flow is bidirectional, *inverter cascaded rectifier*, in other words *back to back inverter topology*, is commonly

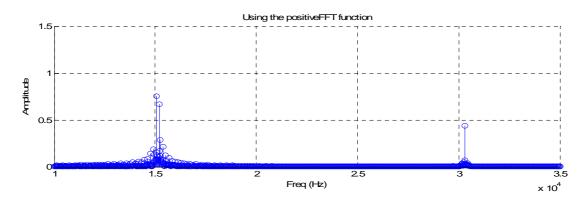

used. In this topology, I<sub>hf</sub> (high frequency current component) is composed of two parts which are rectifier side high frequency current component (Ihfr) and inverter side high frequency current component (Ihfi). Typically both sides operate at the same PWM frequency, and depending on the phase difference between triangular carriers of rectifier and inverter, these high frequency components can be added or subtracted algebraically or can be added in phasor domain depending on the polarities and frequencies of triangular carriers of both sides. If the frequencies are different, then (2.1), where magnitudes are rms, can be directly used to calculate the overall rms value of I<sub>hf</sub>. If the carriers are in the same frequency but not in phase, I<sub>hf</sub> is higher than the right side of (2.1). If the carriers are in the same frequency and in phase, then  $I_{hf}$  is smaller than the right side of (2.1). In the harmonic spectrum of Figure 2.6, triangular carriers are in the same frequency and in phase and thus some of the harmonic of rectifier side is cancelled with the harmonic of inverter side. Therefore the harmonic spectrum is flatter than the case in which carrier frequencies are different. This case is shown in Figure 2.7 with the same simulation parameters except the carrier frequencies. If the modulator types were the same in the case in which carriers are in the same phase with same frequency, the cancellation of Ihfr and I<sub>hfi</sub> would be better.

$$I_{hf} = \sqrt{I_{hfr}^2 + I_{hfi}^2}$$

(2.1)

Figure 2.5 Back to back inverter topology and the current distribution

Figure 2.6 Harmonic spectrum of dc link capacitor current  $I_{hf}$  for rectifier working condition of NSPWM,  $M_i = 0.7$ ,  $\phi = 0^\circ$ ,  $f_c=10$ kHz and inverter working condition of SVPWM,  $M_i = 0.7$ ,  $\phi = 0^\circ$ ,  $f_c=10$ kHz (12.5A/div, 20kHz/div)

Figure 2.7 Harmonic spectrum of dc link capacitor current  $I_{hf}$  for rectifier working condition of NSPWM,  $M_i = 0.7$ ,  $\phi = 0^\circ$ ,  $f_c = 15$  kHz and inverter working condition of SVPWM,  $M_i = 0.7$ ,  $\phi = 0^\circ$ ,  $f_c = 10$  kHz, (12.5A/div, 20kHz/div)

#### 2.5 Diode / Thyristor Rectifier Cascaded with PWM Inverter

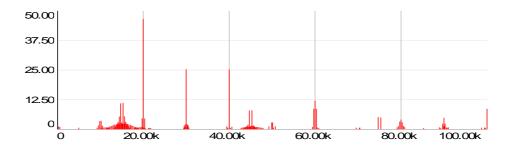

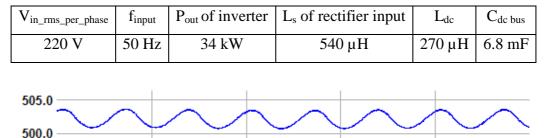

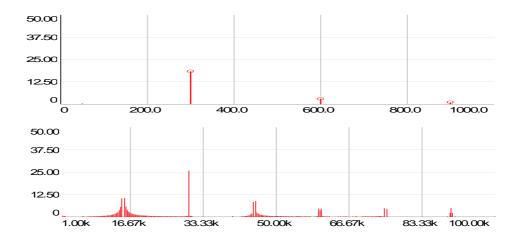

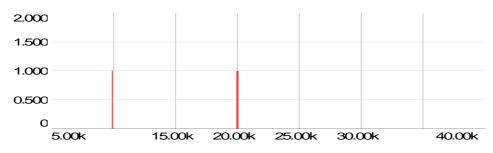

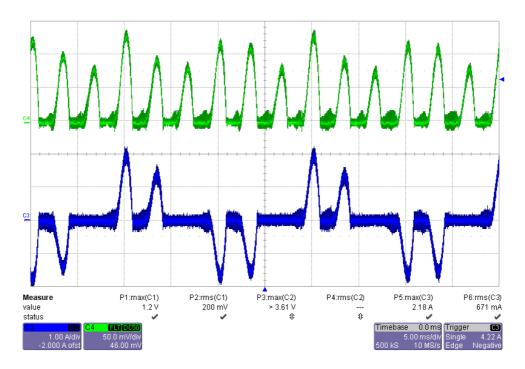

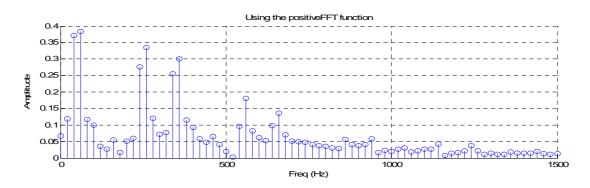

This topology is different from other topologies in the sense that rectifier stage is composed of diodes or thyristors that switch at low frequency (fundamental frequency). This causes injection of dc bus current at low frequency and harmonics at low frequency (6 times the fundamental frequency and its multiples) as seen in Figure 2.9. In order to filter this low frequency current, dc bus capacitor size must be large enough. The harmonic spectrums of  $I_{lfr}$  and  $I_{hfi}$  are illustrated in Figure 2.10.

The simulation parameters used to output the waveform of Figure 2.9 and the spectrum of Figure 2.10 are tabulated in Table 2.1. As observed in the simulation data, at low frequency, the dominant harmonic is located at 300 Hz for the fundamental frequency of 50 Hz and the magnitude of the spectrum decreases rapidly with the increasing frequency. At high frequency, the typical spectrum is observed for the given operating condition.

Figure 2.8 Diode / thyristor rectifier cascaded with PWM inverter

100.0

75.0

50.0

25.0

0

75.00m

80.00m

Table 2.1 3-phase diode rectifier side simulation parameters

90.00m

95.00m

100.00m

85.00m

14

Figure 2.10 Low frequency (top) and high frequency (bottom) harmonic spectrum of  $I_{dc}$  of rectifier with 34 kW output power and inverter working condition of NSPWM,  $M_i = 0.7$ ,  $\phi = 0^\circ$ , (12.5A/div, 16.67kHz/div)

| Topology                    | Dc bus ripple current |           |           |

|-----------------------------|-----------------------|-----------|-----------|

| Source                      | Load                  | Source    | Load      |

| side                        | side                  | side      | side      |

| diode / thyristor rectifier |                       | low       |           |

| pv / dc battery             | PWM                   | frequency | high      |

| PWM transistor rectifier    | inverter              | high      | frequency |

|                             |                       | frequency |           |

Table 2.2 Dc bus current frequency spectrum comparison

At PWM driven sides of these topologies, the dc bus current spectrum changes depending on the pwm method and operating point. Therefore they are important in evaluation of the dc bus performance and design. The topologies and the frequency content of their dc buses are tabulated in Table 2.2. In all these topologies, the PWM structure is common and the core point. Since, diode / thyristor rectifier needs much dc bus capacity with its dc bus current harmonics at low frequency and it injects much current harmonics to mains, this kind of converter is not focused on in this work.

In the next chapter, the detailed analysis of  $I_{dc}$  harmonic spectrum of PWM structure depending on various operating conditions will be done and also a new concept of equivalent harmonic approach, which means grouping the fringe harmonic components under the umbrella of center harmonic, will be introduced.

## **CHAPTER 3**

## ANALYSIS AND CHARACTERIZATION OF DC BUS RIPPLE CURRENT

## **3.1 Introduction**

As mentioned in previous chapters, three-phase Voltage Source Inverters (VSIs) are widely utilized in ac motor drives, uninterruptible power supplies (UPS), renewable energy systems, etc. to control the energy flow precisely, obtain high power quality and high energy efficiency. Pulse Width Modulation (PWM) is the standard approach to operate the inverter switches in order to generate the required output voltages. Due to high frequency switching both the ac and the dc side of the inverter involve high frequency rectangular voltage/current pulses that create stress on the inverter components. This chapter studies the dc bus ripple current due to the PWM operation, and it elaborates on the stresses the ripple creates on the dc bus capacitor.

In this chapter, dc bus current ripple of VSI will be inspected; ripple current characteristics depending on the operating point and PWM technique utilized will be studied. The microscopic (per PWM cycle), the rms, and spectral components will be discussed for various PWM method and operating conditions. The double Fourier analysis approach will be briefly reviewed and utilized to generate the spectral data. Then the equivalent centered harmonic approach (EHA) will be proposed and its results will be demonstrated. After the demonstration of the method, 3D  $I_{dc}$  graph will be shown as a design tool based on EHA.

#### **3.2 Dc Bus Current Ripple of VSI**

This section reviews the dc bus current ripple of the three-phase, two-level inverter for various operating conditions and PWM methods. The main purpose is to provide a basic tutorial before attempting advanced analysis. First via microscopic waveforms the physical understanding will be established. Second via evaluation of the spectral components the dominant frequency range will be shown. In this section, the spectral data used will be based on the double Fourier approach (also verified by means of computer simulations). Finally the ripple current rms value for various PWM methods will be evaluated for various PWM methods and operating condition.

It is helpful to define a modulation index ( $M_i$ , voltage utilization level) term at this stage. For a given dc link voltage ( $V_{dc}$ ), the ratio of the fundamental component magnitude of the line to neutral inverter output voltage ( $V_{1m}$ ) to the fundamental component magnitude of the six-step mode voltage ( $V_{1m-6-step} = 2V_{dc}/\pi$ ) is termed the modulation index  $M_i$  [1] as defined in (3.1).

$$M_{i} = V_{1m} / V_{1m-6-step}$$

(3.1)

The inverter under analysis is the three phase, three wire PWM VSI and the inverter is assumed to be loaded with balanced three phase sinusoidal output current at steady state operation.

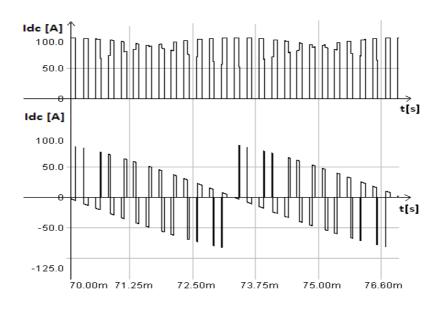

### 3.2.1 Microscopic View

Under balanced, sinusoidal steady state operation, the inverter dc bus current ripple instantaneous waveforms appear as picket-fences (as rectangular pulses at the carrier frequency or higher) and their outer appearance depends on the load current magnitude (I<sub>om</sub>) and power factor, as shown in Figure 3.1 (obtained by computer simulations for SVPWM). The magnitude of the sinusoidal load current is the prime factor in determining the magnitude of current pulses. With unity power factor, the current pulses are always with positive value. However, with decreasing power

factor negative current pulses appear in the waveform. The balanced sinusoidal output current waveforms are expressed in (3.2), the average value of the dc bus current ( $I_{avg}$ ) is expressed in (3.3), and it is supplied by the dc voltage source. The difference of  $I_{dc}$  and  $I_{avg}$  is defined as the ripple current  $I_{hf}$  as given in (3.4), and it is bypassed through the dc bus capacitor. The phase currents are assumed as balanced cosinusoidal with the peak of  $I_{om}$  and lagging power factor of  $cos \varphi$ .

$$I_{a} = I_{om} \cdot \cos(\omega t - \varphi)$$

$$I_{b} = I_{om} \cdot \cos(\omega t - \frac{2\pi}{3} - \varphi)$$

$$I_{c} = I_{om} \cdot \cos(\omega t - \frac{4\pi}{3} - \varphi)$$

(3.2)

$$I_{avg} = \left(\frac{3}{\pi}\right) \cdot M_i \cdot I_{om} \cdot \cos \phi \tag{3.3}$$

$$I_{\rm hf} = I_{\rm dc} - I_{\rm avg} \tag{3.4}$$

While Figure 3.1 is obtained for SVPWM, it is difficult to distinguish it from the waveforms of other PWM methods by outer appearance. However, as will be shown, in the detailed (microscopic) view, significant differences exist. Thus, the harmonic spectrum of different modulation techniques can be correlated with microscopic analysis of dc bus current within a switching period.

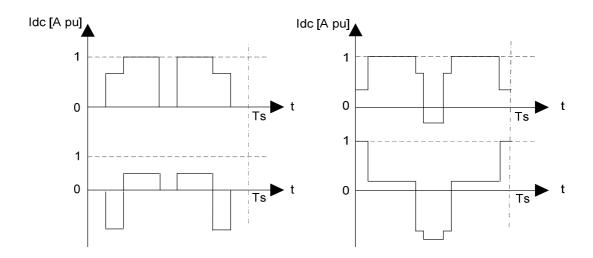

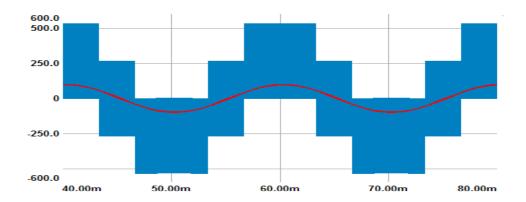

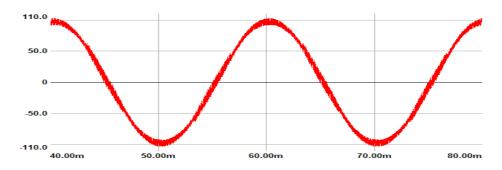

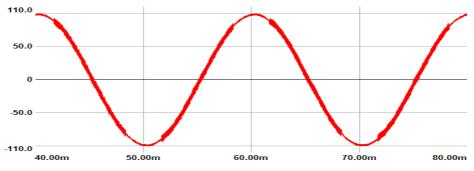

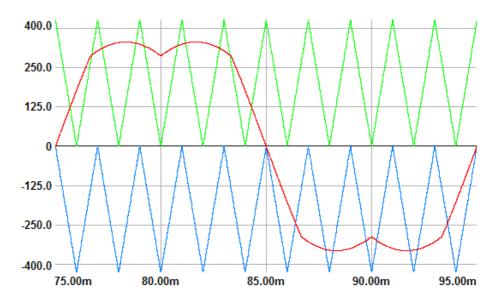

As Figure 3.2 shows, in SVPWM and AZSPWM1,  $I_{dc}$  is composed of two rectangles in a PWM cycle. Thus, they are expected to result in dominant harmonics centered at double the switching frequency (2f<sub>c</sub>). For  $\varphi = 0^{\circ}$  the rectangle is full with high average value and low ripple. For  $\varphi = 90^{\circ}$  the rectangle has low average value and high ripple. Thus, high power factor implies low ripple current. As shown in Figure 3.3, for DPWM1 and NSPWM, the rectangles are gathered into one piece. Based on the appearance of the waveform shapes, it becomes obvious now strong harmonics exist at both  $f_c$  and  $2f_c$ . For  $\varphi = 0^{\circ}$  the rectangle is full with high average value and low ripple. For  $\varphi$  shapes, it becomes obvious now strong harmonics exist at both  $f_c$  and  $2f_c$ . For  $\varphi = 0^{\circ}$  the rectangle is full with high average value and low ripple. For  $\varphi$  increasing the rectangle has low average value and high ripple. Thus, high power factor implies low ripple current. In particular, in NSPWM

the  $\varphi$  dependency is strong and the performance rapidly degrades as  $\varphi$  approaches 30°. Apparent from this discussion, the visual observation does not yield sufficient information about the ripple content and spectral analysis is necessary.

Figure 3.1 DC bus current waveform over a 60° of a fundamental cycle for SVPWM under the operating conditions of  $M_i$ =0,785,  $I_{om}$ =100 A. Top:  $\phi = 0^\circ$ , bottom  $\phi = 90^\circ$ , (50A/div, 1.25ms/div)

Figure 3.2 Inverter microscopic dc bus currents in a PWM period for continuous PWM methods; Left: SVPWM ( $M_i$ =0.7, top:  $\phi = 0^\circ$ , bottom  $\phi = 90^\circ$ ), Right: AZSPWM1 ( $M_i$ =0.7, top:  $\phi = 0^\circ$ , bottom  $\phi = 90^\circ$ )

Figure 3.3 Inverter microscopic dc bus currents in a PWM period for discontinuous PWM methods; Left: DPWM1 ( $M_i$ =0.7, top:  $\phi = 0^\circ$ , bottom  $\phi = 90^\circ$ ), Right: NSPWM ( $M_i$ =0.7, top:  $\phi = 0^\circ$ , bottom  $\phi = 30^\circ$ )

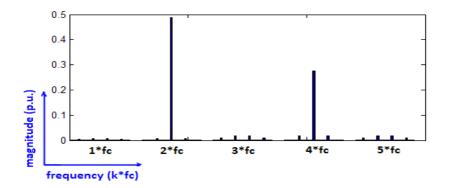

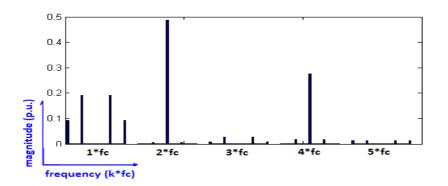

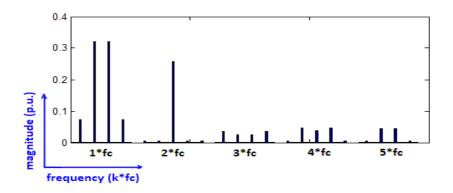

## **3.2.2 Spectral Content**

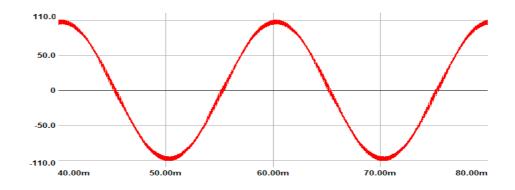

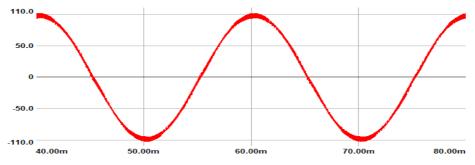

As apparent from the preceding section, the spectral content of the dc bus ripple current is PWM method dependent, as well as the operating conditions. To illustrate typical spectral content, several methods and operating conditions are considered. A three-phase inverter drive is considered. Balanced sinusoidal operation is assumed. The load current ripple is neglected. The discussed PWM methods with a pure-sinusoidal, 100A peak value rated output current, with 50Hz fundamental frequency are considered. The inverter DC bus is 800V and the carrier frequency (f<sub>c</sub>) is 10kHz for SVPWM and AZSPWM1 and 15kHz for NSPWM and DPWM1 such that the average switching frequency is the same (10kHz) in all cases. By this way, continuous and discontinuous PWM methods cause same power loss on the inverter switches which means the same thermal stress inserted on the inverter.

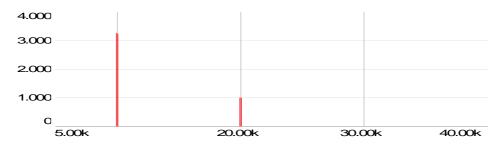

The harmonic spectrum for various methods is shown from Fig. 3.4 to Fig. 3.9 for various operating conditions. As shown in Figure 3.4 and Figure 3.5, for SVPWM and AZSPWM1 at low  $M_i$  the dominant harmonics are at twice the carrier frequency  $2f_c$  (AZSPWM1 has some notable harmonics at  $f_c$  also). As shown in Figure 3.6 and Figure 3.7, DPWM1 dominant harmonics are at  $f_c$ . As shown in

Figure 3.8 and Figure 3.9, NSPWM has harmonics both at  $f_c$  and  $2f_c$ . Depending on  $\phi$  and  $M_i$ , the dominant term may become at  $f_c$  or  $2f_c$ . While  $2f_c$  harmonic is dominant for  $\phi = 0^\circ$ ,  $f_c$  harmonic is dominant for  $\phi = 30^\circ$ .

Figure 3.4 Ripple current spectrum (0.1A-pu/div), SVPWM,  $M_i$ =0,3,  $\phi$  = 0°,  $I_{om}$ =100 A

Figure 3.5 Ripple current spectrum (0.1A-pu/div), AZSPWM1, M<sub>i</sub>=0,3,  $\phi = 0^{\circ}$ ,  $I_{om}$ =100 A

Figure 3.6 Ripple current spectrum (0.1A-pu/div), DPWM1, M\_i=0,7,  $\phi$  = 0°,  $I_{om}$ =100 A

Figure 3.7 Ripple current spectrum (0.1A-pu/div), DPWM1, M\_i=0,7,  $\phi$  = 30°,  $I_{om}{=}100~A$

Figure 3.8 Ripple current spectrum (0.1A-pu/div), NSPWM, M\_i=0,7,  $\phi$  = 0°,  $I_{om}{=}100~A$

Figure 3.9 Ripple current spectrum, (0.1A-pu/div), NSPWM,  $M_i=0.7$ ,  $\varphi = 30^\circ$ ,

$I_{om}$ =100 A

#### 3.2.3 Total RMS Value

In order to compare the DC link current ripple performance of the PWM methods, the ratio of the harmonic rms value of the DC link current  $I_{h-rms}$  to the inverter AC output fundamental component current rms value  $I_{1rms}$  ( $I_{om}/\sqrt{2}$ ) is evaluated and its square is termed as the dc link current coefficient  $K_{dc}$  [1]-[3] defined in (3.5).

$$K_{dc} = I^{2}_{h-rms} / I^{2}_{1rms}$$

(3.5)

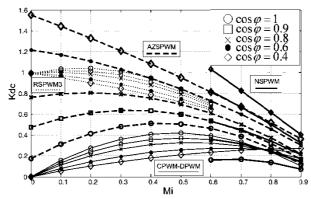

For given  $M_i$  and  $\varphi$ , the RMS ripple DC link current is first calculated over a PWM cycle, then over a fundamental cycle to obtain  $I_{h-rms}$ . Then (3.5) is analytically calculated for all the methods discussed. Evaluating  $K_{dc}$  reveals some important attributes of the modulators. As Figure 3.10 indicates, all methods are  $M_i$  and  $\varphi$  dependent. The reduced common mode voltage PWM methods have several times higher DC link current stress than the SVPWM and DPWM methods. At low  $M_i$  AZSPWM1 (especially at low  $\cos\varphi$ ) method exhibits large stresses. At higher  $\cos\varphi$  the AZSPWM1 stresses become less. At higher  $M_i$  the DC link current stresses of the AZSPWM1 method become comparable to the conventional methods due to the expiration of the active zero state duration. The DC link current harmonic content of NSPWM is strongly dependent on PF and  $M_i$ .  $K_{dc}$  of NSPWM decreases with increasing  $M_i$  and PF. For PF = 1, NSPWM has lower DC link ripple content than all other PWM methods. For PF of 0.8-0.9,  $K_{dc}$  of all PWM methods are similar. However, for PF lower than 0.6,  $K_{dc}$  of NSPWM is inferior to other methods.

Figure 3.10 RMS ripple current characteristics,  $K_{dc} = f(M_i, \cos \phi)$  for various PWM methods

#### **3.3 Ripple Current Spectral Analysis**

As apparent from the preceding section, the ripple current harmonic content is highly PWM method and operating point dependent. For inverter design and analysis purposes, it is necessary to have broad information on the spectra. Thus, a method to calculate the spectral content and a simple approach to be utilized in the inverter design is required. While detailed simulations are exhaustive and not intuitive, the simple rms value approach is insufficient. Thus in this section the double Fourier approach [7]-[9] will be utilized to obtain the spectral data, and in the next section a method to provide a simple design tool based on the data obtained from the double Fourier approach will be introduced. The general analytical approach to obtain the exact harmonic content of periodically switching circuits involves the double Fourier approach. In this approach, first, the phase current functions as in (3.2) and the PWM switching functions as in (3.6), (3.7), and (3.8)are defined. Second, these functions are algebraically manipulated to obtain a raw  $I_{dc}$  function as in (3.13) to be processed in the double integral of (3.14) in order to calculate the harmonic coefficients. For the cosine modulation expressed in (3.6), the fourier integral of (3.14) can be expanded as in (3.10) by using the trigonometric identity in (3.9) and using the bessel function of the first kind expressed in (3.11), the closed form expression of the harmonic spectrum coefficients are obtained as in (3.12).

The closed form expression for cosine modulation is obtained easily and systematically expanding the double fourier integral to the bessel function, however, it is impossible to get such a closed form bessel expression for the other modulation functions since these modulation functions are piecewise as in (3.7) for SVPWM and in (3.8) for DPWM1 modulators. Thus, for these modulators and other modulators with phase reversing carrier (NSPWM, AZSPWM1), the double fourier integral is calculated numerically using matlab code as illustrated in appendix.

In (3.2), the phase currents are defined as balanced three phase cosinusoidal currents with the magnitude  $I_{om}$ . In (3.14),  $F(\cdot)$  is the double Fourier transform where p = a, b, c and  $y = \omega_c t$ ,  $x = \omega_f t$ . Moreover,  $S_p$  denotes switching function and  $M_p$  denotes modulation function. All three phase modulation functions are 120° phase shifted and denoted as  $M_a, M_b, M_c$ .

From the linearity of fourier transform, fourier transform of the  $I_{dc}$  is decomposed into fourier transform of switched phase leg currents. These leg current transforms are added linearly as in (3.15) and the magnitudes of  $I_{dc}$  harmonic components are calculated via using (3.16).

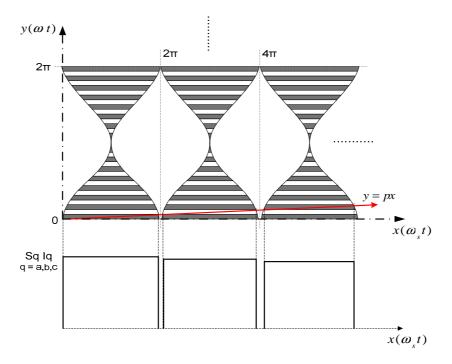

In Figure 3.11, each  $(2\pi, 2\pi)$  region involves a bounded wall structure which is laterally bounded with modulation function (modulation function is SPWM in Figure 3.11). The top (towards the reader) bound of the walls is the output sinusoidal current function which also changes sinusoidally up and down at the fundamental frequency with respect to y axis. Moreover, this pattern repeats itself over (x, y) plane.

$$M(\omega t) = \cos(\omega t) \tag{3.6}$$

$$M(\omega t) = \begin{cases} \frac{\sqrt{3}}{2} \cdot M \cdot \cos\left(\omega t - \frac{\pi}{6}\right), & 0 < \omega t < \frac{\pi}{3} \\ & \cup & \pi < \omega t < \frac{4\pi}{3} \\ \frac{3}{2} \cdot M \cdot \cos(\omega t), & \frac{\pi}{3} < \omega t < \frac{2\pi}{3} \\ & \cup & \frac{4\pi}{3} < \omega t < \frac{5\pi}{3} \\ \frac{\sqrt{3}}{2} \cdot M \cdot \cos\left(\omega t + \frac{\pi}{6}\right), & \frac{2\pi}{3} < \omega t < \pi \\ & \cup & \frac{5\pi}{3} < \omega t < 2\pi \end{cases}$$

(3.7)

$$M(\omega t) = \begin{cases} 1, & \frac{-\pi}{6} < \omega t < \frac{\pi}{6} \\ \sqrt{3} \cdot M \cdot \cos\left(\omega t - \frac{\pi}{6}\right) - 1, & \frac{\pi}{6} < \omega t < \frac{\pi}{2} \\ \sqrt{3} \cdot M \cdot \cos\left(\omega t + \frac{\pi}{6}\right) + 1, & \frac{\pi}{2} < \omega t < \frac{5\pi}{6} \\ -1, & \frac{5\pi}{6} < \omega t < \frac{7\pi}{6} \\ \sqrt{3} \cdot M \cdot \cos\left(\omega t - \frac{\pi}{6}\right) + 1 & \frac{7\pi}{6} < \omega t < \frac{3\pi}{2} \\ \sqrt{3} \cdot M \cdot \cos\left(\omega t + \frac{\pi}{6}\right) - 1 & \frac{3\pi}{2} < \omega t < \frac{11\pi}{6} \end{cases}$$

(3.8)

$$\cos\theta = \frac{1}{2} \cdot \left( e^{j\theta} + e^{-j\theta} \right) \tag{3.9}$$

$$F(S_{p} \cdot I_{p}) = \frac{I_{om}}{j4\pi^{2}m} \cdot \left[e^{j\left(m\frac{3\pi}{2}-\varphi\right)} \int_{0}^{2\pi} e^{j(n+1)y} \cdot e^{j(m \cdot \frac{\pi}{2} \cdot M \cdot \cos(y))} \cdot dy - e^{j\left(m\frac{\pi}{2}-\varphi\right)} \int_{0}^{2\pi} e^{j(n+1)y} \cdot e^{j(-m \cdot \frac{\pi}{2} \cdot M \cdot \cos(y))} \cdot dy + e^{j\left(m\frac{3\pi}{2}+\varphi\right)} \int_{0}^{2\pi} e^{j(n-1)y} \cdot e^{j(m \cdot \frac{\pi}{2} \cdot M \cdot \cos(y))} \cdot dy - e^{j\left(m\frac{\pi}{2}+\varphi\right)} \int_{0}^{2\pi} e^{j(n-1)y} \cdot e^{j(-m \cdot \frac{\pi}{2} \cdot M \cdot \cos(y))} \cdot dy\right]$$

(3.10)

$$J_n(Z) = \frac{j^{-n}}{2\pi} \cdot \int_0^{2\pi} e^{jZ\cos(\theta)} \cdot e^{jn\theta} \cdot d\theta$$

(3.11)

$$F(S_{p} \cdot I_{p}) = \frac{I_{om} \cdot j^{n}}{2\pi m} \cdot \left[ e^{j\left(m\frac{3\pi}{2} - \varphi\right)} \cdot J_{n+1}\left(m \cdot \frac{\pi}{2} \cdot M\right) - e^{j\left(m\frac{\pi}{2} - \varphi\right)} J_{n+1}\left(-m \cdot \frac{\pi}{2} \cdot M\right) - e^{j\left(m\frac{\pi}{2} + \varphi\right)} J_{n-1}\left(-m \cdot \frac{\pi}{2} \cdot M\right) \right]$$

for

$$n = -\infty \dots +\infty$$

and  $m = 1, 2, 3, \dots$  (3.12)

$$I_{dc} = S_a I_a + S_b I_b + S_c I_c$$

$$F(I_{dc}) = F(S_a I_a) + F(S_b I_b) + F(S_c I_c)$$

(3.13)

$$F(S_p \cdot I_p) \equiv \frac{1}{2\pi^2} \cdot \int_0^{2\pi} \left( \int_{\frac{\pi}{2}(1-M_p(y))}^{\frac{\pi}{2}(3+M_p(y))} I_p e^{j(mx+ny)} \, dx \right) \, dy \tag{3.14}$$

$$A_{mn} + jB_{mn} = \sum_{p=a,b,c} F(S_p \cdot I_p)$$

(3.15)

$$I_{mn} = \sqrt{A_{mn}^2 + B_{mn}^2}$$

(3.16)

Figure 3.11 Repeated wall structure with natural triangular sampling

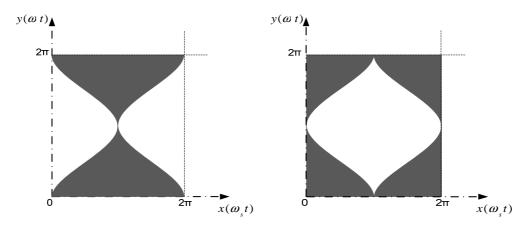

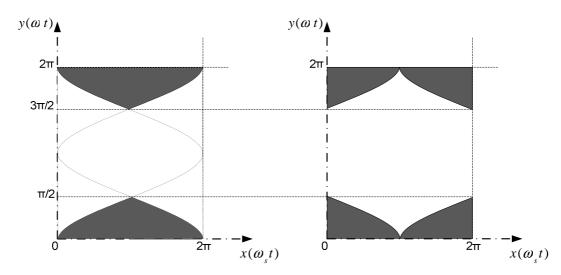

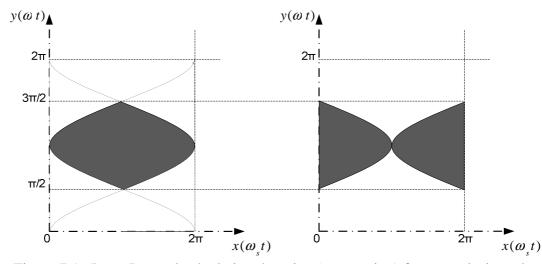

In Figure 3.12, shaded areas are the integration domains that construct the inner integral limits in (3.14) for sinusoidal PWM (SPWM). For other PWM methods, the boundary of the shaded region (modulation function) is changed depending on the PWM waveform under analyze.

Figure 3.12 Integration domains for inner integral of double fourier transform for SPWM. Fourier Integral is calculated in the left domain in the case of normal triangular carrier and calculation is done in the right domain in the case of reverse triangular carrier

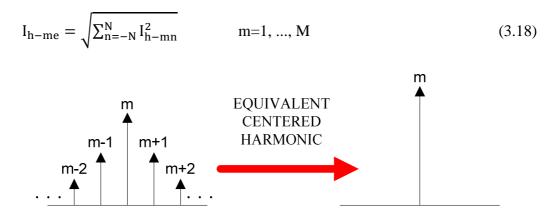

The general spectrum calculation algorithm works as follows: In terms of equations, using the integral of (3.14), the coefficients  $A_{mn}$  and  $B_{mn}$  are obtained as in (3.15), then the ripple current magnitude for each frequency is obtained as  $I_{mn}$  in (3.16). Here m corresponds to the carrier frequency and its multiples, and n corresponds to the fundamental component and its multiples. Thus, the harmonics are at the mf<sub>c</sub>±nf<sub>o</sub>. As a result, the dc link current is obtained as the fourier series expansion F(x,y) given in (3.17). Of the four terms in (3.17), the first one gives the average current of (3.3). The second term gives the possible sub-carrier frequency components. The third term gives the carrier frequency and its multiples (center frequency harmonics). And the final term gives the sideband harmonics for the carrier and its multiples. The details of the double Fourier approach as applied to dc current ripple calculation are laid out in [9].