### ZERO-LEVEL PACKAGING OF MICROWAVE AND MILLIMETERWAVE MEMS COMPONENTS

# A THESIS SUBMITTED TO THE GRADUATE SCHOOL OF NATURAL AND APPLIED SCIENCES OF MIDDLE EAST TECHNICAL UNIVERSITY

BY

#### İLKER COMART

IN PARTIAL FULFILMENT OF THE REQUIREMENTS

FOR

THE DEGREE OF MASTER OF SCIENCE

IN

ELECTRICAL AND ELECTRONICS ENGINEERING

SEPTEMBER 2010

#### Approval of the thesis:

# ZERO-LEVEL PACKAGING OF MICROWAVE AND MILLIMETERWAVE MEMS COMPONENTS

submitted by **İLKER COMART** in partial fulfillment of the requirements for the degree of **Master of Science in Electrical and Electronics Engineering Department, Middle East Technical University** by,

| Prof. Dr. Canan Özgen                                      |  |

|------------------------------------------------------------|--|

| Dean, Graduate School of Natural and Applied Sciences      |  |

| Prof. Dr. İsmet Erkmen                                     |  |

| Head of Department, Electrical and Electronics Eng.        |  |

|                                                            |  |

| Assoc. Prof. Dr. Şimşek Demir                              |  |

| Supervisor, Electrical and Electronics Eng. Dept., METU    |  |

| Prof. Dr. Tayfun Akın                                      |  |

| Co-supervisor, Electrical and Electronics Eng. Dept., METU |  |

|                                                            |  |

| Examining Committee Members:                               |  |

| Assoc. Prof. Dr. Sencer Koç                                |  |

| Electrical and Electronics Eng. Dept., METU                |  |

| Assoc. Prof. Dr. Şimşek Demir                              |  |

| Electrical and Electronics Eng. Dept., METU                |  |

|                                                            |  |

| Prof. Dr. Tayfun Akın                                      |  |

| Electrical and Electronics Eng. Dept., METU                |  |

| Assoc. Prof. Dr. Özlem Aydın Çivi                          |  |

| Electrical and Electronics Eng. Dept., METU                |  |

|                                                            |  |

| M. Sc. Engineer Şebnem Saygıner                            |  |

| ASELSAN, REHIS                                             |  |

Date:

17.09.2010

| presented in accordance | e with academic rules ese rules and conduct, | document has been obtained and<br>and ethical conduct. I also declare<br>I have fully cited and referenced all<br>work. |

|-------------------------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

|                         |                                              |                                                                                                                         |

|                         | Name, Last Name                              | : İlker Comart                                                                                                          |

|                         | Signature                                    | :                                                                                                                       |

|                         | iii                                          |                                                                                                                         |

#### **ABSTRACT**

### ZERO-LEVEL PACKAGING OF MICROWAVE AND MILLIMETERWAVE MEMS COMPONENTS

#### Comart, İlker

M.Sc., Department of Electrical and Electronics Engineering

Supervisor : Assoc. Prof. Dr. Şimşek Demir

Co-Supervisor: Prof. Dr. Tayfun Akın

September 2010, 122 pages

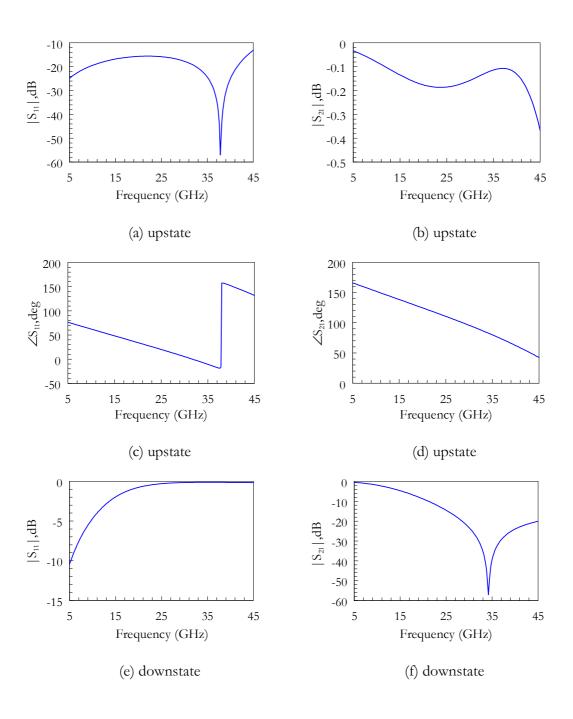

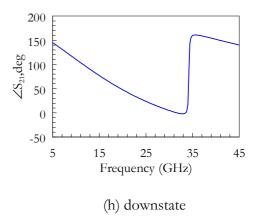

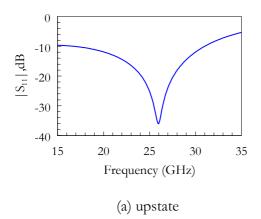

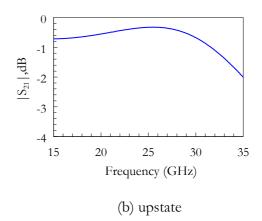

This thesis presents realization of two shunt, capacitive contact RF MEMS switches and two RF MEMS SPDT switches for microwave and millimeter-wave applications, two zero-level package structures for RF MEMS switches and development trials of a BCB based zero level packaging process cycle.

Two shunt, capacitive contact RF MEMS switches for 26 GHz and 12 GHz operating frequencies are designed, fabricated and consistencies between fabricated devices and designs are shown through RF measurements. For the switch design at 26 GHz and at the

iv

operating frequency, return loss in the upstate is measured to be 27.61 dB, insertion loss and isolation in the downstate is measured to be 0.21 dB and 27.16 dB, respectively. For the switch design at 12 GHz and at the operating frequency, return loss in the upstate is measured to be 38.69 dB, insertion loss and isolation in the downstate is measured to be 0.05 dB and 25.84 dB, respectively. Quite accurate circuit models have been obtained for both of the RF MEMS switches. Two RF MEMS SPDT switches, which utilize the shunt, capacitive contact switches as building blocks are designed through circuit simulations. These two designs are fabricated and their RF measurements have been completed. It is shown from circuit model simulations that, the performances of the fabricated devices and desired responses corresponded to each other. For the SPDT switch design at 26 GHz, return loss at the input port is measured to be 12 dB and insertion loss is measured to be 1.24 dB. For the SPDT switch design at 12 GHz, return loss at the input port is measured to be 5.6 dB and insertion loss is measured to be 0.49 dB. The reason behind the unexpectedly bad performances has been investigated and discovered. The bad performances were due to a common mistake in the layouts of both SPDT switches. These mistakes are corrected in the circuit models and expected performances are obtained.

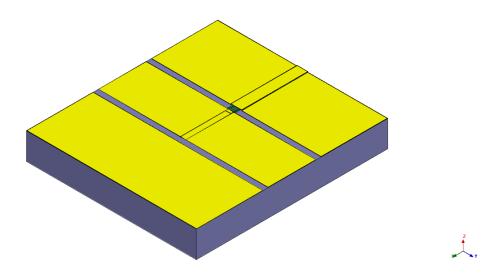

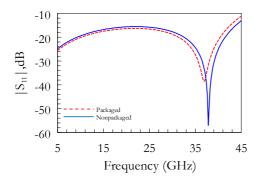

Two different zero-level package structures which use high-resistive Si wafers have been suggested and required design changes have been made on the RF MEMS shunt, capacitive contact switches and SPDT switches in order to minimize the package effects. For this purpose polygonal CPW transitions have been designed and integrated into the designs, followed by the necessary tunings in the switch structures for which EM and circuit simulations are utilized.

For the suggested package structures to be produced, two possible process cycles have been studied. One of the process flows was based on KOH anisotropic Si etching and the other one was based on DRIE (Deep Reactive Ion Etching). Great progress has been achieved in the latter process cycle, however this process cycle still needs some more study and it could not be completed in the time required for this thesis study.

Keywords: RF MEMS, switch, SPDT (single pole double throw), microwave, millimeterwave, package, CPW, KOH, DRIE.

#### ÖZ

## MİKRODALGA VE MİLİMETREDALGA MEMS BİLEŞENLERİNİN SIFIR-SEVİYE PAKETLENMELERİ

#### Comart, İlker

Yüksek Lisans, Elektrik ve Elektronik Mühendisliği Bölümü

Tez Yöneticisi : Doç. Dr. Şimşek Demir

Ortak Tez Yöneticisi : Prof. Dr. Tayfun Akın

Eylül 2010, 122 sayfa

Bu tezde, mikrodalga ve milimetre-dalga uygulamaları için iki adet paralel, sığal değeçli RF MEMS anahtar ve iki adet RF MEMS TGÇÇ (Tek Giriş Çift Çıkış) anahtar yapısının tasarımları, üretim aşamaları ve ölçüm sonuçları, RF MEMS anahtarlar için iki adet sıfırseviye paket yapısının geliştirilmesi ve bu paket yapılarının oluşturulabilmesi için gereken proses adımlarının geliştirilmesi aşamaları anlatılmaktadır.

26 GHz ve 12 GHz çalışma frekanslarında iki adet paralel, sığal değeçli RF MEMS anahtar yapısı tasarlandı, üretildi ve RF ölçümler sonunda üretilen yapılar ile tasarımlar arasındaki

uyumluluk gösterildi. 26 GHz'te tasarlanan anahtar yapısında ve çalışma frekansında, yukarı durumda geriye dönüş kaybı 27.61 dB olarak ölçüldü. 12 GHz'te tasarlanan anahtar yapısında ve çalışma frekansında, yukarı durumda geriye dönüş kaybı 38.69 dB olarak ölçüldü, aşağı durumda araya girme kaybı ve yalıtım sırasıyla 0.05 dB ve 25.84 dB olarak ölçüldü. Her iki RF MEMS anahtar için de oldukça uyumlu devre modelleri elde edildi. Bahsi geçen paralel, sığal değeçli anahtar yapılarının yapı taşı olarak kullanıldığı, iki adet RF MEMS TGÇÇ anahtar yapısı devre benzetimleri ile tasarlandı, üretildi ve RF ölçümleri tamamlandı. Devre modeli benzetimleri gösterdi ki, üretilen yapıların başarımları tasarımlarda elde edilen başarımlarla örtüştü. 26 GHz'teki TGÇÇ anahtar yapısında, geri dönüş kaybı 12 dB ve araya girme kaybı 1.24 dB olarak ölçüldü. 12 GHz'teki TGÇÇ anahtar yapısında, geri dönüş kaybı 5.6 dB ve araya girme kaybı 0.49 dB olarak ölçüldü. Üretilmiş TGÇÇ anahtar yapılarının beklenmeyen derecede kötü başarımlarının sebebi araştırıldı ve bulundu. Bu kötü başarımların SPDT anahtarların serimlerinde ki ortak bir hatadan kaynaklandığı farkedildi. Bu yanlışlıklar devre modeli üzerinde düzeltildi ve beklenen başarımları elde edildi.

Yüksek özdirençli silisyum pulların kullanıldığı iki adet sıfır-seviye paket yapısı önerildi ve bu paket yapısının RF etkilerini en aza indirebilmek için gereken tasarım değişiklikleri RF MEMS paralel, sığal değeçli anahtar yapılarına ve TGÇÇ anahtar yapılarına uygulandı. Bunun için, EDK (Eşdüzlemsel Dalga Kılavuzu) poligonsal geçişler tasarlandı ve anahtar tasarımlarına eklendi ve bu eklemelerin ardından anahtar yapılarındaki gerekli ayarlamalar EM ve devre benzetimleri üzerinden gerçekleştirildi.

Önerilen paket yapısının elde edilebilmesi için, iki adet proses döngüsü üzerinde çalışıldı. Bunlardan bir tanesi KOH anizotropik silisyum aşındırma yöntemine, diğeri ise DRIE ile silisyum aşındırma yöntemine dayanıyordu. İkinci yöntemde büyük gelişim kaydedildi fakat, bu yöntemin kullanılabilir aşamaya gelmesi için hala çalışılmaya ihtiyaç duyulmaktadır ve bu tez çalışması içinde sonuca ulaşılamamıştır.

Anahtar Kelimeler: RF MEMS, anahtar, TGÇÇ (tek giriş çift çıkış), mikrodalga, milimetredalga, paket, KOH, DRIE.

Dedicated to my family...

#### **ACKNOWLEDGEMENTS**

First and foremost, I would like to present my gratitude to my supervisor Assoc. Prof. Şimşek Demir and my co-supervisor Prof. Dr. Tayfun Akın for their guidance and opportunities they have provided me with, in METU RF MEMS group during my graduate life.

I would like to extend my gratitude to Dr. Kağan Topallı and Dr. Mehmet Ünlü for their fellowship, for sharing their extensive knowledge of the subject with me on this study. I have found the opportunity to learn from them and from their experiences. I am very thankful to them because, throughout the times we spent together, they not only coordinated my studies but also motivated me when I needed.

I would like to thank my dear friends Ahmet Hayrettin Yüzer, Ömer Bayraktar, Caner Güçlü, Ozan Doğan Gürbüz, Özgehan Şahin, Ramazan Çetin and Korkut Kağan Tokgöz for their friendship and support during the times we share the same office. More than anybody however, I would like to thank my dear friend and colleague Çağrı Çetintepe for his support, friendship and ability to always coming up with life saving solutions to whichever matter whenever needed.

I would like to moreover thank all the METU MEMS personnel for their help. However, I need to distinguish Orhan Akar, Ebru Topallı and Akın Aydemir, for their supports and efforts during the times I studied in the cleanroom.

I also need to thank to METU MEMS Group members one by one for their support and friendship. Especially, I thank Dr. Said Emre Alper who helped me in my studies when I requested.

I have yet my family to thank, for their everlasting love and encouragement throughout my entire life. It would not be possible for me to succeed without them.

### TABLE OF CONTENTS

| ABSTRACT                                           | iv      |

|----------------------------------------------------|---------|

| ÖZ                                                 | V11     |

| ACKNOWLEDGEMENTS                                   | xi      |

| LIST OF TABLES                                     | XV11    |

| LIST OF FIGURES                                    | X1X     |

| CHAPTERS                                           |         |

| 1 INTRODUCTION                                     | 1       |

| 1.1 Wafer Level Packaging                          | 3       |

| 1.1.1 Thin Film Encapsulation                      | 4       |

| 1.1.2 Chip Capping                                 | 6       |

| 1.1.2.1 Wafer to Wafer Encapsulation               | 6       |

| 1.1.2.2 Cap to Wafer Encapsulation                 | 6       |

| 1.2 Motivation of Dissertation                     | 7       |

| 1.3 Overview of the Thesis                         | 10      |

| 2 REALIZATION OF KU-BAND AND KA-BAND SPST AND SPDT | RF MEMS |

| SWITCHES                                           | 11      |

| 2.1 Introduction                                   | 11      |

| 2.1.1 Overview of RF MEMS SPST Switch              | 12      |

| 2.1.1.1 Contact Types                              | 12      |

|       | 2.1.1.  | 2 Cir   | cuit Configuration Types                             | 13             |

|-------|---------|---------|------------------------------------------------------|----------------|

|       | 2.1.1.  | 3 Act   | tuation Mechanism Types                              | 14             |

| 2.3   | 1.2     | Consi   | dered SPST RF MEMS Switches in This Study            | 15             |

| 2.2   | Ele     | ctroma  | gnetic Design of Devices Used in the SPDT Switch (   | Configurations |

| Inclu | iding ! | SPST S  | witches                                              | 15             |

| 2.2   | 2.1     | Struct  | ture of the SPDT Switches                            | 16             |

| 2.2   | 2.2     | Electr  | romagnetic Design of RF MEMS Switches                | 18             |

|       | 2.2.2.  | 1 Ele   | ctromagnetic Design Specifications                   | 18             |

|       | 2.2.2.  | 2 Lay   | out and Circuit Model of the Switches                | 19             |

|       | 2.2.2.  | 3 De    | sign Methodology                                     | 21             |

|       | 2.2.    | 2.3.1   | CPW Transmission Line Design                         | 21             |

|       | 2.2.    | 2.3.2   | Switch Modeling in the Upstate                       | 24             |

|       | 2.2.    | 2.3.3   | Switch Modeling in the Downstate                     | 26             |

|       | 2.2.    | 2.3.4   | CPW Transition Integrations                          | 28             |

|       | 2.2.    | 2.3.5   | Obtained Switches and Their Responses                | 30             |

| 2.2   | 2.3     | CPW     | T-junction Design                                    | 33             |

| 2.2   | 2.4     | CPW     | 90° Bend Design                                      | 35             |

| 2.2   | 2.5     | Inclus  | sion of DC Bias Lines, DC Pads and CPW Transitions   | 37             |

| 2.2   | 2.6     | Inclus  | sion of DC Blocking MIM Capacitors                   | 38             |

| 2.2   | 2.7     | Integr  | ration of Designed Building Blocks and SPDT Switches | 39             |

| 2.3   | Fab     | ricatio | n of the Devices                                     | 43             |

| 2.3   | 3.1     | Detai   | led Explanations of Process Steps                    | 43             |

| 2.4   | RF      | Measu   | rements and Performances of SPST and SPDT Switches   | 51             |

| ZERO-LEVEL PACKAGE STRUCTURES AND MODIFICATIONS IN                          | THE   |

|-----------------------------------------------------------------------------|-------|

| SPST AND SPDT SWITCH DESIGNS                                                | 63    |

| 3.1 Necessities and Characteristics of Chosen Zero-Level RF MEMS Pack       | aging |

| Method                                                                      | 63    |

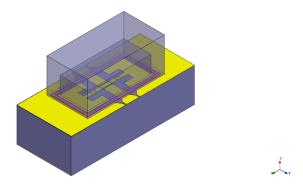

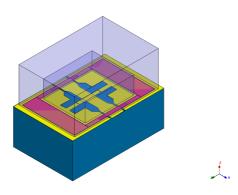

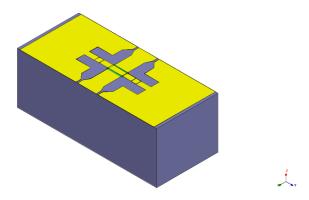

| 3.2 Proposed Package Structures                                             | 64    |

| 3.3 Required Design Modifications for a Shunt, Capacitive Contact RF MEMS S | witch |

| After Introducing Packages                                                  |       |

| 3.3.1 Physical Structure and RF Performances of the RF MEMS Switch at 35    | GHz   |

|                                                                             | 66    |

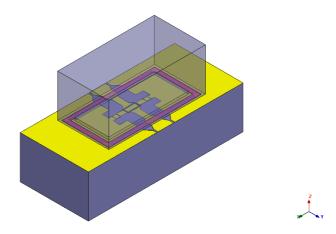

| 3.3.2 Integration of Packages to the EM Models                              | 69    |

| 3.3.3 Design Modifications in the Packaged Switch                           | 71    |

| 3.3.3.1 Polygonal CPW Transition Design                                     | 72    |

| 3.3.3.2 Design Modifications for the Switch at 35 GHz with First Pa         | ckage |

| Structure                                                                   | 74    |

| 3.3.3.3 Design Modifications for the Switch at 35 GHz with Second Page      | ckage |

| Structure                                                                   | 77    |

| 3.4 Design Modifications in the SPST and SPDT Switches                      | 78    |

| DEVELOPMENT OF ZERO-LEVEL PACKAGING PROCESS                                 | 85    |

| 4.1 Utilized Packaging Method in a Process Point of View                    | 85    |

| 4.2 Wafer Bonding Optimization Using BCB as the Adhesive Material           | 87    |

| 4.2.1 BCB Process Optimization                                              | 87    |

| 4.2.2 Wafer Bonding Optimization                                            | 88    |

| 4.2.2.1 Addition of BCB Ring at the Edges of the Cap Wafer                  | 94    |

| 4.3 Packaging Process Development Trials with KOH Anisotropic Si Etching    | 95    |

| 4.4 Packaging Process Development Trials with DRIE                          | 100   |

|   | 4.4.1   | Optimization of First DRIE Step and Wafer Bonding     | 104 |

|---|---------|-------------------------------------------------------|-----|

|   | 4.4.2   | Optimization of Second DRIE Step                      | 106 |

|   | 4.4.2.  | 1 Thermal Contact Problems During Second DRIE Process | 107 |

|   | 4.5 Mo  | dified DRIE Based Packaging Process Cycle             | 109 |

| 5 | CONCI   | LUSION AND FUTURE WORK                                | 113 |

| R | EFERENC | TES                                                   | 117 |

### LIST OF TABLES

#### **TABLES**

| Table 2.1: Design specifications for RF MEMS switch for 26 GHz operating frequency 18   |

|-----------------------------------------------------------------------------------------|

| Table 2.2: Design specifications for RF MEMS switch for 12 GHz operating frequency 18   |

| Table 2.3: Circuit model parameters for the RF MEMS switch designed for 26 GHz          |

| operating frequency                                                                     |

| Table 2.4: Circuit model parameters for the RF MEMS switch designed for 12 GHz          |

| operating frequency                                                                     |

| Table 2.5: Physical dimensions of the RF MEMS switch at 26 GHz                          |

| Table 2.6: Physical dimensions of the RF MEMS switch at 12 GHz                          |

| Table 2.7: Dimensions of CPW T-junction design for 26 GHz operating frequency34         |

| Table 2.8: Dimensions of CPW T-junction design for 12 GHz operating frequency35         |

| Table 2.9: Dimensions of CPW 90° Bend design for 26 GHz operating frequency36           |

| Table 2.10: Dimensions of CPW 90° Bend design for 12 GHz operating frequency37          |

| Table 2.11: Extracted parameters based on the measurements for various CPW line         |

| structures                                                                              |

| Table 2.12: Circuit model parameters extracted from the measurements for the shunt,     |

| capacitive contact RF MEMS switch designed to operate at 26 GHz54                       |

| Table 2.13: Circuit model parameters extracted from the measurements for the shunt,     |

| capacitive contact RF MEMS switch designed to operate at 12 GHz57                       |

| Table 3.1: Physical dimensions of the shunt, capacitive contact RF MEMS switch designed |

| for 35 GHz operating frequency67                                                        |

| Table 3.2: CPW dimensions and characteristic impedances at the points shown in Figure   |

| 3.8, for the switch at 35 GHz with first package structure                              |

| Table 3.3: CPW dimensions and characteristic impedances at the points shown in Figure    |

|------------------------------------------------------------------------------------------|

| 3.8, for the switch at 35 GHz with second package structure                              |

| Table 3.4: Modified dimensions and their values for the packaged RF MEMS switch          |

| operational at 35 GHz (first package structure)                                          |

| Table 3.5: Modified dimensions and their values for the packaged RF MEMS switches        |

| operational at 26 GHz and 12 GHz82                                                       |

| Table 4.1: Process conditions and results of the trials during the wafer bonding process |

| optimization (RT=Room Temperature)                                                       |

| Table 4.2: Process conditions and obtained results for wafer bonding process trials by   |

| using cap wafers patterned with KOH anisotropic Si etching                               |

### LIST OF FIGURES

#### **FIGURES**

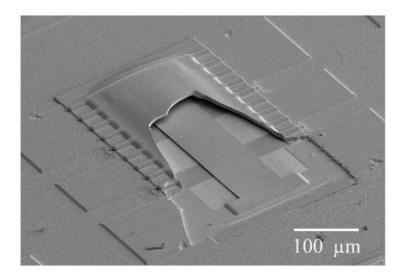

| Figure 1.1: SEM image of a dielectric shell over an RF MEMS switch. Shell partially       |

|-------------------------------------------------------------------------------------------|

| removed to see underlying switch [22]5                                                    |

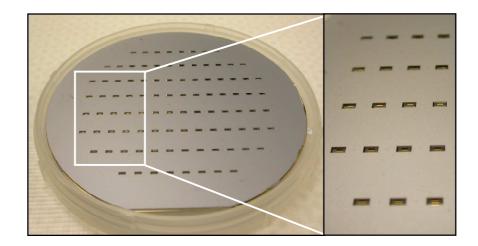

| Figure 1.2: Zero-level packaged CPW lines after the wafer bonding. Pad windows opened     |

| for measurement purposes can be seen better in the right image                            |

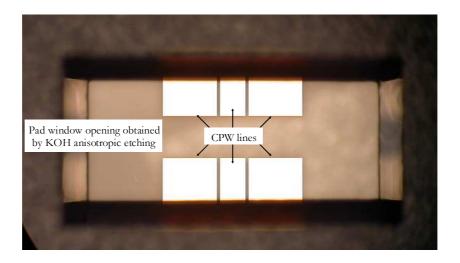

| Figure 1.3: Closer view of one of the pad window openings seen in Figure 1.2              |

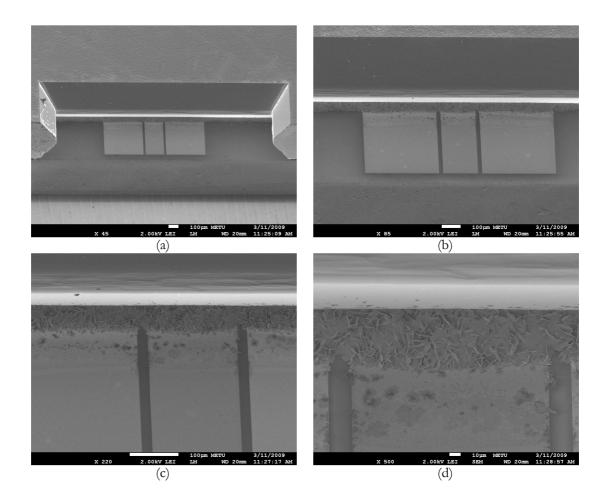

| Figure 1.4: SEM pictures of the same pad window after glass frit packaging with different |

| magnifications9                                                                           |

| Figure 2.1: RF MEMS switch examples in terms of their contact types                       |

| Figure 2.2: Circuit configurations for RF MEMS switch                                     |

| Figure 2.3: Simplified circuit model of SPDT switch structure                             |

| Figure 2.4: One of the designed and fabricated SPDT switch (building blocks are           |

| indicated)                                                                                |

| Figure 2.5: Layout of shunt, capacitive contact SPST MEMS switch                          |

| Figure 2.6: Circuit model of the shunt, capacitive contact SPST RF MEMS switch20          |

| Figure 2.7: CPW transmission line and dimensions                                          |

| Figure 2.8: Lumped element circuit model of a transmission line                           |

| Figure 2.9: Simplified lumped element circuit model of a capacitively loaded transmission |

| line with low loss assumption                                                             |

| Figure 2.10: A micrograph of fabricated RF MEMS switch at 26 GHz operating frequency,     |

| physical dimensions are also defined                                                      |

| Figure 2.11: A micrograph of fabricated RF MEMS switch at 12 GHz operating frequency      |

| 29                                                                                        |

| Figure 2.12: Magnitude S-parameters obtained by electromagnetic and circuit simulations                     |

|-------------------------------------------------------------------------------------------------------------|

| for the RF MEMS switch designed at 26 GHz                                                                   |

| Figure 2.13: Magnitude S-parameters obtained by electromagnetic and circuit simulations                     |

| for the RF MEMS switch designed at 12 GHz                                                                   |

| Figure 2.14: CPW T-junction layout and physical dimensions                                                  |

| Figure 2.15: CPW 90° Bend layout and its dimensions                                                         |

| Figure 2.16: EM model utilized in the design of DC bias lines                                               |

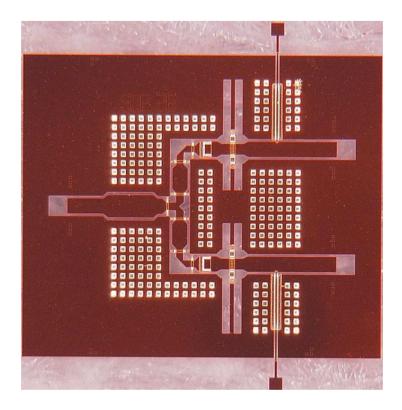

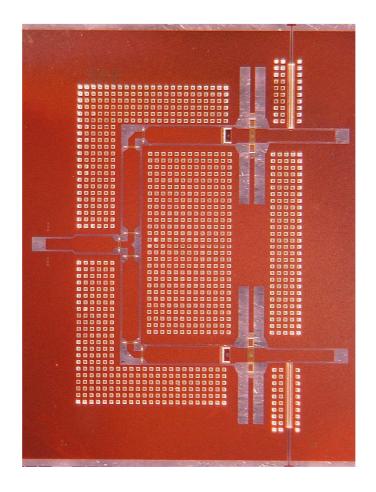

| Figure 2.17: Designed and fabricated SPDT switch with 26 GHz operating frequency 39                         |

| Figure 2.18: Designed and fabricated SPDT switch with 12 GHz operating frequency 40                         |

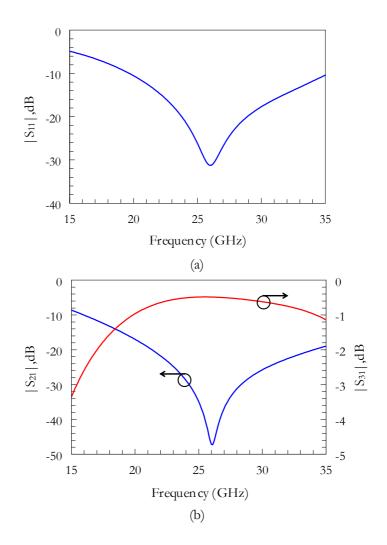

| Figure 2.19: Circuit simulation responses for the SPDT switch operating at 26 GHz41                         |

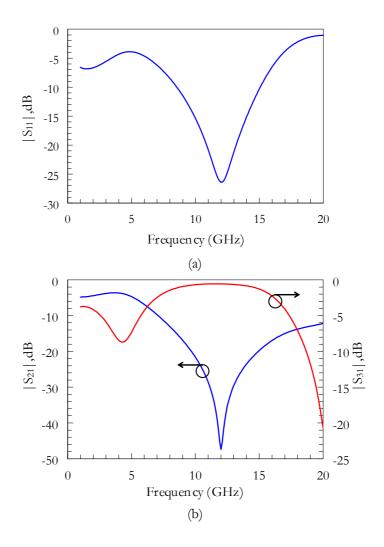

| Figure 2.20: Circuit simulation responses for the SPDT switch operating at 12 GHz 42                        |

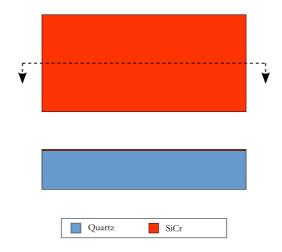

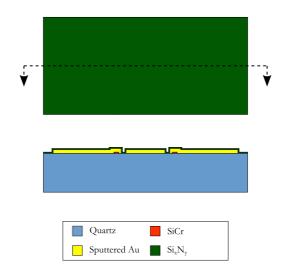

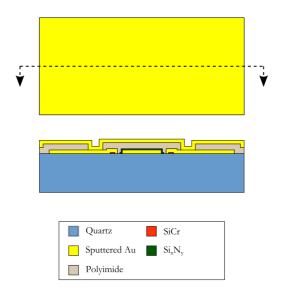

| Figure 2.21: 0.2 μm thick SiCr layer is sputtered on blank quartz substrate                                 |

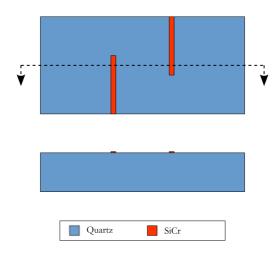

| Figure 2.22: Sputtered SiCr layer is patterned                                                              |

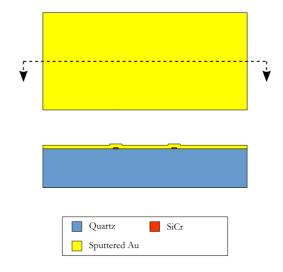

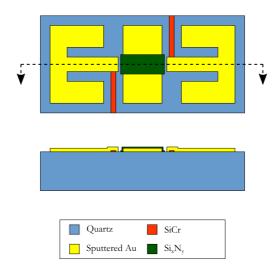

| Figure 2.23: 30 nm Ti and 1 µm Au layer is sputtered on patterned SiCr layer. (Ti is not                    |

| shown on the figure since its thickness is insignificant compared to other layers)45                        |

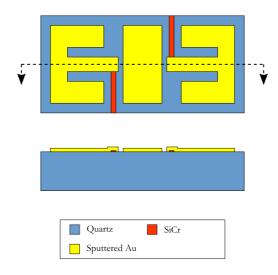

| Figure 2.24: Sputtered Ti and Au layers are patterned                                                       |

| Figure 2.25: $0.3 \mu m \text{ Si}_x N_y$ layer is deposited on patterned first gold metallization layer 46 |

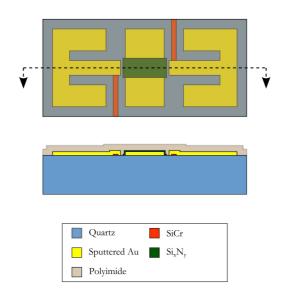

| Figure 2.26: Deposited Si <sub>x</sub> N <sub>y</sub> layer is patterned                                    |

| Figure 2.27: Polyimide sacrificial layer is spin-coated on top of pre-patterned layers 47                   |

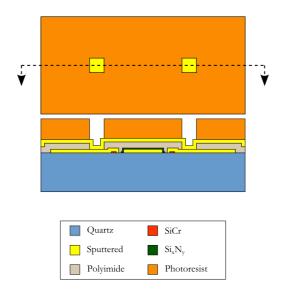

| Figure 2.28: Polyimide sacrificial layer is patterned                                                       |

| Figure 2.29: Structural metal layer sputtered on top of polyimide layer                                     |

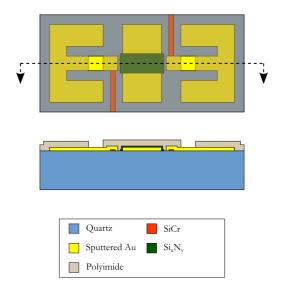

| Figure 2.30: Photoresist spin-coated and patterned for gold electroplating                                  |

| Figure 2.31: Gold electroplating is completed and photoresist is stripped                                   |

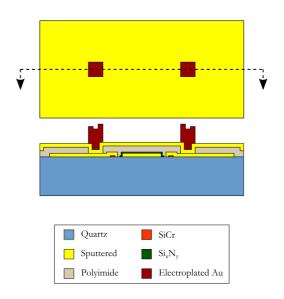

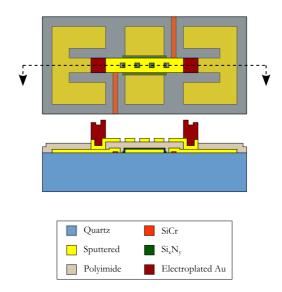

| Figure 2.32: Structural gold layer is patterned and MEMS bridges are formed                                 |

| Figure 2.33: Polyimide sacrificial layer is stripped and MEMS bridges are released 50                       |

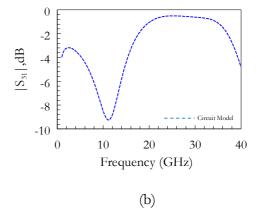

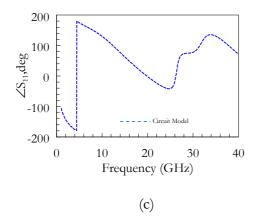

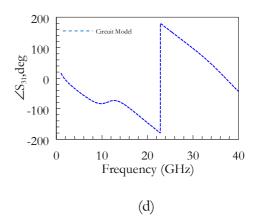

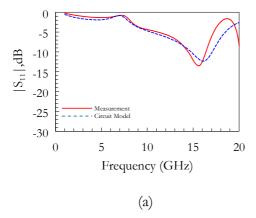

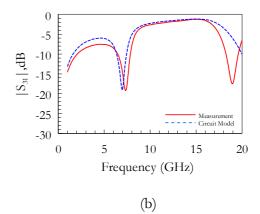

| Figure 2.34: RF measurement results and curve fitted circuit model response of the shunt,                   |

| capacitive contact RF MEMS switch designed at the operating frequency of 26 GHz 53                          |

| Figure 2.35: RF measurement results and curve fitted circuit model response of the shunt,                   |

| capacitive contact RF MEMS switch designed at the operating frequency of 12 GHz 56                          |

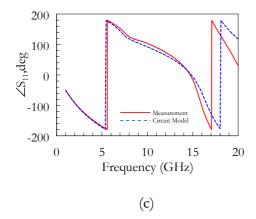

| Figure 2.36: RF measurement results and circuit model response of the RF MEMS SPDT          |

|---------------------------------------------------------------------------------------------|

| switch designed at the operating frequency of 26 GHz                                        |

| Figure 2.37: Altered circuit model response of the RF MEMS SPDT switch designed at the      |

| operating frequency of 26 GHz60                                                             |

| Figure 2.38: RF measurement results and circuit model response of the RF MEMS SPDT          |

| switch designed at the operating frequency of 12 GHz                                        |

| Figure 2.39: Altered circuit model response of the RF MEMS SPDT switch designed at the      |

| operating frequency of 12 GHz                                                               |

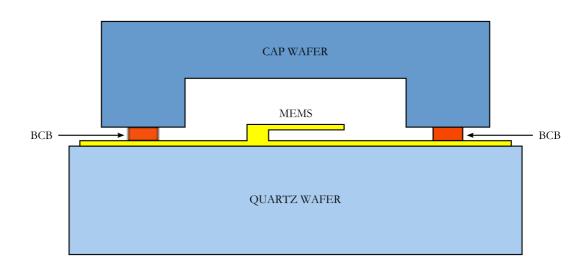

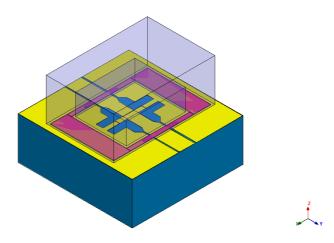

| Figure 3.1: General package structure                                                       |

| Figure 3.2: EM Model drawn for the first package structure without any modifications in     |

| the MEMS switch design (air boxes are not shown)                                            |

| Figure 3.3: EM Model drawn for the second package structure without any modification        |

| in the MEMS switch design (air boxes are not shown)                                         |

| Figure 3.4: EM model of the shunt, capacitive contact RF MEMS switch at 35 GHz (air         |

| boxes are not shown)                                                                        |

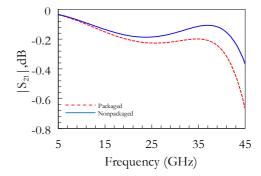

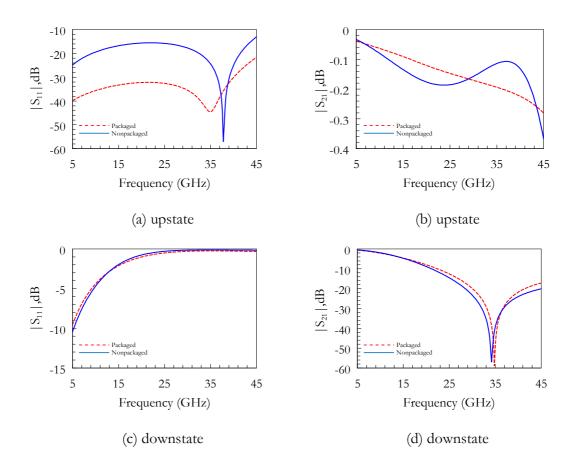

| Figure 3.5: S-parameters of the MEMS switch, designed to operate at 35 GHz, obtained        |

| from EM simulations 69                                                                      |

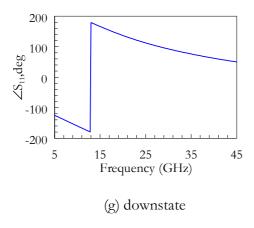

| Figure 3.6: Comparison between the non-packaged and packaged MEMS switch                    |

| performances without any design modifications in the switch (first package structure)70     |

| Figure 3.7: Comparison between the non-packaged and packaged MEMS switch                    |

| performances without any design modifications in the switch (second package structure) .73  |

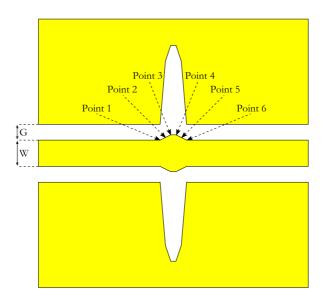

| Figure 3.8: Top view of a polygonal CPW transition                                          |

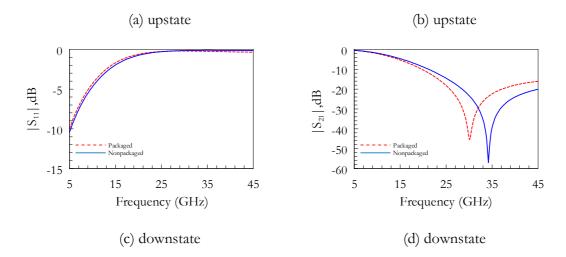

| Figure 3.9: EM Model drawn for the first package structure including design modification    |

| in the MEMS switch (air boxes are not shown)                                                |

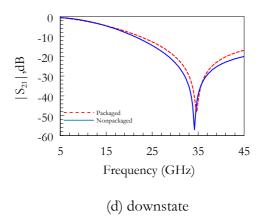

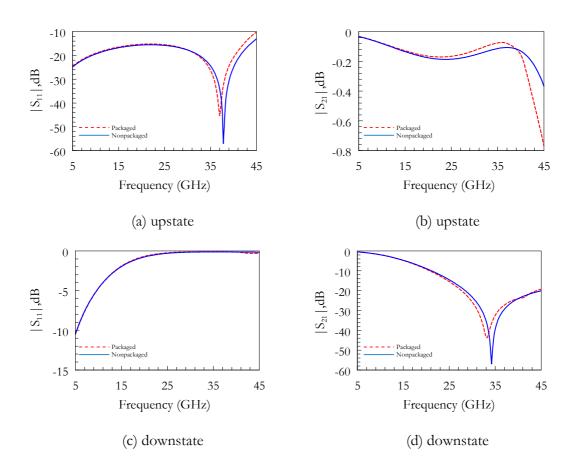

| Figure 3.10: Comparison between the non-packaged and packaged MEMS switch                   |

| performances with applied design modifications in the switch (first package structure)70    |

| Figure 3.11: EM Model drawn for the second package structure including design               |

| modifications in the MEMS switch (air boxes are not shown)                                  |

| Figure 3.12: Comparison between the non-packaged and packaged MEMS switch                   |

| performances with applied design modifications in the switch (second package structure). 78 |

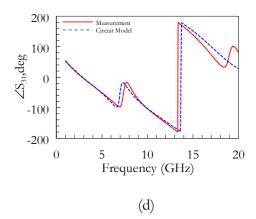

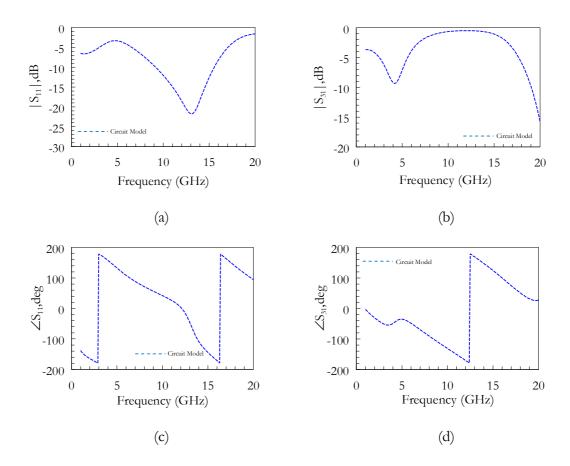

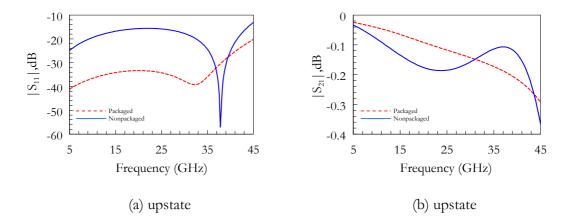

| Figure 3.13: Circuit model simulation results for the packaged shunt, capacitive RF MEMS      |

|-----------------------------------------------------------------------------------------------|

| switch operational at 26 GHz80                                                                |

| Figure 3.14: Circuit model simulation results for the packaged shunt, capacitive RF MEMS      |

| switch operational at 12 GHz82                                                                |

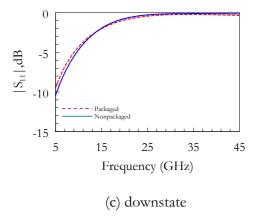

| Figure 3.15: Circuit simulation results for the packaged RF MEMS SPDT switch at 26            |

| GHz83                                                                                         |

| Figure 3.16: Circuit simulation results for the packaged RF MEMS SPDT switch at 12            |

| GHz84                                                                                         |

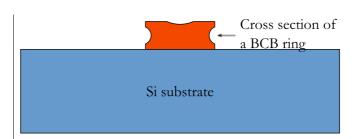

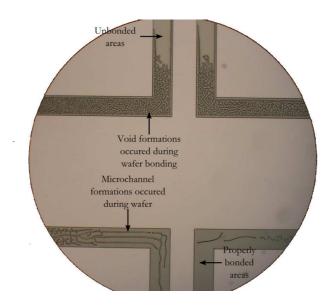

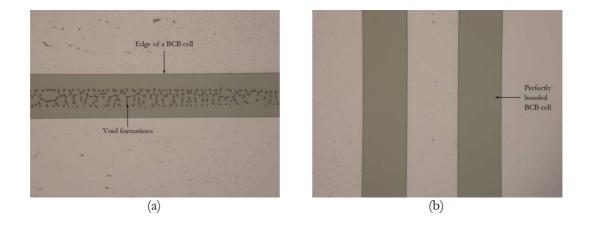

| Figure 4.1: Cross section view of a BCB ring, obtained in Trial #3 in Table 4.191             |

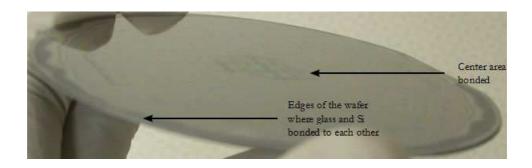

| Figure 4.2: Bonded wafers at the end of trial #6                                              |

| Figure 4.3: A micrograph taken from the center of the wafers, which can be seen in Figure     |

| 4.2, for a closer view                                                                        |

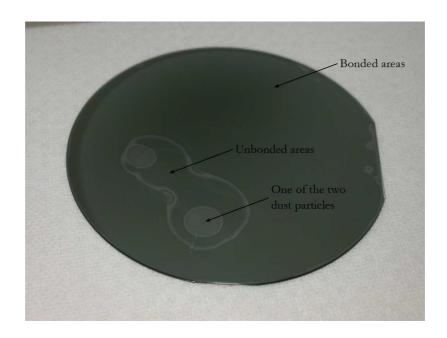

| Figure 4.4: Bonded wafers in trial #7                                                         |

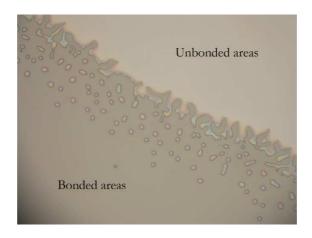

| Figure 4.5: Boundary between the bonded areas and unbounded areas of Figure 4.493             |

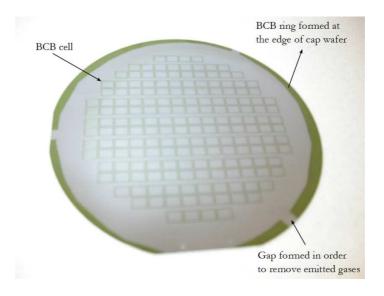

| Figure 4.6: A drawing showing top view of the BCB ring at the edge of the cap wafer 94        |

| Figure 4.7: Properly bonded two BCB cells                                                     |

| Figure 4.8: A cap wafer processed with KOH anisotropic Si etching                             |

| Figure 4.9: BCB layer non-uniformities throughout a wafer utilized in trial #199              |

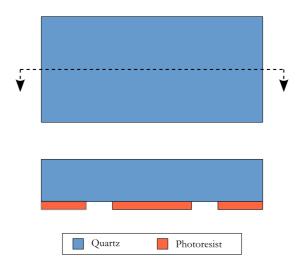

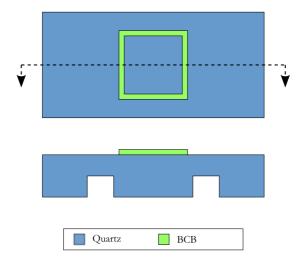

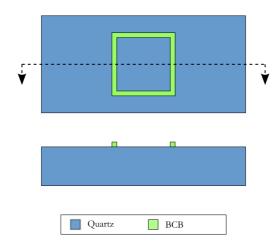

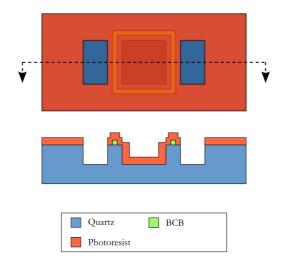

| Figure 4.10: Spin coating and patterning of photoresist on the backside                       |

| Figure 4.11: Half-way through DRIE on the backside of the wafer in order to obtain pad        |

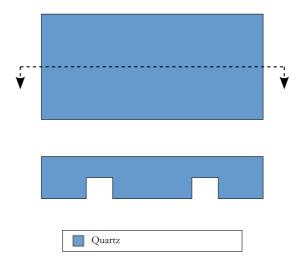

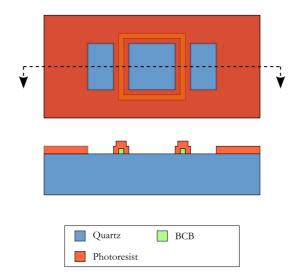

| windows 102                                                                                   |

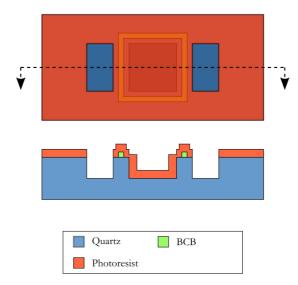

| Figure 4.12: Spin coating and patterning BCB on the front side of the wafer102                |

| Figure 4.13: Spin coating and patterning photoresist on top of BCB layer on the front side    |

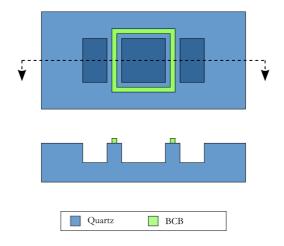

| of the wafer                                                                                  |

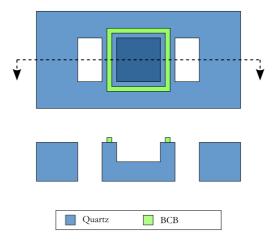

| Figure 4.14: Half-way through DRIE on the front side of the wafer in order to obtain both     |

| pad windows and cavities                                                                      |

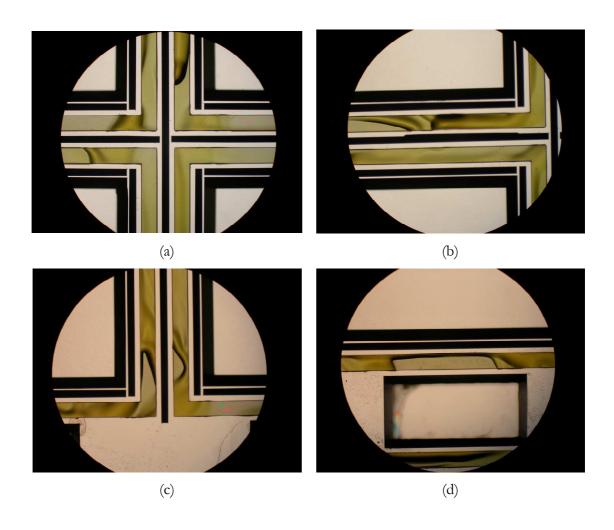

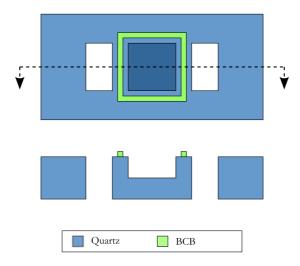

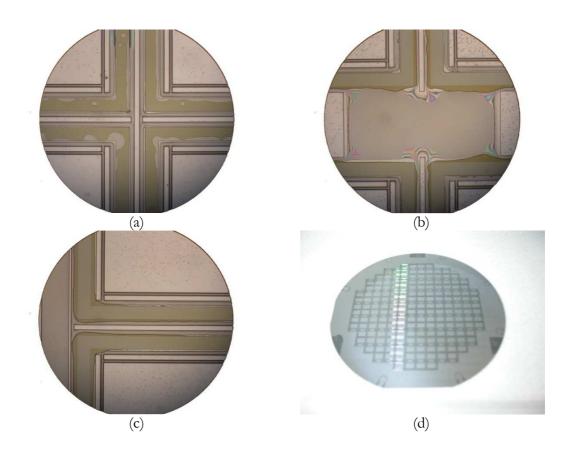

| Figure 4.15: Bonded areas and bonded wafers themselves of a successful wafer bonding          |

| trial where cavities have been formed on the cap wafer                                        |

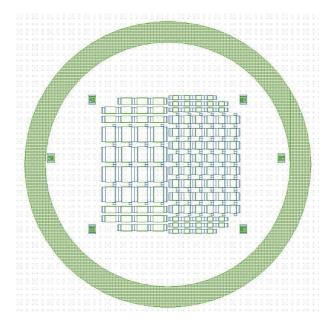

| Figure 4.16: Layout of the mask set utilized in the packaging trials showing the distribution |

| of the devices to be packaged on a wafer                                                      |

| <b>Figure 4.17:</b> Spin coating and patterning and hardbaking of BCB on the front side 109 |

|---------------------------------------------------------------------------------------------|

| Figure 4.18: Spin coating and patterning photoresist on top of patterned BCB fro first      |

| DRIE                                                                                        |

| Figure 4.19: Half-way DRIE from the front side including both cavities and pad windows,     |

| stripping photoresist                                                                       |

| Figure 4.20: Spin coating and patterning of photoresist for second DRIE111                  |

| Figure 4.21: Second half-way DRIE in order to have both cavities and pad windows and        |

| stripping photoresist                                                                       |

#### **CHAPTER 1**

#### INTRODUCTION

Radio Frequency (RF) Micro-Electro-Mechanical Systems (MEMS) mean the devices fabricated by microfabrication processes and they are operational on the RF domain. These sub-millimeter sized movable parts provides the functionality. As they are functional in the RF domain and fabricated by micromachining techniques, RF MEMS devices are constructed on planar transmission lines such as coplanar waveguide (CPW) lines or microstrip lines. Not only by this structural property but because of their relatively small sizes, low electrical loss is a basic specification of RF MEMS devices. Owing to their high electrical performance, rather simpler design, small size and relatively low cost, RF MEMS devices holds the power the be a key solution especially in telecommunications and space applications [1].

One of the most important properties RF MEMS holds is the reconfigurability which is provided automatically. Basic RF MEMS devices are switches [2-14] and tunable capacitors [15-19] that provides the reconfigurability. RF MEMS switch is the basic unit of the technology, by which more complicated devices are constructed. "RF MEMS switch is favored due to its low insertion loss and high isolation, which substantially exceeds the performances of its Field Effect Transistor (FET) and PIN diode counterparts" [1].

Operations of most of the RF MEMS devices are based on the movement of submillimeter sized parts. These devices are produced by microfabrication processes and require a clean environment during fabrication and during operation as well. Because contamination may affect the mechanical movement of the devices which directly influence the electrical performance. Furthermore, RF MEMS devices may be affected from humidity, electromagnetic fields or magnetic fields, which is a drawback in terms of reliability. Especially the performances of the shunt, capacitive contact RF MEMS switches, which this study is mostly based on are exponentially decrease in terms of life time due to humidity. On the other hand, it will not be meaningful to expect cleanroom conditions wherever RF MEMS devices utilized. In order to be able to use RF MEMS devices in outside world, we need protection from the harsh conditions which may affect the functionality.

Packaging of RF MEMS devices is a requirement not only for protection but also for controllability of the environment which the devices work in. Packaging is one of the most essential requirement for gyroscopes, infrared detectors and RF components which are fabricated by MEMS technology [20-23]. Packaging of the micro devices can be classified into three as zero-level (wafer level) packaging, first-level packaging and second-level packaging.

- Wafer level packaging creates an on-wafer device scaled sealed cavity for the fragile

MEMS device, carried out during wafer processing, prior to die singulation [24],

- First-level packaging is, embedding the device into a package usable in the outside world where the connections should be carried outside the package [25],

- Second-level packaging is to mount the first-level packaged system to a board.

In the context of this thesis, zero-level packaging is studied and this subject is considered in detail under the following title.

#### 1.1 Wafer Level Packaging

Packaging and testing the packaged devices compose a great portion of the total cost needed to obtain the MEMS components. In order to decrease the total cost, packaging should be done prior to die singulation on wafer level. By wafer-level packaging approach, MEMS devices can indeed be protected from the chemical and mechanical harms which can occur during the wafer dicing operation. Thus, throughput of the MEMS fabrication may increase. Wafer level package can be defined as the first protective interface which is encapsulation of the movable parts on wafer level in a sealed cavity [23].

Being able to utilize conventional package structures for the zero-level packaged MEMS components is another advantage of wafer-level packaging. Because, by this method the cost required to produce a utilizable MEMS device can be decreased. Wafer level packaging actually is a part of the complete packaging work, which is shifted back in the process chain prior to wafer dicing [25].

Wafer level packages make the handling of the fragile MEMS devices easy. So rather than monolithically fabricating every part of a complete system which is usually not possible, integration of different technologies becomes feasible. Wafer-level packaging processes increase the effectiveness of the integration of passive components into complete systems [26].

In wafer-level packaging processes, either a cap wafer is bonded to the process wafer by using an adhesive material if necessary (wafer bonding) [21],or a shell is formed by growing new layers on top of the device (thin film encapsulation) [22].

In addition to these benefits of wafer level packaging, the conditions inside the package can be controlled. The process can be made hermetic or semi-hermetic, also instead of vacuum inside, an inert gas can be used such as argon (Ar) to prevent any chemical reaction that may take place.

The electrical effects of wafer level packaging to the operation of the structures is not crucial for low frequency applications, however in RF MEMS structures these effects become significant. There are two main electrical effects that should be considered.

- The electrical performance will be altered after 0-level packaging due to the closeness of the wafer level package to the surface of RF MEMS structure. Etched cavities are provided on cap-wafers to minimize these effects.

- Characteristic impedances of the signal paths will be altered due to the loading of the zero-level package and reflections will occur because of the induced mismatches.

Packaging issues should be taken into consideration during the design because of these effects which could alter the performance of the structure significantly. That is why the models used in EM simulations prior to the process should include the zero level packages with the device intended to be packaged.

Zero-level packaging can be categorized into two in terms of the packaging method utilized; chip capping and thin film encapsulation. Furthermore, chip capping can be divided into two as wafer to wafer level packaging and chip to wafer level packaging.

#### 1.1.1 Thin Film Encapsulation

By using LPCVD (Low Pressure Chemical Vapor Deposition) or PECVD (Plasma Enhanced Chemical Vapor Deposition) techniques, poly-SiGe, silicon nitride (Si<sub>x</sub>N<sub>y</sub>), silicon oxide (SiO<sub>2</sub>) materials can be deposited and these layers can be used to encapsulate the MEMS devices [27]. In thin film encapsulation packaging method, a second sacrificial layer

is coated or formed on top of the MEMS device, before releasing the structures, in other words before removing the first sacrificial layer. Forming second sacrificial layer is followed by deposition of the thin film (poly-SiGe, Si<sub>x</sub>N<sub>y</sub>, SiO<sub>2</sub> etc) on top of it as a shell. Sacrificial layers are removed either by wet etching or plasma etching, which could both penetrate into the sacrificial layers from the holes opened on the thin film. After removing the sacrificial layers, the holes on the shell can be closed by applying another PECVD or LPCVD process. Many MEMS components are reported to be packaged by thin film encapsulation [22, 28-31].

**Figure 1.1:** SEM image of a dielectric shell over an RF MEMS switch. Shell partially removed to see underlying switch [22].

In thin film packaging hermeticity may be ensured however, it is not possible to control the environment inside the package. Inside the package, it will be the exact same conditions and gases, which have been utilized in the deposition of the thin films in the PECVD or LPCVD chamber. In addition to this, the temperatures during the deposition of thin films may exceed 400 °C, which will not be suitable if gold structural layer is utilized.

#### 1.1.2 Chip Capping

Chip capping utilizes a cap wafer for enclosing the MEMS device and requires wafer bonding processes. The cap wafer is processed and have cavities on it for housing the MEMS devices. The process wafer and cap wafer are bonded to each other by the use of an adhesive material. Adhesive material is given the shape of a ring around the MEMS devices and seals the MEMS device under the cavity. The hermeticity of the package indeed is determined by the adhesive material utilized. There are many reported package structures which uses gold (eutectic bonding) [32, 33], glass frit [20], BCB [34-38] etc. There are two types of chip capping methods which are wafer-to-wafer encapsulation and cap-to-wafer encapsulation. There is no structural difference between the packages these two methods provide, the only difference is in terms of process chain.

#### 1.1.2.1 Wafer to Wafer Encapsulation

In the wafer-to-wafer encapsulation all of the structures on the process wafers could be capped simultaneously and by this way the spent time decreases substantially.

The bonding material ensures a uniform pressure distribution between the cap wafer and the process wafer. This uniform pressure distribution provides a fixed and uniform cap to device spacing throughout the whole wafer. However, in this case dicing becomes problematic since you have to dice two wafers at the same time.

#### 1.1.2.2 Cap to Wafer Encapsulation

This type of encapsulation can be done with flip chip bonding. (Flip chip microelectronic assembly is the direct electrical connection of face-down (hence, "flipped") electronic components onto substrates, circuit boards, or carriers, by means of conductive bumps on the chip bond pads. In contrast, wire bonding, the older technology which flip chip is

replacing, uses face-up chips with a wire connection to each pad) Cap-to-wafer encapsulation has the disadvantage of being more time consuming. It is because in this type of encapsulation the structures to be packaged will be processed separately. However, in cap-to-wafer encapsulation, dicing is much simpler than in wafer-to-wafer encapsulation.

#### 1.2 Motivation of Dissertation

RF MEMS packaging studies have been started by Dr. Kağan Topallı in METU RF MEMS group. A wafer to wafer encapsulation process has been developed by the use of glass frit as the bonding material [39]. The properties of glass frit which lead METU RF MEMS group to work with this material can be itemized as;

- Proven quality of the glass frit bonding in gyroscope and accelerometer packages,

- Hermetic packaging ability,

- Easy processing and patterning of glass frit by screen printing technology,

In the context of the study CPW transmission lines have been packaged using glass frit bonding. Figure 1.2 presents bonded process wafer and cap wafer, utilized in the glass frit packaging. In addition to this, presents a closer view inside a pad window where CPW lines can be seen. In the processing of the Si cap wafer, KOH anisotropic etching has been utilized and both cavities and pad windows have been formed.

**Figure 1.2:** Zero-level packaged CPW lines after the wafer bonding. Pad windows opened for measurement purposes can be seen better in the right image

Figure 1.3: Closer view of one of the pad window openings seen in Figure 1.2

SEM pictures showing the glass frit layer after the wafer bonding can be seen in Figure 1.4.

**Figure 1.4:** SEM pictures of the same pad window after glass frit packaging with different magnifications

CPW transmission lines have been packaged with glass frit bonding successfully, however packaging a MEMS switch is different. In a MEMS switch there are movable parts, which are suspended. Since glass frit bonding needs a bonding temperature of ~425 °C, packaging suspended structures made of gold is not appropriate for this kind of bonding material.

This reasoning lead METU RF MEMS group to change the bonding material and BCB has been adopted, because;

- BCB needs a relatively low bonding temperature (250 °C),

- BCB is a semi-hermetic material which the RF MEMS group's needs overlap,

- BCB is photodefinable material which can easily be processed and patterned by UV photolithography techniques.

#### 1.3 Overview of the Thesis

This thesis consists of five chapters. This chapter has provided an overview on RF MEMS and RF MEMS wafer-level packaging. Chapter 2 starts with an overview of the RF MEMS switch which is the key component of the technology. Then it gives detailed information on the realization of two, shunt, capacitive contact RF MEMS switches and two RF MEMS SPDT switches where shunt, capacitive contact switches are utilized as building blocks. Realization of the SPDT switches is divided into subsections such as design steps, fabrication steps and measurement results. Chapter 3 provides explanations on the structures of two proposed zero-level packages. Introduction of these packages into a 35 GHz shunt, capacitive contact RF MEMS switch is provided in this section as well. In addition to this, package integrations of RF MEMS SPST and SPDT switches, whose design steps, fabrication steps and measurement results are provided in Chapter 2, are expressed in Chapter 3. Third chapter ends with EM and circuit simulation results of the packaged structures. Process development steps of the proposed BCB based zero-level package structures are provided in Chapter 4. Development of the process cycle is divided into three groups; BCB process optimizations, KOH anisotropic Si etching based packaging approach and DRIE based packaging approach. Chapter 5 presents the conclusions from this study and future work that can be conducted to further the capabilities of presented SPDT switches and to realize the packaging process.

#### **CHAPTER 2**

# REALIZATION OF KU-BAND AND KA-BAND SPST AND SPDT RF MEMS SWITCHES

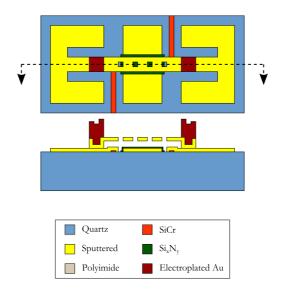

This chapter investigates development of two SPDT (single pole double throw) RF MEMS switches for microwave applications using an in-house RF MEMS fabrication process. The SPDT switch structure consists of two, shunt, capacitive contact SPST (single pole single throw) RF MEMS switches, a CPW (Coplanar Waveguide) T-junction structure, two CPW 90° Bend structures, two MIM (Metal-Insulator-Metal) DC-Blocking capacitors and CPW lines with various types and lengths. This chapter begins with an introduction section which gives detailed information on operating principles and types of RF MEMS SPST switches and SPDT switches. Section 2.2 introduces the electromagnetic designs of the SPDT switches at Ku-Band and Ka-Band by investigating each component individually. Then, Section 2.3 provides information on the in-house RF MEMS fabrication process which has been used during the fabrication of the SPDT and SPST switches. Utilized RF measurement setup, encountered problems during the measurements and obtained results will be presented in Section 2.4, by providing comparisons with the electromagnetic and circuit simulation results.

#### 2.1 Introduction

Among the RF MEMS components, RF MEMS switch is the key component for the enabling technology and it serves as a building block for more complicated device configurations. Since this chapter focuses on RF MEMS SPST and SPDT switches and for

comprehensibility of RF MEMS technology, an overview of the types and features of its key component holds great significance.

#### 2.1.1 Overview of RF MEMS SPST Switch

RF MEMS switches can be classified into different groups according to their contact types, circuit configurations and actuation mechanisms.

#### 2.1.1.1 Contact Types

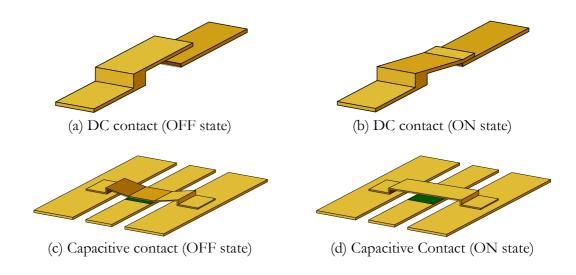

RF MEMS switches can be categorized into two groups in terms of the contact types between the signal line and the MEMS bridge. Figure 2.1 indicates some MEMS switches, which are the most common switch types, classified according to their contact types.

Figure 2.1: RF MEMS switch examples in terms of their contact types.

Considering the DC contact switches in Figure 2.1 (a) and Figure 2.1 (b), when the switch is in OFF state the RF signal cannot be transferred through signal line owing to lack of

electrical connection. In the ON state, the electrical connection is established via MEMS bridge and in this state RF signal is allowed to pass. From a circuit point of view in the ON state, the contact can be modeled by the contact resistance, which is why DC contact switches can operate near DC frequencies. Capacitive contact switches in Figure 2.1 (c) and Figure 2.1 (d) on the other hand, have a different operation type. When the switch is in ON state the MEMS bridge is in upstate position and due to low coupling capacitance between the bridge and the signal line, RF signal can be transferred with insignificant disturbance. The MEMS bridge is in downstate position in the OFF state and due to increased coupling capacitance between the bridge (ground) and the signal line, RF signal is not allowed to pass. Capacitive contact type switches cannot operate properly near DC frequencies since the coupling mechanism will fail.

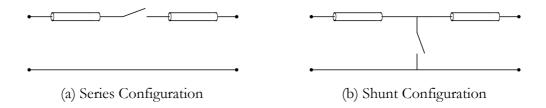

#### 2.1.1.2 Circuit Configuration Types

RF MEMS switches are constructed on top of transmission lines as they can be used to prevent or allow the electrical signals to pass through. Since they are fabricated using planar micro-fabrication processes, transmission lines have been chosen to be either CPW lines or microstrip lines. From a circuit point of view every transmission line needs a signal line and a reference ground line which leads to two types of circuit configurations automatically. In order to allow or prevent the signal flow, RF MEMS switches may be constructed on the signal line which happens to be a series connection or may be constructed between the signal and ground lines which happens to be the shunt connection. Figure 2.2 indicates the two circuit configuration types.

Figure 2.2: Circuit configurations for RF MEMS switch.

In series configuration when the switch is ON state (closed position) RF signal can be transferred through the transmission line. On the other hand, when the switch is in OFF state (open position) it prevents the RF signal to pass through. In shunt configuration, situation is the exact opposite; when the switch is in ON state, RF signal cannot pass through the transmission line since its grounded and when the switch is in OFF state, RF signal can be transferred through the line.

# 2.1.1.3 Actuation Mechanism Types

RF MEMS switches owe their functionality in RF domain to their sub-millimeter sized movable parts. ON and OFF states of the switch are achieved by moving these movable parts. These movements in RF MEMS switches are achieved by electrostatic, piezoelectric, electrothermal and magnetic actuation mechanisms. Among these mechanisms, electrostatic actuation is the most favored, due to the fast response times, rather smaller size and almost zero power consumption of the switches. Since MEMS switches considered in this study have electrostatic actuation mechanisms, it is better to investigate its properties a little deeper.

Shunt, capacitive contact switch structure, whose OFF and ON states have been indicated in Figure 2.1 (c) and Figure 2.1 (d) respectively, is an example for an electrostatically actuated switch. MEMS bridge can be collapsed by applying a DC potential difference between the signal trace and ground planes of the CPW line which is the MEMS bridge

itself. Generated electric field between the bridge and the signal trace of the CPW line will cause a force to be exerted on the bridge. When this force is strong enough to overcome the mechanical stiffness of the MEMS bridge, the bridge will collapse. This phenomenon is known as the pull-in phenomenon and the minimum potential difference applied between the signal trace and ground planes of the CPW line to collapse the bridge is defined as pull-in voltage ( $V_{\rm Pl}$ ).

To sup up, when a potential difference greater than or equal to  $V_{PI}$  is applied between the signal trace and the MEMS bridge, the bridge will collapse and the switch will be in OFF state. When the potential difference is smaller than  $V_{PI}$ , MEMS switch will be in ON state.

# 2.1.2 Considered SPST RF MEMS Switches in This Study

In the light of expressed classifications for an RF MEMS switch in previous sections, considered switch structure can be put into words as a shunt, capacitive contact switch with an electrostatic actuation mechanism. In fact, Figure 2.1 (c) and Figure 2.1 (d) shows a rather simpler model of the considered switch.

Two switches have been considered in this study sharing the same switch structure. One of the switches has been designed for 12 GHz operating frequency and the other one is designed for 26 GHz operating frequency.

# 2.2 Electromagnetic Design of Devices Used in the SPDT Switch Configurations Including SPST Switches

The ultimate aim of this study was to design RF MEMS SPDT switches at 26 GHz and 12 GHz operating frequencies. Owing to the previously obtained experiences on shunt, capacitive contact switches in METU RF MEMS group, this type of switches have been utilized as the main building blocks for the SPDT designs. In addition to the SPST

switches, a CPW T-junction, two CPW 90° Bend designs and two MIM capacitors for each design were required. Electromagnetic design steps will be presented separately for each building block, after explaining the SPDT switch structures.

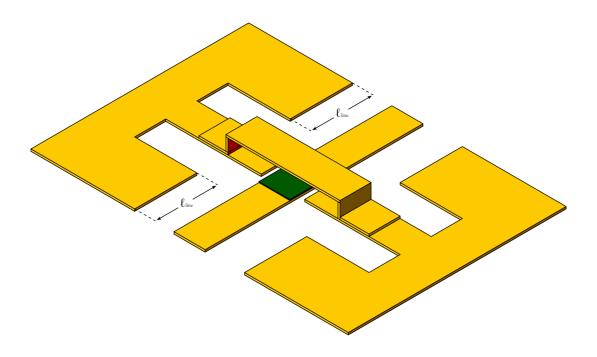

#### 2.2.1 Structure of the SPDT Switches

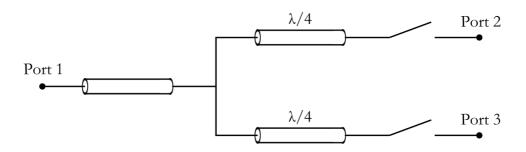

A simplified circuit model is presented in this part in Figure 2.3, in order to demonstrate the operating principle of the SPDT switch structure utilized in this study.

Figure 2.3: Simplified circuit model of SPDT switch structure

As depicted, the circuit model in Figure 2.3 is rather a simplified version. It did not include the CPW 90° Bend structures, CPW T-junction or MIM DC blocking capacitors. However, this model may give the basic idea behind the design. The transmission lines on branches of Port 2 and Prot 3 have an electrical length of  $\lambda/4$  on the operating frequency and the switches seen on the model are shunt, capacitive contact MEMS switches. It has been mentioned in the previous sections of this chapter that, when a shunt, capacitive contact switch will be in its OFF state, which was shown Figure 2.1 (c), the MEMS bridge will be in downstate position and there will be an RF virtual short circuit on the signal trace of the CPW line. This short circuit will be transferred as a virtual open circuit to the T-connection and the power will not be allowed to go into that branch. By this method it is possible to

choose the path of the RF signal and transfer it out from one of the output ports selectively. A more detailed explanation will be given about the operation principles of the SPDT switch structure after examining each building block separately.

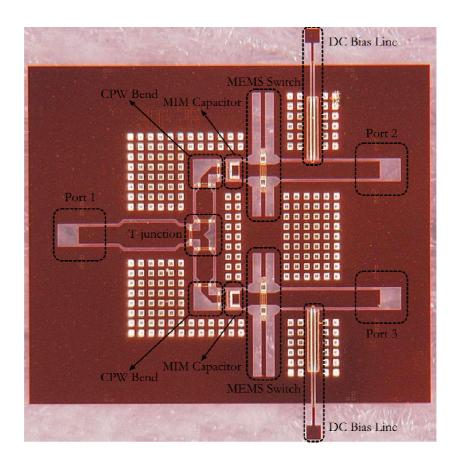

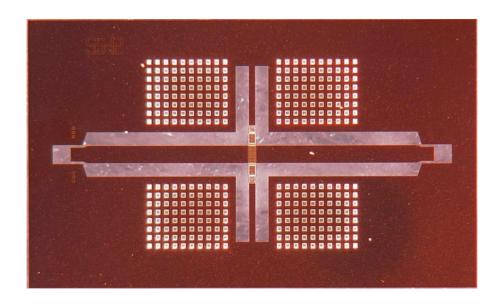

In order to have a better understanding of SPDT structure, Figure 2.4 demonstrates one of the designed and fabricated SPDT switches. Building blocks are also indicated separately on the micrograph.

**Figure 2.4:** One of the designed and fabricated SPDT switch (building blocks are indicated)

#### 2.2.2 Electromagnetic Design of RF MEMS Switches

In this section, electromagnetic designs of the two shunt, capacitive contact switches are investigated for operating frequencies 26 GHz and 12 GHz. The design parameter values will be given separately for each design, under the same titles. To begin with, electromagnetic design specifications of the switches will be given. After that, layouts and circuit models of the switches will be presented. Then, fabrication steps will be covered and finally measurement results will be given including the verification of for the RF MEMS switches.

## 2.2.2.1 Electromagnetic Design Specifications

Electromagnetic design step has been started based on some design specifications and it is aimed to obtain a SPDT switch coherent with these attributes. ON states and OFF states of the switches have different specifications which can be found in Table 2.1 and Table 2.2 for 26 GHz and 12 GHz designs, respectively.

Table 2.1: Design specifications for RF MEMS switch for 26 GHz operating frequency

| STATE | SPECIFICATIONS                                                                                                               |

|-------|------------------------------------------------------------------------------------------------------------------------------|

| ON    | Return Loss better than 15 dB in a 5 GHz band around 26 GHz, Insertion Loss better than 0.5 dB in a 5 GHz band around 26 GHz |

| OFF   | Isolation better than 20 dB at 26 GHz                                                                                        |

**Table 2.2:** Design specifications for RF MEMS switch for 12 GHz operating frequency

| STATE | SPECIFICATIONS                                                                                                               |

|-------|------------------------------------------------------------------------------------------------------------------------------|

| ON    | Return Loss better than 15 dB in a 3 GHz band around 12 GHz, Insertion Loss better than 0.5 dB in a 3 GHz band around 12 GHz |

| OFF   | Isolation better than 20 dB at 12 GHz                                                                                        |

#### 2.2.2.2 Layout and Circuit Model of the Switches

Layout drawing of the shunt, capacitive contact switch, whose specifications are given in Table 2.1 and Table 2.2, can be seen in Figure 2.5. Despite being the layout of a shunt, capacitive contact switch such as Figure 2.1 (d), the drawing in Figure 2.5 has some differences and is more complicated.

Figure 2.5: Layout of shunt, capacitive contact SPST MEMS switch

The first thing to be noticed is the recesses near the MEMS bridge legs, which extends into the ground planes of the CPW line. These recesses are used for *inductive tuning* and their purpose will be explained in detail in the following sections. In addition to the recesses, anchors of the MEMS bridge have extensions towards the signal trace of the CPW line. This so called "anchor extensions" will be given some attention in the following sections as well.

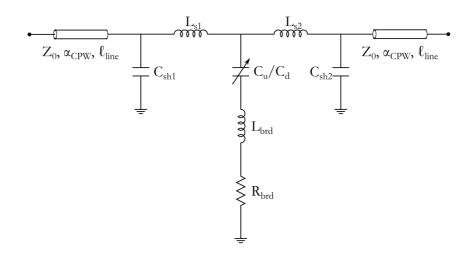

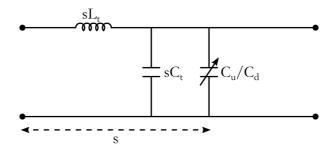

Constituting a circuit model for the MEMS switches is significant because this approach makes it possible to use circuit simulators instead of electromagnetic simulators, which require more effort and time for the simulations. Especially the SPDT structures utilized in this study are too large in this sense, for which it is not possible for the EM simulators to give accurate results. Rather than trying to solve the whole problem in an EM simulator, circuit models of the switches were constructed and rest of the study is attended by the use of these circuit models. Figure 2.6 indicates the utilized circuit model.

Figure 2.6: Circuit model of the shunt, capacitive contact SPST RF MEMS switch

Utilized circuit model is an advanced version of the common CLR circuit model [7] of a shunt, capacitive contact RF MEMS switch. RF MEMS switch model consists of  $C_{sh1}$ ,  $C_{sh2}$ ,  $L_{s1}$  and  $L_{s2}$  which accounts for the step discontinuities on the recess interfaces [40] and two short transmission line segments, whose lengths ( $\ell_{line}$ ) are shown in Figure 2.5, on the series branches.  $C_{sh1}$ ,  $C_{sh2}$  and  $L_{s1}$ ,  $L_{s2}$  are chosen to have different values due to a possible nonsymmetry between the recesses on different ground planes, which will be the case for the designed switch at 26 GHz due to physical layout problems in the SPDT switch design. Shunt branch consists of a two state variable capacitor, an inductor and a resistor.  $C_u$  and  $C_d$

are abbreviation of upstate and downstate capacitances for the switch.  $L_{brd}$  and  $R_{brd}$  are abbreviations of bridge inductance and bridge resistance, respectively. Shunt branch models the MEMS bridge and the electrical components denote the values originated from the bridge itself.

# 2.2.2.3 Design Methodology

Design methodology can be investigated under three subtitles such as CPW transmission line design, return loss optimization in upstate and isolation optimization by inductive tuning in downstate.

# 2.2.2.3.1 CPW Transmission Line Design

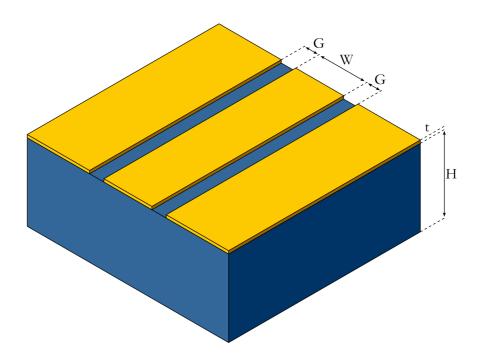

Figure 2.7: CPW transmission line and dimensions

Since shunt, capacitive contact RF MEMS switches are constructed on CPW transmission lines, modeling the line by finding its characteristic impedance ( $Z_0$ ), electrical length at operating frequency ( $\ell_{line}$ ) and attenuation constant is prior and a significant step. Figure 2.7 indicates the physical dimensions of a CPW transmission line on a substrate. Required formulation in order to calculate the characteristic impedance of a conductor-backed CPW transmission line is provided below [41]:

$$Z_{0} = \frac{60\pi}{\sqrt{\epsilon_{eff}}} \frac{1}{\frac{K(k_{1})}{K(k_{1}')} + \frac{K(k_{2})}{K(k_{2}')}}$$

(2.1)

where,

$$k_1 = \frac{\tanh(\pi W/4H)}{\tanh(\pi(W+2G)/4H)}$$

(2.2)

$$k_1' = \sqrt{1 - k_1^2} \tag{2.3}$$

$$k_2 = \frac{W}{W + 2G} \tag{2.4}$$

$$k_2' = \sqrt{1 - k_2^2} \tag{2.5}$$

$$\epsilon_{eff} = 1 + q(\epsilon_R - 1) \tag{2.6}$$

$$q = \frac{\frac{K(k_1)}{K(k'_1)}}{\frac{K(k_1)}{K(k'_1)} + \frac{K(k_2)}{K(k'_2)}}$$

(2.7)

W, G and H are physical dimensions of the CPW transmission line structure which are indicated in Figure 2.7,  $\epsilon_R$  is the relative permittivity of the substrate and K(k) is the complete elliptic integral of first kind. W and G values differs for the two designs, however H is 500  $\mu$ m and  $\epsilon_R$  is 3.8, which are fixed values.

G and W values of the CPW transmission line for the 26 GHz design has been chosen to be 90  $\mu$ m and 130  $\mu$ m. Characteristic impedance and effective permittivity for the 26 GHz design are found to be 85.9  $\Omega$  and 2.38, respectively.

On the other hand, G and W values for the 12 GHz design have been chosen to be 150  $\mu$ m and 220  $\mu$ m which lead to a characteristic impedance of 86.2  $\Omega$ . Effective permittivity in this case is calculated to be 2.34.

Attenuation constant of a CPW transmission line ( $\alpha_{CPW}$ ) have two components; one of them is due to conductor losses ( $\alpha_C$ ) and the second one is for dielectric losses ( $\alpha_D$ ), where:

$$\alpha_{CPW} = \alpha_C + \alpha_D \tag{2.8}$$

Formulations for the two components are available in the literature [41], however it has been observed that these formulations underestimates the real values. Most convenient way seems to be extracting  $\alpha_{CPW}$  from the EM simulation results.

#### 2.2.2.3.2 Switch Modeling in the Upstate

Return loss should be minimized at the desired operating frequency in the upstate (ON state) of a shunt, capacitive contact RF MEMS switch.

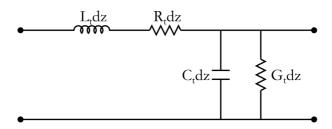

In order to explain the design procedure for the upstate of the switches, loading effect of the shunt, capacitive contact MEMS switches should be investigated. This type of switch loads the CPW transmission line capacitively due to the capacitance between the bridge and the signal trace. Figure 2.8 shows the general lumped element circuit model of a transmission line segment, which is the CPW line in our case.

Figure 2.8: Lumped element circuit model of a transmission line

For the case of a shunt, capacitive contact switch, the transmission line will be loaded by a shunt capacitance. Furthermore, low loss assumption may be made and loss components may be ignored for simplicity. The resulting circuit model for a short section ( $s \ll \lambda$ ) of a loaded transmission line with a length of s can be seen in Figure 2.9.

**Figure 2.9:** Simplified lumped element circuit model of a capacitively loaded transmission line with low loss assumption

After the low loss assumption, unloaded transmission line characteristic impedance may be approximated as:

$$Z_0 \cong \sqrt{\frac{L_t dz}{C_t dz}} = \sqrt{\frac{L_t}{C_t}}$$

(2.9)

The loaded line impedance, whose circuit model is indicated in Figure 2.9, may be calculated as follows:

$$Z_L = \sqrt{\frac{sL_t}{sC_t + C_u}} \tag{2.10}$$

where  $\mathcal{C}_u$  is the upstate capacitance of the RF MEMS switch.

By a comparison between (2.9) and (2.10), loaded line impedance ( $Z_L$ ) will be smaller than unloaded line impedance ( $Z_0$ ) and loading will take part by the effect of the upstate

capacitance of the switch. Therefore, by selecting a high  $Z_0$  and appropriate upstate capacitance,  $Z_L$  may be tuned to be close to 50  $\Omega$  reference impedance at the desired operation frequency and return loss can be minimized.

#### 2.2.2.3.3 Switch Modeling in the Downstate

Isolation should be optimized for the downstate (OFF state) of a shunt, capacitive contact RF MEMS switch.

Standard RF MEMS fabrication process cycle fixes some of the variables for the devices. Sacrificial layer thickness and dielectric layer thickness are two of them. In addition to these, upstate capacitance is fixed in the optimization of ON state return loss. If the circuit model of the switch in Figure 2.6 is considered, only variable remaining for optimizing OFF state isolation is the bridge inductance (L<sub>brd</sub>). By tuning bridge inductance resonance frequency of the switch may be tuned to the desired operation frequency which will maximize the isolation. This method is called inductive tuning and the bridge inductance can be controlled by recesses extending into the ground planes near the bridge.

Recess dimensions may be obtained after finding the required bridge inductance from the circuit model by sweeping this variable in the circuit simulations.

During the downstate design of the switches, partial contact approach is utilized. In this approach the contact area of the downstate capacitance is decreased intentionally in the EM simulations. By this approach, it is aimed to lower the actuation voltages and obtain an ability to tune the resonance frequency by tuning actuation voltage during the measurements. The procedure for this approach has been explained and can further be investigated in [14].  $\eta$  defined in [14] has been chosen as 25  $\mu$ m for 26 GHz design and 50  $\mu$ m for the 12 GHz design.

After applying the design procedure in both upstate and downstate of the MEMS switches, electromagnetic simulation results have been curve fitted with the circuit model simulations and circuit model parameters have been extracted. The circuit model parameters appearing in Figure 2.6, can be seen in Table 2.3 and Table 2.4 for 26 GHz design and for 12 GHz design, respectively.

**Table 2.3:** Circuit model parameters for the RF MEMS switch designed for 26 GHz operating frequency

| Parameter        | Value    |

|------------------|----------|

| $Z_0$            | 85.9 Ω   |

| $C_{u}$          | 62.7 fF  |

| $C_d$            | 423.3 fF |

| $L_{ m brd}$     | 90.1 fF  |

| $R_{brd}$        | 0.41 Ω   |

| $L_{s1}$         | 201 nH   |

| $L_{s2}$         | 201.2 nH |

| $C_{sh1}$        | 9.7 fF   |

| $C_{sh2}$        | 10.5 fF  |

| $\ell_{ m line}$ | 810 μm   |

**Table 2.4:** Circuit model parameters for the RF MEMS switch designed for 12 GHz operating frequency

| Parameter        | Value         |

|------------------|---------------|

| $Z_0$            | 86.2 Ω        |

| $C_{u}$          | 156.9 fF      |

| $C_d$            | 1056 fF       |

| $L_{brd}$        | 90.1 fF       |

| $R_{brd}$        | $0.36~\Omega$ |

| $L_{s}$          | 366.8 nH      |

| $C_{\rm sh}$     | 17.4 fF       |

| $\ell_{ m line}$ | 1760 μm       |

It must be noted that,  $L_s$  and  $C_{sh}$  parameters differs in the two series branch for the 26 GHz design due to nonsymmetry between recesses.

# 2.2.2.3.4 CPW Transition Integrations

Probes utilized in the RF measurements have 220  $\mu m$  ground-to-ground spacing in METU Electrical and Electronics Department. Therefore, it is necessary to have the exact spacing at the ports of the designed switches or any other MEMS devices. In order to accomplish this necessity linear CPW transitions are utilized. Loading effect of the bridge has been explained in the previous sections, where  $Z_L$  has been tuned to have an impedance value close to 50  $\Omega$  reference impedance. Thus it is practical to choose the CPW line impedance close to 50  $\Omega$  reference impedance at the ports of the switches. By assuming a ground to ground spacing of 220  $\mu$ m and using the formulations from (2.1) to (2.5), G and W values have been chosen to be 20  $\mu$ m and 180  $\mu$ m for both 26 GHz and 12 GHz designs which leads to a 52  $\Omega$  characteristic impedance.

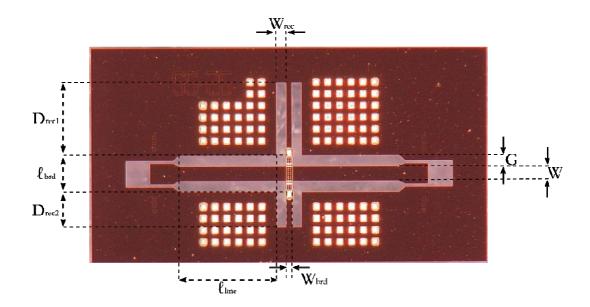

Figure 2.10 and Figure 2.11 indicates the micrographs of fabricated RF MEMS switches for 26 GHz and 12 GHz operating frequencies. In Figure 2.10, significant physical dimensions are shown, whose values are tabulated in Table 2.5 and Table 2.6.

**Figure 2.10:** A micrograph of fabricated RF MEMS switch at 26 GHz operating frequency, physical dimensions are also defined

Figure 2.11: A micrograph of fabricated RF MEMS switch at 12 GHz operating frequency

Table 2.5: Physical dimensions of the RF MEMS switch at 26 GHz

| Parameter                    | Value  |

|------------------------------|--------|

| W                            | 130 μm |

| G                            | 90 µm  |

| $W_{rec}$                    | 80 μm  |

| $D_{rec1}$                   | 620 μm |

| $\mathrm{D}_{\mathrm{rec2}}$ | 300 μm |

| $\mathrm{W}_{\mathrm{brd}}$  | 50 μm  |

| $\ell_{ m brd}$              | 310 µm |

| $\ell_{ m line}$             | 830 μm |

**Table 2.6:** Physical dimensions of the RF MEMS switch at 12 GHz

| Parameter                   | Value   |

|-----------------------------|---------|

| W                           | 220 μm  |

| G                           | 150 μm  |

| $W_{rec}$                   | 150 μm  |

| $D_{rec}$                   | 775 μm  |

| $\mathrm{W}_{\mathrm{brd}}$ | 80 μm   |

| $\ell_{ m brd}$             | 520 μm  |

| $\ell_{ m line}$            | 1760 μm |

# 2.2.2.3.5 Obtained Switches at 26 GHz and 12 GHz and Their Responses

Table 2.3 and Table 2.4 indicate obtained circuit model parameters for the switches both at 26 GHz and 12 GHz. As mentioned before these parameters are obtained by curve fitting of circuit simulation results and electromagnetic simulation results. Ansoft HFSS<sup>TM</sup> v11 is used to perform the electromagnetic simulations and the circuit simulations have been made by the use of AWR Microwave Office<sup>TM</sup> 2006. After obtaining the circuit parameters, CPW transitions are added to the circuit model just by importing their EM simulations results and final circuit model, where fabricated switches can be simulated.

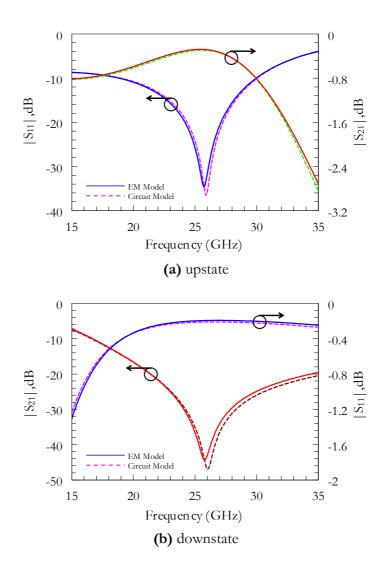

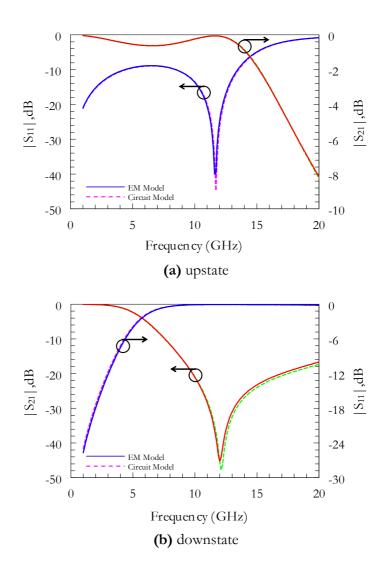

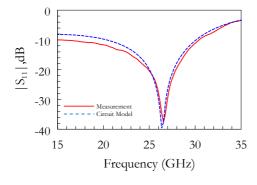

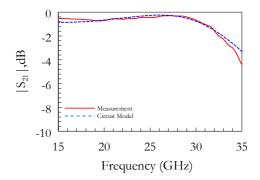

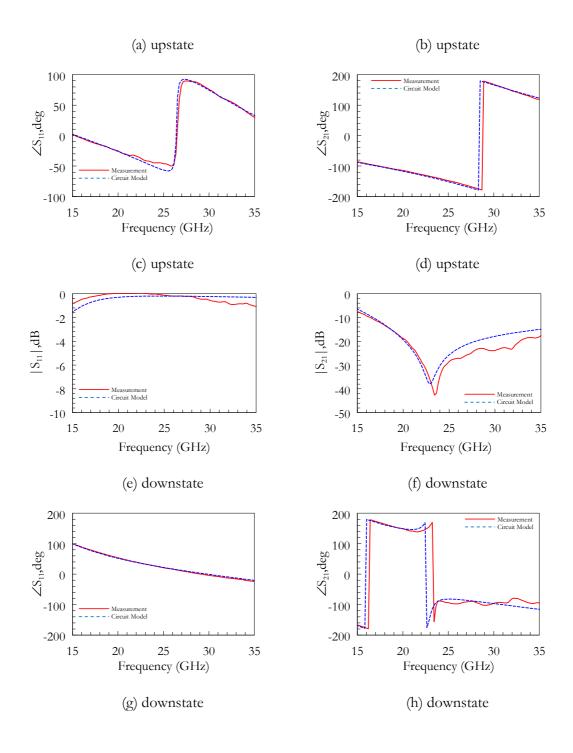

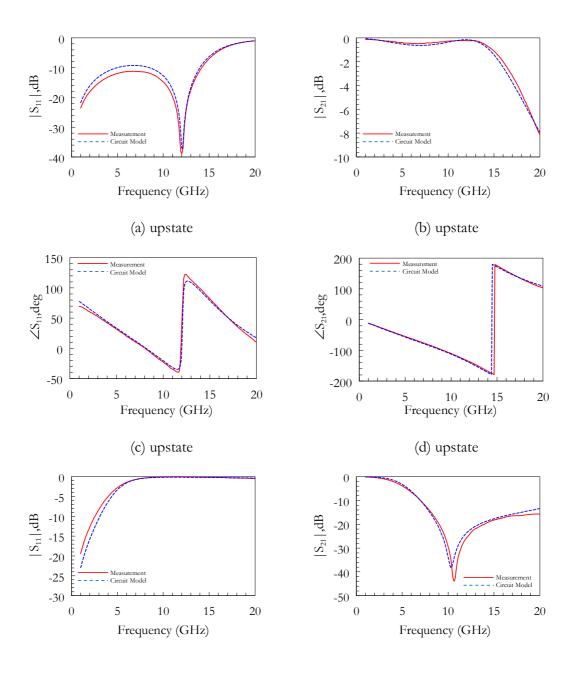

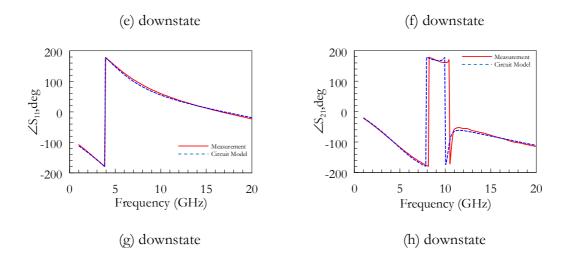

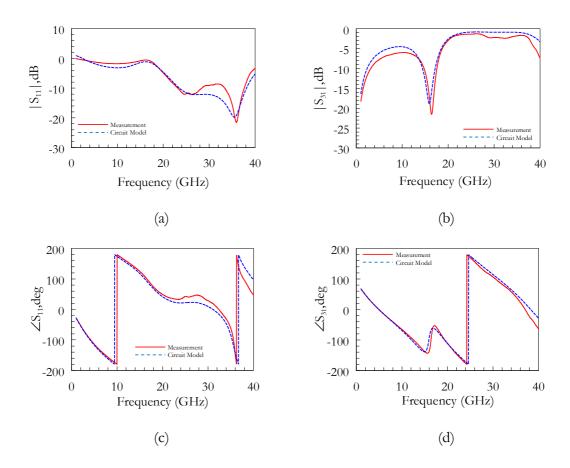

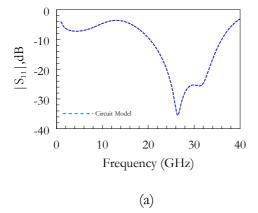

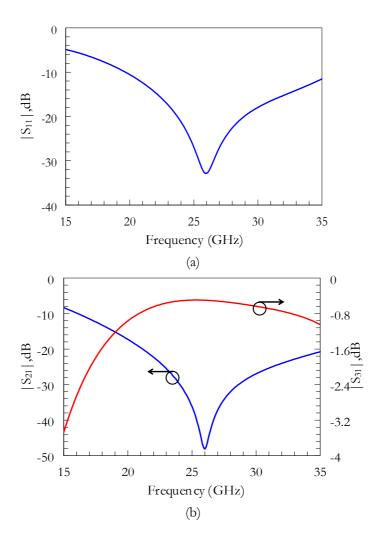

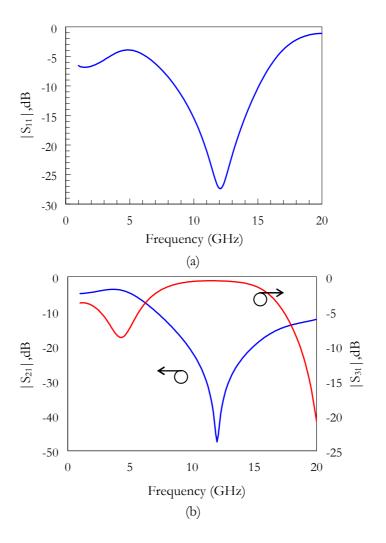

Figure 2.12 indicates obtained RF performances of the RF MEMS switch operating at 26 GHz both from EM simulations and circuit simulations. Consistency between EM and circuit simulation is noticeable.

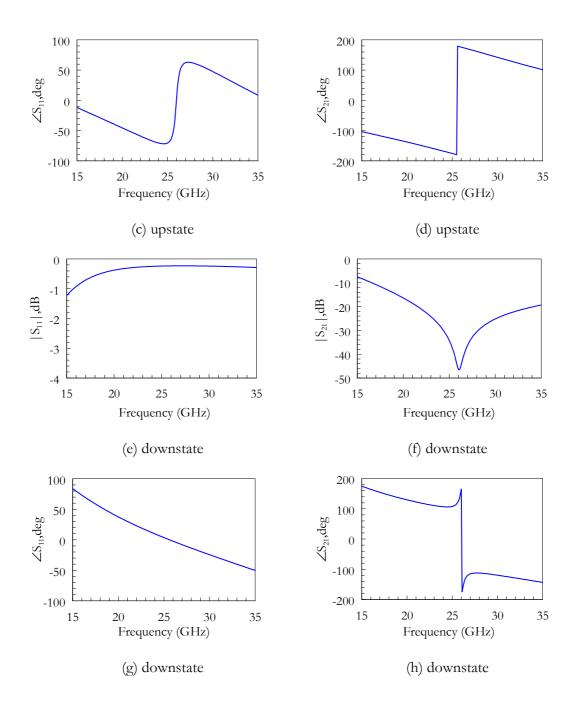

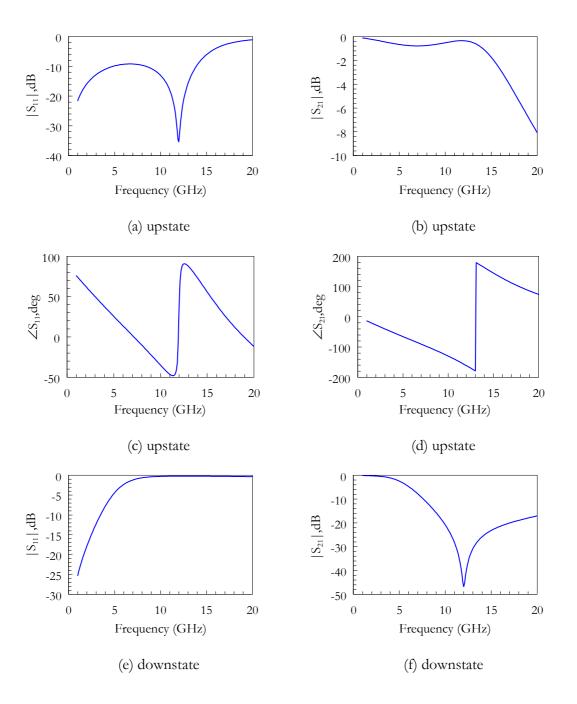

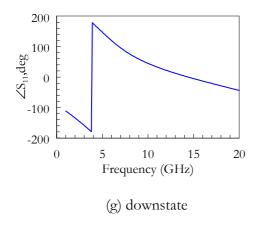

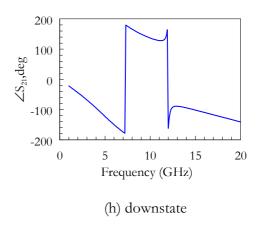

**Figure 2.12:** Magnitude S-parameters obtained by electromagnetic and circuit simulations for the RF MEMS switch designed at 26 GHz

Figure 2.13 indicates obtained RF performances of the RF MEMS switch operating at 12 GHz both from EM simulations and circuit simulations. EM and circuit simulation results are consistent again.

**Figure 2.13:** Magnitude S-parameters obtained by electromagnetic and circuit simulations for the RF MEMS switch designed at 12 GHz

# 2.2.3 CPW T-junction Design

CPW T-junction design is an important part for the utilized SPDT structures. Since a T-junction includes several discontinuities, mode conversion takes place within the circuit. A simple method to suppress the excitation of the coupled slot-line mode is by maintaining electrical continuity between the ground planes of the circuit [41]. It is important in a T-junction design that its effects on the general circuit are minimized. A T-junction should behave as connection of three 50  $\Omega$  transmission lines [42].

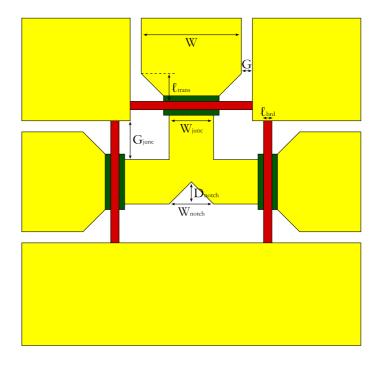

Two CPW T-junctions have been designed in this study; one of them for the SDPT at 26 GHz and the second is for the SPDT at 12 GHz. By inserting air bridges in the vicinity of the T-junction ports, mode conversion and so power loss is prevented. Width of the utilized air bridges are chosen to be as small as possible in order to decrease the loading effects, however due to process limitations a lower bound encountered. Loading effect of the MEMS bridges on the transmission lines has been explained in detail in Section 2.2.2.3.2. This loading effect has been considered in the ports of T-junction designs, where the loaded line impedances are adjusted to be 50 Ω. Ground to ground spacing of the CPW transmission lines entering the T-junction ports are conserved through the T-junction and CPW line dimensions under the MEMS bridges are analytically calculated by considering the loading effects of the bridges by using Matlab<sup>TM</sup>. In addition to these, notches are opened on the connection points of the two designs on the thru line directions. Dimensions of the notches are selected by comparing the EM simulation results, conducted in Ansoft HFSS<sup>TM</sup> v11. Obtained T-junction layouts for 26 GHz and 12 GHz operating frequencies are indicated in Figure 2.14, including abbreviations for the physical dimensions.

Figure 2.14: CPW T-junction layout and physical dimensions

Physical layout dimension appearing in Figure 2.14 are tabulated for both designs in Table 2.7 and Table 2.8.

Table 2.7: Dimensions of CPW T-junction design for 26 GHz operating frequency

| Parameter      | Value  |

|----------------|--------|

| W              | 180 μm |

| G              | 20 μm  |

| $\ell_{brd}$   | 15 µm  |

| $W_{notch}$    | 94 µm  |

| $D_{notch}$    | 50 μm  |

| $\ell_{trans}$ | 50 µm  |

| $W_{junc}$     | 94 µm  |

| $G_{junc}$     | 63 µm  |

**Table 2.8:** Dimensions of CPW T-junction design for 12 GHz operating frequency

| Parameter      | Value  |

|----------------|--------|

| W              | 260 μm |

| G              | 25 μm  |

| $\ell_{brd}$   | 15 μm  |

| $W_{notch}$    | 110 μm |

| $D_{notch}$    | 50 μm  |

| $\ell_{trans}$ | 50 μm  |

| $W_{junc}$     | 110 µm |

| $G_{junc}$     | 100 μm |

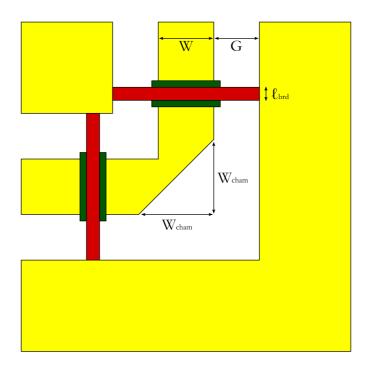

# 2.2.4 CPW 90° Bend Design

Measurement setup, actually the probe stations, in METU Electrical and Electronics Department necessitates utilizing CPW 90° Bend structures in the SPDT designs. Without using these bends it would be impossible for the RF measurements to be done. Due to this necessity two CPW 90° Bend structures have been designed and utilized in the SPDT structures as building blocks.