# SOFT AFDX (AVIONICS FULL DUPLEX SWITCHED ETHERNET) END SYSTEM IMPLEMENTATION WITH STANDARD PC AND ETHERNET CARD

## A THESIS SUBMITTED TO THE GRADUATE SCHOOL OF NATURAL AND APPLIED SCIENCES OF MIDDLE EAST TECHNICAL UNIVERSITY

$\mathbf{B}\mathbf{Y}$

EMRE ERDİNÇ

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE IN ELECTRICAL AND ELECTRONICS ENGINEERING

MAY 2010

# Approval of the thesis:

# SOFT AFDX (AVIONICS FULL DUPLEX SWITCHED ETHERNET) END SYSTEM IMPLEMENTATION WITH STANDARD PC AND ETHERNET CARD

submitted by EMRE ERDİNÇ in partial fulfillment of the requirements for the degree of Master of Science in Electrical and Electronics Engineering Department, Middle East Technical University by,

| Prof. Dr. Canan Özgen<br>Dean, Graduate School of Natural and Applied Sciences             |  |

|--------------------------------------------------------------------------------------------|--|

| Prof Dr. İsmet Erkmen<br>Head of Department, Electrical and Electronics Engineering        |  |

| Prof. Dr. Hasan Güran<br>Supervisor, Electrical and Electronics Engineering Dept, METU     |  |

|                                                                                            |  |

| Examining Committee Members                                                                |  |

| Prof. Dr. Semih Bilgen<br>Electrical and Electronics Engineering Dept, METU                |  |

| Prof. Dr. Hasan Güran<br>Electrical and Electronics Engineering Dept, METU                 |  |

| Assoc. Prof. Dr. Cüneyt F. Bazlamaçcı<br>Electrical and Electronics Engineering Dept, METU |  |

| Asst. Prof. Dr. Şenan Ece Schmidt<br>Electrical and Electronics Engineering Dept, METU     |  |

| MSc. Mert KOLAYLI<br>Avionics Design Engineer, TUSAS                                       |  |

| Date:                                                                                      |  |

I hereby declare that all information in this document has been obtained and presented in accordance with academic rules and ethical conduct. I also declare that, as required by these rules and conduct, I have fully cited and referenced all material and results that are not original to this work.

Name, Last name : Emre ERDİNÇ

Signature :

# ABSTRACT

# SOFT AFDX (AVIONICS FULL DUPLEX SWITCHED ETHERNET) END SYSTEM IMPLEMENTATION WITH STANDARD PC AND ETHERNET CARD

Erdinç, Emre M.Sc. Department of Electrical and Electronics Engineering Supervisor: Prof. Dr. Hasan Güran

May 2010, 107 pages

ARINC 664/AFDX (Avionics Full Duplex Switched Ethernet) protocol is a leading onboard communication technology in civil aviation. As AFDX is a new technology, unit cost of the hardware devices are high and protocol is open to changes. This thesis discusses the design of an AFDX End System application for test environment with a software based solution with cheap COTS (Commercial offthe shelf) equipment, explains the implementation of the software and analysis the performance.

Keywords: Avionics Full Duplex Switched Ethernet, Avionic data buses, Soft AFDX

# STANDART PC VE ETERNET KARTI İLE YAZILIMSAL AFDX (AVIONICS FULL DUPLEX SWITCHED ETHERNET) UÇ SİSTEM UYGULAMASI

Erdinç, Emre M.Sc. Department of Electrical and Electronics Engineering Supervisor: Prof. Dr. Hasan Güran

Mayıs 2010, 107 sayfa

ARINC 664/AFDX (Avionics Full Duplex Switched Ethernet) protokolü, sivil havacılıkta önder bir uçak içi haberleşme teknolojisidir. Çok yeni bir teknoloji olduğundan donanım cihazlarının birim fiyatları yüksektir ve protokol değişikliklere açıktır. Bu tez çalışmasında, bir test ortamı için RAHAT (RAfta HAzır Ticari) ucuz ekipman kullanılarak yazılım tabanlı bir AFDX uç sistem tasarımı tartışılmış, uygulama yazılımı yapılmış ve performans analizleri gerçekleştirilmiştir.

Anahtar Kelimeler: Avionics Full Duplex Switched Ethernet, Avionic Veriyolları, Yazılımsal AFDX

## ACKNOWLEGMENTS

The author wishes to express his gratitude to his supervisor Prof. Dr. Hasan Cengiz Güran for his guidance, advice, criticism, encouragements, insight and his tolerance throughout the research.

He would like to express his appreciation to the members of TAI, Turkish Aerospace Industries for their technical support and tolerance during this study.

The author would also like to thank his mother Neriman Erdinç, his father Nedim Erdinç and especially to his wife Selen Erdinç for their endless support and patience. And lastly, he wishes to thank his friends Gürsu Karateke, Coşkun Çelik and Aykut Erden for their encouragement and support.

# TABLE OF CONTENTS

| ABSTRACT                                                    | iv   |

|-------------------------------------------------------------|------|

| ÖZ                                                          | v    |

| ACKNOWLEGMENTS                                              | vi   |

| TABLE OF CONTENTS                                           | vii  |

| LIST OF TABLES                                              | X    |

| LIST OF FIGURES                                             | xi   |

| LIST OF ABBREVIATIONS                                       | xiii |

| LIST OF CHAPTERS<br>1. INTRODUCTION                         | 1    |

| 2. AVIONICS DATA BUSES                                      | 6    |

| 2.1. Types of Data Bus                                      | 7    |

| 2.1.1.Unidirectional Data Bus                               | 7    |

| 2.1.2.Bidirectional Data Bus                                | 8    |

| 2.2. Some of the Most Used Avionics Communication Protocols | 9    |

| 2.2.1.ARINC 429                                             | 10   |

| 2.2.2.MIL-STD-1553                                          | 14   |

| 2.3. Avionics Full-Duplex Switched Ethernet (AFDX)          | 20   |

| 2.3.1. History                                              | 20   |

| 2.3.2. Characteristics                                      | 20   |

| 2.3.3. AFDX Network Components                              | 21   |

| 2.3.4. Comparison with other Avionics Buses                 |      |

| 2.3.5. AFDX Solutions                                       | 27   |

| 3. FRAME STRUCTURE OF AFDX AND COMPARISON WITH THE          |      |

| RELATED COMMUNICATION STANDARDS                             | 29   |

|        | 3.1. General                                                                                                          | . 29                                                                         |

|--------|-----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

|        | 3.2. Physical Layer                                                                                                   | . 30                                                                         |

|        | 3.3. Data Link Layer                                                                                                  | . 30                                                                         |

|        | 3.3.1 Source Address                                                                                                  | . 32                                                                         |

|        | 3.3.2 Destination Address                                                                                             | . 32                                                                         |

|        | 3.3.3 Type                                                                                                            | . 33                                                                         |

|        | 3.3.4 Integrity Check                                                                                                 | . 33                                                                         |

|        | 3.3.5 Redundancy Management                                                                                           | . 34                                                                         |

|        | 3.3.6 Flow Regulation                                                                                                 | . 35                                                                         |

|        | 3.3.7 Flow Scheduling                                                                                                 | . 35                                                                         |

|        | 3.3.8 Data Link Layer Overview                                                                                        | . 35                                                                         |

|        | 3.4 Network Layer                                                                                                     | . 37                                                                         |

|        | 3.4.1 IP Structure                                                                                                    | . 38                                                                         |

|        | 3.4.2 IP Source Address:                                                                                              | . 38                                                                         |

|        | 3.4.3 IP Destination Address                                                                                          | . 39                                                                         |

|        | 3.5 Transport Layer                                                                                                   | . 39                                                                         |

|        | 3.6 Application Layer                                                                                                 | . 41                                                                         |

| 4. IMP | LEMENTATION                                                                                                           | . 42                                                                         |

|        | 4.1. Platform                                                                                                         | . 42                                                                         |

|        | 4.2. Tools                                                                                                            | 13                                                                           |

|        | 4.2. 10015                                                                                                            | . 43                                                                         |

|        | 4.2.1 Development Environment                                                                                         |                                                                              |

|        |                                                                                                                       | . 43                                                                         |

|        | 4.2.1 Development Environment                                                                                         | . 43<br>. 43                                                                 |

|        | <ul><li>4.2.1 Development Environment</li><li>4.2.2 Data Link Layer Frame Access</li></ul>                            | . 43<br>. 43<br>. 46                                                         |

|        | <ul><li>4.2.1 Development Environment</li><li>4.2.2 Data Link Layer Frame Access</li><li>4.3. Configuration</li></ul> | . 43<br>. 43<br>. 46<br>. 46                                                 |

|        | <ul> <li>4.2.1 Development Environment</li></ul>                                                                      | . 43<br>. 43<br>. 46<br>. 46<br>. 46                                         |

|        | <ul> <li>4.2.1 Development Environment</li></ul>                                                                      | . 43<br>. 43<br>. 46<br>. 46<br>. 46<br>. 47                                 |

|        | <ul> <li>4.2.1 Development Environment</li></ul>                                                                      | . 43<br>. 43<br>. 46<br>. 46<br>. 46<br>. 46<br>. 47                         |

|        | <ul> <li>4.2.1 Development Environment</li></ul>                                                                      | . 43<br>. 43<br>. 46<br>. 46<br>. 46<br>. 47<br>. 47                         |

|        | <ul> <li>4.2.1 Development Environment</li></ul>                                                                      | . 43<br>. 43<br>. 46<br>. 46<br>. 46<br>. 46<br>. 47<br>. 47<br>. 47<br>. 50 |

|        | <ul> <li>4.2.1 Development Environment</li></ul>                                                                      | . 43<br>. 43<br>. 46<br>. 46<br>. 46<br>. 47<br>. 47<br>. 47<br>. 50<br>. 51 |

| 4.5 AFDX Receiver                                           | 64  |

|-------------------------------------------------------------|-----|

| 4.5.1 API Stack Overview                                    | 64  |

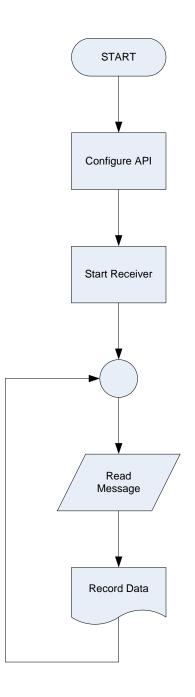

| 4.5.2 Application Flow Chart                                | 67  |

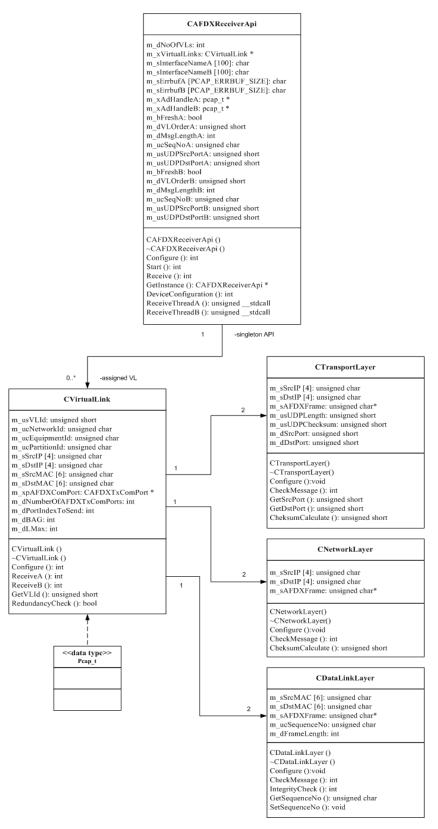

| 4.5.3 Application Class List                                | 68  |

| 4.4.4 Detailed Explanation of the AFDX Receiver ApplicatioN | 78  |

| 5. PERFORMANCE                                              | 81  |

| 5.1. Latency                                                | 81  |

| 5.2. MAC Constraints                                        | 84  |

| 5.3. Jitter                                                 | 85  |

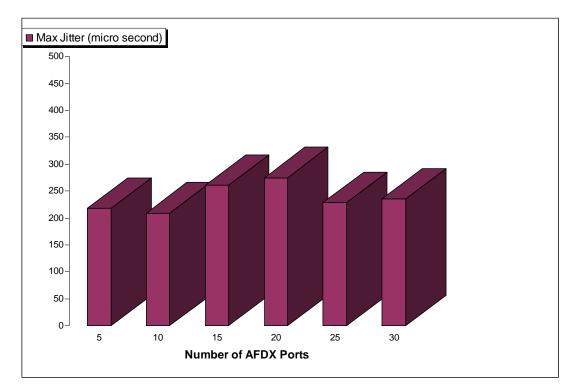

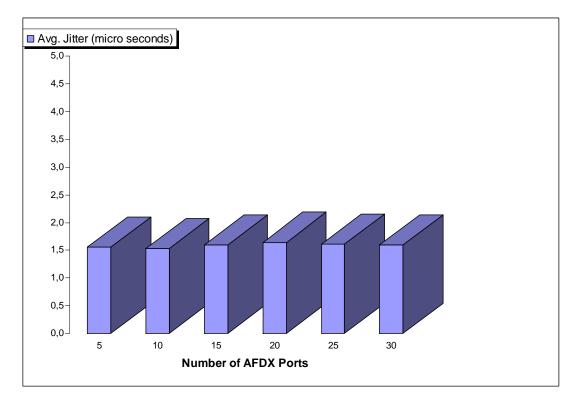

| 5.3.1 The Effect of Number of AFDX Ports on Jitter          | 86  |

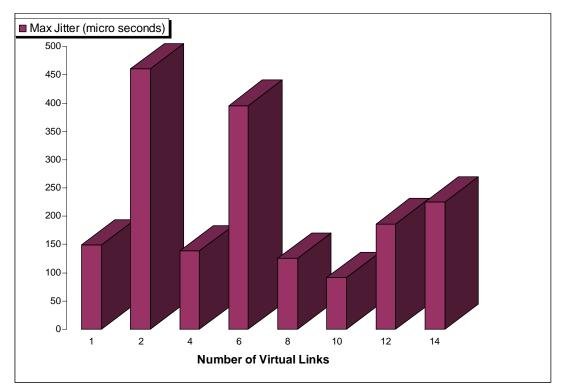

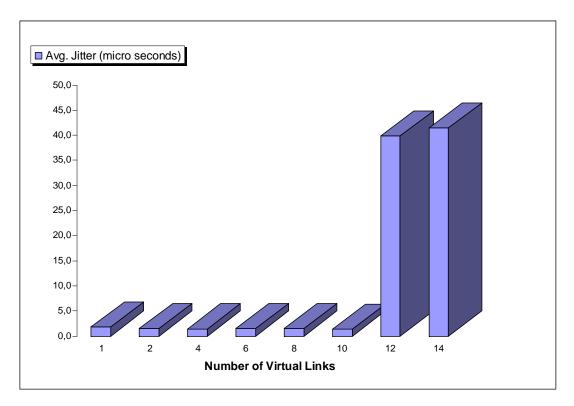

| 5.3.2 The Effect of Number of Virtual Links on Jitter       | 89  |

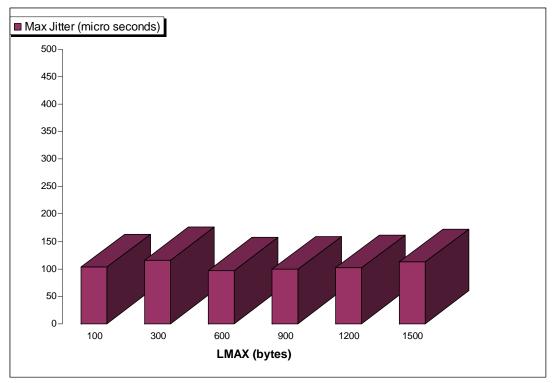

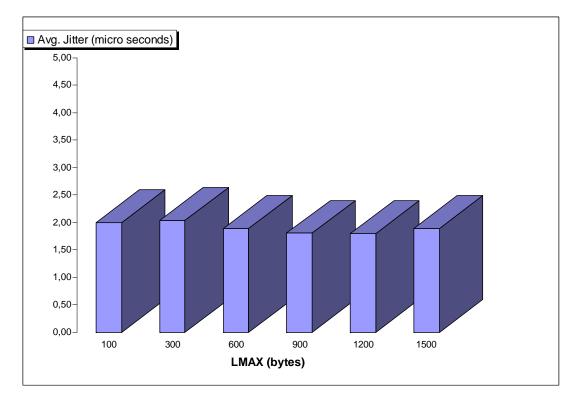

| 5.3.3 The Effect of Lmax on Jitter                          | 92  |

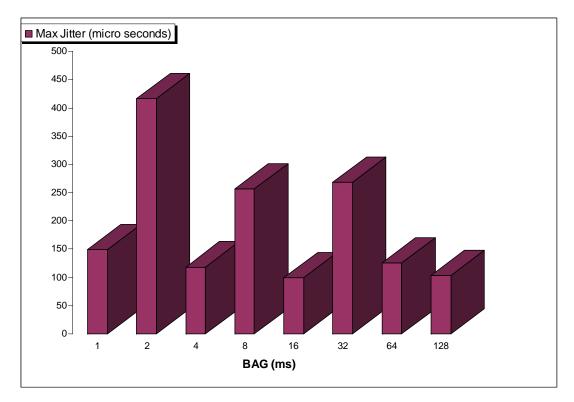

| 5.3.4 The Effect of BAG on Jitter                           | 95  |

| 6. CONCLUSION                                               | 98  |

| REFERENCES                                                  | 102 |

| AFDXAPI.H FILE OF AFDX TRANSMITTER                          | 104 |

| AFDXAPI.H FILE OF AFDX RECEIVER                             | 106 |

# LIST OF TABLES

| Table 2.1 Criteria for an Avionics Data Bus       | 7  |

|---------------------------------------------------|----|

| Table 2.2 SSM Meaning for different data types    | 14 |

| Table 2.3 Comparison Results                      | 27 |

| Table 5.1 Transmitter Latency Test Results Sample | 83 |

# LIST OF FIGURES

| Figure 1.1 Independent Avionics                                    | 2    |

|--------------------------------------------------------------------|------|

| Figure 2.1 Unidirectional data bus                                 |      |

| Figure 2.2 Bidirectional data bus                                  | 9    |

| Figure 2.3 ARINC 429 cabling                                       | . 10 |

| Figure 2.4. ARINC 429 Message Format                               | 11   |

| Figure 2.5. Binary data allocation                                 | 12   |

| Figure 2.6. BCD data allocation                                    | 12   |

| Figure 2.7 MIL-STD-1553B Bus concept                               | 16   |

| Figure 2.8 MIL-STD-1553B Coupling Types                            | 16   |

| Figure 2.9 MIL-STD-1553B Word formats                              | 17   |

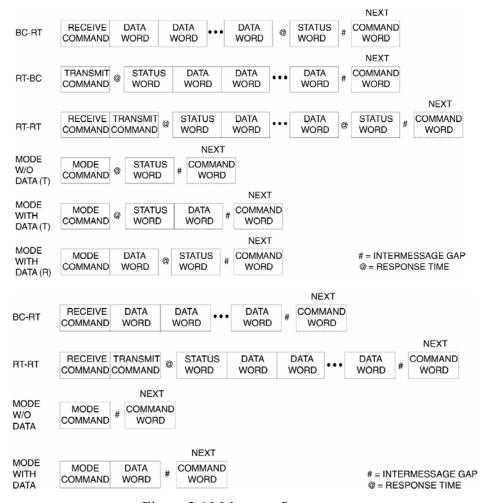

| Figure 2.10 Message Sequence                                       | 19   |

| Figure 2.11. Sample AFDX Network                                   | 21   |

| Figure 2.12. AFDX End System                                       | 21   |

| Figure 2.13. Physical Cable and Virtual Links                      | 23   |

| Figure 2.14. Bandwidth of the Virtual Links                        |      |

| Figure 2.15. Round Robin                                           | 25   |

| Figure 2.16. AFDX Switch                                           | 25   |

| Figure 3.1 A brief description in layered architecture perspective | 30   |

| Figure 3.2 Ethernet Frame (Data Link Layer)                        | 31   |

| Figure 3.3. AFDX Frame (Data Link Layer)                           | 31   |

| Figure 3.4 MAC Source Address                                      | 32   |

| Figure 3.5 MAC Destination Address                                 | 33   |

| Figure 3.6 Network Redundancy Concept                              | 34   |

| Figure 3.7 AFDX Transmitter Data Link Layer Overview               | 36   |

| Figure 3.8 AFDX Receiver Data Link Layer Overview                  | 37   |

| Figure 3.9 AFDX Frame (Network Layer)                              | 37   |

| Figure 3.10 IPv4 Structure                                         | 38   |

| Figure 3.11 IP Source Address                                      | 39   |

| Figure 3.12 IP Destination Address                                 |      |

| Figure 3.13 AFDX Frame (Transport Layer)                           | 39   |

| Figure 3.14 UDP Header                                             | 40   |

| Figure 3.15 Allocation of SAP and AFDX Port Numbers                | 40   |

| Figure 3.16 Port Allocation Range for IP Unicast or Multicast      | 40   |

| Figure 3.17 AFDX Message Structure                                 | 41   |

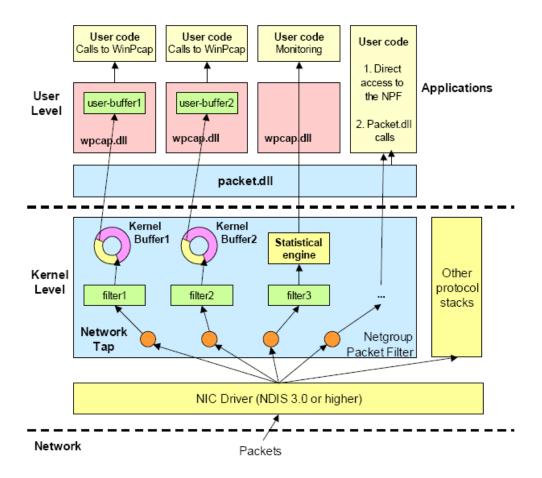

| Figure 4.1. Winpcap Capture Stack                                  | 45   |

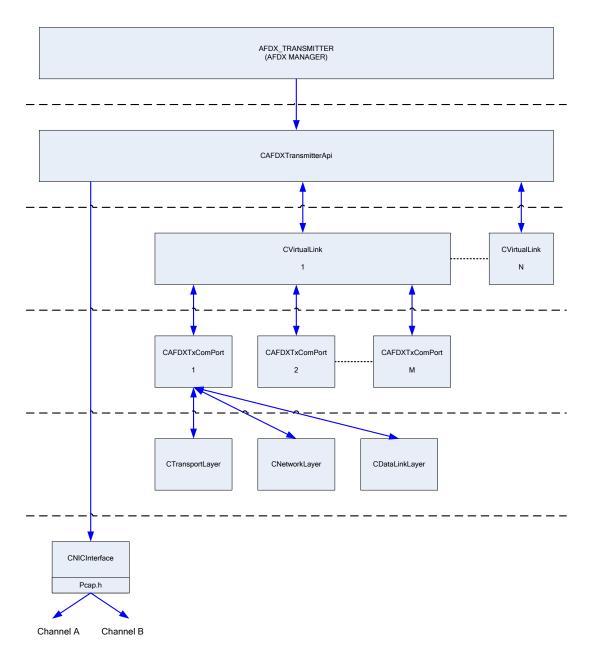

| Figure 4.2. AFDX Transmitter class hierarchy                       | 49   |

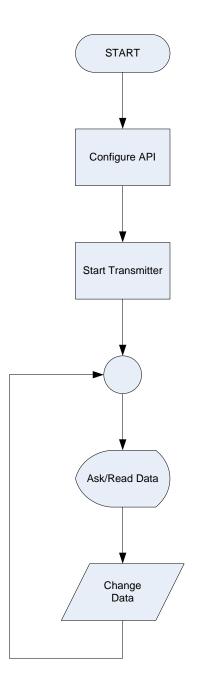

| Figure 4.3. AFDX Transmitter Application Flow Chart                |      |

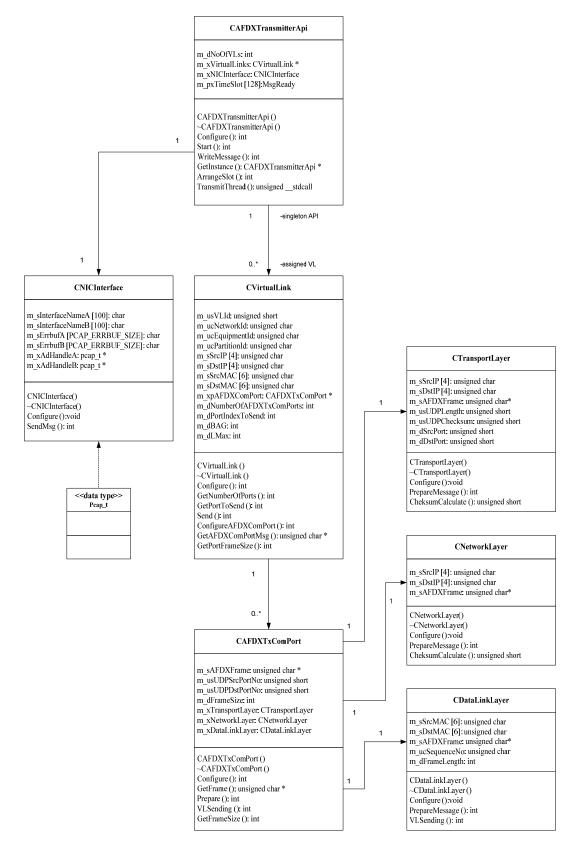

| Figure 4.4. AFDX Transmitter Class Diagram                         | 52   |

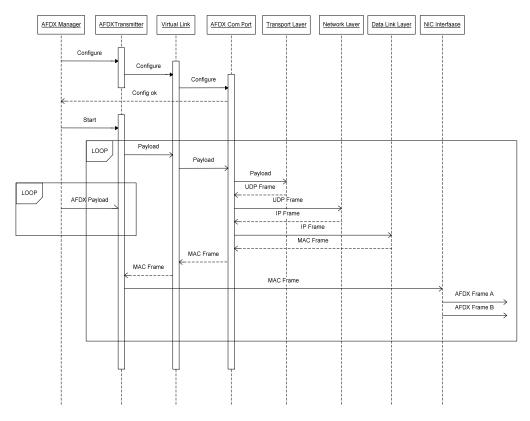

| Figure 4.5. AFDX Transmitter Sequence Diagram                      | 61 |

|--------------------------------------------------------------------|----|

| Figure 4.6. AFDX Transmitter Configuration File                    |    |

| Figure 4.7. AFDX Receiver API Stack Overview                       |    |

| Figure 4.8. AFDX Receiver Application Flow Chart                   |    |

| Figure 4.9. AFDX Receiver Class Diagram                            | 69 |

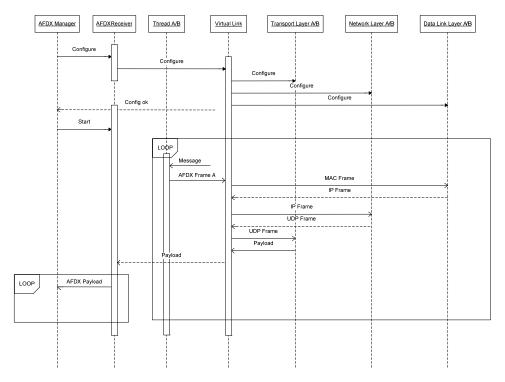

| Figure 4.10 AFDX Receiver Sequence Diagram                         |    |

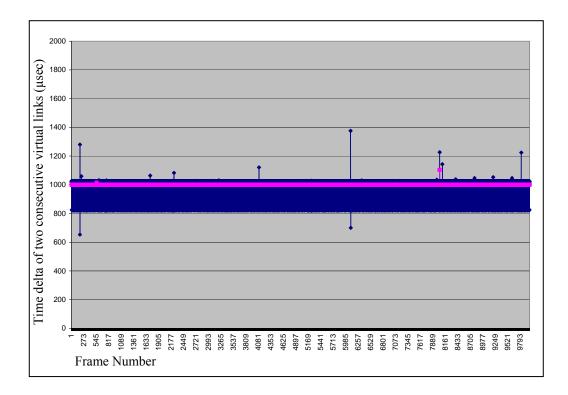

| Figure 5.1 Full Bandwidth Usage Test                               | 85 |

| Figure 5.2 The Effect of Number of AFDX Ports on Maximum Jitter    |    |

| Figure 5.3 The Effect of Number of AFDX Ports on Average Jitter    | 89 |

| Figure 5.4 The Effect of Number of Virtual Links on Maximum Jitter |    |

| Figure 5.5 The Effect of Number of Virtual Links on Average Jitter |    |

| Figure 5.6 The Effect of Lmax on Maximum Jitter                    |    |

| Figure 5.7 The Effect of Lmax on Average Jitter                    |    |

| Figure 5.8 The Effect of BAG on Maximum Jitter                     |    |

| Figure 5.9 The Effect of BAG on Average Jitter                     |    |

# LIST OF ABBREVIATIONS

| AEEC  | Airlines Electronic Engineering Committee         |

|-------|---------------------------------------------------|

| AFDX  | Avionics Full Duplex Switched Ethernet            |

| API   | Application Programming Interface                 |

| ARINC | Aeronautical Radio Incorporated                   |

| BC    | Bus Controller                                    |

| BCD   | Binary Coded Decimal                              |

| BM    | Bus Monitor                                       |

| BNR   | . Two's complement binary                         |

| BNRZ  | Bipolar Non Return to Zero                        |

| CAN   | Controller Area Network                           |

| CSV   | Comma-Separated Values                            |

| CPU   | Central Processing Unit                           |

| DAL   | Design Assurance Level                            |

| DAS   | Data Acquisition System                           |

| DLL   | Dynamic Link Library                              |

| EASA  | European Aviation Safety Agency                   |

| FAA   | Federal Aviation Administration                   |

| FADEC | Full Authority Digital Engine Control             |

| FCS   | Frame Check Sequence                              |

| ID    | Identification                                    |

| IEEE  | Institute of Electrical and Electronics Engineers |

| IETF  | Internet Engineering Task Force                   |

| IFG   | . Inter Frame Gap                                 |

| IMA   | Integrated Modular Avionics                       |

| IP    | Internet Protocol                                 |

| IP     | . Intellectual Property                          |

|--------|--------------------------------------------------|

| ISO    | . International Organization for Standardization |

| Kbps   | . Kilo bits per seconds                          |

| LRU    | . Line Replaceable Unit                          |

| MAC    | . Medium Access Control Protocol                 |

| NIC    | . Network Interface Card                         |

| NPF    | . Netgroup Packet Filter                         |

| OS     | . Operating System                               |

| OSI    | . Open System Interconnection                    |

| PCI    | . Peripheral Component Interconnect              |

| РМС    | . PCI Mezzanine Card                             |

| PHY    | . Physical Layer                                 |

| RM     | . Redundancy Management                          |

| RT     | . Remote Terminal                                |

| RTCA   | . Radio Technical Commission for Aeronautics     |

| RTOS   | . Real Time Operating System                     |

| SAE    | . Society of Automotive Engineers                |

| SDI    | . Source/Destination Identifier                  |

| SFD    | . Start Frame Delimiter                          |

| SMTP   | . Simple Mail Transfer Protocol                  |

| SN     | . Sequence Number                                |

| SNMP   | . Simple Network Management Protocol             |

| SSM    | . Sign/Status Matrix                             |

| ТСР    | . Transmission Control Protocol                  |

| TFTP   | . Trivial File Transfer Protocol                 |

| TTL    | . Time To Live                                   |

| UDP    | . User Datagram Protocol                         |

| VL     | . Virtual Link                                   |

| VMEbus | . Versa Module Eurocard Bus                      |

# **CHAPTER 1**

## **INTRODUCTION**

The term "avionics" is the combination of the aviation and electronics, which could be defined as electronics of aircrafts, artificial satellites and spacecrafts. Collinson mentions that the word avionics "was first used in the USA in the early 1950s and has since gained wide scale usage and acceptance" [1].

The sensors and instrumentation structure in the aircrafts became more and more complicated in parallel with the development of the aircrafts day by day. In 1783, the Montgolfier brothers used a barometer to measure altitude. From about 1914, first gyro systems were used. "World War 2 drove a number of important advances including navigation aids, airborne radar and electronic warfare equipment" [2].

In the beginning of the second half of 20th century, aircraft avionics were composed of a few separate, analog systems such as radar, navigation and communication equipment and cockpit displays, connected by dedicated wiring. During 1960's and 1970's, the number of avionics increased per aircraft, digital technology appeared and systems began to be more complex. Also with the rise of digital technology, equipment was started to be designed to share information with each other. This communication needed increased the number of wirings in the aircraft which resulted in an increase of power consumption and weight. After 1970s, the use of data bus was introduced in aviation and this helped to reduce number of wirings and simplify total design and also maintenance.

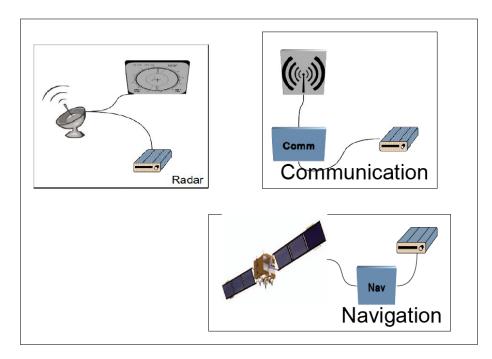

Avionics architectures were also affected with these revolutions. The earliest architecture was independent avionics architecture in which each equipment had its own functionality independent of other similar or different equipment. Following figure represents a sample of independent avionic architecture.

Figure 1.1 Independent Avionics

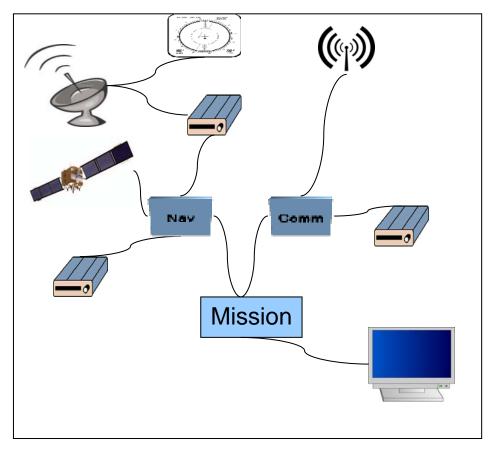

In the next decades, the integration of the different kind of systems emerged as a Federated Avionics Systems. Federated System Architectures have separate subsystems implementing functions using dedicated components, dedicated modules, LRUs, and software. Federated Architectures do not share or time-share component or information across subsystems in the avionics suite

Figure 1.2 Federated Avionics

Integrated Architectures share "components" to support multiple functions. Integrated front ends simultaneously share or time-share the same antennas, RF/EO modules, processor modules and data buses. Integrated Software/Data/Control Architectures share information and control across subsystems or functions.

Last generation avionics architecture at the time of writing of this thesis was Integrated Modular Avionics (IMA). IMA combines LRU's into software packages running on a computer. IMA defines the separation of the resources and enables certification independently [3]. "In the IMA architecture model, most special-topurpose controllers are replaced by common standardized platforms (so-called IMA modules) that usually host applications of several systems. For inter-system communication, either IMA module-internal communication or standardized aircraft networking technology with guaranteed bandwidth and high availability is used" [4]. New architectures require new communication skills. Avionics Full Duplex Switched Ethernet (AFDX) is a suitable data communication specification for IMA which supports means for addressing partitions.

AFDX is the leading edge avionics network technology that is chosen by the greatest aircraft companies like Airbus and Boeing. The first application of AFDX was started with A380 of Airbus and continued with A400M of Airbus Military and Boeing 787.

As the AFDX is a very new technology and is considered to be the future of the aviation, more companies started to focus on components and development of AFDX systems.

In this thesis we aim to study well known avionics data buses. Describe their basic specifications, characteristics and usage. Moreover we aim to study the features of the ARINC 664/AFDX specification in details and investigate layers of AFDX and messaging specifications, give a comparison with other avionics buses and underline its superiorities. Finally we aim to develop software running on a standard PC with a Windows XP operating system that uses standard Ethernet cards to implement AFDX communications and make performance analysis.

Chapter 2 gives a brief background on different avionic data buses. Describes the specifications of AFDX, makes a comparison between AFDX and other buses and lists advantages and disadvantages of both hard AFDX solutions and soft AFDX solutions.

Chapter 3 looks more closely into the AFDX frame structure and investigates the basic differences with the standard UDP/IP frames on Ethernet.

Chapter 4 explains the development environment, tools and the software developed for this thesis.

Chapter 5 gives the performance criteria for AFDX End System and describes the performance test conducted.

Finally Chapter 6 summarizes the thesis and concludes with comments on the test results and on the performance and states some future work directions.

## CHAPTER 2

# **AVIONICS DATA BUSES**

Wide usage of information sharing in avionics systems brought defining safety-critical communication protocols. Most modern avionics flight control systems are designed with a group of central computers named as mission computer, flight control computer, central control computer, etc. that are connected to sensors and actuators using point-to-point connections. To decrease the weight and increase flexibility, broadcast communication protocols is replacing the point-to-point architecture. As an example, the military transport aircraft C130J's avionic systems were previously using discrete wiring and were upgraded to the MIL-STD-1553B bidirectional data bus. This upgrade returned a significant weight saving, and a very high amount of work hour was saved to wire the harnesses. However, the bus handling became more complex.

The communication bus handling has grown up as a new discipline besides the engineering of the integrating complex systems. Some main basic rules (Table 2.1) have been defined to certificate an avionics data bus.

| Criterion                   | Selected Evaluation Factors                    |

|-----------------------------|------------------------------------------------|

| Safety                      | Availability and reliability,                  |

|                             | Partitioning, Failure detection,               |

|                             | Common cause/mode failures,                    |

|                             | Bus expansion strategy,                        |

|                             | Redundancy management                          |

| Data Integrity              | Maximum error rate,                            |

|                             | Error recovery, Load analysis                  |

|                             | Bus capacity, Security                         |

| Performance                 | Operating speed, Bandwidth,                    |

|                             | Schedulability of messages,                    |

|                             | Bus length and max. load,                      |

|                             | Retry capability, Data latency                 |

| Electromagnetic Compability | Switching speed, Wiring, Pulse rise and fall   |

|                             | times,                                         |

| Design Assurance            | Compliance with standards (such as DO-254      |

|                             | & DO-178B)                                     |

| Configuration Management    | Change control, compliance with standards,     |

|                             | documentation, interface control, etc.         |

| Continued Airworthiness     | Physical degradation, in-service modifications |

|                             | and repairs, impact analysis, etc.             |

Table 2.1 Criteria for an Avionics Data Bus [5]

## 2.1. Types of Data Bus

#### 2.1.1. Unidirectional Data Bus

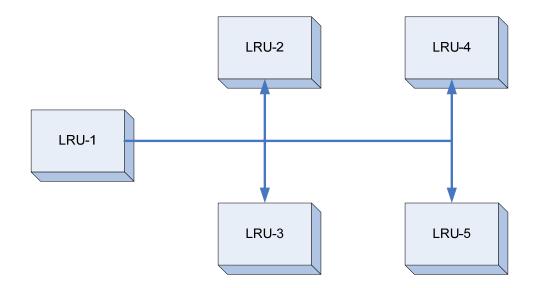

In a unidirectional data bus, the system is driven by a single transmitter and a number of receivers that monitor the line and listen for all or specific data. If it is necessary to communicate back to the transmitter node, a separate transmission line should be defined. The simplicity of this topology makes the bus more reliable and easy to design and implement. But with respect to bidirectional buses, unidirectional buses need more wiring; resulting in more weight, more cost. The following figure represents a unidirectional data bus, LRU-1 is the driver (transmitter) and other LRUs are receivers.

Figure 2.1 Unidirectional data bus

## 2.1.2. Bidirectional Data Bus

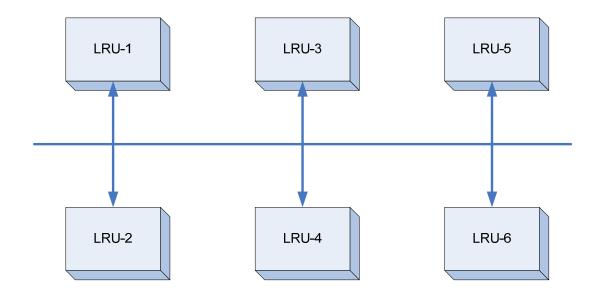

In a bidirectional data bus, each node can both receive and transmit. Arbitration of the bus may be master/slave or multi-master type.

In a master/slave mode type bus, there should always be a master that is responsible for all messaging on the bus. The master can initiate a data transfer from master to slave, slave to master or a slave to another slave. It is possible to design the bus with one or more backup masters that can take the control of the bus with a predefined scenario and control the messaging on the bus.

In a multi-master type bus, there is more than one node which can start a transmission. For this kind of buses arbitration mechanism should be defined. This mechanism may be realized electrically as in CAN bus, or in a time sharing basis.

Also the messaging can be half-duplex or full-duplex.

Following figure represents a bidirectional data bus. Each LRU is able to transmit and receive data on the same media.

Figure 2.2 Bidirectional data bus

#### 2.2. Some of the Most Used Avionics Communication Protocols

As the number of functions added to an air vehicle increase, to decrease the pilot workload, many complex functions that use lots of data are ported to the computers. As a result, data transfer for an aircraft increases, lots of intelligent LRUs appear and the need to communicate all of the LRUs becomes more and more important and complex.

The definition of the protocols makes it easier to integrate the systems and experience sharing for an aircraft development which gets more complicated in each new product. These definitions are published by some leading aviation committees like ARINC that cooperates with RTCA/EUROCAE, IEEE, Society of Automotive Engineers (SAE), EIA/ANSI/ISO Standards Organizations, etc.

These organizations develop and publish specifications for data communication for general and special purposes. Some of these protocols are widely used and some others are used for special applications. Following sections introduce into most common used protocols in aviation world.

#### 2.2.1. ARINC 429

ARINC 429 is one of the most used data transfer protocol in aviation and according to ARINC 429 Tutorial of Condor Engineering [6], "is the most commonly used data bus for commercial and transport aircraft."

ARINC 429 was developed from the old ARINC 419 Specification which was released in 1966 and had a final revision in 1983. ARINC 419 was defining four different wiring topologies which were also including ARINC 429 wiring type. In 1978, Aeronautical Radio Incorporated published the first release of ARINC 429 specification which was adopted by the AEEC in 1995. Specification is comprised of 3 parts; "ARINC Specification 429, Part 1-15: Functional Description, Electrical Interface, Label Assignments and Word Formats" which addresses the buses physical parameters, label and address assignments, and word formats, "ARINC Specification 429, Part 2-15: Discrete Word Data Standards" which defines the formats of words with discrete word bit assignments and "ARINC Specification 429, Part 3-15: File Data Transfer Techniques" which defines link layer file data transfer protocol for data block and file transfers [7].

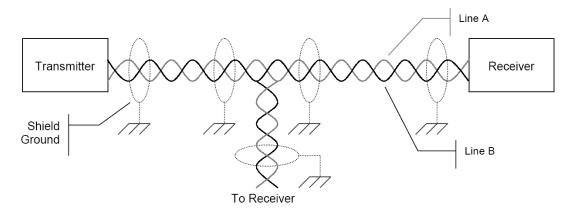

The first issue about ARINC 429 specification is the physical layer characteristics. 78 ohm twisted shielded cable is used to connect the nodes. Shields should be grounded in both ends and in each junction as given in the figure.

Figure 2.3 ARINC 429 cabling [7]

ARINC 429 is a differential line with bipolar non return to zero (BNRZ) signaling. Differential voltage between two lines is +10V (between 7,25 and 11V), - 10V (between -7,25 and -11V) or 0 V (between -0,5 and 0,5V) for high, low and null respectively. 32 bit words are separated with 4 bit times of null gaps and each bit has a transition from the zero volts according to BNRZ which together help synchronization without a clock signal.

ARINC 429 is a simplex data bus, the transmitter starts unidirectional message flow to at least one but up to 20 receivers. Line length is not specified in the specification which depends on number and location of receivers.

Two bit rates are defined in the specification; high speed 100 kbps and low speed 12-14,5 kbps. Rise and fall times of the signal is  $10\pm5$  µs for low speed and  $1,5\pm0,5$  µs for high speed [8].

32 bit message consists of Label, SDI (Source/Destination Identifier), Data, SSM (Sign/Status Matrix) and Parity fields as given in the Figure 2.4. Label and parity are required fields in the message in contrast with optional SSM, SDI and data which can be used for different purposes.

| 32 | 31 3 | 0 | 29   |         | 11        | 10 | 9 | 8 1   |

|----|------|---|------|---------|-----------|----|---|-------|

| P  | SSM  |   | DATA | ← PAD ← | DISCRETES | S  | Z | LABEL |

|    |      |   | MSB  |         | LSB       |    |   |       |

Figure 2.4. ARINC 429 Message Format

8 bit Label identifies the data and message format which is generally expressed in 3 octal digits. Label is the first transmitted field that informs the receivers about the remaining of the message. Bit order of the message is least significant bit first but this order shows difference only for the label, of which the 8<sup>th</sup> bit is transmitted first. Source/Destination Identifier is used to identify either the source of the data or the destination receiver. As it is optional it may also be added to the data in order to increase the resolution.

The 19 bits Data field starts from the 11<sup>th</sup> bit and continues up to 29<sup>th</sup> bit. This may be considered as a disadvantage that the resolution is not high enough for sensitive parameters. As ARINC 429 specification is very flexible, data may be used in different formats such as two's complement binary (BNR), decimal coded binary (BCD), discrete data, maintenance data and acknowledgement and ISO Alphabet #5 character data.

For binary format, generally 16 bits of the 19 bit is used as left aligned data and the remaining 3 bits (bits 11, 12 and 13) are padded with 0. But it is also possible to use all 19 bits for data. The most significant bit (29<sup>th</sup> bit) is the sign bit. A 1 in the sign bit indicates a negative number or a direction; "South", "West", "Left", "From" or "Below". A zero is used to indicate a positive number or "North", "East", "Right", "To" or "Over".

| 29   | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20   | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 |

|------|----|----|----|----|----|----|----|----|------|----|----|----|----|----|----|----|----|----|

| Sign |    |    |    |    |    |    |    | Ι  | alue |    |    |    |    |    |    |    | Pa | d  |

Figure 2.5. Binary data allocation

When BCD data format is used, the data field is divided into 5 subfields each representing a BCD digit. The most significant digit is 3 bits and it is possible to put numbers 0 to maximum 7. Other digits are 4-bit standard BCD digits.

| 29 28 27    | 26 25 24 23 | 22 21 20 19 | 18 17 16 15 | 14 13 12 11 |

|-------------|-------------|-------------|-------------|-------------|

| BCD Digit 1 | BCD Digit 2 | BCD Digit 3 | BCD Digit 4 | BCD Digit 5 |

Figure 2.6. BCD data allocation

In a Discrete data format ARINC 429 word, bits are named one by one to represent a specific Boolean data. Generally, bit assignment starts with the 11<sup>th</sup> bit

and unused bits are padded with 0. It is also common that discrete data are combined with binary or BCD data that is called as mixed data format. When the data format is mixed, discrete data starts from least significant bit of data and binary or BCD part is assigned from the most significant part.

Maintenance data or acknowledgement requires two way communications which can be established by using two ARINC 429 channels. Williamsburg/Buckhorn is a bit-oriented file transfer protocol where more than 21 bits are necessary to transfer also used in maintenance data or acknowledgement. This file transfer mechanism uses handshake, that's why, requires two ARINC 429 channels.

Another field in the ARINC 429 word is Sign/Status Matrix, bits 30 and 31, has different meanings according to data type. The sign or direction of the data, status of the transmitting equipment or validity of the data transmitted may be indicated with this two bit field. The meaning of the field according to data type is given in Table 2.2.

The  $32^{nd}$  bit of the word is parity bit. Odd parity is used in ARINC 429 messages.

| BIT |    | BNR Data Type    | BCD Data Type                            | Discrete Data Type                 |

|-----|----|------------------|------------------------------------------|------------------------------------|

| 31  | 30 | Di la Dum 1990   | Dod Data Type                            | Discrete Dum Type                  |

| 0   | 0  | Failure Warning  | Plus, North, East, Right,<br>To, Above   | Verified Data, Normal<br>Operation |

| 0   | 1  | No Computed Data | No Computed Data                         | No Computed Data                   |

| 1   | 0  | Functional Test  | Functional Test                          | Functional Test                    |

| 1   | 1  | Normal Operation | Minus, South, West, Left,<br>From, Below | Failure Warning                    |

Table 2.2 SSM Meaning for different data types

#### 2.2.2. MIL-STD-1553

US Department of Defense published MIL-STD-1553 specifications in 1973 as a standard of US Air Force that defines mechanical, electrical and functional properties of a time division command response multiplex bus. It was designed to be used in military aviation but it is still being widely used in civil and transport aircrafts and also for in other sectors like railway systems. The first application of MIL-STD-1553 was F-16 Fighting Falcon. Then, it was used in F-18 Hornet and many other programs.

MIL-STD-1553A of 1975 was revised as MIL-STD-1553B in 1978. One of the most important differences between two versions is; MIL-STD-1553B defines protocol more strictly and clearly than MIL-STD-1553A and therefore enables an easier integration of subsystems from different companies. Also redundancy requirement of MIL-STD-1553B is a major difference. MIL-STD-1553B has six revisions from 1978 to date.

Bi-phase Manchester coded data is transmitted via a cable pair that has a 70-80  $\Omega$  -typically 78  $\Omega$ - impedance at 1 MHz. The bit rate is 1 Mbps for the bus. Bus can have double or triple redundant media as using various pairs of cables independently. Common usage is dual redundant bus. For dual redundant usages, one of the lines is active and the alternate bus always stays silent and is used only when a failure occurs in the active bus. General naming for redundant lines in a MIL-STD-1553B bus is; Primary bus (Bus A) and Secondary bus (Bus B).

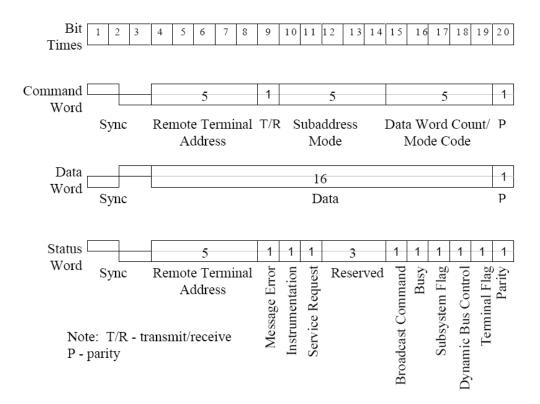

The messages are transmitted over 16 bits words (command, data or status). Each word starts with a 3  $\mu$ s synchronization pulse, 1,5  $\mu$ s low and 1,5  $\mu$ s high, and ends with a parity bit. Parity for MIL-STD-1553B is odd. In practical, each word can be considered as 20 bits: 3 bits for synchronization, 16 bits of payload and 1 bit for parity check. The words in a message are transmitted consecutively and there is a 4  $\mu$ s delay between each word. A remote terminal is required to respond a command in maximum 12  $\mu$ s.

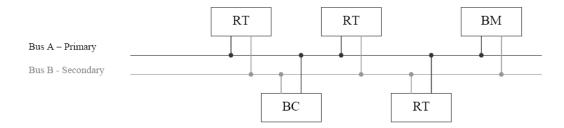

The elements of the MIL-STD-1553B bus are BC (bus controller), RT (remote terminal) and BM (bus monitor). For a MIL-STD-1553B network, BC and RT are essential.

Bus controller is responsible to control all communication in the bus, emission or reception is done with a command of the bus controller. There can only be one bus controller for a bus. Also backup bus controller (BBC) is defined as a backup for the bus which is able to take the control [9].

Remote terminals are 5 bit addressed slave devices responding to the bus controller. Remote terminals count has been limited with 31 devices for each line [10].

There is no limitation in number for bus monitors. System integrator is free to install unlimited number of bus monitors to the bus in order to record traffic or simply not to use a bus monitor. Bus monitors are devices that have no address and never respond to any message. Alignment of the devices in the bus is given in the following figure.

Figure 2.7 MIL-STD-1553B Bus concept

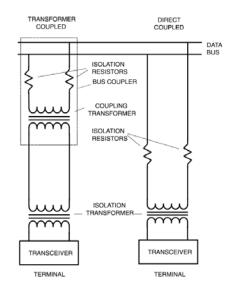

Connection of devices to the bus can be done in two types; direct coupling and transformer coupling. Direct coupling is connecting the conductors directly whereas transformer coupling is connecting a terminal to the bus over a transformer. Stub length for direct coupling is 1 foot and this length increases up to 6 feet for a transformer coupling. Following figure shows both coupling types.

Figure 2.8 MIL-STD-1553B Coupling Types

There are three types of words defined for MIL-STD-1553B bus; command word, data word and status word.

Bus controller always initiates the messaging by a command word. The command word is formed as follows; The first 5 bits are the address of the remote terminal (0-31). The sixth bit is "0" for reception and "1" for transmission. The

direction of the flow is always decided with the remote terminal view. The 5 following bits indicate the position at which to supply or acquire the data (subaddress) in the terminal (1-30) or the type of the message is a mode code (0, 31). The final 5 bits indicate the number of the words to wait for (1-32). If all are "0", indicate 32 words to transmit or receive. In the case of the mode code, these bits are the number of the mode code; such as Initiate Self Test, Transmit BIT Word, etc.

The status word is formed as; the first 5 bits are the remote terminal address that is replying. 9<sup>th</sup> to 19<sup>th</sup> bits are used as flags and as reserved bits. Following figure shows each word type with bit field indications.

Figure 2.9 MIL-STD-1553B Word formats

There are 9 types of transaction between bus controller and remote terminals.

• BC to RT: The bus controller sends one command word that includes the remote terminal address, subaddress and number of data words to

be received by the RT which is immediately followed by 1 to 32 data words. The remote terminal which is selected sends only one status word to the bus controller that informs about status of the transaction and terminal.

- RT to BC: The bus controller sends one word to the remote terminal that includes the remote terminal address, subaddress and number of data words to be transmitted by the RT. The remote terminal sends only one status word hat informs about status of the transaction and terminal which is immediately followed by 1 to 32 data words to the bus controller.

- Mode Code with / without data word: The bus controller sends one command word with a subaddress/ mode field filled with 0 or 32. The command can be followed by a word dependent to the selected mode code. The remote terminal responds with a status word that can be followed by a single word of data according to mode code type.

- RT to RT: The bus controller sends one command word for the receiving remote terminal to receive data followed by one command word to the transmitting remote terminal to transmit data. The transmitting terminal sends one word followed by 1 to 32 words of data to the receiving terminal. The receiving terminal sends its status word finally.

- BC to RTs (Broadcast Data): This functionality did not exist at MIL-STD-1553A. The bus controller sends one command word to terminal 31, in reality this indicates that the command word is sent as broadcast type, followed by 1 to 32 data words. All the remote terminals accept the data without replying with a status word. This functionality can be used for the actualization of the whole system such as time information.

- Broadcast Mode Code with / without data word: The bus controller sends one command word with a subaddress/ mode field filled with 0 or 32. The command can be followed by a word dependent to the selected mode code.

The sequence for each transaction is defined in the standard. The sequences guarantee that the terminal is working properly and ready to transmit or receive data. The request issued at the end of the transmission shows that the data is received and the result of the transmission of the data is legitimate. This sequence proves the high-integrity of the MIL-STD-1553B.

Remote terminal device can not originate the transmission by itself. The requests of the transmissions are generated by the bus controller to the terminals. The high-priority messages appear more frequently compared to the low-priority ones but the protocol does not specify any time-share between word types. This is decided by the system architectures by taking into account that the absence of the reply indicates failure.

Figure 2.10 Message Sequence

#### **2.3.** Avionics Full-Duplex Switched Ethernet (AFDX)

#### **2.3.1.** History

As described in the other network types, limitations due to the topology or protocol forced the system integrators to develop a new definition by taking the advantage of the flexibility and wide usage in terrestrial networks and readily available software of IEEE 802.3, Ethernet.

"ARINC 664 Aircraft Data Network specification defines electrical characteristics and protocol recommended for commercial avionics. It is Ethernet for avionics, which is usually shunned by avionics engineers for its non-determinism. This was overcome when Airbus created Avionics Full Duplex Ethernet (AFDX<sup>TM</sup>) and the Airlines Electronic Engineering Committee (AEEC) adapted it in ARINC 664 Part 7, published on June 27, 2005. AFDX is a deterministic protocol for real time application on Ethernet media." [11]

#### **2.3.2.** Characteristics

AFDX is a serial data bus which supports data transmission at 10 or 100 Mbps rates over a copper or fiber transmission medium. It is a deterministic network, which guarantees the bandwidth of each logical communication channel, called a Virtual Link (VL) with traffic flow control. The jitter and transmit latency are defined and limited. Packets are received in the same order that they are transmitted. Carrying the same information at the same time over two redundant channels ensures the reliability and availability of the AFDX standard; each AFDX channel has to be a dual redundant channel.

These characteristics make AFDX to ensure "a BER as low as  $10^{-12}$  while providing a bandwidth up to 100 Mbps." [12]

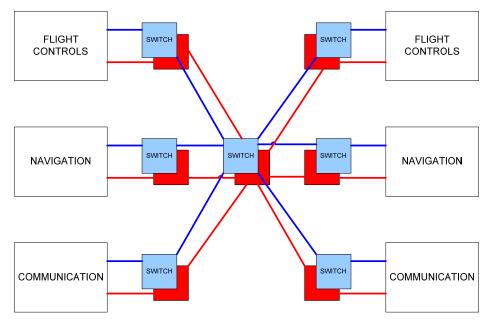

Figure 2.11. Sample AFDX Network

## 2.3.3. AFDX Network Components

#### 2.3.3.1. End System

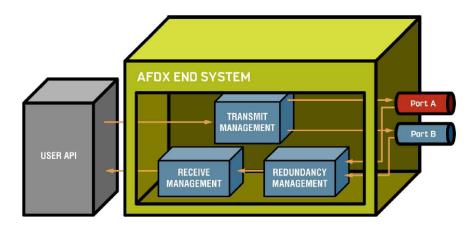

The AFDX End System (ES) is the part of an avionics system or an avionics subsystem that connects logical unit to the physical AFDX network. An End System implements protocol specific functions and carries out messaging features. Functions may be classified as transmitting function and receiving functions.

Figure 2.12. AFDX End System [13]

"Transmit Management allows creation of VL, transmitting of data, and scheduling of messages onto the network interconnect media. Redundancy Management allows gathering of the correctly ordered data using both port A and port B in case of data corruption. Receive Management allows correctly ordered data to reach the API" [13]. The requirements for an AFDX End System which will be described later are addressed in ARINC 664 specification.

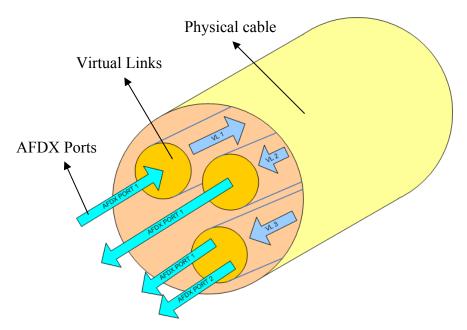

#### 2.3.3.2. Virtual Link

The Virtual Link (VL) concept has been inspired from ARINC 429 protocol. Virtual Links are logical implementations of the unidirectional point-to-point physical connections of ARINC 429. A transmitting Virtual Link may be connected to unlimited number of receiving Virtual Links but a receiving Virtual Link is shall be connected to only and only one transmitting Virtual Link.

Each interface of an AFDX End System is connected to the switch which connects the End System to the AFDX network. This connection is established via a single physical transmission line. However, definition of the Virtual Links enables establishing many separate and "isolated" logical connections between End Systems on the same physical medium.

"VLs make it possible to establish a sophisticated network communication while ensuring a deterministic behavior through VL bandwidth policing carried out by the switch." [12] An AFDX End-Systems is required to support up to 128 VLs.

Figure 2.13. Physical Cable and Virtual Links

### Virtual Link Scheduling

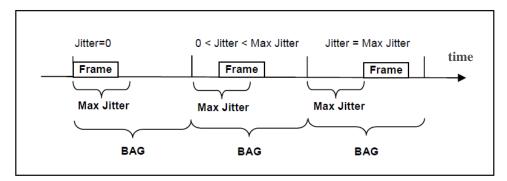

An End System has to shape the generated traffic according configuration of the network and AFDX messaging properties. In the AFDX specifications, the bandwidth of the Virtual Links is fixed by defining a time window Band Allocation Gap (BAG) and a jitter that tolerates the delays which occur on the medium (Figure 2.14). In each VL there are multiple frames that have to be ordered into a single flow of frames. The BAG defines the minimum time slot between two consecutive frames which has a value in the range of 1 to 128 ms with the powers of 2; 1ms, 2 ms, 4 ms, 8 ms, 16 ms, 32 ms, 64 ms and 128 ms. "The variation (i.e., standard deviation) in the packet arrival times is called jitter." [14] In AFDX messaging, it is expected to observe a frame of the same VL in the interval of BAG time after the last frame and BAG time plus maximum jitter time after the last frame.

Figure 2.14. Bandwidth of the Virtual Links

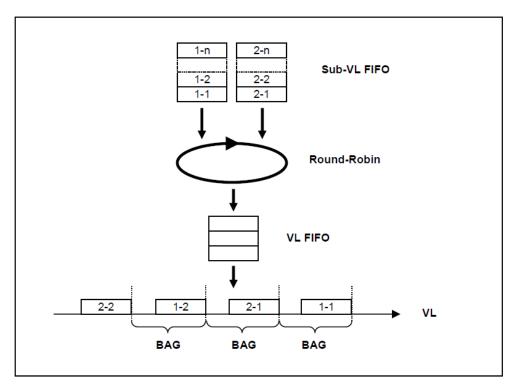

### Sub Virtual Links

"To accommodate less critical data communication needs, AFDX also allows for the construction of sub virtual links (sub-VLs)." [15] Sub Virtual Links are data queues that share a single Virtual Link. A Virtual Link reads each data queue in a round robin manner and services the available data to the network according to its BAG definition. Sub Virtual Link and normal port communication cannot be assigned to a Virtual Link at the same time; if sub Virtual Links are assigned to a Virtual Link, it can only serve to these sub Virtual Links. On the other hand any sub Virtual Link cannot distribute its messages across different Virtual Links. Sub-VLs are useful for non critical or non time critical data transmission.

Figure 2.15. Round Robin

### 2.3.3.3. AFDX Switch

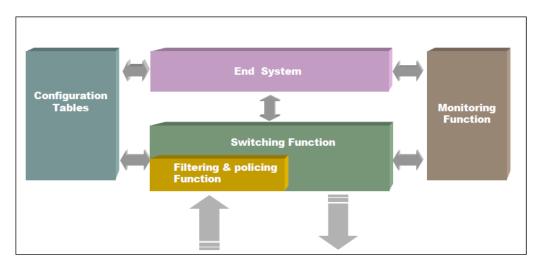

AFDX switch is the central element of the star topology of AFDX network that interconnects the End System to the End System and network to the network.

Figure 2.16. AFDX Switch [16]

The functions assigned to an AFDX Switch are; filtering, policing and switching valid incoming frames to the correct destinations according to network configuration. All incoming frames enter to the filtering and policing functional block that drops the invalid frames and switching functional block deliver the valid frames to the correct destinations. Information about the frames is stored in the configuration tables. Switch is configured with "static" configuration tables according to the network architect's definitions.

Monitoring Function is used to monitor and log all switch operations and service health and network status data to the subsystems.

AFDX Switch plays the most important role for the shaped traffic feature of the AFDX network.

#### 2.3.4. Comparison with other Avionics Buses

Schuster and Verma [11] made a comparison between AFDX and two major avionics data buses; ARINC 429 which is commonly used in civil aircrafts and MIL-STD-1553B which is commonly used in military aircrafts. They started to evaluation with six stakeholders; Performance, Reliability, Security & Certifiability, Cost, Evolvability & Flexibility and Supportability & Logistics. Then they listed 13 criteria; Transmission Speed, Throughput, Latency, Quality of Service (QoS), Partitioning, Redundancy, Topology, Harness Requirements, Software (SW) Development, Weight, Hardware (HW) Reliability, Software Reliability and COTS Availability. They weighted each criterion according to stakeholders with subjective approach according to their experience and graded them with four numbers; 0 for not linked, 1 for possibly linked, 3 for moderately linked and 9 for strongly linked.

According to their evaluation result "AFDX bus provides more redundancy, security, speed, determinism, and long-term cost effectiveness for the cumulative

required support (wire, hardware, and software)." Following table shows the results of their evaluation.

|                      | BU        | S SCOR            | E    |            |

|----------------------|-----------|-------------------|------|------------|

| CRITERIA             | ARINC 429 | MIL-STD-<br>1553B | AFDX | PRIORITIES |

| Transmission Speed   | 1         | 3                 | 9    | 5%         |

| Throughput           | 1         | 3                 | 9    | 4%         |

| Latency              | 9         | 1                 | 3    | 9%         |

| QoS                  | 9         | 1                 | 3    | 4%         |

| Partitioning         | 3         | 1                 | 9    | 12%        |

| Redundancy           | 9         | 3                 | 9    | 9%         |

| Topology             | 3         | 3                 | 9    | 12%        |

| Harness Requirements | 1         | 3                 | 9    | 6%         |

| SW Development       | 3         | 3                 | 9    | 6%         |

| Weight               | 3         | 3                 | 3    | 2%         |

| HW Reliability       | 3         | 3                 | 3    | 12%        |

| SW Reliability       | 3         | 3                 | 3    | 11%        |

| COTS Availability    | 3         | 3                 | 9    | 7%         |

| SCORE                | 4         | 2,5               | 6,7  |            |

Table 2.3 Comparison Results [11]

#### **2.3.5. AFDX Solutions**

#### 2.3.5.1. Hard AFDX Stack

Most common implementation type of AFDX is with specific hardware in PMC, PCI, PCI-X, VMEbus or other form factors. The electronics circuitry may use standard Ethernet chips with a microcontroller or a DSP or implement with an FPGA with use of specific IP (Intellectual Property) core. Some FPGA companies like Actel publishes design guidelines for AFDX End System implementation. [15]

Pickles [13] lists the advantages of a hard AFDX solution as reduced host processing requirement and easy distribution as a COTS PMC style board.

He also lists the disadvantages as possible hardware design change requirements due to being new technology of AFDX, component obsolescence issues that may require redesign and re-certification of the product and costs of creating and maintaining firmware code, which is typically written in low-level assembly language.

#### 2.3.5.2. Soft AFDX Stack

Soft AFDX stack is another idea to implement End System in the host computer along with application software. This implementation option uses processing resources of computer to realize protocol requirements and readily available Ethernet hardware for interconnection to the physical medium.

For Soft AFDX, Pickles [13] starts to list the advantages with cheap and readily available hardware. He implies the easily updating opportunity to faster transmission rates without changing the design. He adds that there is no obsolescence issue and possible protocol changes may be implemented in a high-level language, such as C, C++ or Ada.

He also highlights the disadvantages of Soft AFDX stack as the need for more processing power for protocol implementation on the host and necessity to Ethernet driver and protocol stack optimization for hard performance requirements of the standard such as latency.

# **CHAPTER 3**

# FRAME STRUCTURE OF AFDX AND COMPARISON WITH THE RELATED COMMUNICATION STANDARDS

### 3.1. General

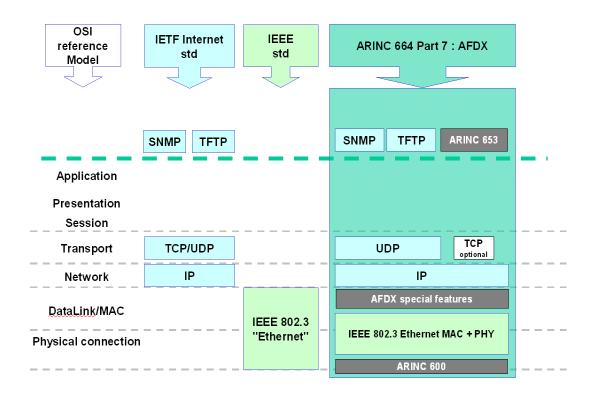

OSI (Open System Interconnection) Reference Model is composed of seven layers as given below;

- Physical Layer

- Data Link Layer

- Network Layer

- Transport Layer

- Session Layer

- Presentation Layer

- Application Layer

On the other hand, TCP/IP Model is composed of 4 layers given below;

- Link Layer

- Internet Layer

- Transport Layer

- Application Layer

AFDX is also an open standard, inspired with these layered models and common protocols. Following figure gives a brief description in layered architecture perspective.

Figure 3.1 A brief description in layered architecture perspective

### **3.2. Physical Layer**

Physical layer is not restrictedly specified for AFDX, but should be any of the ARINC 664 Part 2 defined solutions. The physical layer that is used in modern day computers is acceptable. Connection with CAT-5, CAT-6 or fiber media may be used with a star topology. The physical layer part of Ethernet 802.3 is used for AFDX systems.

### 3.3. Data Link Layer

In Draft 3 of Project Paper 664: Aircraft Data Network, Part 7 - Avionics Full Duplex Switched Ethernet (AFDX) Network [16], it is denoted that IEEE Standard 802.3, 2000 Edition, is considered an integral part of ARINC 664 specification.

A standard Ethernet frame is given below;

| 7 (bytes) | 1           | 6                      | 6                 | 2                | 45-1499          | 4           | 12  |

|-----------|-------------|------------------------|-------------------|------------------|------------------|-------------|-----|

| Preamble  | S<br>F<br>D | Destination<br>Address | Source<br>Address | T<br>y<br>p<br>e | Ethernet Payload | F<br>C<br>S | IFG |

Figure 3.2 Ethernet Frame (Data Link Layer)

Ethernet frame has a header;

- Destination MAC Address (6 bytes)

- Source MAC Address (6 bytes)

- Ethernet Type (2 bytes) And a trailer;

- Frame Check Sequence (4 bytes)

Payload part is minimum 46 bytes and maximum 1500 bytes.

For AFDX this structure is same with a difference, just after the end of the payload part and before the FCS, a Sequence Number is inserted which will be described later.

| 7 (bytes) | 1           | 6                      | 6                 | 2                | 45-1499      | 1  | 4           | 12  |

|-----------|-------------|------------------------|-------------------|------------------|--------------|----|-------------|-----|

| Preamble  | S<br>F<br>D | Destination<br>Address | Source<br>Address | T<br>y<br>p<br>e | AFDX Payload | SN | F<br>C<br>S | IFG |

Figure 3.3. AFDX Frame (Data Link Layer)

#### 3.3.1 Source Address

The specification specifies the MAC Source address as an Individual and Locally Administered address compliant with IEEE 802.3 protocol.

|            | Ethernet MAC controller Identification 48-bits |        |                   |        |             |        |                 |  |  |  |

|------------|------------------------------------------------|--------|-------------------|--------|-------------|--------|-----------------|--|--|--|

| Cons       | Constant field: 24-bits                        |        | Network_ID 8 bits |        | t_ID 8-bits | -      | Constant field: |  |  |  |

|            |                                                |        | 4-bits            | 3-bits | 5-bits      | 3-bits | 5-bits          |  |  |  |

| "0000 0010 | 0000 0000 0000 0000"                           | "0000" |                   |        |             |        | "00000"         |  |  |  |

Figure 3.4 MAC Source Address

Network ID and Equipment ID are assigned by the network and equipment designers.

Interface ID is 3 bits long but has two options;

'001' The Ethernet MAC controller is connected to the network A '010' The Ethernet MAC controller is connected to the network B

Network identification is used for redundancy and other bit combinations are not used.

The main difference from standard Ethernet is the ability of the end-user to configure the source MAC address according to his network by either jumper set or soft pre-configuration.

### **3.3.2 Destination Address**

The specification specifies the MAC Destination address as a Group and Locally Administered address compliant with IEEE 802.3, which carries the Virtual Link information in the last 16 bits.

| 48-bits                                |                         |

|----------------------------------------|-------------------------|

| Constant field                         | Virtual Link Identifier |

| 32-bits                                | 16-bits                 |

| xxxx xx11 xxxx xxxx xxxx xxxx xxxx xxx |                         |

Figure 3.5 MAC Destination Address

Each End System should get "constant field" and "Virtual Link Identifier" values from the system integrator. The values are not specified in ARINC 664. The constant field should be the same for each End System in any given AFDX network. The least significant bit of the first byte indicates the group address (always = 1).

In order to use the standard Ethernet frame, MAC group addresses should be changed to send frames from End System to End System (s).

The second to least significant bit of the first byte indicates the locally administered address (always = 1).

### 3.3.3 Type

2 byte type part of the frame is always 0x800, indicating IPv4.

### **3.3.4 Integrity Check**

In addition to the frame check sequence bytes of the standard Ethernet frame, frame sequence number (SN) is 1 byte long and should be located just before the MAC CRC field as illustrated in the Figure 3.3. Sequence number is used for integrity check.

The transmitter is in charge of putting a sequence number per VL basis in a range of 0 to 255. Transmitter initializes the sequence number of each Virtual Link as 0 after each End System reset and increments by one for each consecutive frame

of the same Virtual Link. When the value reaches 255, transmitter wraps-around the sequence number to 1 instead of 0.

When the frame is valid according to sequence number, integrity check function passes the frame to redundancy management. When the sequence number is faulty, it drops the invalid frame and informs network management. Frames with a sequence number 1 or 2 more than the sequence number of last received frame are accepted as valid frames. Increment with one or 2 must be conducted with the care of wrapping-around to 1 after 255.

"This function increases integrity robustness by, for example, eliminating stuck frames or single abnormal frames and reducing the impact of a babbling switch. Loss of one single frame is considered as a normal event due to a non-zero Bit Error Rate." [16]

### 3.3.5 Redundancy Management

As another difference from standard Ethernet, AFDX has a defined redundancy management. The interconnections of End Systems are established through two different redundant networks. This protects the loss of communication from single failure of a cable or switch.

Figure 3.6 Network Redundancy Concept

According to the specification [16] on a per VL basis, the End System should be able to receive:

- a redundant VL and deliver to the application one of the redundant data (RM active)

- a redundant VL and deliver to the application both redundant data (RM not active)

- a non redundant VL on either attachment and submit data from it to the application (in this case, RM can be active or not).

#### **3.3.6 Flow Regulation**

ARINC 664 defines fixed BAG for each Virtual Link. If application generates frames exceeding this BAG, in the data link layer, End System makes a regulation as one frame per gap basis. Flow regulation is only applicable to transmitter side End System.

#### **3.3.7 Flow Scheduling**

As several Virtual Links defined in an End System with a single physical output (except the redundant) there should be a scheduling control for each Virtual Link to direct the physical layer.

In a transmitting end system with multiple VLs, the Scheduler multiplexes the different flows coming from the Regulators.

The End System should regulate transmitted data on a per VL basis, since this Traffic Shaping Function (exact knowledge of flow characteristics) is the basis of the determinism analysis. On a per VL basis the traffic regulator or traffic shaping function should shape the flow to send no more than one packet in each interval of BAG milliseconds.

#### 3.3.8 Data Link Layer Overview

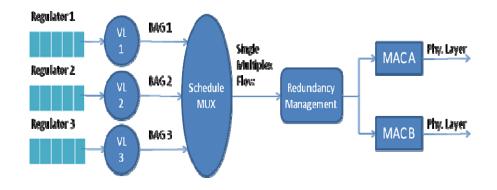

Figure 3.7 represents the data link layer operations in the transmitter point of view of AFDX End System.

- Regulator regulates frames coming from upper layer

- Regulated frames in Virtual Link are put inside the BAG.

- Schedule Multiplexer multiplexes the frames coming from several Virtual Links and conducts to Redundancy Management.

- Redundancy Management unit produces two instances of the same frame if not disabled.

- Each MAC put its source MAC address to the frame and passes to the physical layer.

Figure 3.7 AFDX Transmitter Data Link Layer Overview

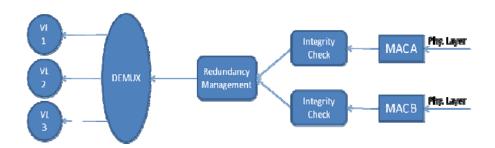

Figure 3.8 represents the data link layer operations in the transmitter point of view of AFDX End System.

- Received frames (according to MAC number, after CRC) are passed to Integrity Check.

- Integrity Check unit checks the Sequence Numbers and passes to Redundancy Management (RM) if not disabled. If RM is disabled, both frames pass to next step.

- Redundancy Management unit passes the first valid frame to demultiplexer.

• Demultiplexer delivers frames according to Virtual Links to the upper layer.

Figure 3.8 AFDX Receiver Data Link Layer Overview

#### **3.4 Network Layer**

From the transmission point of view; the IP network layer receives the packet from upper layer and determines whether it needs to be fragmented using the appropriate VL's Lmax value. The IP header is added, and IP checksum is calculated for each fragment.

From the reception point of view; the network layer is responsible for checking the IP checksum field and the packet reassembly, if necessary. The packet is passed to the upper (transport) layer.

AFDX frame with the bytes filled by network layer is given below;

| 7 (bytes) | 1           | 6                      | 6                 | 2                | 20        | 9-1479       | 0-16 | 1      | 4           | 12  |

|-----------|-------------|------------------------|-------------------|------------------|-----------|--------------|------|--------|-------------|-----|

| Preamble  | S<br>F<br>D | Destination<br>Address | Source<br>Address | T<br>y<br>p<br>e | IP Header | AFDX Payload | Pad  | S<br>N | F<br>C<br>S | IFG |

Figure 3.9 AFDX Frame (Network Layer)

### 3.4.1 IP Structure

AFDX has standard IPv4 structure except not including option bytes (0 or more) between IP payload and IP destination address.

| 4-bits  | 4-bits | 8-bits     | 16-bits         | 16-bits                    | 3-bits          | 13-bits            | 8-bits          | 8-bits   | 16-bits            | 32-bits      | 32-bits           | 1-1479        |

|---------|--------|------------|-----------------|----------------------------|-----------------|--------------------|-----------------|----------|--------------------|--------------|-------------------|---------------|

|         |        |            |                 |                            |                 |                    |                 |          |                    |              |                   | bytes         |

| Version | IHL    | Type<br>of | Total<br>length | Fragment<br>identification | Control<br>flag | Fragment<br>offset | Time<br>to live | Protocol | Header<br>checksum | IP<br>Source | IP<br>Destination | IP<br>Payload |

|         |        | service    | -               |                            | -               |                    |                 |          |                    | address      | address           |               |

#### Figure 3.10 IPv4 Structure

- Version: (IPv4 = 4)

- IHL: IP Header Length, number of 4 byte blocks (20 bytes=5) Type of service: Not used

- Total Length: Total Length of the IP frame (header + payload)

- Fragmentation Identification: An id to the fragmented group given by transmitter

- Control flag: Not used

- Fragmentation Offset: Position of the fragment relative to original payload

- Time to live: Number of hops

- Protocol: TCP uses 6, UDP uses 17, ICMP uses 1.

- Header Checksum: Checksum for the IP header

### **3.4.2 IP Source Address:**

The 32-bit IP source address should be a Class A and private Internet Unicast Address used to identify the transmitting partition associated with the End System.

| Class | s A | Private IP Address | Network ID |        | Equipment ID  |  | Partition ID |        |  |

|-------|-----|--------------------|------------|--------|---------------|--|--------------|--------|--|

| 1-b   | it  | 7-bits             | 8-1        | oits   | 8-bits        |  | 8-t          | oits   |  |

| "0"   |     | "0001010"          | "0000"     | 4-bits | 3-bits 5-bits |  | 3-bits       | 5-bits |  |

Figure 3.11 IP Source Address

### **3.4.3 IP Destination Address**

According to the specification, the IP destination address of the AFDX frame should be either the IP Unicast address to identify the target subscriber or an IP Multicast address compliant to the format shown in Figure below.

| Class D | IP Multicast<br>Identifier                       |    |  |  |  |  |  |  |

|---------|--------------------------------------------------|----|--|--|--|--|--|--|

| 4-bits  |                                                  | 28 |  |  |  |  |  |  |

| "1110"  | "0000 1110 0000" Virtual Link Identifier 16-bits |    |  |  |  |  |  |  |

# **3.5 Transport Layer**

The whole AFDX frame with the bytes filled by transport layer is given below;

| 7 (bytes) | 1           | 6                       | 6                 | 2    | 20           | 8             | 1-1471          | 0-16 | 1      | 4           | 12  |

|-----------|-------------|-------------------------|-------------------|------|--------------|---------------|-----------------|------|--------|-------------|-----|

| Preamble  | S<br>F<br>D | Destinatio<br>n Address | Source<br>Address | Туре | IP<br>Header | UDP<br>Header | AFDX<br>Payload | Pad  | S<br>N | F<br>C<br>S | IFG |

Figure 3.13 AFDX Frame (Transport Layer)

UDP Header is figured out as below;

| 16-bit      | 16-bit           | 16-bit     | 16-bit   |

|-------------|------------------|------------|----------|

| Source Port | Destination Port | UDP Length | UDP      |

| Number      | Number           |            | Checksum |

### Figure 3.14 UDP Header

Port number allocation is defined in ARINC Specification 664, Part 4: Internet Based Address Structures and Assigned Numbers [17] according to the tables below;

| Port range (decimal value) | Allocation range ARINC 664        | Allocation range AFDX       |

|----------------------------|-----------------------------------|-----------------------------|

| 0-1023                     | Administered by ICANN             | Administered by ICANN       |

|                            | "Well-known" port number          | "Well-known" port number    |

| 1 024 - 16 383             | Registered by ICANN               | Assigned by network manager |

|                            | A664 assigned                     |                             |

| 16 384 - 32 767            | Registered by ICANN               |                             |

|                            | System integrator Or User defined |                             |

| 32 768 - 65 535            | Registered by ICANN               |                             |

|                            | Recommended for temporary port    |                             |

|                            | assignment                        |                             |

### Figure 3.15 Allocation of SAP and AFDX Port Numbers

| Type of port  | Type of communication                      | Port range     | Commentaries                                                                                            |

|---------------|--------------------------------------------|----------------|---------------------------------------------------------------------------------------------------------|

| AFDX          | $AFDX \Leftrightarrow AFDX$                | 1 024 - 65 535 | Used for sampling and queuing                                                                           |

| Communication | AFDX ⇔ Compliant                           |                | communications                                                                                          |

| port          | network                                    |                |                                                                                                         |

| SAP           | AFDX ⇔ AFDX<br>AFDX ⇔Compliant<br>network  | 0 – 1023       | Used for standard communications<br>e.g Port 69 to open a TFTP, Data<br>loading (ARINC 615A), SNMP, etc |

|               | AFDX ⇔ AFDX<br>AFDX ⇔ Compliant<br>network | 1 024 – 65 535 | Used for bi-directional communication:<br>specific TFTP etc,                                            |

Figure 3.16 Port Allocation Range for IP Unicast or Multicast

As AFDX is a closed network, network architect is free to choose port numbers from full range; 0 to 65535. However specification encourages the use of Dynamic/Private range of numbers only. The reason for this is to avoid possible conflicts with adjacent networks when an AFDX network is integrated with other networks through a gateway. Port numbers shall be identical in a Virtual Link.

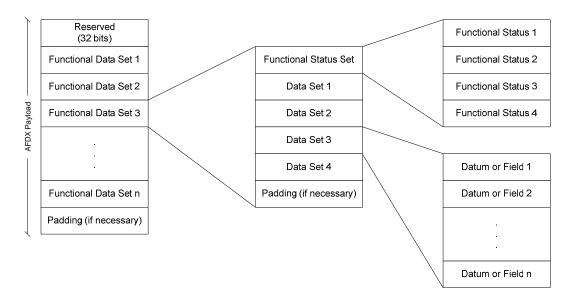

#### **3.6 Application Layer**