## DESIGN AND SYSTEMC IMPLEMENTATION OF A CRYPTO PROCESSOR FOR AES AND DES ALGORITHMS

# A THESIS SUBMITTED TO THE GRADUATE SCHOOL OF NATURAL AND APPLIED SCIENCES OF MIDDLE EAST TECHNICAL UNIVERSITY

BY

TUFAN EGEMEN

### IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE IN ELECTRICAL AND ELECTRONICS ENGINEERING

DECEMBER 2007

Approval of the thesis:

# DESIGN AND SYSTEMC IMPLEMENTATION OF A CRYPTO PROCESSOR FOR AES AND DES ALGORITHMS

submitted by Tufan Egemen in partial fulfillment of the requirements for the degree of Master of Science in Electrical and Electronics Engineering, Middle East Technical University by,

Prof. Dr. Canan Özgen Dean, Graduate School of Natural and Applied Sciences

Prof. Dr. İsmet Erkmen

Head of Department, Electrical and Electronics Engineering

Prof. Dr. Murat Aşkar Supervisor, Electrical and Electronics Engineering Dept., METU

### **Examining Committee Members:**

Prof. Dr. Rüyal Ergül \_\_\_\_\_\_ Electrical and Electronics Engineering Dept., METU

Prof. Dr. Murat Aşkar Electrical and Electronics Engineering Dept., METU

Prof. Dr. Hasan Güran Electrical and Electronics Engineering Dept., METU

Assoc. Prof. Dr. Melek Yücel Electrical and Electronics Engineering Dept., METU

Dr. Hamdi Murat Yıldırım Computer Tech. & Information Sys. Dept., Bilkent University

Date: 05.12.2007

I hereby declare that all information in this document has been obtained and presented in accordance with academic rules and ethical conduct. I also declare that, as required by these rules and conduct, I have fully cited and referenced all material and results that are not original to this work.

Name, Last name: Tufan EgemenSignature:

#### ABSTRACT

# DESIGN AND SYSTEMC IMPLEMENTATION OF A CRYPTO PROCESSOR FOR AES AND DES ALGORITHMS

Egemen, Tufan

M.Sc., Department of Electrical and Electronics Engineering

Supervisor: Prof. Dr. Murat Aşkar

December 2007, 129 pages

This thesis study presents design and SystemC implementation of a Crypto Processor for Advanced Encryption Standard (AES), Data Encryption Standard (DES) and Triple DES (TDES) algorithms. All of the algorithms are implemented in single architecture instead of using separate architectures for each of the algorithm. There is an Instruction Set Architecture (ISA) implemented for this Crypto Processor and the encryption and decryption of algorithms can be performed by using the proper instructions in the ISA. A permutation module is added to perform bit permutation operations, in addition to some basic structures of general purpose micro processors. Also the Arithmetic Logic Unit (ALU) structure is modified to process some crypto algorithm-specific operations.

The design of the proposed architecture is studied using SystemC. The architecture is implemented in modules by using the advantages of SystemC in modular structures. The simulation results from SystemC are analyzed to verify the proposed design. The instruction sets to implement the crypto algorithms are presented and a detailed hardware synthesis study has been carried out using the tool called SystemCrafter.

Keywords: AES, DES, TDES, Crypto Processor, Encryption, Bit Permutation

# AES VE DES ALGORİTMALARI İÇİN BİR KRİPTO İŞLEMCİSİ TASARIMI VE SYSTEMC İLE GERÇEKLENMESİ

Egemen, Tufan

Yüksek Lisans, Elektrik ve Elektronik Mühendisliği Bölümü Tez Yöneticisi: Prof. Dr. Murat Aşkar

Aralık 2007, 129 sayfa

Bu tezde, İleri Şifreleme Standardı (AES), Veri Şifreleme Standardı (DES) ve Üçlü Veri Şifreleme Standardı (TDES) algoritmaları için bir Kripto İşlemcisi tasarımı ve SystemC gerçekleştirimi sunulmaktadır. Her bir algoritma için ayrı bir yapı kullanmak yerine, üç algoritma da tek bir yapı içerisinde gerçekleştirilmiştir. Kripto işlemcisi için ayrı bir Komut Küme Yapısı (ISA) oluşturulmuştur; şifreleme ve çözme algoritma işlemleri bu Komut Küme Yapısındaki uygun komutların kullanımı ile yapılabilir. Genel amaçlı mikro işlemcilerdeki bazı temel yapılara ek olarak, bit permütasyon işlemlerini gerçekleştirmek üzere bir permütasyon modülü eklenmiştir. Bunun yanında Aritmetik Mantık Birimi (ALU) yapısı da kullanılan bazı kripto algoritmalarına has fonksiyonları işlemek için değiştirilmiştir.

Önerilen yapının tasarımı SystemC kullanılarak çalışılmıştır. Bu yapı SystemC'nin modüler yapılardaki avantajlarını kullanan modüller halinde gerçeklenmiştir. SystemC'den elde edilen simülasyon sonuçları, önerilen tasarımın doğruluğunu kontrol etmek için analiz edilmiştir. Kripto algoritmalarını gerçeklemek için Komut seti sunulmuş ve SystemCrafter adlı program kullanılarak detaylı bir donanım sentez çalışması yapılmıştır.

Keywords: AES, DES, TDES, Kripto İşlemci, Şifreleme, Bit Permütasyon

To My Family

#### ACKNOWLEDGEMENTS

I would like to express my special thanks to my supervisor Prof. Dr. Murat Aşkar for his guidance and great support in the development of this thesis work.

I would also like to thank my dear family for their support, understanding and encouragement during this thesis work.

# **TABLE OF CONTENTS**

| ABSTRACT                                    | iv   |

|---------------------------------------------|------|

| ÖZ                                          | vi   |

| ACKNOWLEDGEMENTS                            | ix   |

| TABLE OF CONTENTS                           | X    |

| LIST OF TABLES                              | xiii |

| LIST OF FIGURES                             | xiv  |

| CHAPTER                                     |      |

| 1. INTRODUCTION                             |      |

| 2. CHARACTERISTICS OF CRYPTO ALGORITHMS     |      |

| 2.1 Introduction                            |      |

| 2.2 Types of Cryptographic Algorithms       |      |

| 2.2.1 Symmetric-key Algorithms              |      |

| 2.2.1.1 Block Ciphers                       | 7    |

| 2.2.1.2 Stream Ciphers                      | 7    |

| 2.2.2 Asymmetric (Public-Key) Algorithms    |      |

| 2.2.3 Hash Algorithms                       | 9    |

| 2.3 AES Algorithm                           | 9    |

| 2.3.1 Galois Field (2 <sup>8</sup> )        |      |

| 2.3.1.1 Addition and Subtraction            |      |

| 2.3.1.2 Multiplication                      |      |

| 2.3.2 Encryption Process of AES             |      |

| 2.3.2.1 The SubBytes Transformation         |      |

| 2.3.2.2 The ShiftRows Transformation        |      |

| 2.3.2.3 MixColumns Transformation           |      |

| 2.3.2.4 AddRoundKey Transformation          |      |

| 2.3.3 Decryption Process of AES             |      |

| 2.3.4 Key Expansion and Round Key Selection |      |

| 2.4 DES Algorithm                          |     |

|--------------------------------------------|-----|

| 2.4.1 DES Rounds                           |     |

| 2.4.1.1 Initial Permutation                |     |

| 2.4.1.2 Cipher Function                    |     |

| 2.4.1.3 Inverse Initial Permutation        |     |

| 2.4.2 Key Expansion Part                   |     |

| 2.5 TDES Algorithm                         |     |

| 3. CRYPTO PROCESSOR ARCHITECTURES          |     |

| 3.1 Introduction                           |     |

| 3.2 Different Processor Implementations    |     |

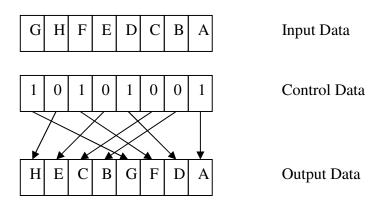

| 3.3 Bit Permutation Instructions           | 57  |

| 3.3.1 GRP instruction                      |     |

| 3.3.2 PPERM3R and PPERM instructions       | 59  |

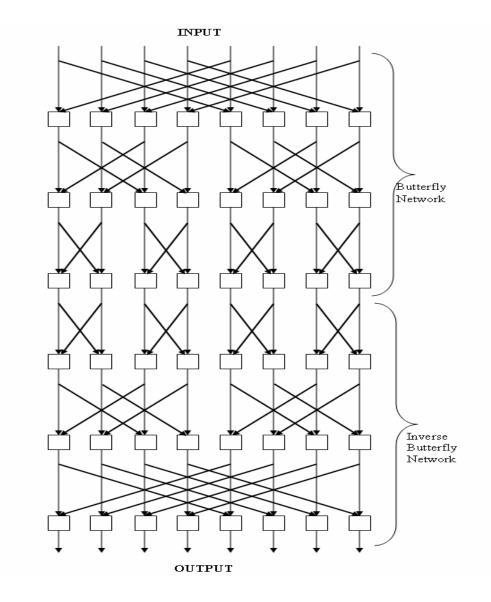

| 3.3.3 CROSS instruction                    | 60  |

| 3.3.4 OMFLIP instruction                   |     |

| 3.3.5 SWPERM and SIEVE instruction         |     |

| 4. IMPLEMENTATION OF THE CRYPTO PROCESSOR  | 64  |

| 4.1 Introduction                           | 64  |

| 4.2 Architecture of the Crypto Processor   | 64  |

| 4.3 Control Unit Module                    | 66  |

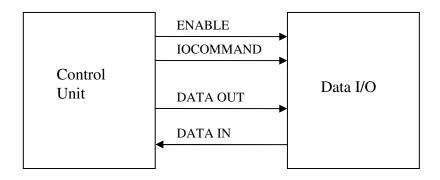

| 4.4 Data Input/Output Module               | 67  |

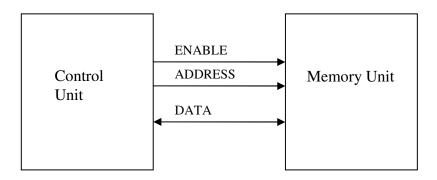

| 4.5 Memory Module                          |     |

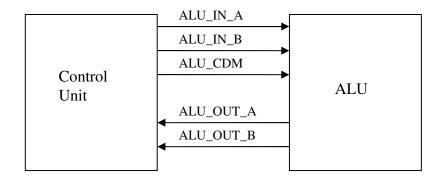

| 4.6 Arithmetic Logic Unit (ALU) Module     | 69  |

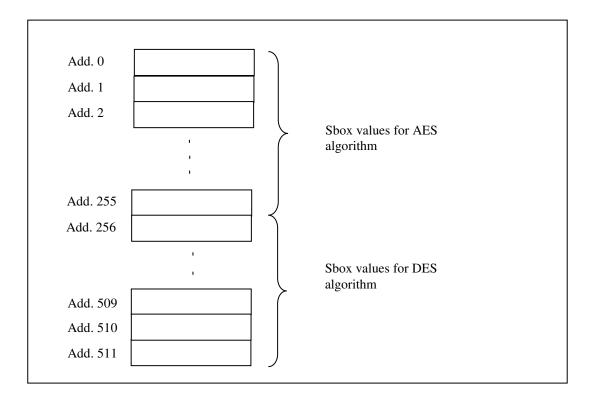

| 4.6.1 SBox Memory Unit                     | 72  |

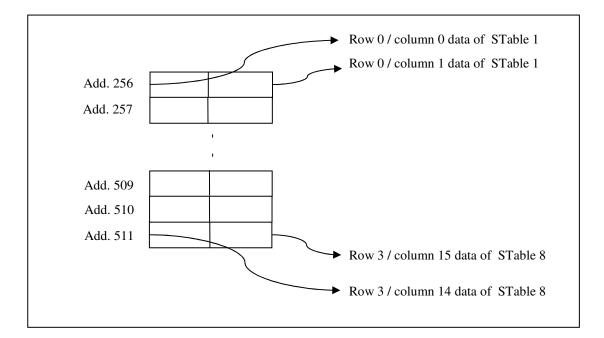

| 4.7 Permutation Module                     | 74  |

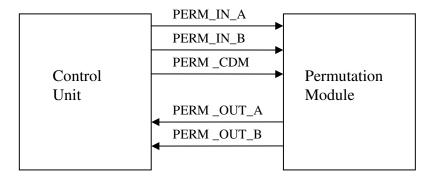

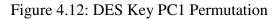

| 4.8 Instruction Set Architecture           |     |

| 4.9 Simulations and Implementation Results |     |

| 5. CONCLUSION                              |     |

| REFERENCES                                 |     |

| APPENDICES                                 |     |

| Appendix A: SBox Tables                    | 119 |

| Appendix B: Sample Programming Codes       |     |

# LIST OF TABLES

# TABLES

| Table 2.1: Round numbers $(N_r)$ for different data and key lengths         | 12  |

|-----------------------------------------------------------------------------|-----|

| Table 2.2: The Shift Row operation offset values for different data lengths | 18  |

| Table 2.3: Initial Permutation Table                                        |     |

| Table 2.4: E Bit Selection Table                                            | 31  |

| Table 2.5: SBox S1 Table                                                    | 32  |

| Table 2.6: P Permutation Table                                              | 32  |

| Table 2.7: Inverse Initial Permutation Table                                | 33  |

| Table 2.8: PC-1 Permutation Table                                           | 34  |

| Table 2.9: PC-2 Permutation Table                                           | 35  |

| Table 2.10: Left Shift Offset Value Table                                   | 35  |

| Table 3.1: Cryptonite architecture results                                  | 42  |

| Table 3.2: Estimated results of CryptoManiac architecture                   | 45  |

| Table 4.1: ALU Commands                                                     | 71  |

| Table 4.2: Slices values for some crypto specific blocks                    | 106 |

| Table 4.3: Approximately Slices values for SBox and Permutation blocks      | 107 |

| Table 4.4: Machine Cycles for performed Crypto Algorithms                   | 107 |

| Table 4.5: Comparison between Machine Cycles of Programmable Crypto         |     |

| Processors                                                                  | 107 |

| A.1 DES SBox S1                                                             | 119 |

| A.2 DES SBox S2                                                             | 119 |

| A.3 DES SBox S3                                                             | 120 |

| A.4 DES SBox S4                                                             | 120 |

| A.5 DES SBox S5                                                             | 121 |

| A.6 DES SBox S6                                                             | 121 |

| A.7 DES SBox S7                                                             | 122 |

| A.8 DES SBox S8       |     |

|-----------------------|-----|

| A.9 AES SBox          | 123 |

| A.10 AES Inverse SBox |     |

# LIST OF FIGURES

# FIGURES

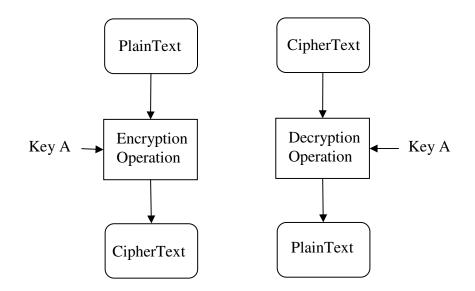

| Figure 2.1: Symmetric Key Algorithms                     | 6    |

|----------------------------------------------------------|------|

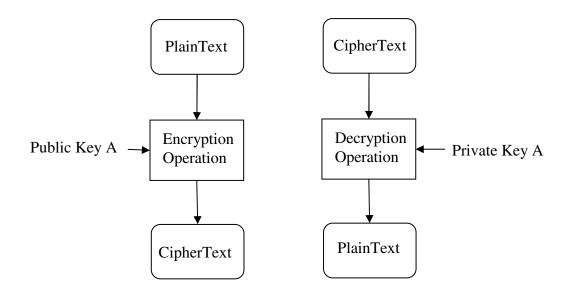

| Figure 2.2: Asymmetric Key Algorithms                    | 8    |

| Figure 2.3: Data State (for 128-bit data $N_b = 4$ )     | .11  |

| Figure 2.4: Key State (for 192-bit key data $N_k = 6$ )  | .11  |

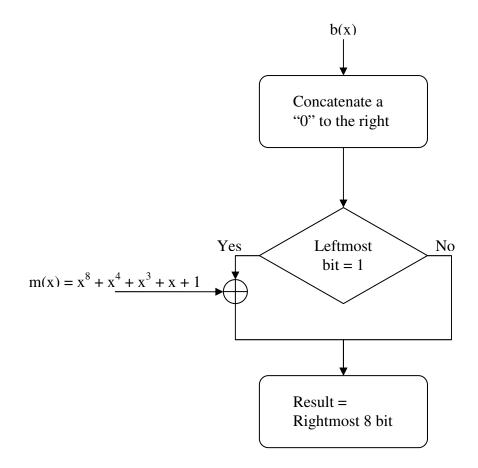

| Figure 2.5: Multiplication of b(x) and x AES Encryption  | . 14 |

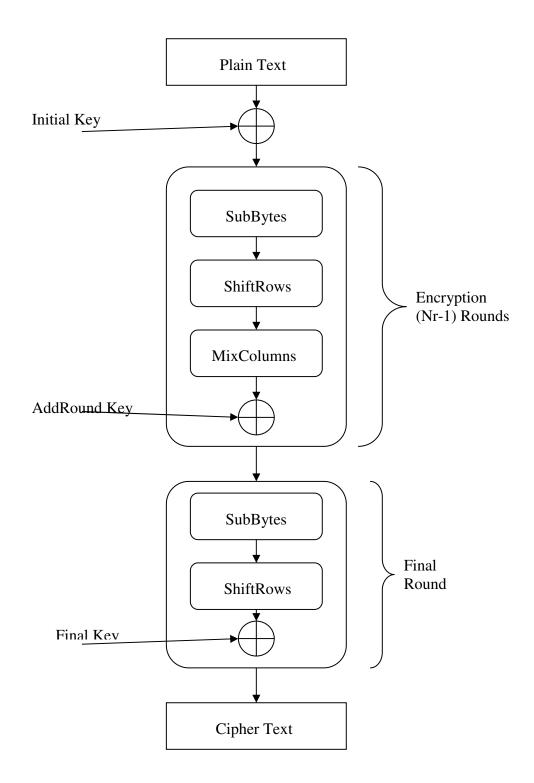

| Figure 2.6: AES Encryption                               | . 16 |

| Figure 2.7: Affine Transformation                        | . 17 |

| Figure 2.8: Byte Sub transformation on States            | . 18 |

| Figure 2.9: The multiplication of State Column and c(x)  | . 19 |

| Figure 2.10: Mix Column operation                        | . 20 |

| Figure 2.11: Round Key Addition                          | . 20 |

| Figure 2.12: AES Decryption                              | . 22 |

| Figure 2.13: The multiplication of State Column and d(x) | . 23 |

| Figure 2.14: Key Expansion for 128 and 192 bits          | . 25 |

| Figure 2.15: Key Expansion for 256 bits                  | . 26 |

| Figure 2.16: Round Key Selection                         | . 27 |

| Figure 2.17: DES Algorithm                               | . 29 |

| Figure 2.18: DES Cipher Function                         | . 30 |

| Figure 2.19: DES Key Expansion                           | . 36 |

| Figure 2.20: TDES Encryption Operation                   | . 37 |

| Figure 2.21: TDES Decryption Operation                   | . 37 |

| Figure 3.1: Cryptonite architecture                      | . 40 |

| Figure 3.2: Vectored Memory Access                       | .41  |

| Figure 3.3: Schematic of CryptoManiac Architecture       | . 43 |

| Figure 3.4: Schematic of a single functional unit        | . 44 |

| Figure 3.5: SBox and Mix Column computation using BRAM                | 46    |

|-----------------------------------------------------------------------|-------|

| Figure 3.6: The switch structure                                      | 49    |

| Figure 3.7: The architecture of AES Core                              | 50    |

| Figure 3.8: Block diagram of the AESTHETIC processor                  | 51    |

| Figure 3.9: Block diagram of the implemented architecture             | 52    |

| Figure 3.10: Block diagram of the one DES circuit                     | 54    |

| Figure 3.11: Pipelined cell structure                                 | 55    |

| Figure 3.12: The third proposed architecture                          | 56    |

| Figure 3.13 : An 8-bit GRP operation                                  | 59    |

| Figure 3.14: An 8-bit Benes network for CROSS instruction             | 61    |

| Figure 3.15: SWPERM instruction                                       | 63    |

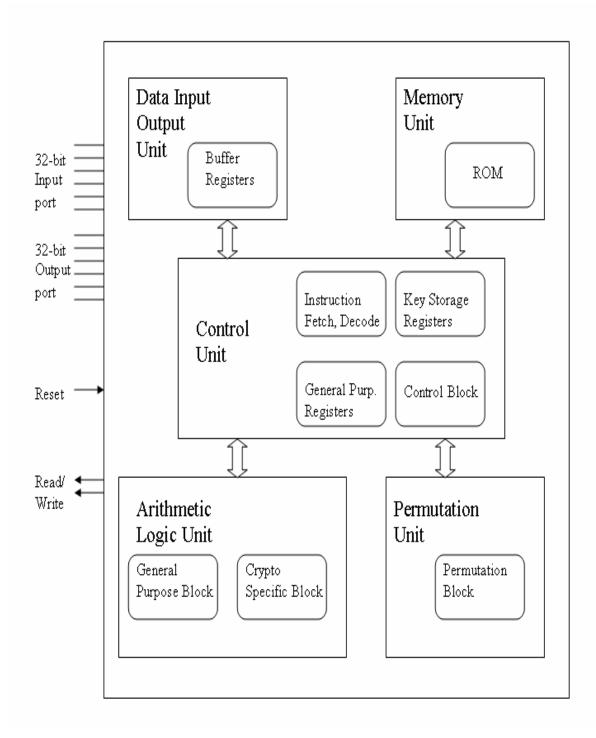

| Figure 4.1: The main architecture of the implemented Crypto Processor | 65    |

| Figure 4.2: Control Unit – Data Input/Output Module Interface         | 68    |

| Figure 4.3: Control Unit – Memory Module Interface                    | 68    |

| Figure 4.4: Control Unit – ALU Interface                              | 69    |

| Figure 4.5: SBox memory unit                                          | 72    |

| Figure 4.6: SBox memory unit organization for DES                     | 74    |

| Figure 4.7: Control Unit – Permutation Module Interface               | 75    |

| Figure 4.8: DES Initial Permutation                                   | 76    |

| Figure 4.9: DES Inverse Initial Permutation                           | 77    |

| Figure 4.10: DES E Table Permutation                                  | 78    |

| Figure 4.11: DES Cipher (P) Permutation                               | 80    |

| Figure 4.12: DES Key PC1 Permutation                                  | 81    |

| Figure 4.13: DES Key PC2 Permutation                                  | 82    |

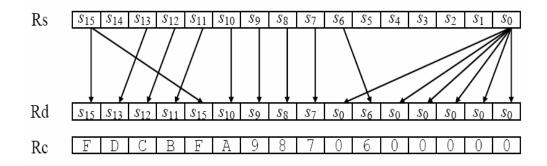

| Figure 4.14: Register State values before shift operation             | 85    |

| Figure 4.15: Register State values after shift operation              | 86    |

| Figure 4.16: BMAP function                                            | 95    |

| Figure 4.17: DES Encryption Console Output                            | . 100 |

| Figure 4.18: DES Decryption Console Output                            | . 101 |

| Figure 4.19: TDES Encryption Console Output                           | . 101 |

| Figure 4.20: TDES Decryption Console Output                           | . 102 |

| Figure 4.21: AES-128 Encryption Console Output | 102 |

|------------------------------------------------|-----|

| Figure 4.22: AES-128 Decryption Console Output | 103 |

| Figure 4.23: AES-192 Encryption Console Output | 103 |

| Figure 4.24: AES-192 Decryption Console Output | 104 |

| Figure 4.25: AES-256 Encryption Console Output | 104 |

| Figure 4.26: AES-256 Decryption Console Output | 105 |

| Figure 4.27: Instruction read                  | 108 |

| Figure 4.28: Instruction <i>exk0</i>           | 108 |

| Figure 4.29: Instruction <i>rord</i>           | 109 |

| Figure 4.30: Instruction <i>cipp</i>           | 109 |

| Figure 4.31: Instruction <i>mix</i>            | 110 |

| Figure 4.32: Instruction <i>sbox</i>           | 110 |

| Figure 4.33: Instruction <i>shift 128</i>      | 111 |

| Figure 4.34: Instruction <i>rorb</i>           | 111 |

|                                                |     |

#### **CHAPTER 1**

#### **INTRODUCTION**

Cryptography is the science of encryption and decryption of data. With the help of cryptography, people aim to hide some important information as secret. Generally, cryptography is used for the privacy of information, while it facilitates communication between two points. This requirement can be realized by encrypting the plaintext data with a key to a ciphertext, and then decrypting the ciphertext back to its original form on the other side of the communication channel. Nowadays authentication, digital signatures, and secure computation are other important application areas of cryptography.

The most commonly used crypto algorithms are the Advanced Encryption Algorithm (AES) [1] - [3], which is the standard announced for block ciphers, the previous Data Encryption Standard (DES) [4], and Triple Data Encryption Algorithm (TDEA), also known as Triple DES (TDES) [4] algorithm.

The designs for crypto systems are generally implemented using a specific algorithm and using special hardware architecture which is dedicated to that algorithm. With such architecture, it is much easier to configure the hardware according to the desired specification; hence the crypto algorithm process is much faster.

There are several strategies to make the design of architecture specific to the algorithm. The area and the throughput of the chip are the main parameters while determining the structure of the design according to the desired specification.

To maximize the throughput of the selected algorithm when there is no area constraint in the design, all the iterated rounds of the algorithm can be implemented in the chip layout. For example as given in [9] [10], for AES, the throughput can be increased with inner-round and outer-round pipeline structure. The data path of the structure is also an important parameter in the algorithm-specific design. The data path can be set to the input plaintext length for fast applications, or it can be set to smaller data lengths for area limited operations. There are many categories in the market, which have different data path characteristics. In [15], the data path and bit length discussions are presented.

Another parameter for the algorithm-specific designs is the key schedule part. The key schedule can be arranged as on-the-fly key generation method, which produces the keys in each clock, simultaneously with the round process. Therefore, it is not necessary to use internal registers for the round keys, as explained for AES in [6] [13]. The second key schedule method produces all the round keys before encryption or decryption process and then performs the algorithm's round operations. This method requires storage registers for the round keys.

Basic crypto operations of algorithms can be executed on using general purpose micro processors. But in general purpose processors, there are no special instructions, or any special block to perform cryptographic operations, making it difficult to process a crypto algorithm in a general purpose processor. Besides general purpose processors, there are crypto processors, which are designed for crypto operations and have crypto specific blocks. Most of these crypto processors are designed to process only a single algorithm with configurable parameters. For example such a structure is discussed in [11] [14] for AES algorithm. Some of the crypto processors can perform several algorithms in a single design. Most of the time there is one disjoint block for each included crypto algorithm. These kinds of structures are not area efficient and they are used mainly for high throughput applications.

There are programmable crypto processors, which are able to process more than one crypto algorithm in a single architecture, such as the joint implementations of AES, DES and TDEA as presented in [7] [8]. The most important property of these kinds of processors is their programmable architectures. The processors can be programmed according to the applied crypto algorithm.

The objective of this work is the implementation of a programmable Crypto processor architecture using the SystemC tool. The Advanced Encryption Algorithm (AES), which is the standard announced for block ciphers, the previous Data Encryption Standard (DES), and Triple Data Encryption Algorithm (TDEA), also known as Triple DES (TDES) algorithms are chosen for the implementation of the architecture. The Crypto architecture is implemented in the SystemC [24] environment. SystemC is based on C++, with some additional class libraries to model the hardware based features like clock, signals, logic and delay elements. SystemC allows modeling from the system level to Register Transfer Level (RTL). This modeling structure provides higher productivity than other modeling environments due to its easier and faster implementation. In the SystemC approach the design is implemented in modular structures. With this property of SystemC, the design can be modified to add new hardware blocks without changing the general structure.

In this thesis, instead of implementing two different blocks for each algorithm, the architecture is implemented as a common unit, which can perform operations of the chosen crypto algorithms. The implemented architecture is fully programmable and all the algorithms' operations are performed according to the instructions. The architecture is similar to general microcontroller's structure, but there are some differences for crypto operations. The internal structure of the implemented architecture is based on 32-bit data length and all crypto operations are performed in 32-bit arithmetic.

The operations are controlled by a Control Unit module and performed in Arithmetic Logic Unit (ALU) module or Permutation module according to Control Unit signals. The main operations are performed in the ALU. ALU is responsible for performing the crypto specific instructions as well as general purpose instructions. There is an internal memory block implemented inside the ALU for Substitution Table (SBox) operations. The SBox values for both of the AES and DES algorithms are stored in this memory unit.

Besides ALU, which performs the logic and arithmetic operations, a Permutation module is added into the design. In general applications, the bit permutation operation is implemented as a memory based structure or as a hardware routing structure. But in this implemented architecture, all of the bit permutation operations are performed in a single permutation module block. The bit permutation operations are used in Data Encryption Standard (DES) algorithm; therefore, the main purpose of this permutation module is performing DES permutations. But it can also perform other bit permutations depending on the applications.

The characteristics of Crypto Algorithms are described in Chapter 2. The types of the crypto algorithms are described in the first section of this chapter. Then the transformations of AES and DES algorithms and their basic process structures are explained in the following two sections. In Chapter 3, different implementations of Crypto processors in literature are discussed. In the first part of this chapter, the structures dedicates to a single algorithm and in the second part, crypto processors, which are capable of performing several algorithms, are discussed. The implemented architecture and its module structures are given in Chapter 4, where each module in the architecture is explained in detail. Also, the implemented Instruction Set Architecture and the instruction descriptions are given in this chapter. Finally, a conclusion for this work and proposed future works are presented in Chapter 5.

#### **CHAPTER 2**

### **CHARACTERISTICS OF CRYPTO ALGORITHMS**

#### **2.1 Introduction**

This chapter explains the general description of the cipher algorithms and detailed structure of Advanced Encryption Standard and Data Encryption Standard algorithms. In the first section, the types and properties of the cryptographic algorithms are described. The AES algorithm, the DES algorithm and their operations are discussed in the second and third sections, respectively.

### 2.2 Types of Cryptographic Algorithms

Cryptography becomes a more important parameter with today's increasing security issues on communication area. There are lots of activities over communication networks of different applications and the security of the data in these applications are provided by using different cryptographic algorithms. These algorithms can be divided into three groups, as symmetric-key algorithms, public-key algorithms and hash algorithms.

#### 2.2.1 Symmetric-key Algorithms

The encryption and decryption processes in the symmetric-key algorithms are performed with one key. There is only one secret key between the two sides of communication. The plaintext is encrypted by using the secret key and transmitted. Then this ciphered data is decrypted by using the same secret key, which is used in the encryption part [5] [20]. This communication structure can be seen in Figure 2.1.

Figure 2.1: Symmetric Key Algorithms

The power of the symmetric algorithm is directly dependent to the key length. Because of the decryption process can be performed with trying all possible key combinations. Therefore the resistance of the symmetric algorithm against possible key trials is much higher with the increasing key length.

Symmetric algorithms can be divided into two groups as stream ciphers and block ciphers. The difference between these two groups is, the block ciphers use always the same sized data chunks in the encryption or decryption operations, but stream ciphers use different sized data in encryption or decryption operation.

#### 2.2.1.1 Block Ciphers

Encryption and decryption operations are performed over blocks of data in the Block ciphers. Each block is used sequentially in the cipher operations. More clearly, a set of Boolean operations are performed on a definite length of bit vectors in a block cipher [1] [5].

There are normally two main techniques used in the Block ciphers. These are confusion and diffusion techniques. The aim of the confusion is making the output of the encryption as much as different from the input plaintext. Therefore the relation between input and output of the encryption will be more unpredictable. The substitution operation is mainly used in confusion technique.

On the other hand the diffusion technique is used to distribute the redundancy of the plaintext as much as possible into the cipher text. The main operation used for diffusion technique is permutation operation.

#### 2.2.1.2 Stream Ciphers

Unlike block ciphers, stream ciphers operate on data context, with different bit lengths. Encryption or decryption is processed over these different sized data [5].

There are keys for each stream, which are generated by a key stream generator. The lengths of the key data is depends on the length of the data stream. Therefore the sequential key stream's length may show differences. In the encryption these keys and the plain data streams are XORed to get the ciphered data. Also in the decryption the same operation is performed. The same key stream data is XORed with the ciphered data, in this case to get the plaintext back.

In the stream cipher operation, the power of the operation is directly related to the key stream generator performance.

#### 2.2.2 Asymmetric (Public-Key) Algorithms

Unlike symmetric algorithms, the asymmetric algorithms use different keys for encryption and decryption algorithms. There are two types of keys in the asymmetric algorithms. One of them is called private key and this key is known only by its owner. The other key type is called public key and this is known by all users in the communication [5].

In the asymmetric algorithms the relation between encryption side and decryption side is given in Figure 2.2. The encryption operation is processed by using the public key. Unlike encryption, decryption operation is processed only with the private key. The important point in the decryption is the private key's owner issue. The private key should belong to the unit, which encrypted data with its public key, for a correct decryption.

Figure 2.2: Asymmetric Key Algorithms

#### 2.2.3 Hash Algorithms

Hash algorithms are a kind of pseudo random number generators in cryptography. There is no any formal description of Hash algorithms, but there are some general properties for it.

- For a given input message, there should be not any second input message, which gives the same hash output as the first input message. This property is known as collision resistance.

- For a given hash algorithm output, it should be hard to compute the input message. This property depends on the one-way function characteristic of the hash algorithms.

In the Hash algorithms, the input plaintext length is not fixed and can have a variety of lengths. But the output ciphered data of the Hash algorithm has a fixed data length. This property is achieved generally by processing the input data in equal-sized blocks and performed a one-way compression on the blocks. Therefore a very small change at the input side can create a very big change at the output side [1].

#### 2.3 AES Algorithm

The Advanced Encryption Standard (AES) is a new Federal Information Processing Standard (FIPS) which was announced after an encryption algorithm standard competition by National Institute of Standards and Technology [5]. AES is also known as Rijndael [1] [2], but there are some small differences between AES and original Rijndael. The input data length is fixed to 128-bit in AES, while it can be 128, 192 or 256 bits in Rijndael.

The AES algorithm is a symmetric key algorithm and operates the encryption and decryption processes in blocks. The input data and key data of AES can be considered as one-dimensional array [1]. Each element of the array consists of 8-bit data. The one dimensional array of the incoming plaintext data (P) can be denoted by

$$P = p_0 p_1 p_2 p_3 \cdots p_{4*Nb-1},$$

where  $p_0$  is the first byte and  $p_{4*Nb-1}$  is the last byte of plaintext. The incoming plaintext data is then mapped into a two dimensional matrix, which is called State [1]. All the AES operations are performed on the State matrix. The State matrix has a variable column number for different data and key lengths, with four rows. The column numbers are denoted by N<sub>b</sub> for data state matrix and defined as;

$N_b$  = input data length / 32.

The elements of the two dimensional State matrix can be defined as;

$$a_{i,j} = p_{i+4j}, 0 \le i < 4, 0 \le j < N_b,$$

where  $a_{i,j}$  denotes the byte in row i and column j.

Similarly, the input key is also mapped into a two dimensional matrix. The row number of key matrix is also four like in state matrix, and the column number is denoted by  $N_k$ , which is defined as below;

$$N_k$$

= input key length / 32.

If we denote the one dimensional array of the key data (Z) by

$$\mathbf{Z} = \mathbf{z}_0 \mathbf{z}_1 \mathbf{z}_2 \mathbf{z}_3 \cdots \mathbf{z}_{4*Nk-1},$$

where  $z_0$  is the first byte and  $z_{4*Nk-1}$  is the last byte of key, then the two dimensional matrix elements can be defined as below;

$$k_{i,j} = z_{i+4j}, \, 0 \le i < 4, \, 0 \le j < N_k.$$

The input key bytes are mapped onto key state matrix in the order  $k_{0,0}$ ,  $k_{1,0}$ ,  $k_{2,0}$ ,  $k_{3,0}$ ,  $k_{0,1}$ ,  $k_{1,1}$ ,  $k_{2,1}$ ,... [1]. The Data State matrix for 128-bit data is shown in Figure 2.3 and the Key State matrix for 192-bit key is shown in Figure2.4. The N<sub>b</sub> value is 4 for AES, because the data input is fixed at 128-bit. N<sub>k</sub> can have the values of 4, 6 and 8 for 128-bit, 192-bit and 256-bit, respectively.

| a <sub>0,0</sub> | a <sub>0,1</sub> | a <sub>0,2</sub> | a <sub>0,3</sub> |

|------------------|------------------|------------------|------------------|

| a <sub>1,0</sub> | a <sub>1,1</sub> | a <sub>1,2</sub> | a <sub>1,3</sub> |

| a <sub>2,0</sub> | a <sub>2,1</sub> | a <sub>2,2</sub> | a <sub>2,3</sub> |

| a <sub>3,0</sub> | a <sub>3,1</sub> | a <sub>3,2</sub> | a <sub>3,3</sub> |

Figure 2.3: Data State (for 128-bit data  $N_b = 4$ )

| k <sub>0,0</sub> | k <sub>0,1</sub> | k <sub>0,2</sub> | k <sub>0,3</sub> | k <sub>0,4</sub> | k <sub>0,5</sub> |

|------------------|------------------|------------------|------------------|------------------|------------------|

| k <sub>1,0</sub> | k <sub>1,1</sub> | k <sub>1,2</sub> | k <sub>1,3</sub> | k <sub>1,4</sub> | k <sub>1,5</sub> |

| k <sub>2,0</sub> | k <sub>2,1</sub> | k <sub>2,2</sub> | k <sub>2,3</sub> | k <sub>2,4</sub> | k <sub>2,5</sub> |

| k <sub>3,0</sub> | k <sub>3,1</sub> | k <sub>3,2</sub> | k <sub>3,3</sub> | k <sub>3,4</sub> | k <sub>3,5</sub> |

Figure 2.4: Key State (for 192-bit key data  $N_k = 6$ )

The rounds have sequential operations to perform encryption or decryption. The round numbers  $(N_r)$  are also depending on the  $N_b$  and  $N_k$  values. The Table 2.1 gives the round numbers for different data and key lengths for Rijndael.

| Nr                 | $N_b = 4$ | $N_b = 6$ | N <sub>b</sub> = 8 |

|--------------------|-----------|-----------|--------------------|

| $N_k = 4$          | 10        | 12        | 14                 |

| $N_k = 6$          | 12        | 12        | 14                 |

| N <sub>k</sub> = 8 | 14        | 14        | 14                 |

Table 2.1: Round numbers (Nr) for different data and key lengths

In the AES algorithm, most of the operations are based on mathematical operations in Galois Field  $(2^8)$ . Therefore, a brief explanation of the Galois Field  $(2^8)$  is discussed in the next part.

# **2.3.1 Galois Field** $(2^8)$

The byte level operations in the AES algorithm are defined in the finite field (or Galois Field) GF  $(2^8)$  [1]. There are only a finite number of elements in a finite field and this number of elements is given as  $p^n$ , where p is a prime number and n is a positive integer.

The Galois Field  $(2^8)$  is an extension field of Galois Field (2) and it is represented by the coefficients of  $\{0, 1\}$ . A finite field can be represented as polynomials of degree smaller than the degree of the irreducible, reduction polynomial. A byte polynomial representation is given below;

$$b(x) = b_7 x^7 + b_6 x^6 + b_5 x^5 + b_4 x^4 + b_3 x^3 + b_2 x^2 + b_1 x^1 + b_0 x^0.$$

The arithmetic operations in the finite field are different from standard arithmetic and they will be explained in the following part. When the elements are represented as polynomials, then the arithmetic operations are performed modulo m. m is an irreducible polynomial over the Galois field with the same degree. For AES algorithm this irreducible polynomial is given by;

$$m(x) = x^8 + x^4 + x^3 + x + 1$$

#### 2.3.1.1 Addition and Subtraction

The addition and subtraction of the polynomials in a finite field is a simple EXOR operation and same for both of addition and subtraction.

#### 2.3.1.2 Multiplication

In the finite field the multiplication operation can be expressed as multiplication of the polynomials with using an irreducible reducing polynomial for a modulus operation [1]. The irreducible polynomial for AES is given in m(x). The multiplication operation between a polynomial b(x) and "x" can be expressed in Figure 2.5.

First of all the polynomial is shifted to the left with a concatenated "0" on the leftmost bit. If the leftmost bit of the b(x) is "1", an EXOR operation is performed between the polynomial b(x) and the irreducible polynomial m(x), else EXOR operation is not performed. The result polynomial is the rightmost eight bits. The multiplication with "x" can be assumed as a fundamental operation in multiplication. Because of other polynomial multiplications can be considered as a sequence of multiplication with "x" [6].

Figure 2.5: Multiplication of b(x) and x

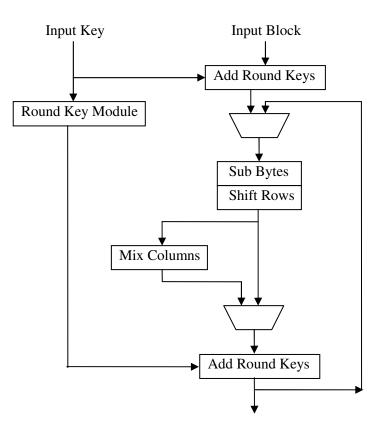

#### 2.3.2 Encryption Process of AES

The encryption process performed the inner state transformations over the plaintext data and as a result of these transformations the ciphertext data is given as output. The encryption diagram of the AES is given in Figure 2.6. There are four different transformations operation in the encryption process of AES algorithm. These are;

- SubBytes operation

- ShiftRows operation

- MixColumns operation

- AddRoundKey operation

The encryption process starts with an EXOR operation of plaintext and initial key data. Then the main iterated block, which consist of SubBytes, ShiftRows, MixColumns and AddRoundKey operations respectively. This main block repeats itself  $N_r - 1$  times. In the final round only MixColumns operation is missing as a difference of main iterative block. The output of the final round is called as ciphertext data.

Figure 2.6: AES Encryption

# 2.3.2.1 The SubBytes Transformation

In the SubBytes operation each State byte is replaced with the related substitution table element, which is determined according the State byte's value. The Substitution operation is the only nonlinear operation and the table is invertible.

In the construction of the SBox table, there are two operations. Firstly, the multiplicative inverse of the State byte is calculated in GF  $(2^8)$ . Then an affine transformation is applied, which is given in below Figure.

|                | I | _ |   |   |   |   |   |   |   | 1 | <u> </u>              | 1 | <u> </u>  |

|----------------|---|---|---|---|---|---|---|---|---|---|-----------------------|---|-----------|

| bo             |   | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 |   | ao                    |   | 1         |

| b <sub>1</sub> |   | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 |   | a <sub>1</sub>        |   | 1         |

| b <sub>2</sub> |   | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 |   | <b>a</b> <sub>2</sub> |   | 0         |

| b <sub>3</sub> | = | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 1 |   | a <sub>3</sub>        | + | 0         |

| b <sub>4</sub> |   | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 |   | $a_4$                 | • | 0         |

| b <sub>5</sub> |   | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 0 |   | $a_5$                 |   | 1         |

| b <sub>6</sub> |   | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 0 |   | a <sub>6</sub>        |   | 1         |

| b <sub>7</sub> |   | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 |   | a <sub>7</sub>        |   | 0         |

|                |   |   |   |   |   |   |   |   |   | 1 | L _                   |   | $\square$ |

Figure 2.7: Affine Transformation

|                  |                  |                  |                  |                  |                  | S-box |     |                  |                  |                  |                  |                  |

|------------------|------------------|------------------|------------------|------------------|------------------|-------|-----|------------------|------------------|------------------|------------------|------------------|

| a <sub>0,0</sub> | a <sub>0,1</sub> | a <sub>0,2</sub> | a <u>,</u> 3     | a <sub>0,4</sub> | a <sub>0,5</sub> | b     | 0,0 | b <sub>0,1</sub> | $b_{0,2}$        | b <sub>0,3</sub> | b <sub>0,4</sub> | b <sub>0,5</sub> |

| a <sub>1,0</sub> | a <sub>1,1</sub> | a <sub>i,j</sub> | 1,3              | a <sub>1,4</sub> | a <sub>1,5</sub> | b     | 1,0 | b <sub>1,1</sub> | b <sub>i,j</sub> | 1,3              | b <sub>1,4</sub> | b <sub>1,5</sub> |

| a <sub>2,0</sub> | a <sub>2,1</sub> | a <sub>2,2</sub> | a <sub>2,3</sub> | a <sub>2,4</sub> | a <sub>2,5</sub> | b     | 2,0 | b <sub>2,1</sub> | b <sub>2,2</sub> | b <sub>2,3</sub> | b <sub>2,4</sub> | b <sub>2,5</sub> |

| a <sub>3,0</sub> | a <sub>3,1</sub> | a <sub>3,2</sub> | a <sub>3,3</sub> | a <sub>3,4</sub> | a <sub>3,5</sub> | b     | 3,0 | b <sub>3,1</sub> | b <sub>3,2</sub> | b <sub>3,3</sub> | b <sub>3,4</sub> | b <sub>3,5</sub> |

Figure 2.8: SubBytes Transformation on State

# 2.3.2.2 The ShiftRows Transformation

In this operation the rows of the State matrix are shifted to the right cyclically. For each data length and for each State matrix row, there is a different shift offset. The offset values are given for data length and row numbers in Table 2.2.

| Row number   | 128 | 192 | 256 |

|--------------|-----|-----|-----|

| /Data length |     |     |     |

| Row0         | 0   | 0   | 0   |

| Row1         | 1   | 1   | 1   |

| Row2         | 2   | 2   | 3   |

| Row3         | 3   | 3   | 4   |

### 2.3.2.3 MixColumns Transformation

The MixColumns Transformation is a polynomial multiplication operation over GF  $(2^8)$ . Each column of the State is considered as a unique polynomial and multiplied with a constant and invertible polynomial c(x), which is co prime to  $x^4+1$ .

$$c(x) = '03' x^3 + '01' x^2 + '01' x + '02'$$

The multiplication of the State column a(x) with the constant polynomial c(x) and the result State column b(x) can be written in a matrix form as given in Figure 2.9.

$$b(x) = c(x) * a(x) \pmod{x^4 + 1}$$

| $\langle \rangle$ | <b>`</b> |        |    |    |    | ( ) |

|-------------------|----------|--------|----|----|----|-----|

| b0                |          |        |    | 01 |    | a0  |

| b1                | _        | 01     | 02 | 03 | 01 | a1  |

| b2                | —        | 01     | 01 | 02 | 03 | a2  |

| b3                |          | 03     | 01 | 01 | 02 | a3  |

|                   | ,        | $\sim$ |    |    |    |     |

Figure 2.9: The multiplication of State Column and c(x)

|                                   | a <sub>0,j</sub>              |                                   | x)                                  | b <sub>0,j</sub> |                                   |

|-----------------------------------|-------------------------------|-----------------------------------|-------------------------------------|------------------|-----------------------------------|

| a <sub>0,0</sub> a <sub>0,1</sub> | <sup>ه</sup> a <sub>1,j</sub> | a <sub>0,4</sub> a <sub>0,5</sub> | b <sub>0,0</sub> b <sub>0,1</sub>   | b <sub>1,j</sub> | b <sub>0,4</sub> b <sub>0,5</sub> |

| a <sub>1,0</sub> a <sub>1,1</sub> | ē                             | a <sub>1,4</sub> a <sub>1,5</sub> | b <sub>1,0</sub> b <sub>1,1</sub>   |                  | b <sub>1,4</sub> b <sub>1,5</sub> |

| a <sub>2,0</sub> a <sub>2,1</sub> | a 2,j                         | a <sub>2,4</sub> a <sub>2,5</sub> | b <sub>2,0</sub> b <sub>2,1</sub> ł | b <sub>2,j</sub> | b <sub>2,4</sub> b <sub>2,5</sub> |

| a <sub>3,0</sub> a <sub>3,1</sub> | <sup>a</sup> a <sub>3,j</sub> | a <sub>3,4</sub> a <sub>3,5</sub> | b <sub>3,0</sub> b <sub>3,1</sub> ł | b <sub>3,j</sub> | b <sub>3,4</sub> b <sub>3,5</sub> |

|                                   | -                             |                                   | II                                  |                  |                                   |

Figure 2.10: MixColumns operation

# 2.3.2.4 AddRoundKey Transformation

In AddRoundKey Addition operation the round data and AddRoundKey data is subjected to an EXOR operation.

| a <sub>0,0</sub> | a <sub>0,1</sub> | a <sub>0,2</sub> | a <sub>0,3</sub> |  |

|------------------|------------------|------------------|------------------|--|

| a <sub>1,0</sub> | a <sub>1,1</sub> | a <sub>1,2</sub> | a <sub>1,3</sub> |  |

| a <sub>2,0</sub> | a <sub>2,1</sub> | a <sub>2,2</sub> | a <sub>2,3</sub> |  |

| a <sub>3,0</sub> | a <sub>3,1</sub> | a <sub>3,2</sub> | a <sub>3,3</sub> |  |

$\oplus$

| k <sub>0,0</sub> | k <sub>0,1</sub> | k <sub>0,2</sub> | k <sub>0,3</sub> |   | b <sub>0,0</sub> | b <sub>0,1</sub> | b <sub>0,2</sub> |

|------------------|------------------|------------------|------------------|---|------------------|------------------|------------------|

| k <sub>1,0</sub> | k <sub>1,1</sub> | k <sub>1,2</sub> | k <sub>1,3</sub> | _ | b <sub>1,0</sub> | b <sub>1,1</sub> | b <sub>1,2</sub> |

| k <sub>2,0</sub> | k <sub>2,1</sub> | k <sub>2,2</sub> | k <sub>2,3</sub> | _ | b <sub>2,0</sub> | b <sub>2,1</sub> | b <sub>2,2</sub> |

| k <sub>3,0</sub> | k <sub>3,1</sub> | k <sub>3,2</sub> | k <sub>3,3</sub> |   | b <sub>3,0</sub> | b <sub>3,1</sub> | b <sub>3,2</sub> |

b<sub>0,3</sub>

$b_{1,3}$

$b_{2,3}$

b<sub>3,3</sub>

Figure 2.11: AddRoundKey Addition

## 2.3.3 Decryption Process of AES

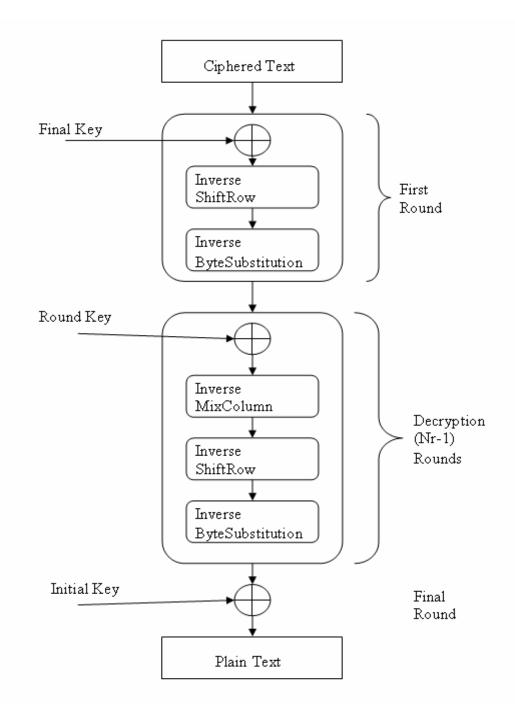

The decryption process is the inverse operation of the encryption process. The transformations in the encryption round are reversed in the mean of the sequence. The decryption diagram of the AES is given in Figure 2.12.

The transformations used in encryption operation are also inversed in the decryption process. The InvSubBytes transformation is the inverse operation of the SubBytes. The InvSubBytes transformation uses the inverse table of the normal SBox table.

The inverse SBox table is obtained by applying the inverse of the affine transformation followed by taking the multiplicative inverse in  $GF(2^8)$  [1]. For example the SBox value of the input 0x81 is 0x0c. And in the inverse SBox table the output of the 0x0c is 0x81.

The inverse SBox table is given in Table A.10 in Appendix A. In the Inverse ShiftRows transformation the shift operation is performed to the right instead of the left side in the encryption process. The offset values in the both shift transformations are same.

Figure 2.12: AES Decryption

The Inverse MixColumns transformation is similar to MixColumns in encryption. But the coefficients of the constant polynomial are changed. The constant polynomial for the Inverse MixColumns transformation is named as d(x), where

$$d(x) = '0B' x^{3} + '0D' x^{2} + '09' x + '0E',$$

and  $c(x) \cdot d(x) \equiv 01 \pmod{x^4+1}$ .

| < > |   | ~      |    |    | ~                    |   | < > |   |

|-----|---|--------|----|----|----------------------|---|-----|---|

| 60  |   | (0e    | 0Ъ | 0d | 09)                  |   | a0  |   |

| b1  | _ | 09     | 0e | 0Ъ | 0d                   |   | a1  |   |

| 62  | — | 0d     | 09 | 0e | 09<br>0d<br>0b<br>0e | • | a2  |   |

| 63  |   | lоъ    | 0đ | 09 | 0e )                 |   | a3  |   |

| ( ) |   | $\sim$ |    |    | _                    |   | ( ) | / |

Figure 2.13: The multiplication of State Column and d(x)

The round number is same for decryption process. But the AddRoundKey is applied in reverse order. The first operation of the decryption is EXOR operation between the final round key and the ciphered data, which is the input of the decryption process.

Then inverse ShiftRows and Inverse SubBytes are performed sequentially. The iterated rounds start with the AddRoundKey transformation and then continue with Inverse MixColumns, Inverse ShiftRows and Inverse SubBytes transformations. As a last operation the EXOR operation with the first round key is performed to get the plaintext.

#### 2.3.4 Key Expansion and Round Key Selection

The Key Expansion part is responsible to provide the round keys for relevant rounds of cipher operation. While the round number can be different for different key lengths, the operation of the Key Expansion can show differences. The operation is same for 128-bit and 192-bit key length but it is different for 256-bit key length.

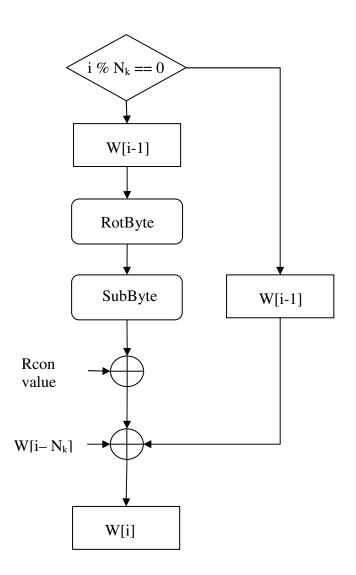

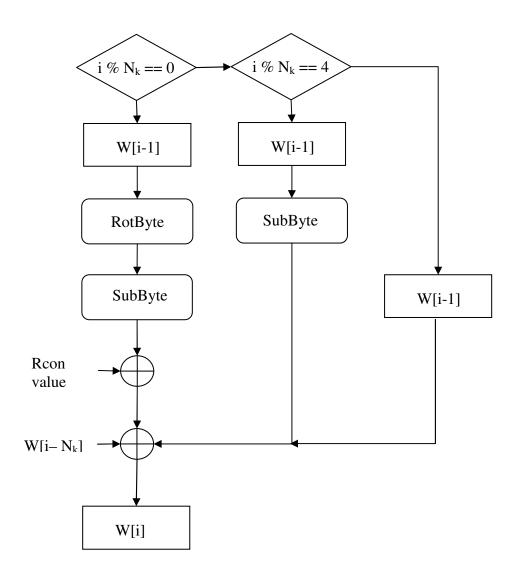

The operations in the Key Expansion is made over 32 bits, named as word "W". The input key is assigned as the first  $N_k$  words of the Key Expansion. All of the other words are obtained recursively of these words. The expansion operation of the remaining words is given in Figure 2.14 for 128 and 192 bits and in Figure 2.15 for 256 bits.

The recursive operation for obtaining the following words after first  $N_k$  word uses the previous words, the  $N_k$  positions earlier words and round constants. The recursive function is directly related to the position of the word. If the current position "i" is not a multiple of the  $N_k$ , then a simple XOR operation between previous word (W[i-1]) and  $N_k$  earlier word (W[i -  $N_k$ ]) gives the current word value (W[i]). In the other situation, if "i" is a multiple of the  $N_k$ , the current word W[i] is the result of the EXOR operation of  $N_k$  earlier word and the nonlinear function of the previous word W[i - 1]. This nonlinear function consists of a cyclically rotation operation to right by one byte, which is called RotByte, a nonlinear byte substitution operation for each byte in the word element, which is called SubByte, and addition of a round constant value. The round constants are independent of the  $N_k$  value, and defined by a recursion rule in GF (2<sup>8</sup>) as shown below.

Rcon [1] =

$$x^0$$

(i.e. 01)

Rcon [2] =  $x^1$  (i.e. 02)

Rcon [k] =  $x * Rcon [k-1] = x^{k-1}$ , k > 2.

Figure 2.14: Key Expansion for 128 and 192 bits

Figure 2.15: Key Expansion for 256 bits

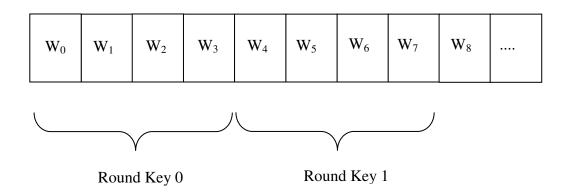

The round keys are chosen from the word array of Key Expansion part. The round keys' length should be equal to the input plaintext length. Hence the round key consists of array elements from word W  $[N_b*i]$  to word W  $[N_b*(i+1)]$ .

The round key selection is illustrated in Figure 2.16.

Figure 2.16: Round Key Selection

# 2.4 DES Algorithm

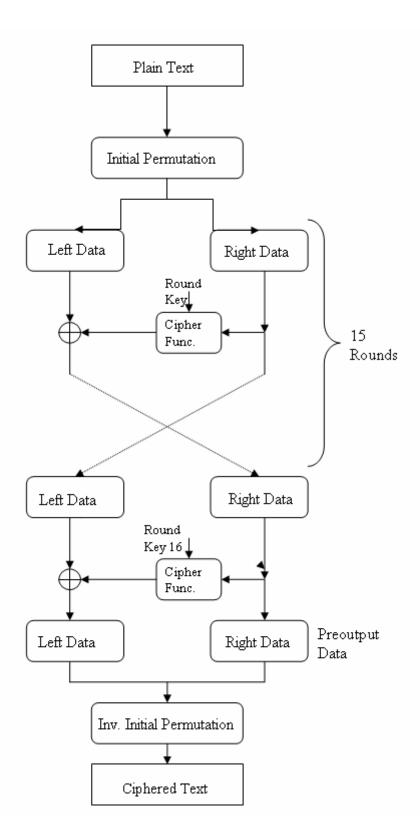

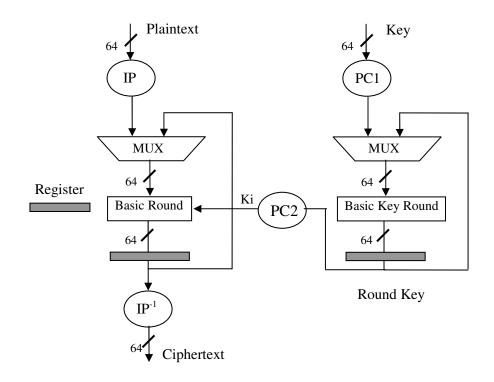

The Data Encryption Standard (DES) was developed by IBM in 1970s and then approved as a standardized crypto algorithm by Federal Information Processing Standard (FIPS) [4] in 1977. DES is a symmetric crypto algorithm, which operates on 64-bit block size within 16 rounds. The input plaintext and the output ciphered text are 64-bit. The encryption or decryption operation is achieved by a 64-bit key data. But only the 56bits of the whole key data is effective. The remaining 8 bits have no effect on the encryption/decryption process of the DES. The encryption and decryption processes use the same key due to symmetric nature of the algorithm. Also the ciphering flow is same for both the encryption and decryption. The only difference is the order of the round keys. The round keys are in reverse order for the decryption process. The block diagram of the DES encryption algorithm is given in Figure 2.17. The DES algorithm can be analyzed in two parts. The first part is the Key Expansion part, which generates the necessary round keys. And the second part is the encryption part. In the second part the encryption or decryption process is operated with the contribution of the round keys. Also the encryption part can be divided into two group of operation. First one is the permutation operations, which are the first and last operations of the cipher part, and the second group consists of rounds operation between these permutations.

# 2.4.1 DES Rounds

# 2.4.1.1 Initial Permutation

The Initial Permutation is the first operation in the DES encryption algorithm. The incoming 64-bit plaintext data is subjected to initial permutation table, which is given in Table2.3. According to the table the first bit of the output data is the 58. bit of the input data, the second bit of the output is the 50. bit of the input data and so on.

| 58 | 50 | 42 | 34       | 26 | 18 | 10 | 2 |

|----|----|----|----------|----|----|----|---|

| 60 | 52 | 44 | 36       | 28 | 20 | 12 | 4 |

| 62 | 54 | 46 | 38       | 30 | 22 | 14 | 6 |

| 64 | 56 | 48 | 40       | 32 | 24 | 16 | 8 |

| 57 | 49 | 41 | 33       | 25 | 17 | 9  | 1 |

|    |    |    |          |    |    |    |   |

| 59 | 51 | 43 | 35       | 27 | 19 | 11 | 3 |

|    |    |    | 35<br>37 |    |    |    |   |

Figure 2.17: DES Algorithm

The main round processes start after the Initial permutation. The data is split into two groups of 32 bits as shown in Figure 2.17. These groups of data are named as "R" right half and "L" left half. The Right half is joined to the encryption or decryption process with the round key data. The key-dependent operation, substitution tables operations are processed in a function, called cipher function.

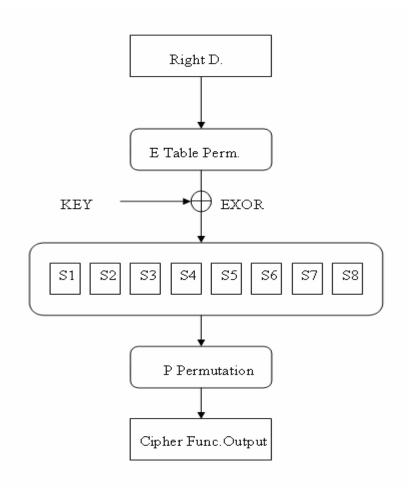

# 2.4.1.2 Cipher Function

The operations in the Cipher function are given in Figure 2.18. There are two permutation operations, which are E Table permutation and P permutation, a Substitution operation and an EXOR operation with the round key data.

Figure 2.18: DES Cipher Function

Table 2.4: E Bit Selection Table

| 32 | 1  | 2  | 3  | 4  | 5  |

|----|----|----|----|----|----|

| 4  | 5  | 6  | 7  | 8  | 9  |

| 8  | 9  | 10 | 11 | 12 | 13 |

| 12 | 13 | 14 | 15 | 16 | 17 |

| 16 | 17 | 18 | 19 | 20 | 21 |

| 20 | 21 | 22 | 23 | 24 | 25 |

| 24 | 25 | 26 | 27 | 28 | 29 |

| 28 | 29 | 30 | 31 | 32 | 1  |

The E Bit Selection table is the first operation in the Cipher function. The round keys in the DES algorithm are 48 bits, while the round data from group R is 32 bits. The E Bit Selection table matches the number of bits of the round data to the round key data, as duplicating some of the bits, which is given in Table 2.4.

After this operation an EXOR operation performed between the key data and round data. The output of the EXOR operation is fed into a SBox array. Each one of the eight SBox units takes 6-bit data as input and gives 4-bit data as output.

The SBox Table S1 is given below. The whole SBox tables from S1 to S8 appear in Appendix A.

| Row | Col | umn | Num | ber |    |    |    |    |    |    |    |    |    |    |    |    |

|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|----|----|

| Num | 0   | 1   | 2   | 3   | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 12 | 13 | 14 | 15 |

| 0   | 14  | 4   | 13  | 1   | 2  | 15 | 11 | 8  | 3  | 10 | 6  | 12 | 5  | 9  | 0  | 7  |

| 1   | 0   | 15  | 7   | 4   | 14 | 2  | 13 | 1  | 10 | 6  | 12 | 11 | 9  | 5  | 3  | 8  |

| 2   | 4   | 1   | 14  | 8   | 13 | 6  | 2  | 11 | 15 | 12 | 9  | 7  | 3  | 10 | 5  | 0  |

| 3   | 15  | 12  | 8   | 2   | 4  | 9  | 1  | 7  | 5  | 11 | 3  | 14 | 10 | 0  | 6  | 13 |

Table 2.5: SBox S1 Table

Each of the SBox units has 64 memory elements. The input 6-bit data is replaced with one of the SBox memory elements according to its value. The first and last bits of the incoming data to the SBox unit determines the row number and the middle 4 bits represent the column number of the output data in the SBox unit. The output data of the SBox units is 32-bit data again. Hence the expanded round data is reduced again to its normal bit length with this operation. The output data of the SBox undergoes to another permutation, P permutation, which is defined in Table 2.6.

# Table 2.6: P Permutation Table

| 16 | 7  | 20 | 21 |

|----|----|----|----|

| 29 | 12 | 28 | 17 |

| 1  | 15 | 23 | 26 |

| 5  | 18 | 31 | 10 |

| 2  | 8  | 24 | 14 |

| 32 | 27 | 3  | 9  |

| 19 | 13 | 30 | 6  |

| 22 | 11 | 4  | 25 |

The definition of the table is same with other permutation tables. The first bit of the output is the 16. bit, the second bit is the seventh bit of the input and so on.

The P permutation is the last operation of the Cipher function. Then the output of the Cipher function and the Left part of the round data is XORed. The result of the XOR operation will be the Right part of the next round data. And the Right data of the current round becomes the Left part of the next round data. This swap operation between Left part and Right part is not performed in the 16.th round.

# 2.4.1.3 Inverse Initial Permutation

The Left and Right data of the 16.th round are concatenated and named as preoutput block. This preoutput block data is subjected to the Inverse Initial permutation. This permutation is the last operation of the DES encryption/decryption process and it is the inverse operation of the Initial permutation.

Table 2.7: Inverse Initial Permutation Table

| 40 | 8 | 48 | 16 | 56 | 24 | 64 | 32 |

|----|---|----|----|----|----|----|----|

| 39 | 7 | 47 | 15 | 55 | 23 | 63 | 31 |

| 38 | 6 | 46 | 14 | 54 | 22 | 62 | 30 |

| 37 | 5 | 45 | 13 | 53 | 21 | 61 | 29 |

| 36 | 4 | 44 | 12 | 52 | 20 | 60 | 28 |

| 35 | 3 | 43 | 11 | 51 | 19 | 59 | 27 |

| 34 | 2 | 42 | 10 | 50 | 18 | 58 | 26 |

| 33 | 1 | 41 | 9  | 49 | 17 | 57 | 25 |

That is, the output of the algorithm has bit 40 of the preoutput block as its first bit, bit 8 as its second bit, and so on, until bit 25 of the preoutput block is the last bit of the output.

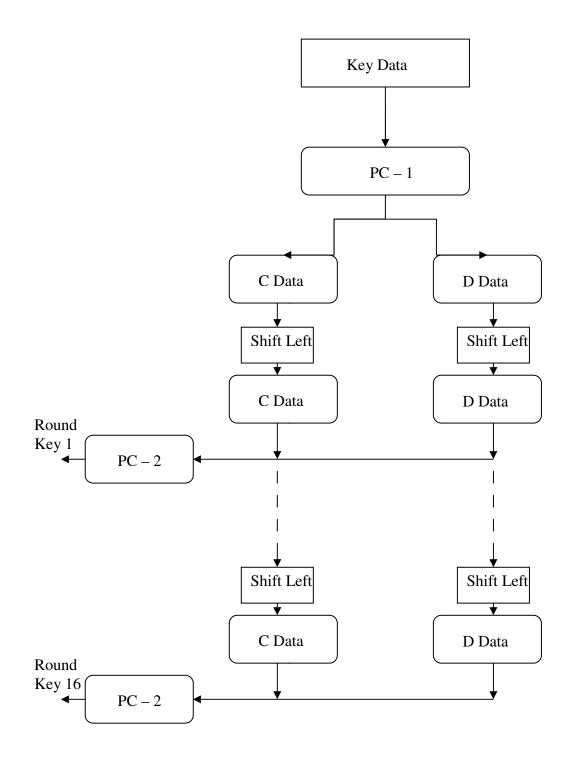

#### 2.4.2 Key Expansion Part

The Key Expansion part takes the 64-bit key data as input and prepares the 16 round key data for encryption process. However the input data is 64-bit length, only 56-bit data is used for the round keys preparation. The eight bits of the each byte is dropped. In some cases the 8<sup>th</sup> bits can be used as parity bit for error detection in key generation. There are three parts of the Key Expansion part. In the first part the input data is subjected to the PC-1 permutation. The permutation table of the PC-1 is given in Table 2.8. Then the output data are split into two parts like in encryption process, but here the divided parts are 28-bit long. The second part of the Key Expansion is cyclic left shift operation applied each of these two 28-bit parts individually. The two parts are shifted to left with predefined offset values before calculating the round key. The offset values for each round are given in Table 2.10. The last process in the Key Expansion is PC-2 permutation, which permutation table is given in Table 2.9. The input of the PC-2 permutation is 56-bit data and the output is 48-bit data. There is compressing process applied into the key data with the PC-2 permutation. After each left shift operation the data is subjected to the PC-2 permutation and the result of this operation is the round key data.

Table 2.8: PC-1 Permutation Table

| 57 | 49 | 41 | 33 | 25 | 17 | 9  |

|----|----|----|----|----|----|----|

| 1  | 58 | 50 | 42 | 34 | 26 | 18 |

| 10 | 2  | 59 | 51 | 43 | 35 | 27 |

| 19 | 11 | 3  | 60 | 52 | 44 | 36 |

| 63 | 55 | 47 | 39 | 31 | 23 | 15 |

| 7  | 62 | 54 | 46 | 38 | 30 | 22 |

| 14 | 6  | 61 | 53 | 45 | 37 | 29 |

| 21 | 13 | 5  | 28 | 20 | 12 | 4  |

Table 2.9: PC-2 Permutation Table

| 14 | 17 | 11 | 24 | 1  | 5  |

|----|----|----|----|----|----|

| 3  | 28 | 15 | 6  | 21 | 10 |

| 23 | 19 | 12 | 4  | 26 | 8  |

| 16 | 7  | 27 | 20 | 13 | 2  |

| 41 | 52 | 31 | 37 | 47 | 55 |

| 30 | 40 | 51 | 45 | 33 | 48 |

| 44 | 49 | 39 | 56 | 34 | 53 |

| 46 | 42 | 50 | 36 | 29 | 32 |

# Table 2.10: Left Shift Offset Value Table

| Round Number | Left Shift Offset |

|--------------|-------------------|

| 1            | 1                 |

| 2            | 1                 |

| 3            | 2                 |

| 4            | 2                 |

| 5            | 2                 |

| 6            | 2                 |

| 7            | 2                 |

| 8            | 2                 |

| 9            | 1                 |

| 10           | 2                 |

| 11           | 2                 |

| 12           | 2                 |

| 13           | 2                 |

| 14           | 2                 |

| 15           | 2                 |

| 16           | 1                 |

Figure 2.19: DES Key Expansion

#### **2.5 Triple DES (TDES) Algorithm**

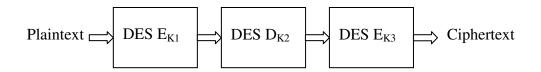

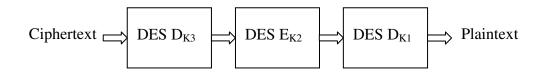

The Triple Data Encryption Algorithm (TDEA), more commonly Triple DES is an approved cryptographic algorithm, which is enlarge the key space of the DES algorithm. There are three DES keys in the TDES operation, which are called as Key<sub>1</sub>, Key<sub>2</sub>, Key<sub>3</sub> and referred to as a key bundle (KEY). These three keys are used in two allowed option to form the key bundle. In the first option, all three keys are mutually independent (i.e. Key<sub>1</sub>, Key<sub>2</sub> and Key<sub>3</sub>, where Key<sub>1</sub>  $\neq$  Key<sub>2</sub>  $\neq$  Key<sub>3</sub>  $\neq$  Key<sub>1</sub>). And in the second option, there are mutually independent keys and a third key that is the same as the first key (i.e. Key<sub>1</sub>, Key<sub>2</sub> and Key<sub>3</sub>, where Key<sub>1</sub>  $\neq$  Key<sub>2</sub> and Key<sub>3</sub> = Key<sub>1</sub>). The simple encryption and decryption operations of the TDES are given in Figure 2.20 and Figure 2.21 respectively. In the TDES encryption operation, the algorithm process begins with the DES encryption by using Key<sub>1</sub>, then continue with DES decryption operation by using Key<sub>2</sub> and it is finished with DES encryption operation by using Key<sub>3</sub>.

Figure 2.20: TDES Encryption Operation

Figure 2.21: TDES Decryption Operation

In this chapter the AES, DES and TDES algorithms have been discussed. The crypto algorithm types, the encryption and decryption structures of the AES, DES and TDES algorithm and the transformations used in algorithms are explained. The next chapter presents the different implementations of these algorithms.

#### **CHAPTER 3**

# **CRYPTO PROCESSOR ARCHITECTURES**

#### **3.1 Introduction**

In Section 3.2, different architectures and implementations of these architectures are discussed. In Section 3.3 bit permutation instructions in the literature, are described.

#### **3.2 Different Processor Implementations**

There are many studies about the crypto processors in the literature. Some of these studies are focused on only a single crypto algorithm, and some others are designed to support several algorithms in a single architecture. The different architectures are discussed in this chapter.

Crypto processor architecture, called Cryptonite, is presented by Rainer Buchty, Nevin Heintze and Dino Oliva in [7]. This study is about a programmable architecture for the cryptographic applications. DES, TDES, AES, IDEA, RC6, MD5, and SHA-1 algorithms are supported by this architecture.

This architecture has a different instruction set for cryptographic processing such as parallel 8-way permutation lookups, parameterized 64-bit/32-bit rotation, and XOR-based fold operations.

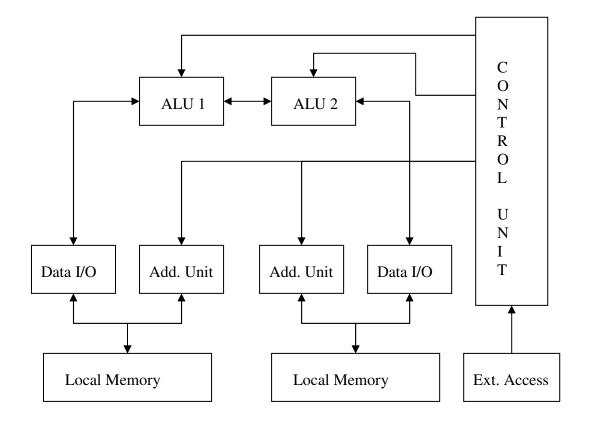

These instructions are used for the core functions of different crypto algorithms and show differences than general purpose instructions. All instructions are executed in a single cycle. 64-bit and 32-bit computations are supported in this study. The main architecture of the Cryptonite is given in Figure 3.1.

Figure 3.1: Cryptonite architecture

The Control unit controls the system according to the instructions. There is a twocluster architecture presented in the study. There is an ALU and its accompanying data I/O unit for each of cluster. The data unit of the ALU is responsible of the data access between local data memory and ALU. There is an interlink between the ALUs to enable the data change in complex computations.

Furthermore the new XOR unit implementation into the data path, a parameterizable permutation engine, a DES specific unit and some AES supporting functions are implemented in the architecture. The DES specific unit is implemented into the memory unit instead of the ALU.

The XOR unit of this architecture has 6 input. These inputs come from ALU registers, memory unit and as immediate value. The aim of this 6-input XOR unit is to avoid the sequential operations between multi input XOR operations.

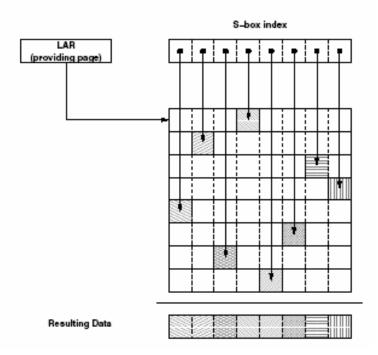

The other new unit is the parameterizable permutation engine. The permutation operations are performed with a lookup table, which can be used up to 8 parallel lookups. The vector memory unit, which is used as reconfigurable permutation engine, receives a vector of indexes and a scalar base address to address the memories of a vector. The collections of addressed memories form the result data vector. The structure of the vectored memory access is given in Figure 3.2.

The results of the Cryptonite architecture are given in Table 3.1.

Figure 3.2: Vectored Memory Access

Table 3.1: Cryptonite architecture results

| Algorithm | Throughput<br>(Mbit/s) | Cycle count | Speed (MHz) |

|-----------|------------------------|-------------|-------------|

| DES       | 732                    | 35          | 400         |

| TDES      | 244                    | 105         | 400         |

| AES       | 731                    | 70          | 400         |

| MD5       | 421                    | 504         | 400         |

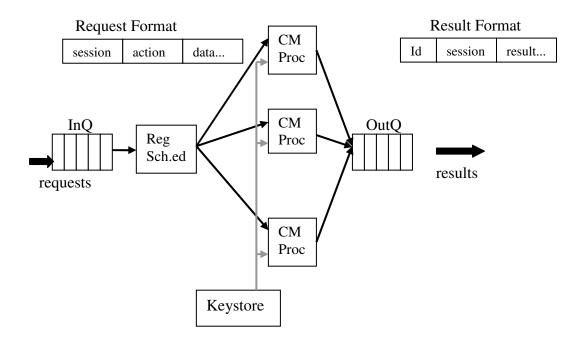

Another architecture for the programmable processor is presented by Lisa Wu, Chris Weaver and Todd Austin [8]. The presented architecture, called CryptoManiac, is a 4-wide, 4-stage 32-bit VLIW processor with a three input operand ISA. There is a simple branch predicter in the processor, but it does not have a cache. The code and data is stored in a static RAM. The branch predicter is used to make predictions about the next target address when there are more than one branch instructions in an instruction word.

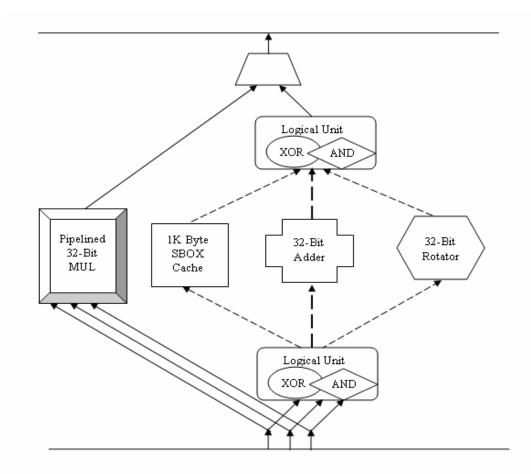

Figure 3.3: Schematic of CryptoManiac Architecture

The interface between a host processor and CryptoManiac is provided by input and output request queues. A request scheduler distributes the requests of host processor to CryptoManiac processor in the order of receive. The Keystore part is a highdensity storage element for storing key data and substitution tables. Simultaneous session processing on the same processor is available by storing key-specific data in the shared keystore. This data includes substitution data, permutation counters, and other internal algorithm state data. This part is only used for multisession applications and not necessary for single session applications. There are four parallel functional units in the CryptoManiac architecture. The process in the architecture is started with fetching a single VLIW instruction word that contains four independent instructions.

The instruction set consists of 32-bit instructions and enhanced for the cryptographic processes by combining general arithmetic instructions with logical instructions, substitutions with logical instructions, and rotate operations with logical instructions. Each instruction has three operands as input and one operand for the output, again to combine some instructions.

Figure 3.4: Schematic of a single functional unit

The Figure 3.4 shows the internal structure of a functional unit. Each functional unit consists of two logical units, one adder, one 1k-byte SBox cache, and one rotator. The multiplier block is added to only two blocks. The XOR, AND operations are processed in the logical units. SBox cache is responsible for holding all the data, key and SBox parameters instead of using a memory. The estimated result of the CryptoManiac is given in Table 3.2.

| Algorithm         | Throughput<br>(Mbit/s) | Cycle count | Speed (MHz) |

|-------------------|------------------------|-------------|-------------|

| TDES              | 68                     | 336         | 360         |

| TDES corr.        | 59                     | 392         | 360         |

| AES 128/128       | 511                    | 90          | 360         |

| AES 128/128 corr. | 353                    | 130         | 360         |

Table 3.2: Estimated results of CryptoManiac architecture

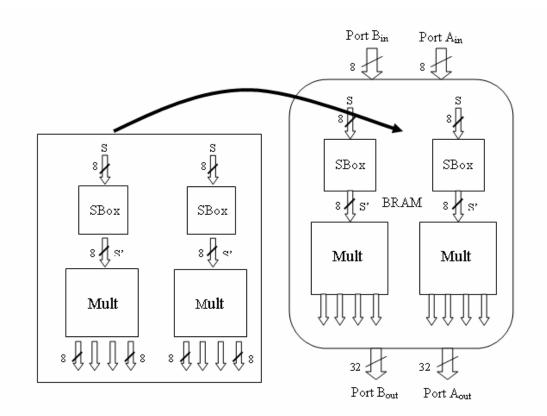

In another study by Ricardo Chaves, Georgi Kuzmanov, Stamatis Vassiliadis and Leonel Sousa [9] the AES encryption/decryption algorithm with a memory based hardware design is proposed. In the memory based design both the SubBytesand the polynomial multiplication are implemented in internal memories of the FPGA (BRAM).

There are two AES encryption/ decryption cores presented. One of them is a completely unrolled loop structure capable of achieving a throughput above 34 Gbits/s, with an implementation cost of 3513 slices and 80 BRAMs; and the other one is a fully folded structure, requiring only 515 slices and 12 BRAMs, capable of a throughput above 2 Gbits/s.

The first structure has not any area constraints and it is designed for the higher throughput requirements. The second structure is designed for the area constraints. In the general AES block implementation they use dual port memory blocks such as BRAM's in the FPGA's for the SBox and MixColumns processes. In the BRAM's 2 SubBytesstitutions and 2 full multiplications can be mapped in a single memory block.

Figure 3.5: SBox and MixColumns computation using BRAM

After implementing the BRAM structure, the paper proposes two architectures for the AES operation. AES unfolded core is designed with adding sequentially all the rounds and AES folded core is designed with only one core which repeats the rounds.

In a study by Alireza Hodjat, Ingrid Verbauwhede [10] an area-throughput trade-off for an ASIC implementation of the Advanced Encryption Standard is presented. The paper presents throughputs of 30 Gbits/s to 70 Gbits/s with loop unrolling and innerround and outer-round pipelining techniques, using a 0,18 µm CMOS technology. Also, the possibility of achieving a throughput of over 30 Gbits/s encryption using the AES algorithm with minimum area cost is explored in this paper. The main goal of the paper is combining the pipelining with a composite field implementation. The paper calculates the SBox values using the Galois Field operations. The input byte (element of GF  $(2^8)$ ) is mapped to two elements of GF  $(2^4)$ . Then, the multiplicative inverse is calculated using GF  $(2^4)$  operators. Then, the two GF  $(2^4)$  elements are inverse mapped to one element in GF  $(2^8)$ . In the end, the affine transformation is performed. There is also used pipelined structure in the SBox calculation structure to avoid the high latency in the Galois field operations. By using a pipelined structure in the SBox process, the area is reduced up to 35 percent and by designing an offline key scheduling unit for the high speed AES processor, an area reduction of an extra 28 percent is achieved according to the paper.

In another study by Oscar Perez, Yves Berviller, Camel Tanougast and Serge Weber [11] the experimental results of different strategies of implementation of AES encryption algorithm is presented. There is given a comparison between different techniques at the beginning of the study.

These techniques are Inner-Round pipelining, Outer-Round pipelining, Full Loop Unrolling, Iterative looping and reconfiguration. They divided the algorithm into two parts, which are Key Expansion part and Cipher Part. The above strategies are used in the implementation of these two parts and then a comparison is made between the cost and the performance of the implemented techniques. The paper offers three strategies to compare the performances.

- 1. Unrolling the loop and reconfiguration techniques

- 2. Iterative looping and the reconfiguration techniques

- 3. Pipelined technique

The performance tests are implemented on the FPGA Xilinx XC2V6000. According to the results the best throughput is achieved by config1. But the weak side of this technique is reconfiguration time. By contrast, in config2 who uses reconfiguration and the reusing of operators, the throughput is very low, but it offers two advantages: the use of few resources and a density of calculation quite near the other implementations. The performance, surface is interesting because these values are close to the best implementation. On the other hand, they are penalized in terms of latency by the time used for the reconfiguration. The pipelined technique also has good throughput results, but it uses higher BRAM capacity.

A reconfigurable processor implementation is proposed by Yongzhi Fu, Lin Hao and Xuejie Zhang [12]. This study is about the implementation of a counter mode AES based on the Xilinx Virtex2 FPGA platform. In the AES design there is loop unrolling, inner and outer round and mixed pipelining. The clock frequency of the fully mixed inner and outer round pipelined architecture has achieved 212.5MHz and that translate to throughput of 27.1Gb/s. The difference of this article is using a switch between MixColumns operation and AddRoundKey operation.

For the SBox operation Look Up Tables are used and the ShiftRows is implemented by configuring the routing resources. In the MixColumns operation they use shift and accumulation method, which is shift the incoming data 0 bit left when the polynomial constant is '02' and then XOR the results. The AddRoundKeys are computed before the encryption process for a pipelined structure. According to the several implementation tests the best result is achieved using the mixed structure, which includes inner and outer pipelining, and loop unrolling.

Figure 3.6: The switch structure

In another study by Alireza Hodjat, David D. Hwang, Bocheng Lai, Kris Tiri and Ingrid Verbauwhede [13] an AES crypto processor, which can handle both feedback and non feedback modes of operation is presented. It is reported that this implementation can achieve a throughput of 3.84 Gbps at a 330 MHz clock frequency. For the implementation of the non-feedback modes of the operation the design has a non-pipelined structure. In this design all implementation is based on the single clock cycle. All rounds are designed for this purpose. In the SBox operation the LUT are used and in the MixColumns operation there are used a chain of XORs.

Figure 3.7: The architecture of AES Core

The proposed crypto coprocessor can be programmed through the memory-mapped interface of an embedded CPU core. The embedded CPU core can read or write to the registers by accessing different memory locations. The memory-mapped interface decodes the memory addresses and updates the registers' values.

Another configurable AES processor and its experimental results are presented by Chih-Pin Su, Chia-Lung Horng, Chih-Tsun Huang and Cheng-Wen Wu [14]. This study proposes a configurable AES processor, which can run both the original AES and the extended AES algorithm. The extended AES algorithm has some additional properties like providing some flexibility to the configuring to parameters of each transform defined in AES. They provide the flexibility by configuring the parameters given below;

- 1. Irreducible polynomial in SBox

- 2. Fixed polynomial values in MixColumns

- 3. Affine transformation in SBox

The AES core is called AESTHETIC. The original AES algorithm and the extended AES algorithm are reconfigured depending on the application.

#### **AESTHETIC Processor**

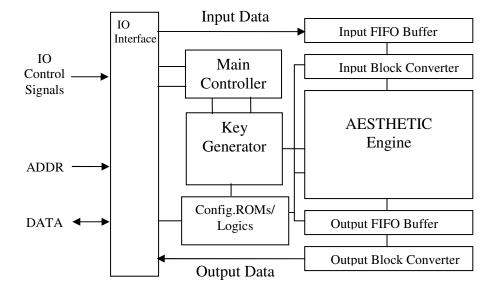

Figure 3.8: Block diagram of the AESTHETIC processor

The AESTHETIC core is similar like the original AES operations. In the design the SBox operation is implemented as using Galois Field arithmetic operations. And for the MixColumns operation there are 64 GF  $((2^4)^2)$  multipliers to process the data block in parallel. The design generates the AddRoundKeys on the fly method. The implementation results of this design are;

844.8 Mbps for 128-bit keys @66MHz clock frequency 704.0 Mbps for 192-bit keys @66MHz clock frequency 603.4 Mbps for 256-bit keys @66MHz clock frequency

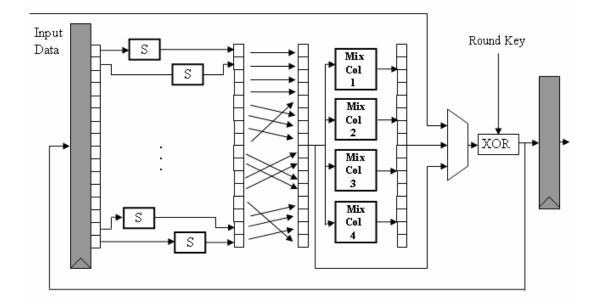

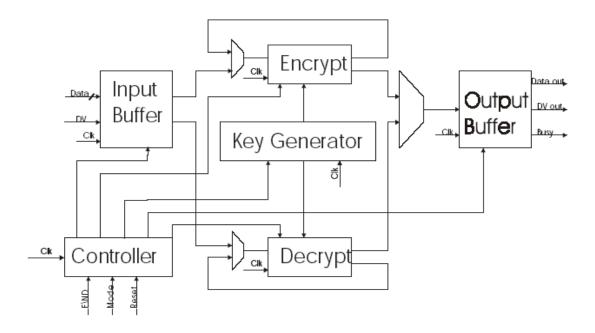

In another study by Refik Sever, A. Neslin İsmailoğlu, Yusuf C. Tekmen and Murat Aşkar [6] the VLSI design and implementation of Rijndael algorithm is presented. In this study, both of the encryption and decryption algorithms are implemented for all data and key sizes on a single ASIC, with a non pipelined structure. The main diagram of the implemented architecture is given in Figure 3.9.

Figure 3.9: Block diagram of the implemented architecture

A single round of the algorithm is completed in one clock cycle. There are 32-S box to complete one round of the algorithm in one clock cycle.

The SBox part is implemented using combinatorial logic instead of using Look up Table. There are two separate EXOR blocks. The last round of the encryption of the current block and the first round of the encryption of the next block are processed at the same time. This two separate EXOR blocks are necessary for not loosing one clock cycle. Key Generator module consists of three sub modules: Key Expansion module, Key Storage module and Key selection module. All the keys needed for encryption and decryption processes are produced by Key Expansion module and stored by Key Storage module.

All the keys are generated and stored before encryption or decryption starts. The implementation results are given below,

- 0.35 µm CMOS technology

- Modules are described using Verilog HDL, and then synthesized with Synopsys Design Analyzer

- The chip area is 12.8 mm<sup>2</sup>

- There are 149K gates

- The worst case clock frequency is 132 Mhz

- The maximum throughput is 2.41 Gbps

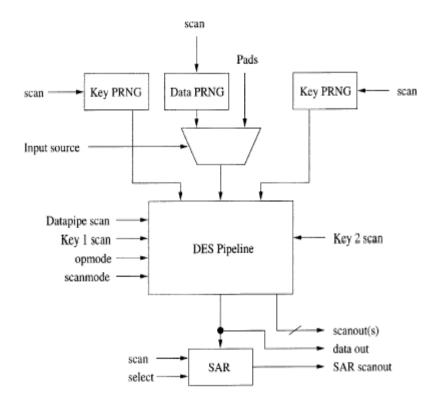

In a study by Toby Schaffer, Alan Glaser and Paul D. Franzon [18] the design and implementation of a DES processor is presented. The processor has three separate circuit, each can operate on an individual data stream to perform DES algorithm, or three can operate together to perform TDES algorithm. The block diagram of one block is given in Figure 3.10.

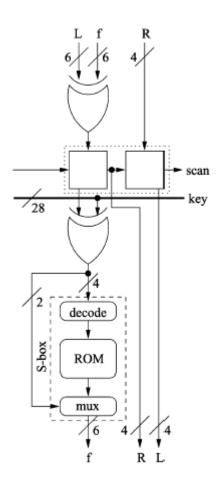

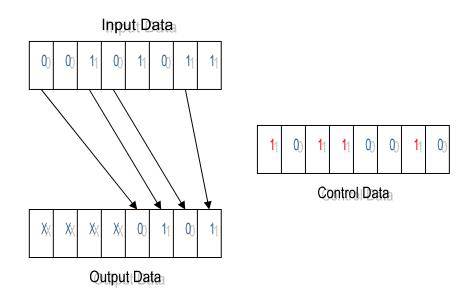

Figure 3.10: Block diagram of the one DES circuit