## COMMON MODE VOLTAGE AND CURRENT REDUCTION IN VOLTAGE SOURCE INVERTER DRIVEN THREE PHASE AC MOTORS

## A THESIS SUBMITTED TO THE GRADUATE SCHOOL OF NATURAL AND APPLIED SCIENCES OF MIDDLE EAST TECHNICAL UNIVERSITY

BY

EMRE ÜN

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE IN ELECTRICAL AND ELECTRONICS ENGINEERING

NOVEMBER 2007

Approval of the thesis:

## COMMON MODE VOLTAGE AND CURRENT REDUCTION IN VOLTAGE SOURCE INVERTER DRIVEN THREE PHASE AC MOTORS

submitted by EMRE ÜN in partial fulfillment of the requirements for the degree of Master of Science in Electrical and Electronics Engineering Department, Middle East Technical University by,

| Prof. Dr. Canan Özgen<br>Dean, Graduate School of <b>Natural and Applied Sciences</b>          |            |

|------------------------------------------------------------------------------------------------|------------|

| Prof. Dr. İsmet Erkmen<br>Head of Department, <b>Electrical and Electronics Enginee</b>        | ring       |

| Asst. Prof. Dr. Ahmet M. Hava<br>Supervisor, <b>Electrical and Electronics Engineering Dep</b> | t., METU   |

| Examining Committee Members:                                                                   |            |

| Prof. Dr. Muammer Ermiş<br>Electrical and Electronics Engineering Dept., METU                  |            |

| Asst. Prof. Dr. Ahmet M. Hava<br>Electrical and Electronics Engineering Dept., METU            |            |

| Prof. Dr. Nevzat Özay<br>Electrical and Electronics Engineering Dept., METU                    |            |

| Assoc. Prof. Dr. Sencer Koç<br>Electrical and Electronics Engineering Dept., METU              |            |

| Dr. Erbil Nalçacı<br>EPDK                                                                      |            |

| Date:                                                                                          | 27/11/2007 |

I hereby declare that all information in this document has been obtained and presented in accordance with academic rules and ethical conduct. I also declare that, as required by these rules and conduct, I have fully cited and referenced all material and results that are not original to this work.

Name, Last name : Emre Ün

Signature :

### ABSTRACT

### COMMON MODE VOLTAGE AND CURRENT REDUCTION IN VOLTAGE SOURCE INVERTER DRIVEN THREE PHASE AC MOTORS

Ün, Emre

M.S., Department of Electrical and Electronics Engineering Supervisor: Asst. Prof. Dr. Ahmet M. Hava

November 2007, 246 pages

In this thesis various reduced common mode voltage (RCMV) pulse width modulation (PWM) techniques and active/passive common mode voltage (CMV) reduction methods for voltage source inverter driven three-phase AC motors are theoretically and practically investigated. A novel RCMV-PWM method, the near state PWM (NSPWM) method is proposed for operation at high modulation index. At low modulation index, a modified version of an existing RCMV-PWM method, AZSPWM1, termed as MAZSPWM, is proposed to mitigate the voltage reflection problem of the method. An optimum modulation algorithm combining NSPWM and MAZSPWM with seamless transition is proposed. The proposed RCMV-PWM methods significantly reduce CMV but they suppress common mode current (CMC) partially. Utilization of a common mode inductor together with RCMV-PWM methods is effective in suppressing the CMC. In the study, in addition to the CMV characteristics, various practical performance characteristics such as voltage linearity, inverter output current ripple, inverter DC-link current ripple, and output line-to-line voltage pulse pattern are also analyzed. The study involves analysis, computer simulations, and detailed laboratory experiments.

Keywords: PWM, inverter, common mode, near state PWM, motor, EMI

# GERİLİM KAYNAKLI EVİRİCİLERLE SÜRÜLEN ÜÇ FAZLI ALTERNATİF AKIM MOTORLARINDA ORTAK MOD GERİLİMİ VE AKIMININ AZALTILMASI

Ün, Emre

Yüksek Lisans, Elektrik ve Elektronik Mühendisliği Bölümü Tez Yöneticisi: Yrd. Doç. Dr. Ahmet M. Hava

Kasım 2007, 246 sayfa

Bu tezde gerilim kaynaklı eviriciden sürülen üç fazlı AC motorlar için çeşitli ortak mod gerilimi düsürücü (OMGD) darbe genişlik modülasyon (DGM) yöntemleri ve aktif/pasif ortak mod gerilimi (OMG) düşürücü yöntemler teorik ve pratik olarak incelenmektedir. Yüksek modülasyon indisi bölgesi için yeni bir OGMD-DGM yöntemi olan yakın komşu (YKDGM) yöntemi önerilmiştir. Düşük modülasyon indisi bölgesinde, mevcut bir OMGD-DGM yöntemi olan AZSPWM1'in geliştirilmiş hali olan MAZSPWM, yöntemin gerilim yansıması problemini gidermek üzere önerilmiştir. YKDGM ve MAZSPWM yöntemlerini birleştiren ve geçişleri yumuşak olan optimum bir modülasyon algoritması önerilmiştir. Önerilen OMGD-DGM yöntemleri, OMG'yi etkin bir şekilde azaltmakta ancak ortak mod akımını (OMA) kısmen bastırmaktadır. OMGD-DGM yöntemleri ile birlikte ortak mod indüktörünün kullanılması OMA'yı etkili biçimde bastırmaktadır. Bu çalışmada, OMG karakterstiklerine ek olarak, gerilim doğrusallığı, evirici çıkış akım dalgacığı, DCbara akımı dalgacığı ve faz-arası çıkış gerilimi darbe şablonu gibi değişik pratik başarım karakteristikleride analiz edilmektedir. Bu çalışma, analiz, bilgisayar benzetimi ve laboratuvar deneylerini kapsamaktadır.

Anahtar Kelimeler: DGM, evirici, ortak mod, yakın komşu DGM, motor, EMI

To my family

### ACKNOWLEDGMENTS

I express my sincerest thanks to my supervisor, Dr. Ahmet M. Hava, for his guidance, support, encouragement, and valuable contributions throughout my graduate education.

I would like to express my deepest gratitude to my family for their support.

I would like to express my deepest gratitude and respect to Dr. Tsuneo Kume for his valuable comments and suggestions.

I would like to thank Mr. Turgay Halimler for providing the Yaskawa Varispeed G7 voltage source inverter utilized in this thesis.

Special appreciation goes to Ömer Göksu for the cooperation in the hardware of my thesis; to Bülent Üstüntepe for his helps in DSP software coding; and to Eyyüp Demirkutlu for reading and editing my thesis.

I would like to thank my reasearch groupmates Osman Selçuk Şentürk, Hasan Özkaya, Mutlu Uslu, Süleyman Çetinkaya, Mehmet Can Kaya, and Fuat Onur Bağlan for their help and support. I would also like to thank my officemates Atilla Dönük, Naci Genç, and Seda Karadeniz and all my friends for their support.

I wish to thank to the Departmant of Electrical and Electronics Engineering faculty and staff for their help throughout my graduate study.

## **TABLE OF CONTENTS**

| ABSTRACT          | iv   |

|-------------------|------|

| ÖZ                | v    |

| DEDICATION        | vii  |

| ACKNOWLEDGMENTS   | viii |

| TABLE OF CONTENTS | ix   |

| LIST OF FIGURES   | xii  |

| LIST OF TABLES    | xxiv |

## CHAPTER

| 1. | INTRODUCTION                                       | 1  |

|----|----------------------------------------------------|----|

|    | 1.1. Adjustable Speed Drives                       | 1  |

|    | 1.2. Common Mode Voltage and Current               | 6  |

|    | 1.3. Scope of The Thesis                           | 9  |

|    |                                                    |    |

| 2. | PWM METHODS AND CHARACTERISTICS                    | 11 |

|    | 2.1. Introduction                                  | 11 |

|    | 2.2. PWM Basics, Scalar and Vector Implementations | 13 |

|    | 2.3. Standard PWM Methods                          | 16 |

|    | 2.3.1. Space Vector PWM (SVPWM)                    | 18 |

|    | 2.3.2. Discontinuous PWM (DPWM)                    | 20 |

|    | 2.4. Reduced Common Mode PWM Methods               | 21 |

|    | 2.4.1. Active Zero State PWM (AZSPWM)              | 22 |

|    | 2.4.2. Remote State PWM (RSPWM)                    | 26 |

|    | 2.4.3. Near State PWM (NSPWM)                      | 30 |

|    | 2.5. Performance Characteristics of PWM Methods                |          |

|----|----------------------------------------------------------------|----------|

|    | 2.5.1. Voltage Linearity                                       |          |

|    | 2.5.2. Output Current Waveform Quality                         | 39       |

|    | 2.5.3. Inverter DC Link Current Ripple                         | 51       |

|    | 2.5.4. Inverter Output Line-to-Line Voltage Characteristics    |          |

|    | 2.6. Combined Algorithm of PWM Methods                         | 59       |

|    | 2.7. Summary                                                   | 60       |

|    |                                                                |          |

| 3. | INPUT AND OUTPUT CURRENT RIPPLE PERFORMANCE ANAI               | LYSIS OF |

|    | PWM METHODS BY MEANS OF COMPUTER SIMULATIONS                   | 63       |

|    | 3.1. Introduction                                              | 63       |

|    | 3.2. Adjustable Speed Drive Simulation Model                   | 64       |

|    | 3.3. Simulation Results                                        | 67       |

|    | 3.3.1. Simulation Results at $M_i = 0.61$                      | 68       |

|    | 3.3.2. Simulation Results at $M_i = 0.9$                       |          |

|    | 3.4. Simulations of the Combined Algorithm                     | 104      |

|    | 3.5. Summary                                                   | 110      |

|    |                                                                |          |

| 4. | COMMON MODE VOLTAGE AND COMMON MODE CURRENT                    | 114      |

|    | 4.1. Introduction                                              | 114      |

|    | 4.2. CMV in Different Inverter Topologies                      | 115      |

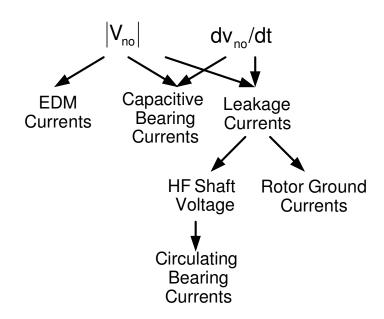

|    | 4.3. Common Mode Current Generating Mechanisms and The Bearing | Currents |

|    |                                                                | 118      |

|    | 4.4. Factors Effecting CMCs                                    | 123      |

|    | 4.5. Common Mode Voltage and Current Mitigation Methods        | 124      |

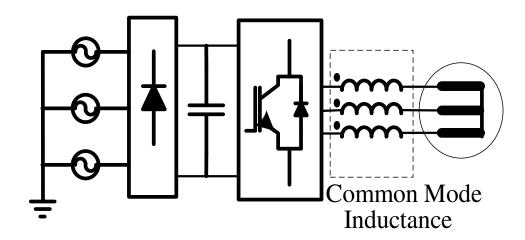

|    | 4.5.1. Common Mode Inductance (CMI)                            | 124      |

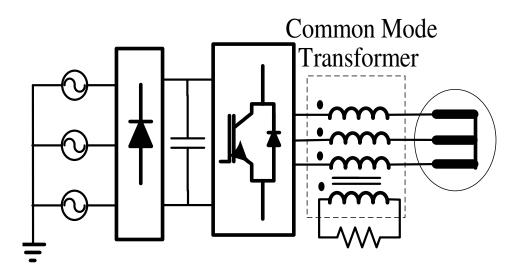

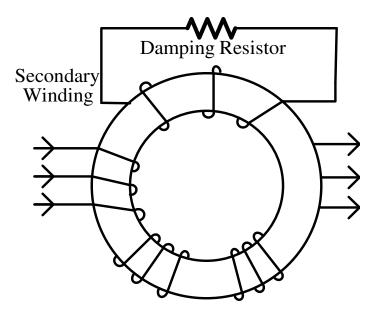

|    | 4.5.2. Common Mode Transformer (CMT)                           | 128      |

|    | 4.5.3. RLC Type Passive CM Filter                              | 132      |

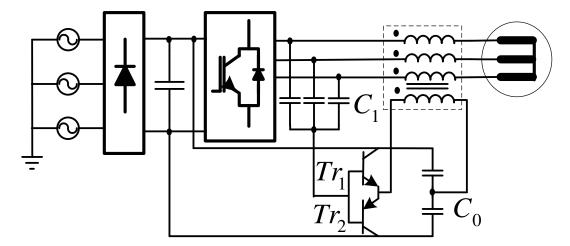

|    | 4.5.4. Active Common Mode Filter                               | 133      |

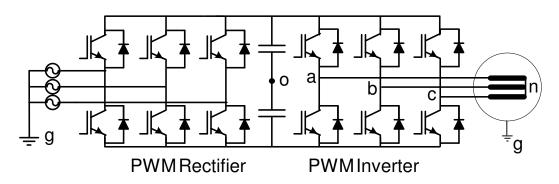

|    | 4.5.5. Utilizing PWM Rectifier                                 | 134      |

|    | 4.6. CMV/CMC Reduction By Means of PWM Pulse Pattern Modifica  | tion 136 |

|    | 4.7. Summary                                                   | 136      |

| 5. | EXPERIN     | IENTAL WORK                                               |                         |

|----|-------------|-----------------------------------------------------------|-------------------------|

|    | 5.1. Introd | luction                                                   |                         |

|    | 5.2. Adjus  | stable Speed Drive System Hardware                        | 139                     |

|    | 5.3. PWM    | I Signal Generation                                       |                         |

|    | 5.4. CMV    | C/CMC Experimental Results without Passive Filters        |                         |

|    | 5.4.1.      | CMV/CMC Experimental Results without Passive Filters      | at M <sub>i</sub> =0.8  |

|    |             |                                                           |                         |

|    | 5.4.2.      | CMV/CMC Experimental Results without Passive Filters      | at M <sub>i</sub> =0.61 |

|    |             |                                                           | 153                     |

|    | 5.4.3.      | CMV/CMC Performance Evaluation without Passive Filter     | ers 158                 |

|    | 5.5. CMV    | C/CMC Experimental Results with Common Mode Inductor      | s 159                   |

|    | 5.5.1.      | CMV/CMC Experimental Results with CMI-2                   | 164                     |

|    | 5.5.2.      | CMV/CMC Experimental Results with Common Mode T           | ransformer              |

|    |             |                                                           | 169                     |

|    | 5.5.3.      | CMV/CMC Performance Evaluation of Passive Filters         | 174                     |

|    | 5.6. CMV    | C/CMC Experiments of Commercial Inverters                 |                         |

|    | 5.6.1.      | CMV/CMC Experiments for Commercial Two-Level Inve         | erter 177               |

|    | 5.6.2.      | CMV/CMC Experiments for Commercial Three-Level N          | PC Inverter             |

|    |             |                                                           |                         |

|    | 5.6.3.      | CMV/CMC Performance Evaluation of The Commercial          | VSIs 191                |

|    | 5.7. Expe   | rimental Investigation of The Motor Terminal Overvoltages | s In Long               |

|    | Cable       | e Applications                                            | 192                     |

|    | 5.8. Modi   | fication Algorithm for AZSPWM1 (MAZSPWM)                  |                         |

|    | 5.9. Labor  | ratory Experiments of Combined Algorithm                  |                         |

|    | 5.10. Sum   | ımary                                                     | 229                     |

|    |             |                                                           |                         |

| 6. | CONCLUS     | SIONS                                                     |                         |

|    |             |                                                           |                         |

| RF | EFERENCE    | ES                                                        |                         |

|    |             |                                                           |                         |

| AI | PENDIX.     |                                                           |                         |

## LIST OF FIGURES

## FIGURES

| 1.1 The circuit diagram of a three-phase inverter drive with diode rectifier front-end.        |

|------------------------------------------------------------------------------------------------|

|                                                                                                |

| 1.2 Generation method of the PWM signals and the corresponding phase voltage                   |

| waveform for phase "a"                                                                         |

| 1.3 The experimental inverter output phase voltage expanded waveform and the                   |

| corresponding phase current of a 4 kW VSI during the turn-on instant                           |

| 1.4 Simplified common mode equivalent circuit of an inverter drive and an induction            |

| motor7                                                                                         |

| 1.5 Experimental CMV (red) and leakage current (blue) waveforms                                |

| 2.1 Inverter output line-to-line voltage waveform and its fundamental component                |

| when square wave method is utilized                                                            |

| 2.2 Scalar implementation of a PWM method and the resulting output line-to-line                |

| voltages                                                                                       |

| 2.3 Voltage space vectors of the two-level inverter                                            |

| 2.4 Voltage space vectors and $60^{\circ}$ sector definitions: (a) A-type, (b) B-type regions. |

|                                                                                                |

| 2.5 Zero sequence signal injection diagram for PWM methods                                     |

| 2.6 Voltage space vectors of a standard PWM method                                             |

| 2.7 SVPWM reference signal and injected zero sequence signal for $M_i = 0.78$ 19               |

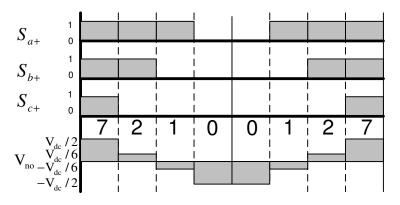

| 2.8 Inverter switch state PWM pulse pattern of SVPWM for the region A1                         |

| 2.9 DPWM1 reference signal and zero sequence injected                                          |

| 2.10 Inverter switch states and the PWM pulse pattern of DPWM1 for the region                  |

| A1∩B2                                                                                          |

| 2.11 The AZSPWM voltage space vectors                                                          |

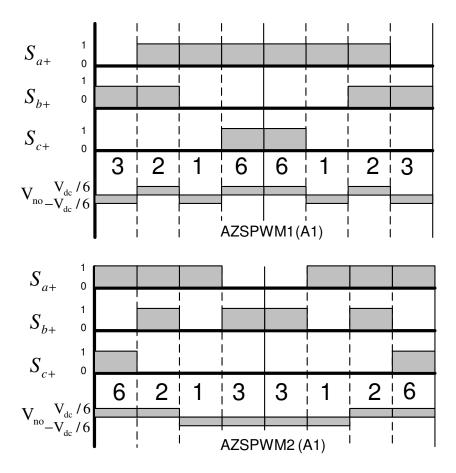

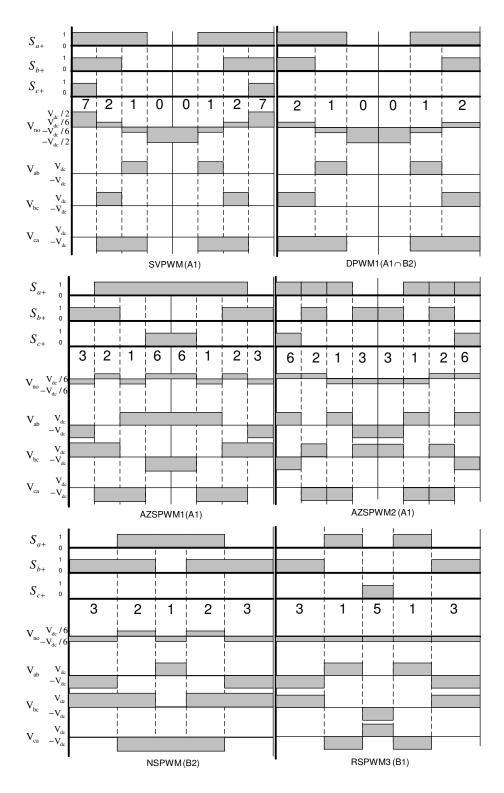

| 2.12 PWM pulse patterns of AZSPWM1 and AZSPWM2 in region A1                                    |

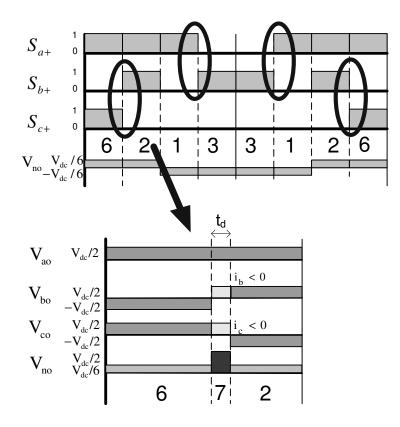

| 2.13 The inverter dead-time related performance problems of AZSPWM226                                          |

|----------------------------------------------------------------------------------------------------------------|

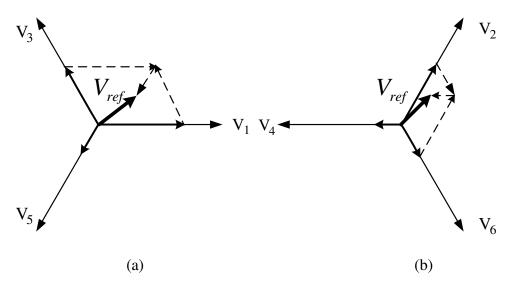

| 2.14 The RSPWM voltage space vectors utilizing: (a) $V_1$ , $V_3$ , $V_5$ (b) $V_2$ , $V_4$ , $V_6$ 27         |

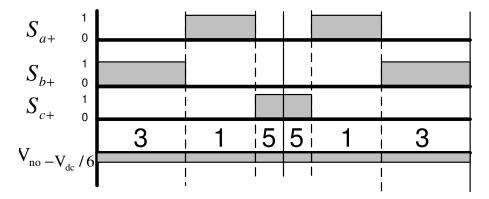

| 2.15 PWM pulse pattern of RSPWM3 in region B1 and the resulting CMV pattern 29                                 |

| 2.16 The inverter dead-time related performance problems of RSPWM3                                             |

| 2.17 Illustration of the NSPWM space vectors for B2                                                            |

| 2.18 Inverter switch state and PWM pulse pattern of NSPWM in region B2                                         |

| 2.19 Scalar implementation of NSPWM (region B2)                                                                |

| 2.20 Voltage linearity regions of: (a) SVPWM, DPWM, AZSPWM1 and                                                |

| AZSPWM2, (b) SPWM, (c) RSPWM1 and RSPWM2, (d) RSPWM3 and (e)                                                   |

| NSPWM                                                                                                          |

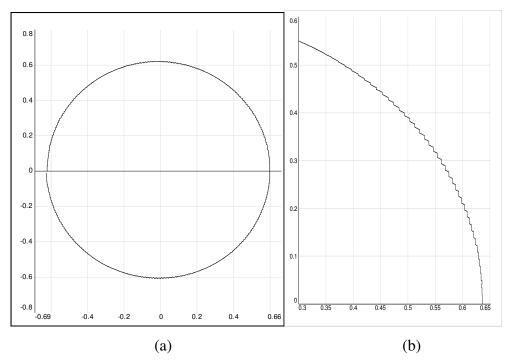

| 2.21 The inverter flux as a function of the applied voltage vectors                                            |

| 2.22 Harmonic flux vectors and harmonic flux trajectories of: (a) SVPWM, (b)                                   |

| AZSPWM1, (c) AZSPWM1, (d) RSPWM and (e) NSPWM41                                                                |

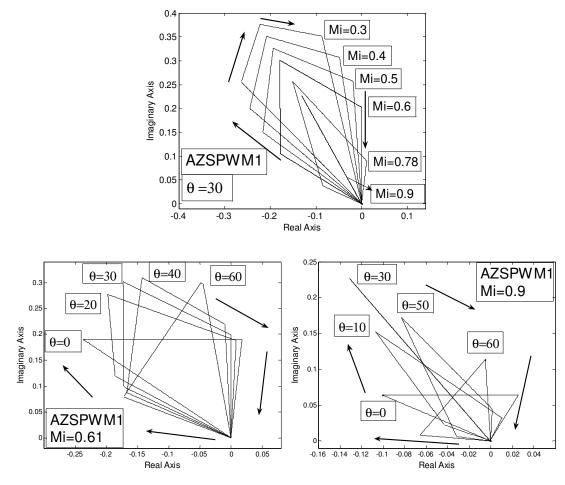

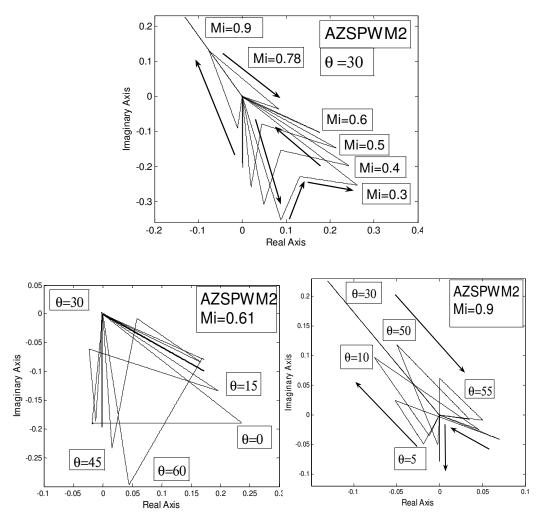

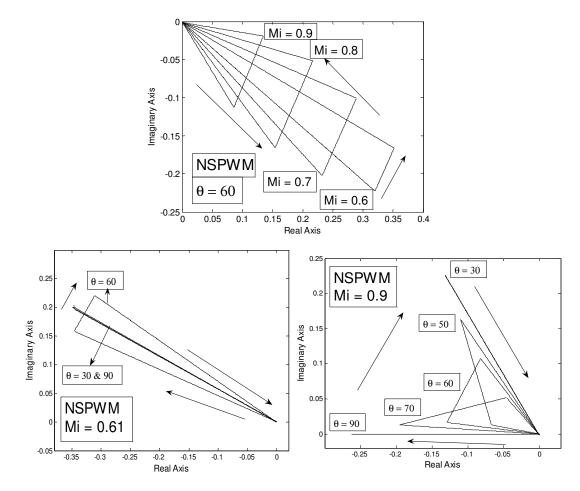

| 2.23 Parametric harmonic flux trajectories of AZSPWM1                                                          |

| 2.24 Parametric harmonic flux trajectories of AZSPWM2                                                          |

| 2.25 Parametric harmonic flux trajectories of RSPWM3                                                           |

| 2.26 Parametric normalized harmonic flux trajectories of NSPWM45                                               |

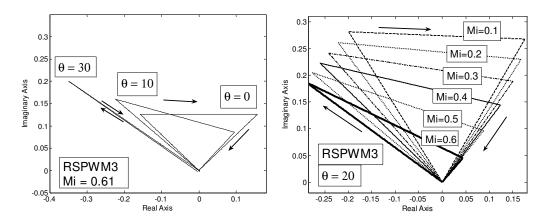

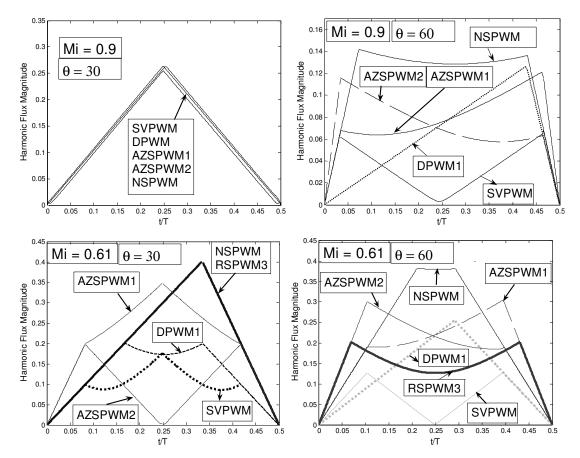

| 2.27 Normalized harmonic flux magnitudes of PWM methods                                                        |

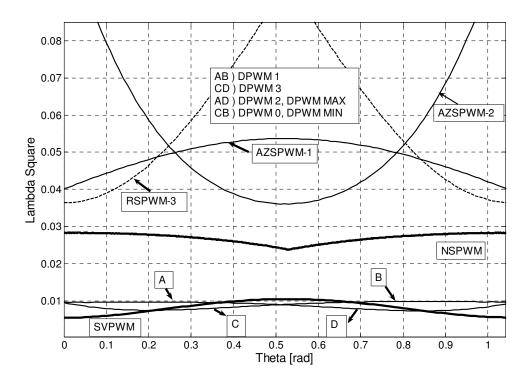

| 2.28 $\lambda^2 = f(\theta)$ spatial variation for M <sub>i</sub> =0.61                                        |

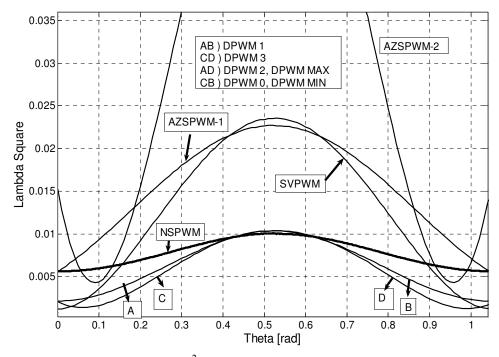

| 2.29 $\lambda^2 = f(\theta)$ spatial variation for M <sub>i</sub> =0.9                                         |

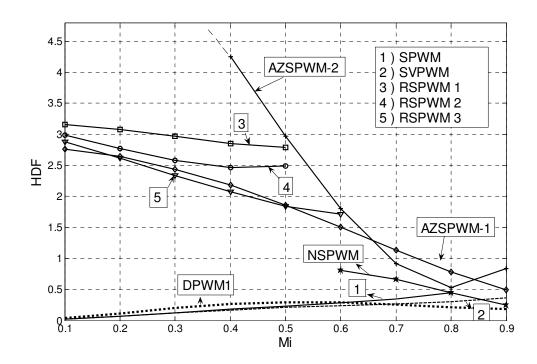

| $2.30 \text{ HDF}=f(M_i)$ for various PWM methods                                                              |

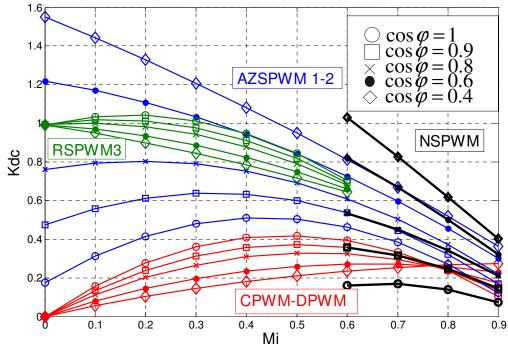

| 2.31 $K_{dc}$ =f(M <sub>i</sub> ,cos $\phi$ ) for various PWM methods                                          |

| 2.32 PWM Pulse pattern and line to line voltages of SVPWM, DPWM1,                                              |

| AZSPWM1, AZSPWM2, NSPWM and RSPWM3 methods55                                                                   |

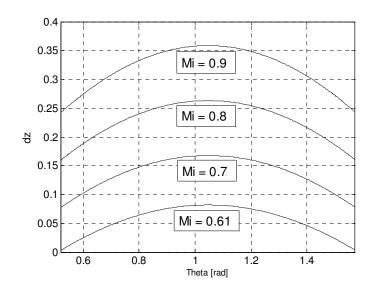

| 2.33 NSPWM Zero voltage time duty cycle $d_{zNSPWM}$ for various $M_i$ for region B257                         |

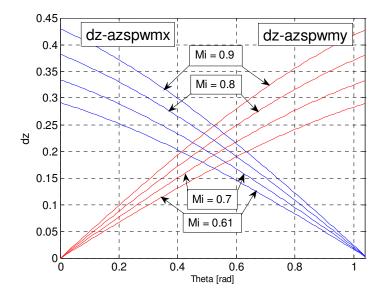

| 2.34 AZSPWM1 Zero voltage time duty cycles $d_{z\text{-}azspwmx}$ and $d_{z\text{-}azspwmy}$ for various $M_i$ |

| for region A157                                                                                                |

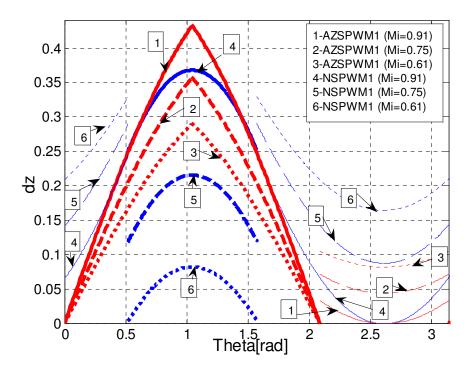

| 2.35 Variation of zero-voltage time interval duty cycle of the line-to-line voltages                           |

| with respect to $M_i$ and $\theta$ (Blue: NSPWM, Red: AZSPWM1)                                                 |

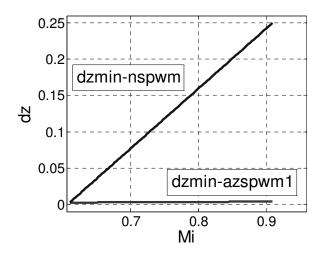

| 2.36 Minimum zero-voltage time duty cycles of NSPWM and AZSPWM159                                              |

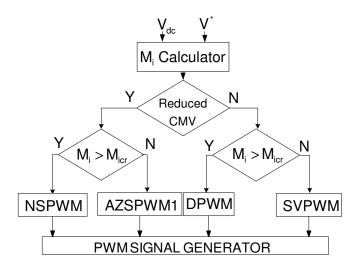

| 2.37 Decision flowchart of the combined modulation algorithm                                                   |

| 3.1 Three-phase ASD simulation model                                                                           |

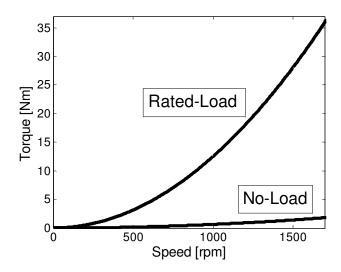

| 3.2 The fan load torque – speed curve for no-load and rated-load operations          |

|--------------------------------------------------------------------------------------|

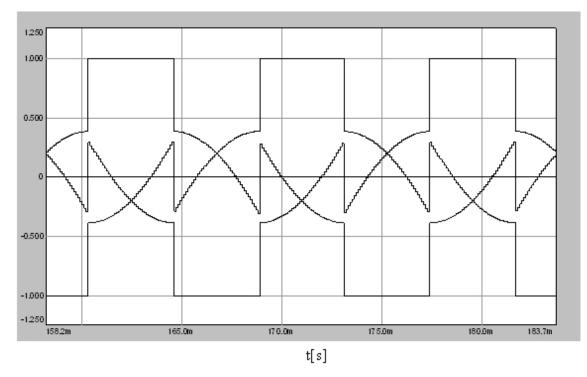

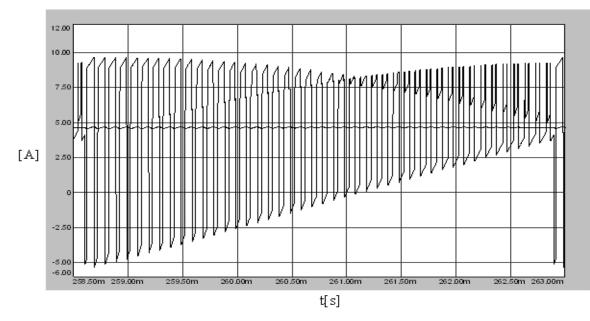

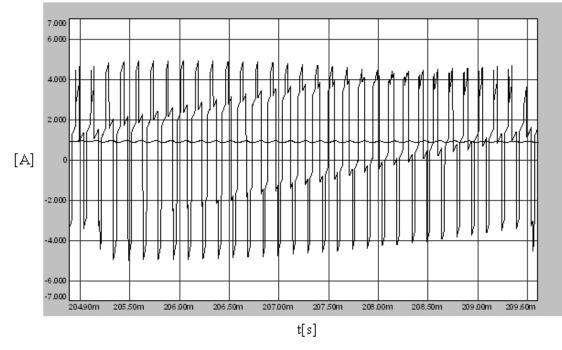

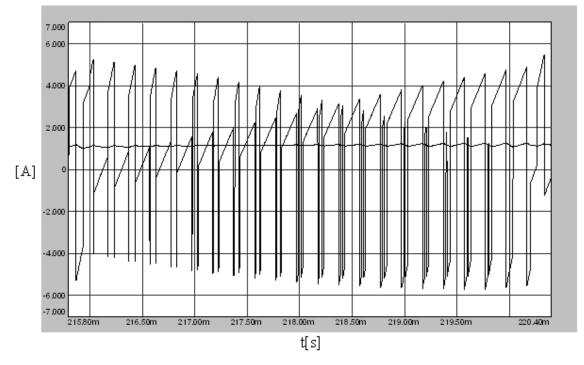

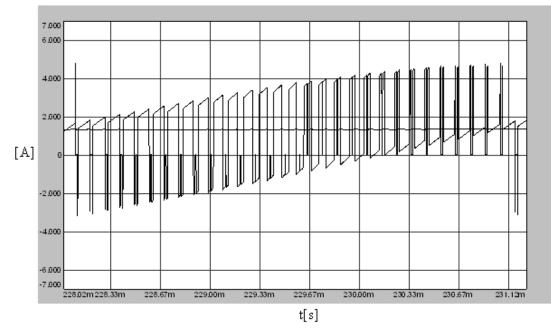

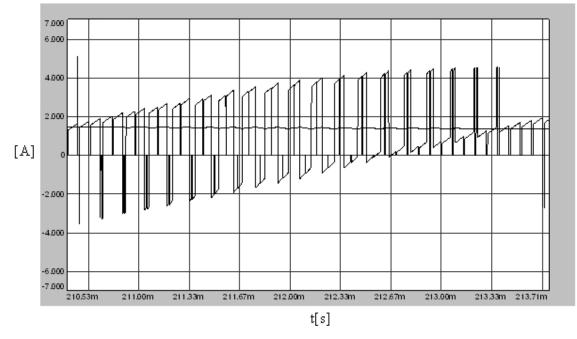

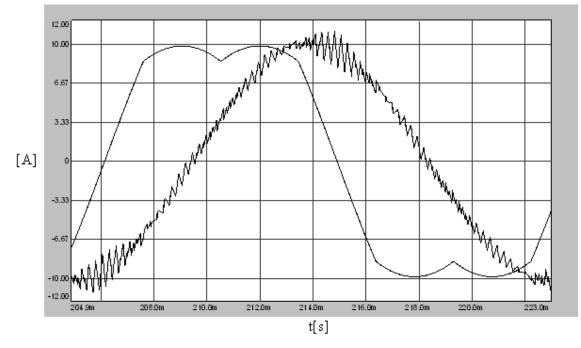

| 3.3 Modulation signals of all three-phases of NSPWM ( $M_i$ =0.61) under no-load 71  |

| 3.4 Load currents of all three-phases of NSPWM ( $M_i$ =0.61) under no-load71        |

| 3.5 CMV of NSPWM ( $M_i$ =0.61) over a fundamental cycle under no-load72             |

| 3.6 The DC link current of NSPWM (M <sub>i</sub> =0.61) under no-load72              |

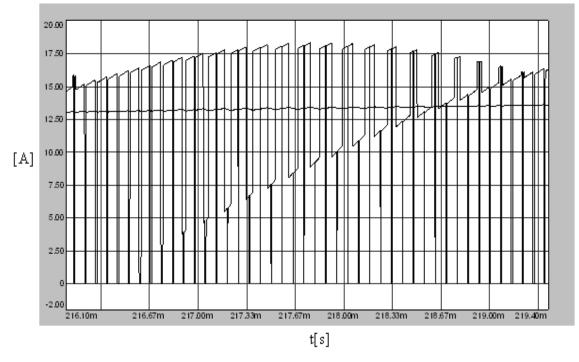

| 3.7 Expanded view of the DC link current of NSPWM ( $M_i=0.61$ ) under no-load and   |

| its average value73                                                                  |

| 3.8 Load current (scale: x2) and the modulation signal (scale: x10) of NSPWM         |

| $(M_i=0.61)$ for one phase under no-load73                                           |

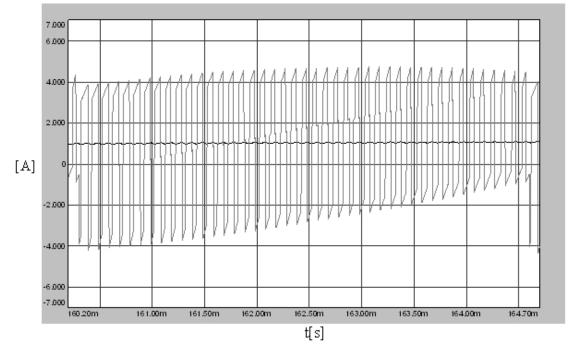

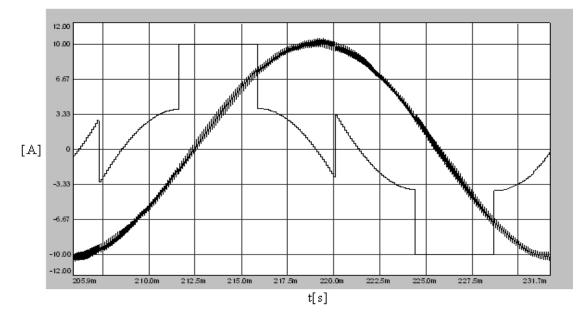

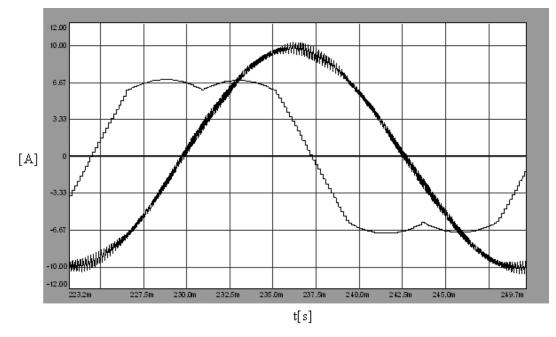

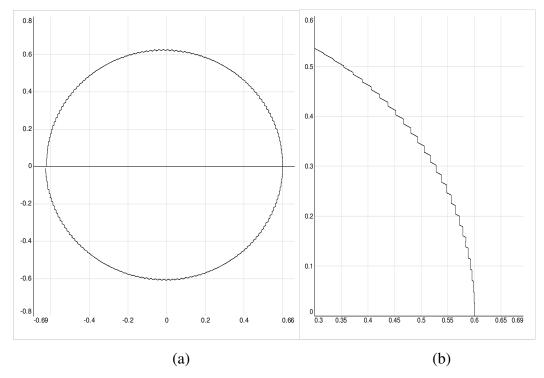

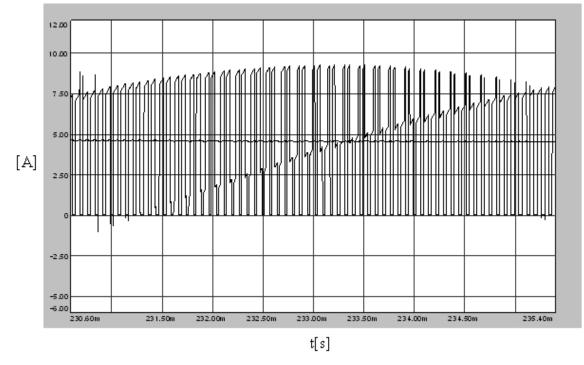

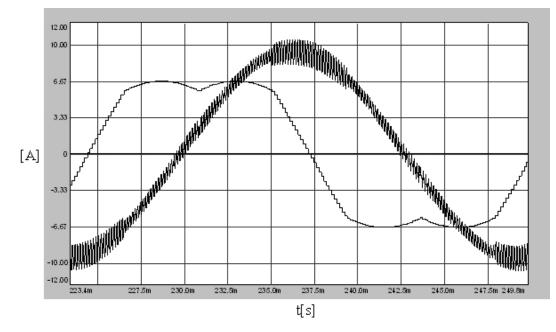

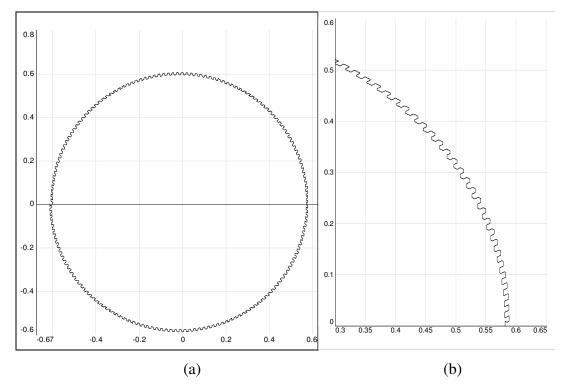

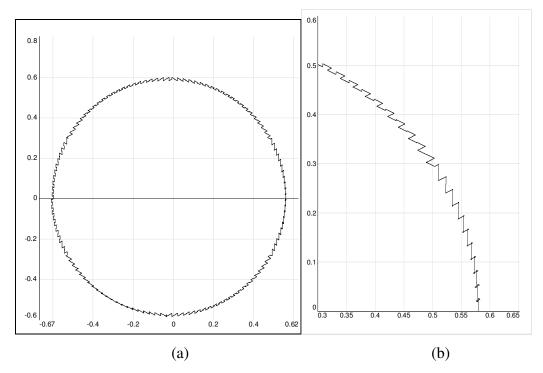

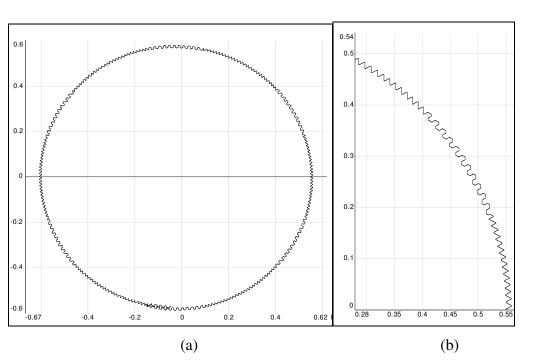

| 3.9 The inverter flux of NSPWM ( $M_i$ =0.61) under no-load (a) and the zoom-in view |

| over a 60° interval (b)74                                                            |

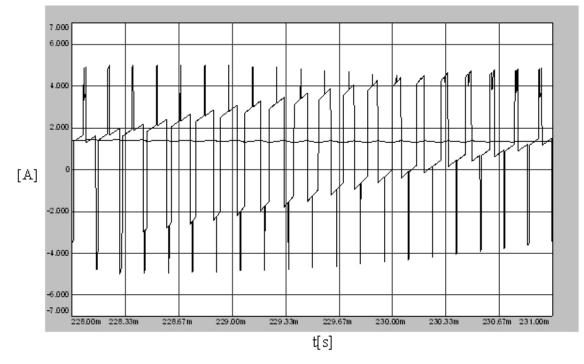

| 3.10 One phase load current and the modulation signal (scale: x10) of NSPWM          |

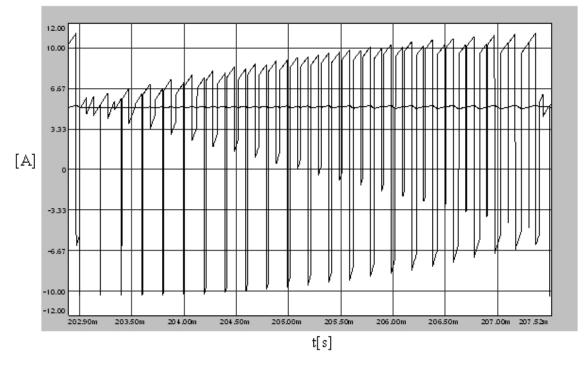

| (M <sub>i</sub> =0.61) under rated-load74                                            |

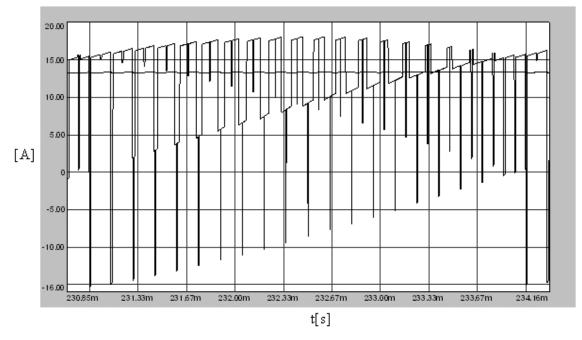

| 3.11 The DC link current of NSPWM ( $M_i$ =0.61) under rated-load and its average    |

| value75                                                                              |

| 3.12 One phase load current (scale: x2) and the modulation signal (scale: x10) of    |

| DPWM1 (M <sub>i</sub> =0.61) under no-load77                                         |

| 3.13 Inverter flux of DPWM1 ( $M_i$ =0.61) under no-load (a) and the zoom-in view    |

| over a 60° interval (b)                                                              |

| 3.14 CMV of DPWM1 (M_i=0.61) over a fundamental cycle under no-load78                |

| 3.15 The DC link current of DPWM1 ( $M_i$ =0.61) under no-load and its average value |

|                                                                                      |

| 3.16 The DC link current of DPWM1 ( $M_i$ =0.61) under rated-load and its average    |

| value79                                                                              |

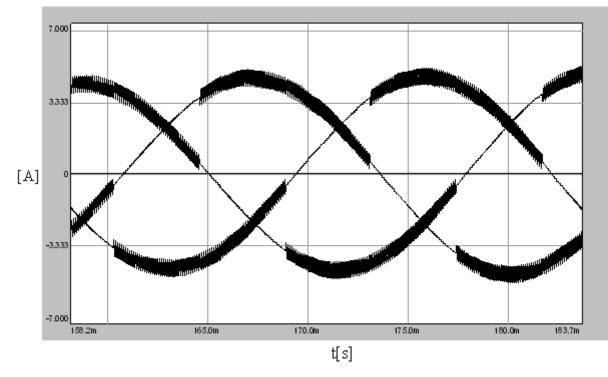

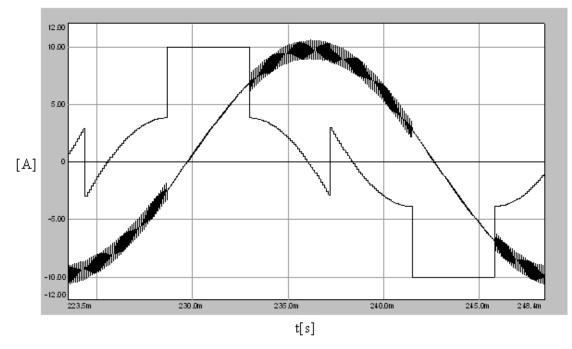

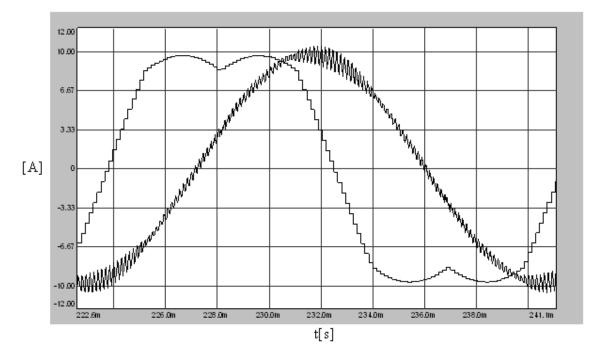

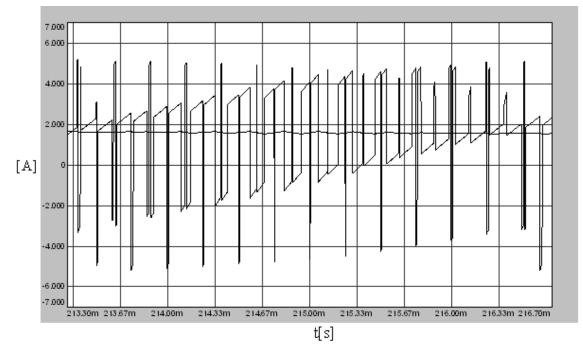

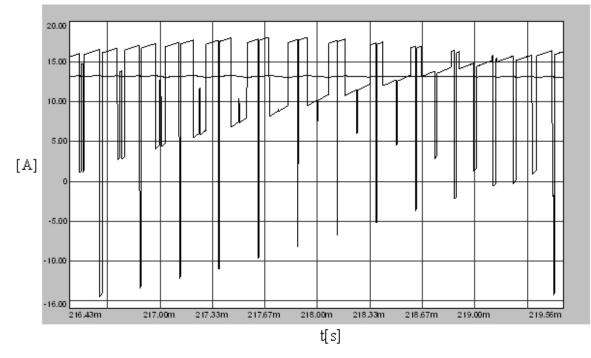

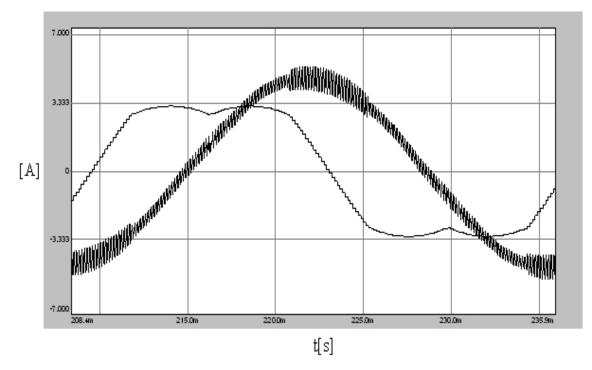

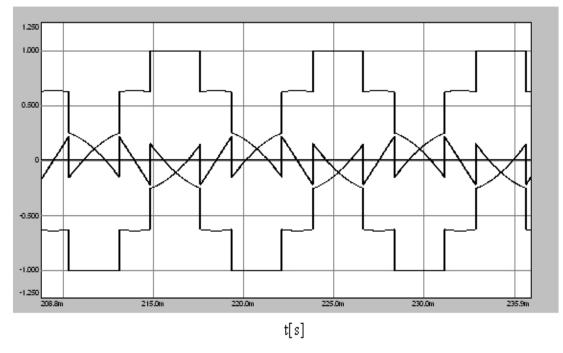

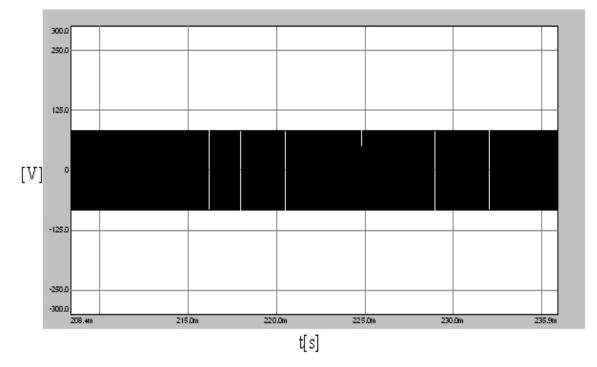

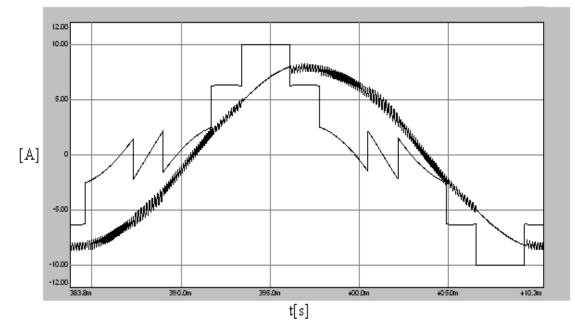

| 3.17 The modulation signals (top), phase currents (center), and switch logic signals |

| (bottom) of NSPWM (left) and DPWM1 (right) at $M_i$ =0.61 under rated-load 80        |

| 3.18 Voltage space vectors and harmonic voltage vectors of (a) DPWM1 (b)             |

| NSPWM for $0^{\circ} < \theta < 30^{\circ}$                                          |

| 3.19 One phase load current (scale: x2) and the modulation signal (scale: x10) of    |

| SVPWM (M <sub>i</sub> =0.61) under no-load                                           |

| 3.20 Inverter flux of SVPWM ( $M_i$ =0.61) under no-load (a) and the zoom-in view    |

| over a 60° interval (b)                                                              |

| 3.21 | CMV of SVPWM ( $M_i$ =0.61) over a fundamental cycle under no-load                     | 2 |

|------|----------------------------------------------------------------------------------------|---|

| 3.22 | The DC link current of SVPWM ( $M_i$ =0.61) under no-load and its average value        | ) |

|      |                                                                                        | 3 |

| 3.23 | The DC link current of SVPWM (M <sub>i</sub> =0.61) under rated-load and its average   |   |

|      | value                                                                                  | 3 |

| 3.24 | One phase load current (scale: x2) and the modulation signal (scale: x10) of           |   |

|      | AZSPWM1 (M <sub>i</sub> =0.61) under no-load                                           | 5 |

| 3.25 | Inverter flux of AZSPWM1 ( $M_i$ =0.61) under no-load (a) and the zoom-in view         |   |

|      | over a 60° interval (b)                                                                | 6 |

| 3.26 | CMV of AZSPWM1 ( $M_i$ =0.61) over a fundamental cycle under no-load 8                 | 6 |

| 3.27 | The DC link current of AZSPWM1 (M <sub>i</sub> =0.61) under no-load and its average    |   |

|      | value                                                                                  | 7 |

| 3.28 | The DC link current of AZSPWM1 (M <sub>i</sub> =0.61) under rated-load and its average |   |

|      | value                                                                                  | 7 |

| 3.29 | One phase load current (scale: x2) and the modulation signal (scale: x10) of           |   |

|      | AZSPWM2 (M <sub>i</sub> =0.61) under no-load                                           | 8 |

| 3.30 | Inverter flux of AZSPWM2 ( $M_i$ =0.61) under no-load (a) and the zoom-in view         |   |

|      | over a 60° interval (b)                                                                | 8 |

| 3.31 | CMV of AZSPWM2 (M <sub>i</sub> =0.61) over a fundamental cycle under no-load 8         | 9 |

| 3.32 | The DC link current of AZSPWM2 (M <sub>i</sub> =0.61) under no-load and its average    |   |

|      | value                                                                                  | 9 |

| 3.33 | The DC link current of AZSPWM2 ( $M_i$ =0.61) under rated-load and its average         |   |

|      | value                                                                                  | 0 |

| 3.34 | One phase load current (scale: x2) of RSPWM3 ( $M_i$ =0.61) under no-load9             | 1 |

| 3.35 | Inverter flux of RSPWM3 ( $M_i$ =0.61) under no-load (a) and the zoom-in view          |   |

|      | over a 60° interval (b)                                                                | 2 |

| 3.36 | CMV of RSPWM3 (M <sub>i</sub> =0.61) over a fundamental cycle under no-load            | 2 |

| 3.37 | The DC link current of RSPWM3 ( $M_i=0.61$ ) under no-load and its average             |   |

|      | value                                                                                  | 3 |

| 3.38 | The DC link current of RSPWM3 (M <sub>i</sub> =0.61) under rated-load and its average  |   |

|      | value                                                                                  | 3 |

| 3.39 One phase load current (scale: x2) and the modulation signal (scale: x10) of                                  |

|--------------------------------------------------------------------------------------------------------------------|

| NSPWM (M <sub>i</sub> =0.9) under no-load                                                                          |

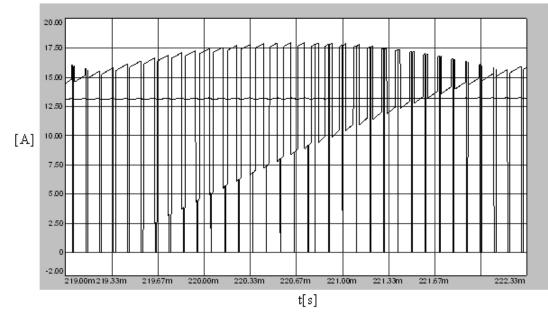

| 3.40 The DC link current of NSPWM ( $M_i$ =0.9) over a fundamental cycle under no-                                 |

| load and its average value                                                                                         |

| 3.41 The DC link current of NSPWM (M <sub>i</sub> =0.9) over a fundamental cycle under                             |

| rated-load and its average value                                                                                   |

| 3.42 One phase load current (scale: x2) and the modulation signal (scale: x10) of                                  |

| DPWM1 ( $M_i$ =0.9) under no-load                                                                                  |

| 3.43 The DC link current of DPWM1 (M <sub>i</sub> =0.9) under no-load and its average value                        |

|                                                                                                                    |

| 3.44 The DC link current of DPWM1 ( $M_i=0.9$ ) under rated-load and its average                                   |

| value                                                                                                              |

| 3.45 One phase load current (scale: x2) and the modulation signal (scale: x10) of                                  |

| SVPWM ( $M_i$ =0.9) under no-load                                                                                  |

| 3.46 The DC link current of SVPWM ( $M_i=0.9$ ) under no-load and its average value                                |

|                                                                                                                    |

| 3.47 The DC link current of SVPWM (M <sub>i</sub> =0.9) under full-load and its average value                      |

|                                                                                                                    |

| 3.48 One phase load current (scale: x2) and the modulation signal (scale: x10) of                                  |

| AZSPWM1 (M <sub>i</sub> =0.9) under no-load                                                                        |

| 3.49 The DC link current of AZSPWM1 (M <sub>i</sub> =0.9) under no-load and its average                            |

| value                                                                                                              |

| 3.50 The DC link current of AZSPWM1 (M <sub>i</sub> =0.9) under rated-load and its average                         |

| value                                                                                                              |

| 3.51 One phase load current (scale: x2) and the modulation signal (scale: x10) of                                  |

| AZSPWM2 ( $M_i$ =0.9) under no-load                                                                                |

| 3.52 The DC link current of AZSPWM2 ( $M_i=0.9$ ) under no-load and its average                                    |

| value                                                                                                              |

| 3.53 The DC link current of AZSPWM2 ( $M_i=0.9$ ) under rated-load and its average                                 |

| value                                                                                                              |

|                                                                                                                    |

| -5.04 Une phase load chilem and the moduliation signal iscale is though the with                                   |

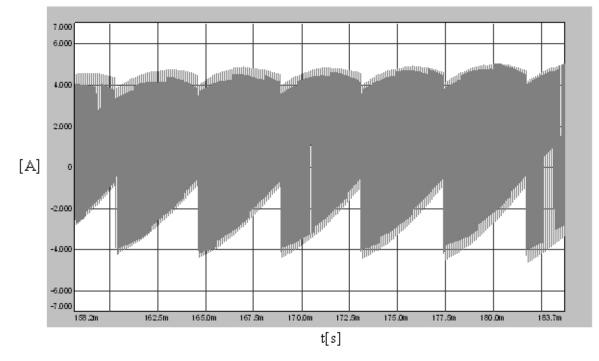

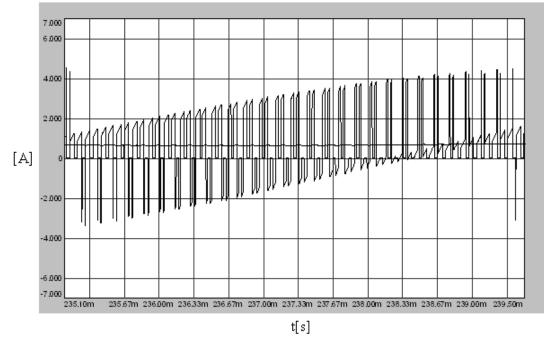

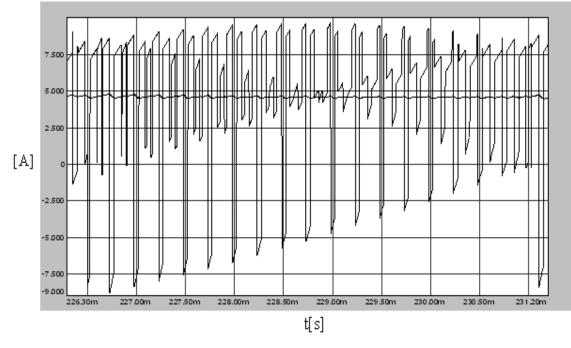

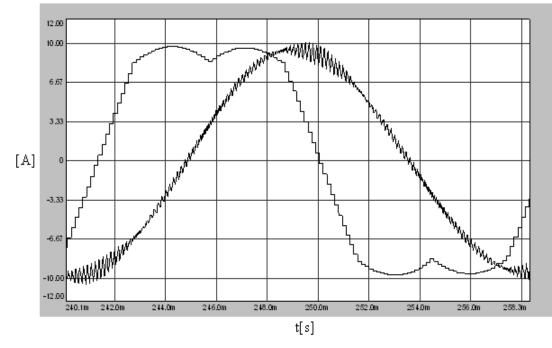

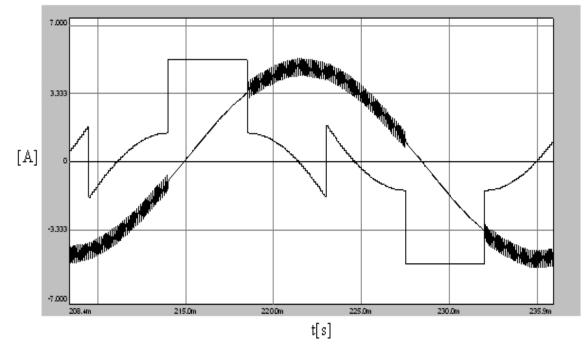

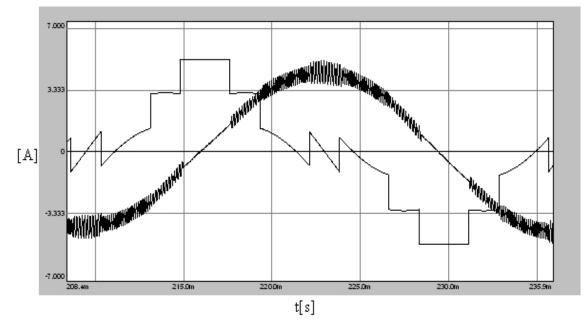

| 3.54 One phase load current and the modulation signal (scale: x5) of NSPWM<br>(M <sub>i</sub> =0.58) under no-load |

| 3.55 One phase load current and the modulation signal (scale: x5) of AZSPWM1             |

|------------------------------------------------------------------------------------------|

| (M <sub>i</sub> =0.58) under no-load                                                     |

| 3.56 The modulation signal of all three phases for the combined algorithm ( $M_i=0.58$ ) |

|                                                                                          |

| 3.57 CMV of the combined algorithm ( $M_i$ =0.58) over a fundamental cycle under no-     |

| load                                                                                     |

| 3.58 One phase load current and the modulation signal (scale: x5) of AZSPWM1             |

| (M <sub>i</sub> =0.58) under no-load                                                     |

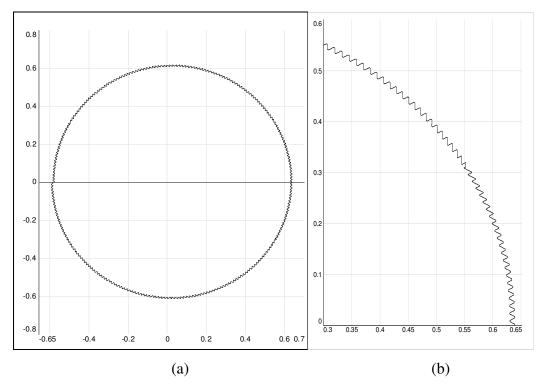

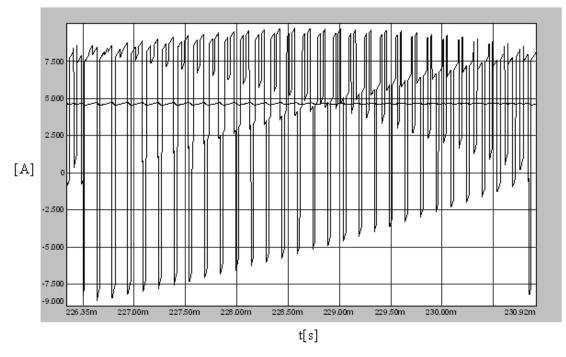

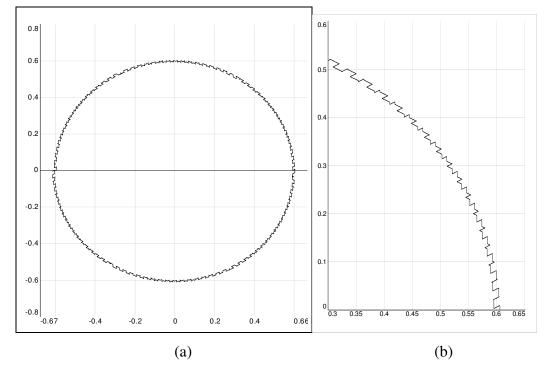

| 3.59 Inverter flux of the combined algorithm ( $M_i=0.58$ ) under no-load (a) and the    |

| zoom-in view over a 60° interval (b)109                                                  |

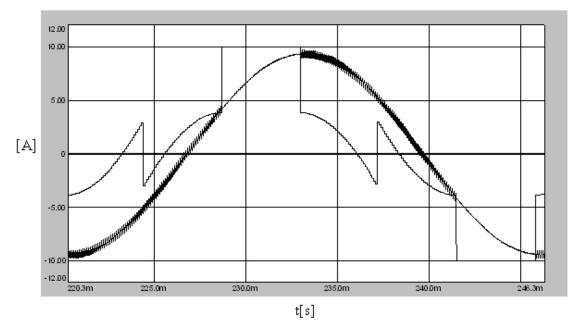

| 3.60 One phase load current and the modulation signal (scale: x10) of the combined       |

| algorithm (M <sub>i</sub> =0.58) under rated-load109                                     |

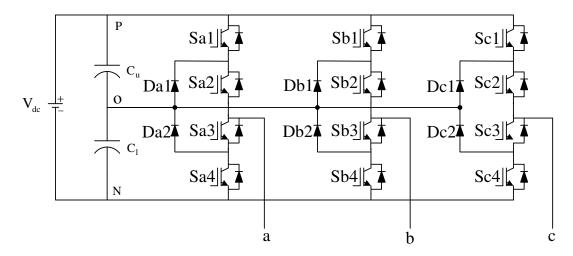

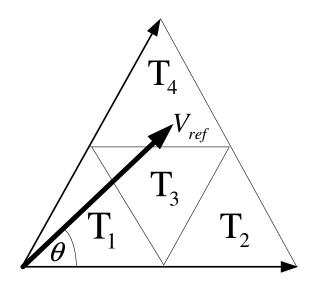

| 4.1 The three-level neutral point clamped VSI topology                                   |

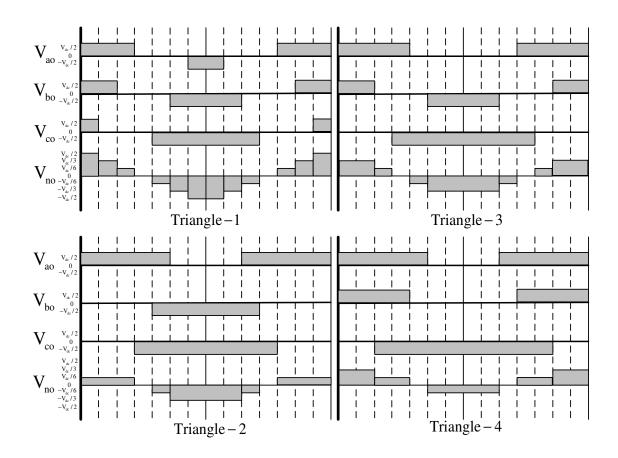

| 4.2 Triangular region definitions for sector A1                                          |

| 4.3 The NPC three-level inverter phase-to-midpoint output voltages and CMV pulse         |

| patterns for NTV-PWM                                                                     |

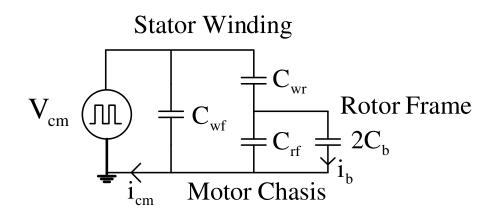

| 4.4 Detailed common mode high frequency equivalent circuit of a three-phase AC           |

| induction motor                                                                          |

| 4.5 Simplified common mode high frequency equivalent circuit of three-phase AC           |

| induction motor drive system                                                             |

| 4.6 Equivalent capacitances between stator winding, rotor frame, and motor chassis       |

|                                                                                          |

| 4.7 Cause-and-effect chains of inverter-induced bearing currents                         |

| 4.8 The utilization of CMI in a motor drive                                              |

| 4.9 A three-phase CMI                                                                    |

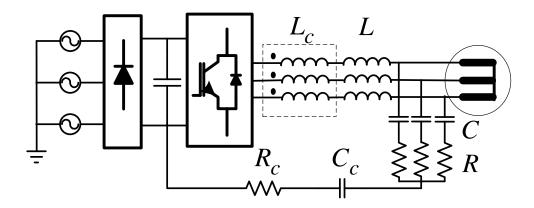

| 4.10 The utilization of a CMT in a motor drive                                           |

| 4.11 Common mode transformer                                                             |

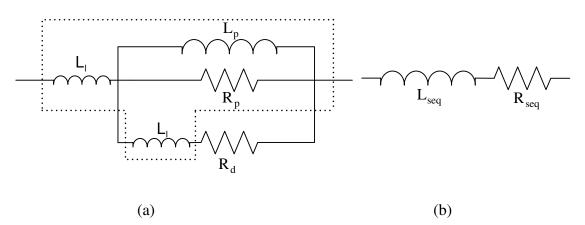

| 4.12 Simplified common mode equivalent circuit of the CMT (a) parallel equivalent,       |

| (b) series equivalent                                                                    |

| 4.13 Utilization of RLC type passive CMC filter in a motor drive                         |

| 4.14 Motor drive diagram with active CMC filter                                          |

|                                                                                          |

| 4.15 A motor drive with PWM rectifier and inverter                                       |

| 5.1 Experimental inverter drive system hardware and the control diagram 141        |

|------------------------------------------------------------------------------------|

| 5.2 The CMV/CMC measurement set-up in the three-phase induction motor drive        |

| system                                                                             |

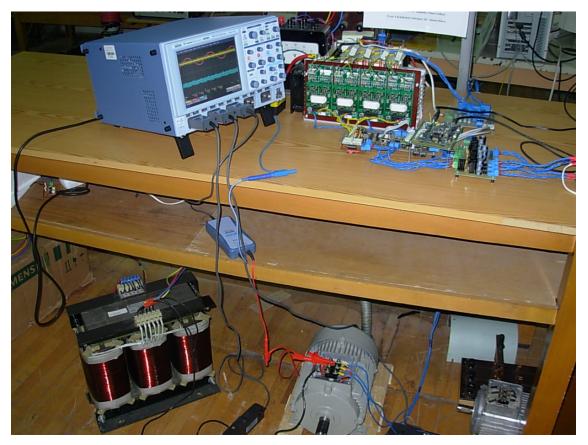

| 5.3 Laboratory experimental set-up 143                                             |

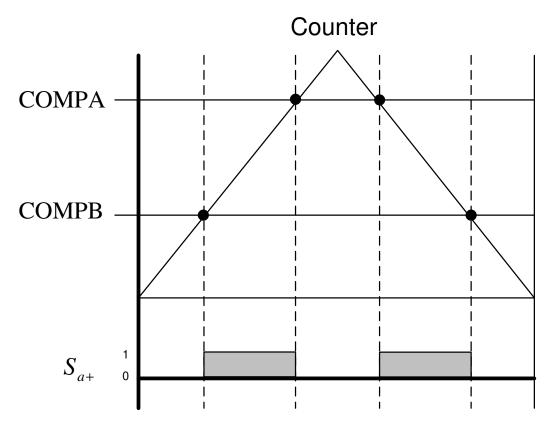

| 5.4 Generation of the PWM pulses by the PWM unit of the TMS320F2808 DSP            |

| utilizing the EPWM unit with two comparator registers COMPA and                    |

| СОМРВ145                                                                           |

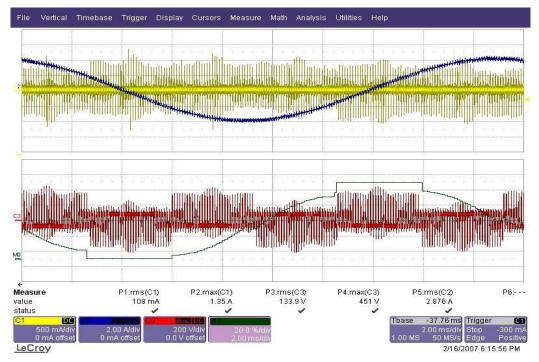

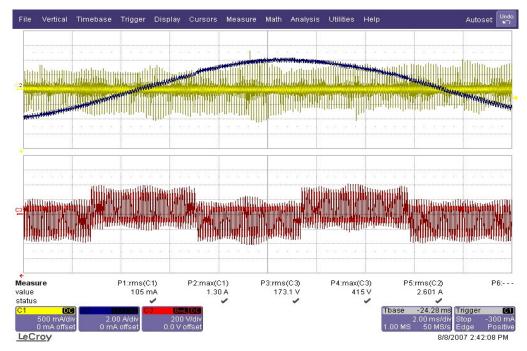

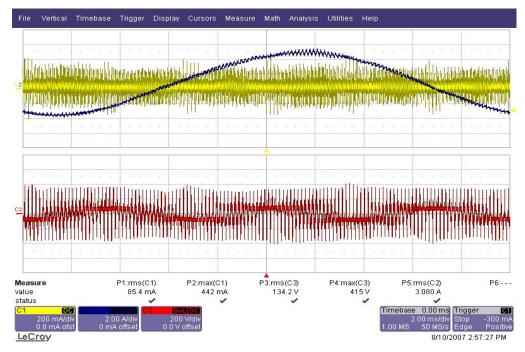

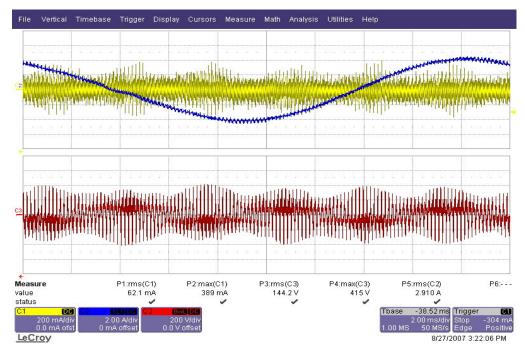

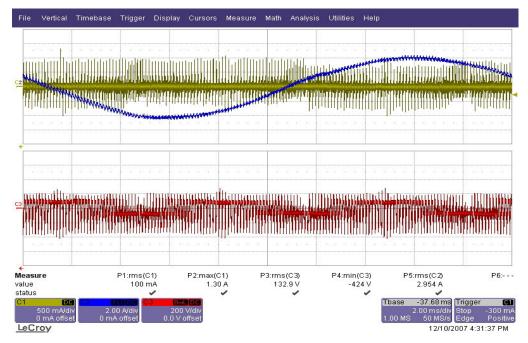

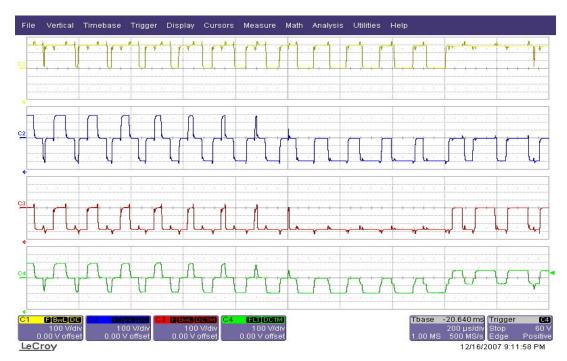

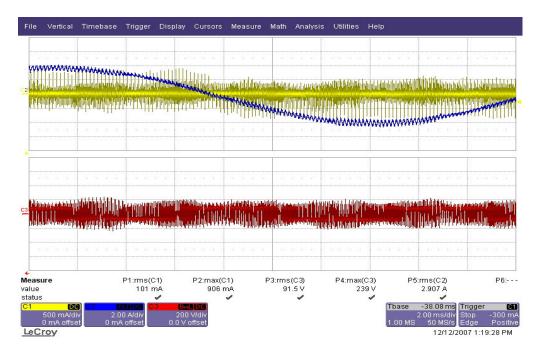

| 5.5 Phase current (blue), CMC (yellow), CMV (red), and modulation signal (green)   |

| waveforms for DPWM1 ( $M_i$ =0.8 and $f_s$ =10 kHz)149                             |

| 5.6 Phase current (blue), CMC (yellow), CMV (red), and modulation signal (green)   |

| waveforms for NSPWM ( $M_i$ =0.8 and $f_s$ =10 kHz)                                |

| 5.7 Phase current (blue), CMC (yellow), CMV (red), and modulation signal (green)   |

| waveforms for SVPWM( $M_i$ =0.8 and $f_s$ =6.6 kHz)                                |

| 5.8 Phase current (blue), CMC (yellow), CMV (red), and modulation signal (green)   |

| waveforms for AZSPWM1( $M_i$ =0.8 and $f_s$ =6.6 kHz)150                           |

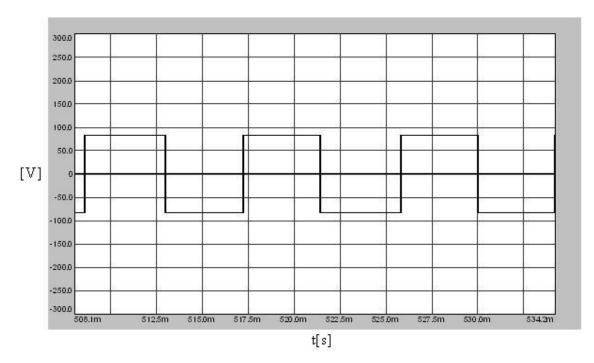

| 5.9 DPWM1 zoom in CMC (blue) and CMV (red) waveforms for $M_i$ =0.8151             |

| 5.10 NSPWM zoom in CMC (blue) and CMV (red) waveforms for $M_i \!\!=\!\! 0.8151$   |

| 5.11 SVPWM zoom in CMC (blue) and CMV (red) waveforms for $M_i$ =0.8152            |

| 5.12 AZSPWM1 zoom in CMC (blue) and CMV (red) waveforms for $M_i {=} 0.8152$       |

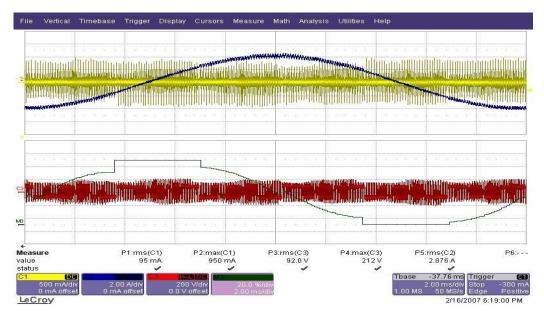

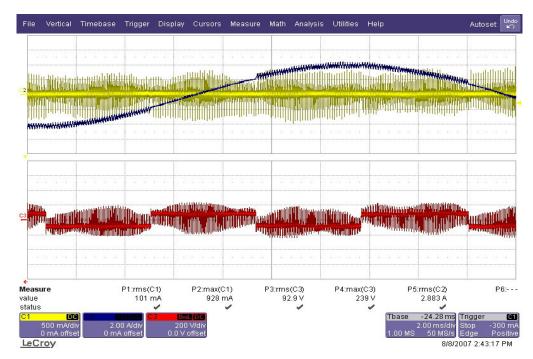

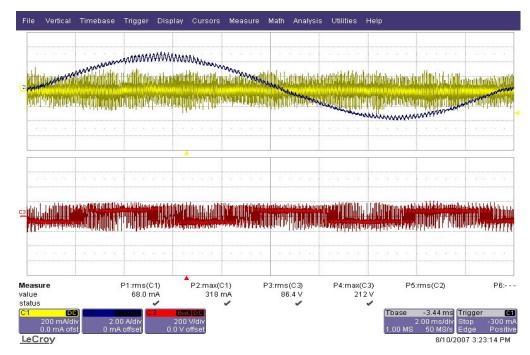

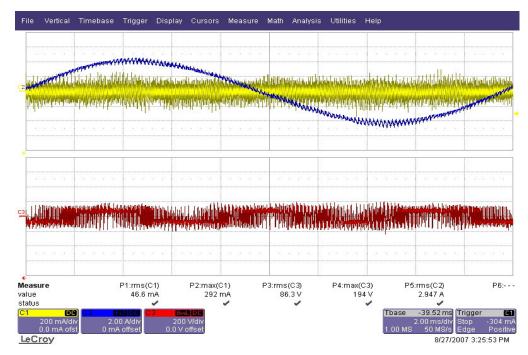

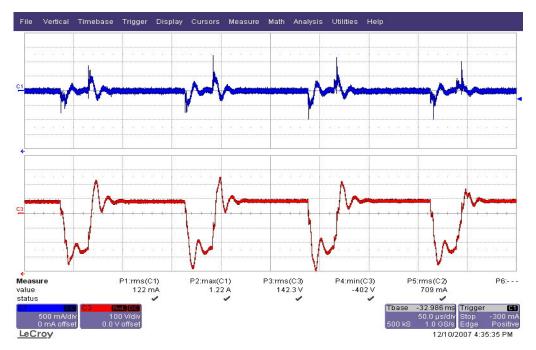

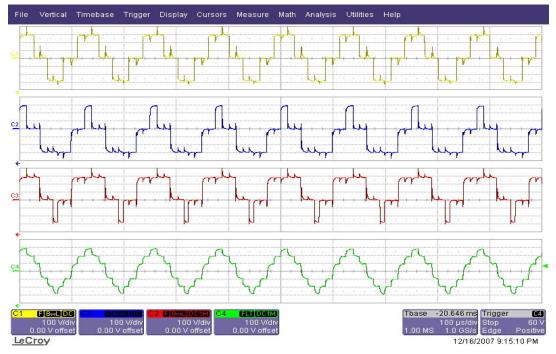

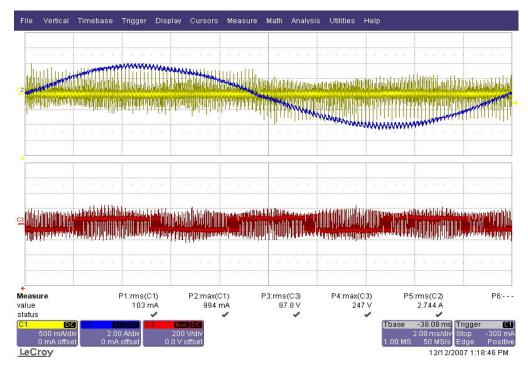

| 5.13 Phase current (blue), CMC (yellow), and CMV (red) waveforms for DPWM1         |

| $(M_i=0.61 \text{ and } f_s=10 \text{ kHz})$                                       |

| 5.14 Phase current (blue), CMC (yellow), and CMV (red) waveforms for NSPWM         |

| $(M_i=0.61 \text{ and } f_s=10 \text{ kHz})$ 154                                   |

| 5.15 Phase current (blue), CMC (yellow), and CMV (red) waveforms for SVPWM         |

| $(M_i=0.61 \text{ and } f_s=6.6 \text{ kHz}).$ 155                                 |

| 5.16 Phase current (blue), CMC (yellow), and CMV (red) waveforms for AZSPWM1       |

| $(M_i=0.61 \text{ and } f_s=6.6 \text{ kHz}).$ 155                                 |

| 5.17 DPWM1 zoom in CMC (blue) and CMV (red) waveforms for $M_i$ =0.61 156          |

| 5.18 NSPWM zoom in CMC (blue) and CMV (red) waveforms for $M_i$ =0.61156           |

| 5.19 SVPWM zoom in CMC (blue) and CMV (red) waveforms for M <sub>i</sub> =0.61 157 |

| 5.20 AZSPWM1 zoom in CMC (blue) and CMV (red) waveforms for $M_i$ =0.61157         |

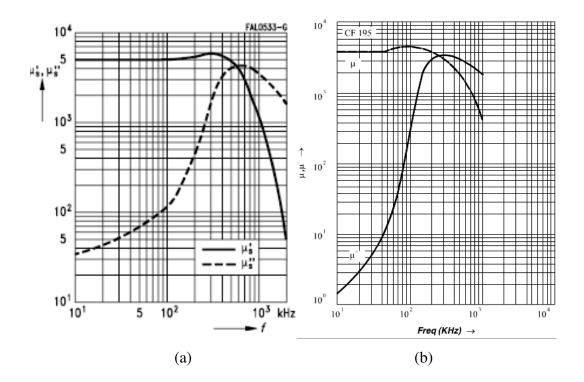

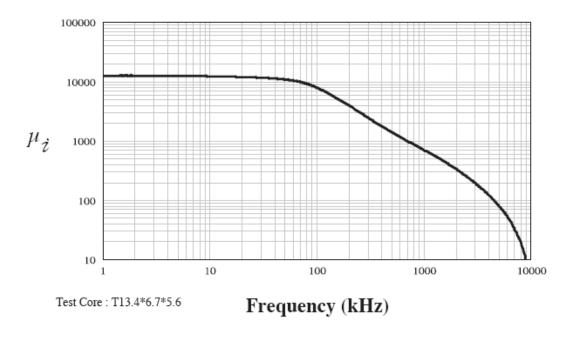

| 5.21 CMIs built and utilized in the experiments                                    |

| 5.22 Initial permeability vs. frequency curves for a) Epcos T-65 (CMI-1); b) Cosmo |

|------------------------------------------------------------------------------------|

| CF195 (CMI-3); c) Acme A121 (CMI-2)                                                |

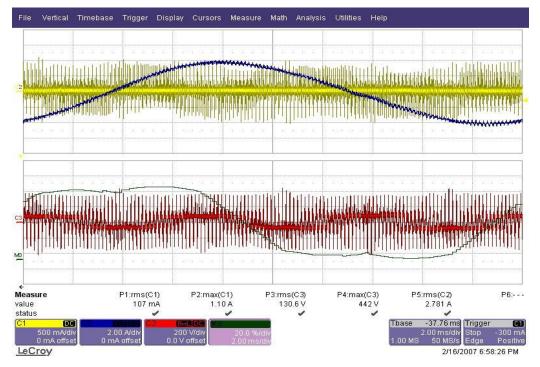

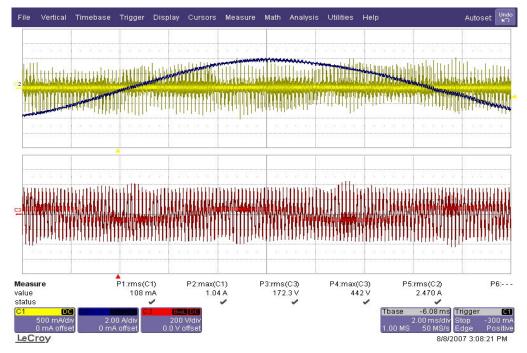

| 5.23 Phase current (blue), CMC (yellow), and CMV (red) waveforms for DPWM1         |

| $(M_i=0.8 \text{ and } f_s=10 \text{ kHz})$ with CMI-2                             |

| 5.24 Phase current (blue), CMC (yellow), and CMV (red) waveforms for NSPWM         |

| $(M_i=0.8 \text{ and } f_s=10 \text{ kHz})$ with CMI-2                             |

| 5.25 Phase current (blue), CMC (yellow), and CMV (red) waveforms for SVPWM         |

| $(M_i=0.8 \text{ and } f_s=6.6 \text{ kHz})$ with CMI-2                            |

| 5.26 Phase current (blue), CMC (yellow), and CMV (red) waveforms for AZSPWM1       |

| $(M_i=0.8 \text{ and } f_s=6.6 \text{ kHz})$ with CMI-2                            |

| 5.27 DPWM1 zoom in CMC (blue) and CMV (red) waveforms for $M_i$ =0.8 with          |

| CMI-2                                                                              |

| 5.28 NSPWM zoom in CMC (blue) and CMV (red) waveforms for $M_i$ =0.8 with          |

| CMI-2                                                                              |

| 5.29 SVPWM zoom in CMC (blue) and CMV (red) waveforms for $M_i$ =0.8 with          |

| CMI-2                                                                              |

| 5.30 AZSPWM1 zoom in CMC (blue) and CMV (red) waveforms for $M_i$ =0.8 with        |

| CMI-2                                                                              |

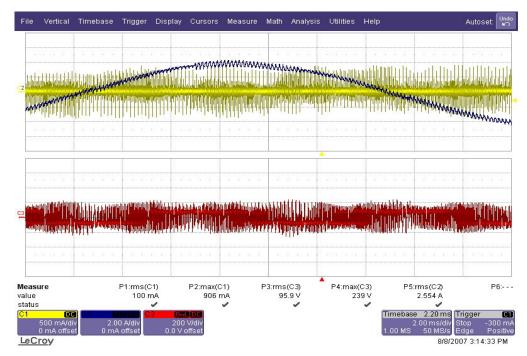

| 5.31 Phase current (blue), CMC (yellow), and CMV (red) waveforms for DPWM1         |

| $(M_i=0.8 \text{ and } f_s=10 \text{ kHz})$ with CMT                               |

| 5.32 Phase current (blue), CMC (yellow), and CMV (red) waveforms for NSPWM         |

| $(M_i=0.8 \text{ and } f_s=10 \text{ kHz})$ with CMT                               |

| 5.33 Phase current (blue), CMC (yellow), and CMV (red) waveforms for SVPWM         |

| $(M_i=0.8 \text{ and } f_s=6.6 \text{ kHz})$ with CMT                              |

| 5.34 Phase current (blue), CMC (yellow), and CMV (red) waveforms for AZSPWM1       |

| $(M_i=0.8 \text{ and } f_s=6.6 \text{ kHz})$ with CMT                              |

| 5.35 DPWM1 zoom in CMC (blue) and CMV (red) waveforms for $M_i$ =0.8 with          |

| СМТ                                                                                |

| 5.36 NSPWM zoom in CMC (blue) and CMV (red) waveforms for $M_i$ =0.8 with          |

| CMT172                                                                             |

| 5.37 SVPWM zoom in CMC (blue) and CMV (red) waveforms for $M_i$ =0.8 with          |

| СМТ173                                                                             |

|                                                                                    |

| 5.20 AZCDWALL                                                                        |

|--------------------------------------------------------------------------------------|

| 5.38 AZSPWM1 zoom in CMC (blue) and CMV (red) waveforms for M <sub>i</sub> =0.8 with |

| CMT                                                                                  |

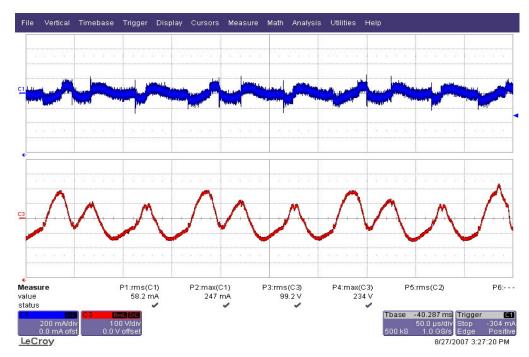

| 5.39 The commercial VSIs utilized in this thesis (a) standard two-level VSI, (b)     |

| three-level NPC VSI                                                                  |

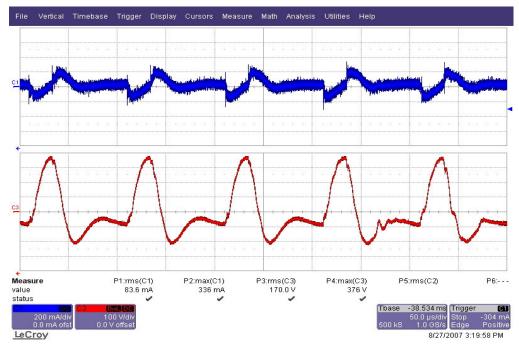

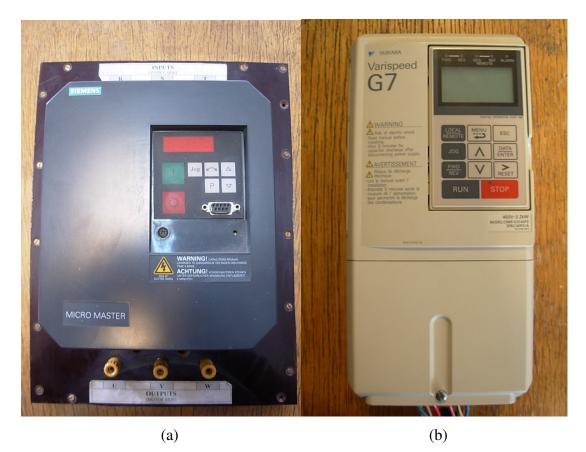

| 5.40 The phase-to-midpoint output voltage (PWM average) of the two-level VSI at a)   |

| $M_i=0.8 \text{ b}) M_i=0.4$ 177                                                     |

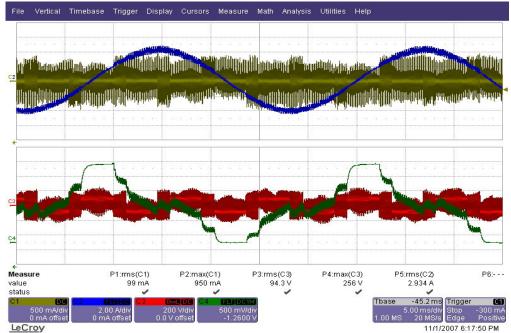

| 5.41 Phase current (blue), CMC (yellow), and CMV (red) waveforms of the              |

| commercial two-level VSI (Mi=0.8)                                                    |

| 5.42 Zoom in CMC (blue) and CMV (red) waveforms for the commercial two-level         |

| VSI (M <sub>i</sub> =0.8)                                                            |

| 5.43 Phase current (blue), CMC (yellow), and CMV (red) waveforms for the             |

| commercial two-level VSI (Mi=0.4)                                                    |

| 5.44 Zoom in CMC (blue) and CMV (red) waveforms for the commercial two-level         |

| VSI (M <sub>i</sub> =0.4)                                                            |

| 5.45 Phase current (blue), CMC (yellow), and CMV (red) waveforms for the             |

| commercial two-level VSI with CMI-2 (M <sub>i</sub> =0.8)                            |

| 5.46 Zoom in CMC (blue) and CMV (red) waveforms for the commercial two-level         |

| VSI with CMI-2 (M <sub>i</sub> =0.8)                                                 |

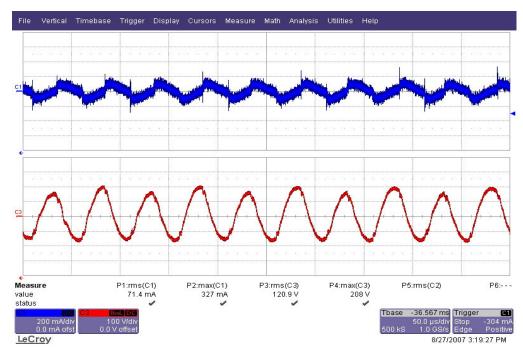

| 5.47 The phase-to-midpoint output voltage (PWM average) of the three-level NPC       |

| VSI at a) $M_i=0.8$ b) $M_i=0.4$                                                     |

| 5.48 The phase-to-midpoint output voltages (top three) and the CMV (bottom) of the   |

| three-level NPC VSI at M <sub>i</sub> =0.7                                           |

| 5.49 The zoom-in view of the phase-to-midpoint output voltages (top three) and the   |

| CMV (bottom) of the three-level NPC VSI at M <sub>i</sub> =0.7                       |

| 5.50 The phase-to-midpoint output voltages (top three) and the CMV (bottom) of the   |

| three-level NPC VSI at M <sub>i</sub> =0.35                                          |

| 5.51 The zoom-in view of the phase-to-midpoint output voltages (top three) and the   |

| CMV (bottom) of the three-level NPC VSI at M <sub>i</sub> =0.35                      |

| 5.52 Phase current (blue), CMC (yellow) and CMV (red) waveforms for the              |

| commercial three-level NPC VSI (M <sub>i</sub> =0.8)                                 |

| 5.53 Zoom in CMC (blue) and CMV (red) waveforms for the commercial three-level       |

| NPC VSI (M <sub>i</sub> =0.8)                                                        |

|                                                                                      |

| 5.54 Phase current (blue), CMC (yellow) and CMV (red) waveforms for the           |

|-----------------------------------------------------------------------------------|

| commercial three-level NPC VSI (M <sub>i</sub> =0.4)                              |

| 5.55 Zoom in CMC (blue) and CMV (red) waveforms for the commercial three-level    |

| NPC VSI (M <sub>i</sub> =0.4)                                                     |

| 5.56 Phase current (blue), CMC (yellow) and CMV (red) waveforms for the           |

| commercial three-level NPC VSI with CMI-2 (Mi=0.8)                                |

| 5.57 Zoom in CMC (blue) and CMV (red) waveforms for the commercial three-level    |

| NPC VSI with CMI-2 (M <sub>i</sub> =0.8)                                          |

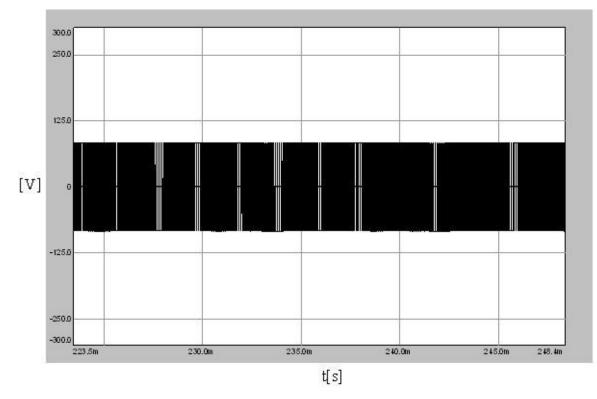

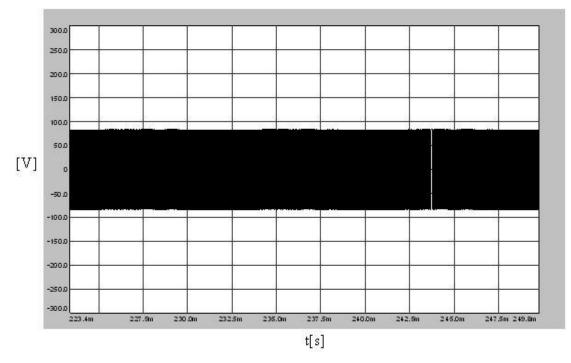

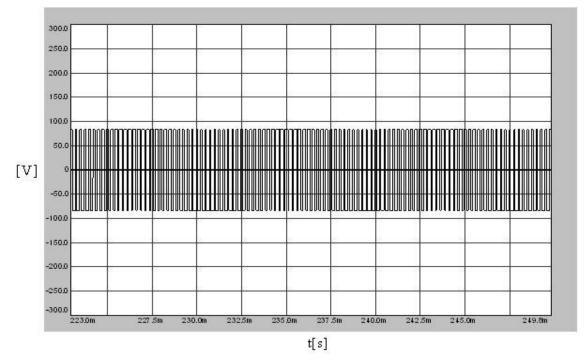

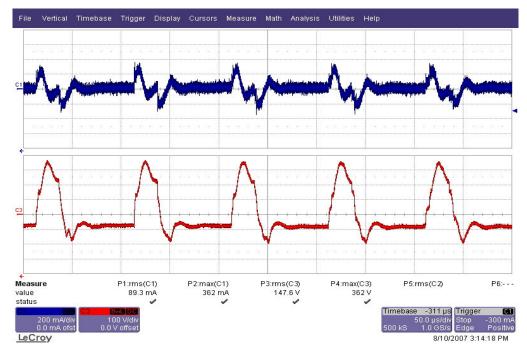

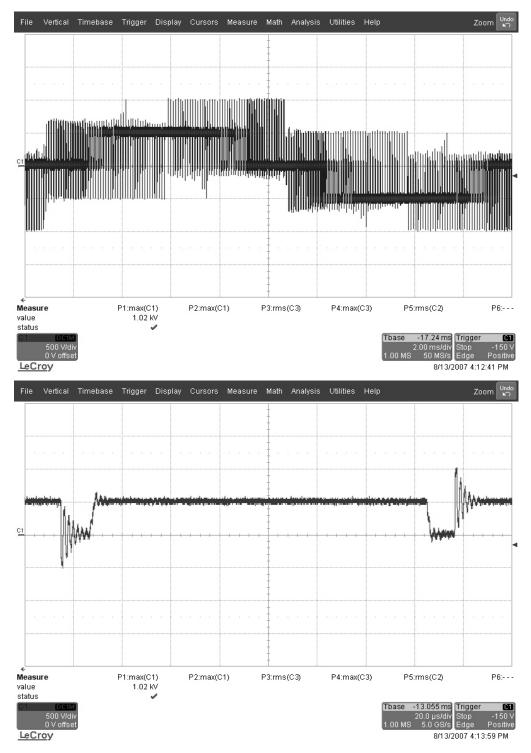

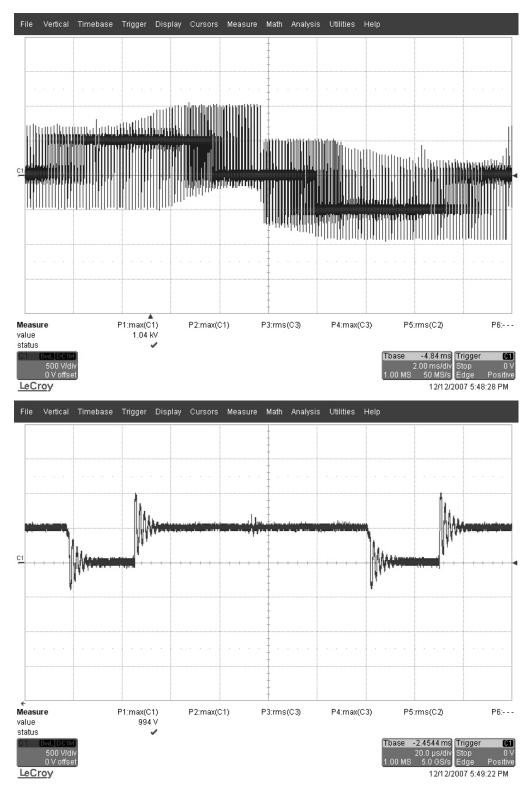

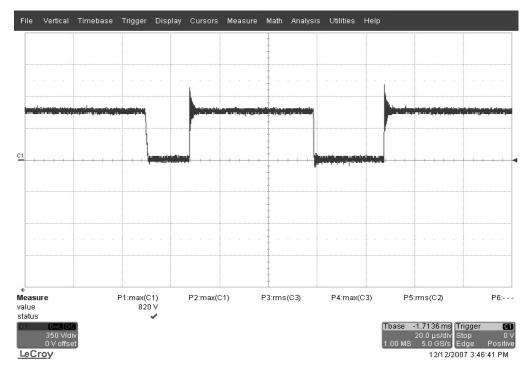

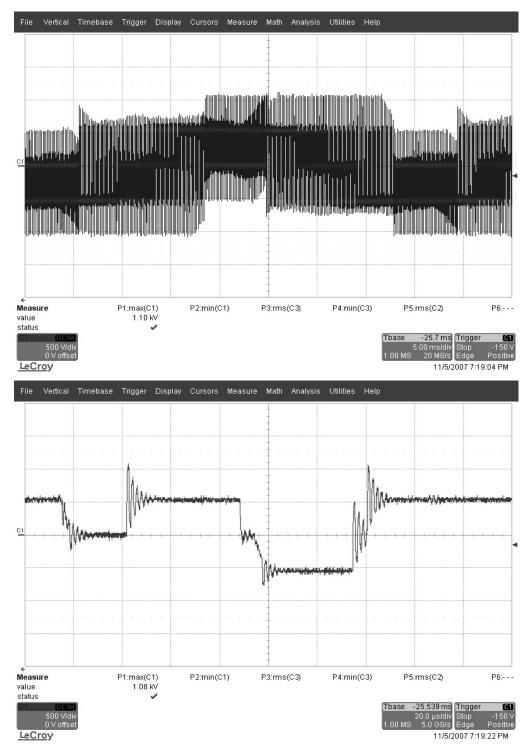

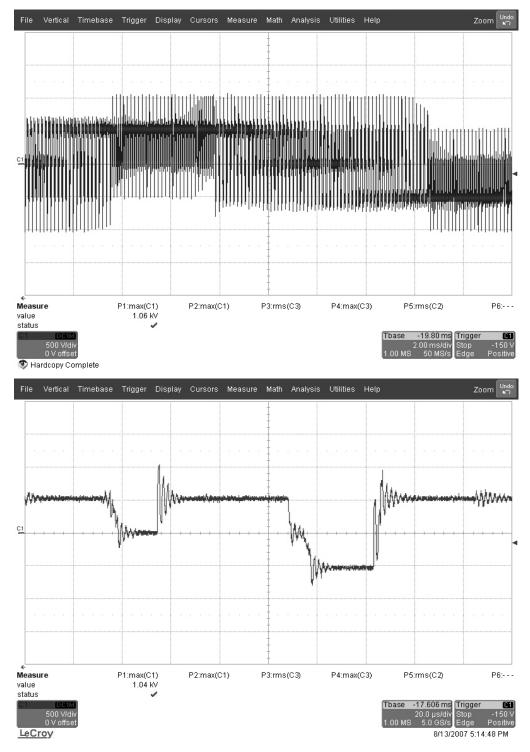

| 5.58 Line-to-line voltage waveform of DPWM1 (top) and its zoom-in view at its     |

| worst overshoot voltage region (bottom) for $M_i=0.8$ and 70m cable               |

| 5.59 Line-to-line voltage waveform of SVPWM (top) and its zoom-in view at its     |

| worst overshoot voltage region (bottom) for $M_i=0.8$ and 70m cable               |

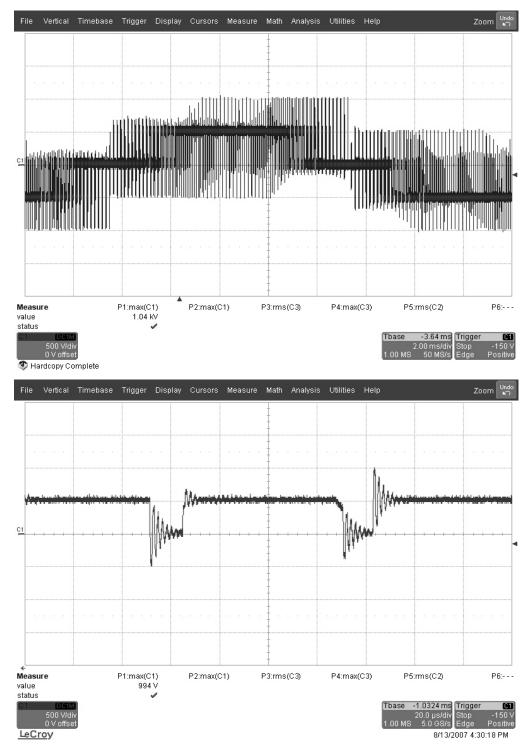

| 5.60 Line-to-line voltage waveform of NSPWM (top) and its zoom-in view at its     |

| worst overshoot voltage region (bottom) for $M_i=0.61$ and 70m cable              |

| 5.61 Line-to-line voltage waveform of NSPWM (top) and its zoom-in view at its     |

| worst overshoot voltage region (bottom) for $M_i=0.8$ and 70m cable               |

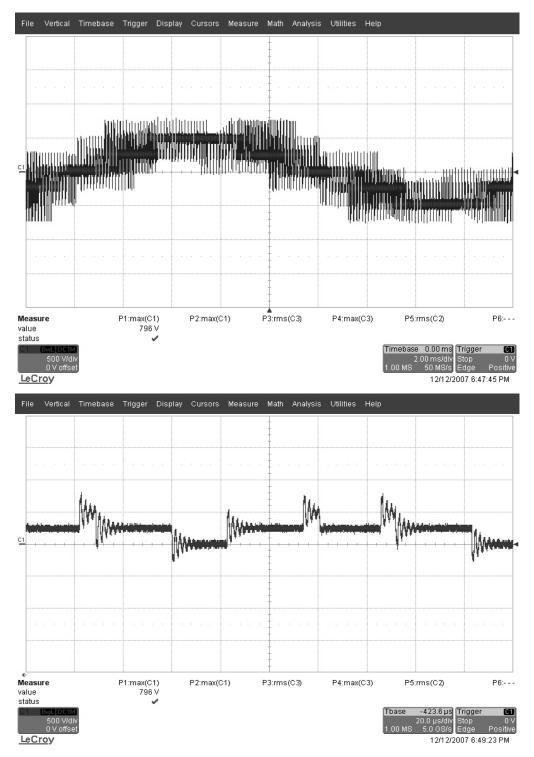

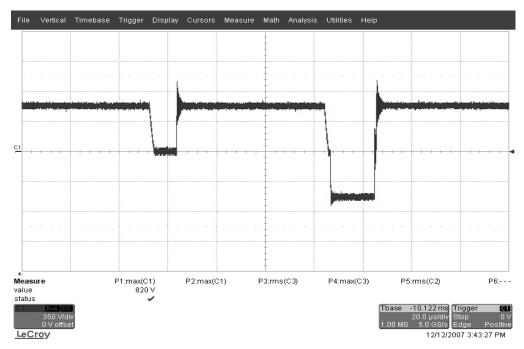

| 5.62 Line-to-line voltage waveform of AZSPWM1 (top) and its zoom-in view at its   |

| worst overshoot voltage region (bottom) for $M_i$ =0.61 and 70m cable             |

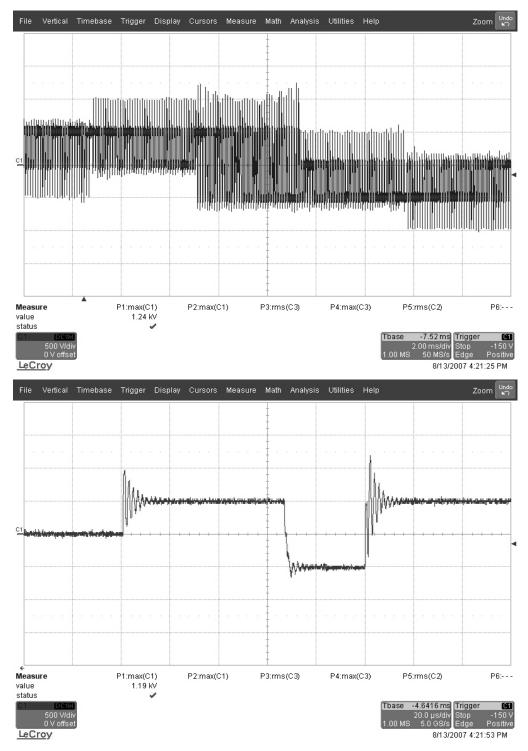

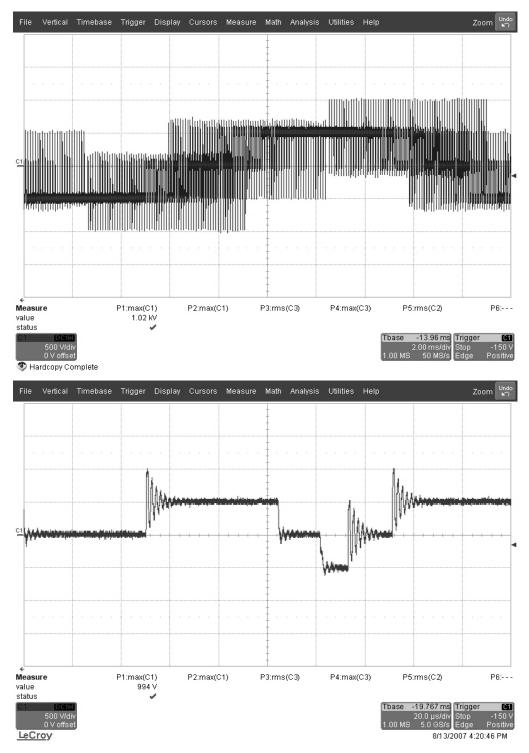

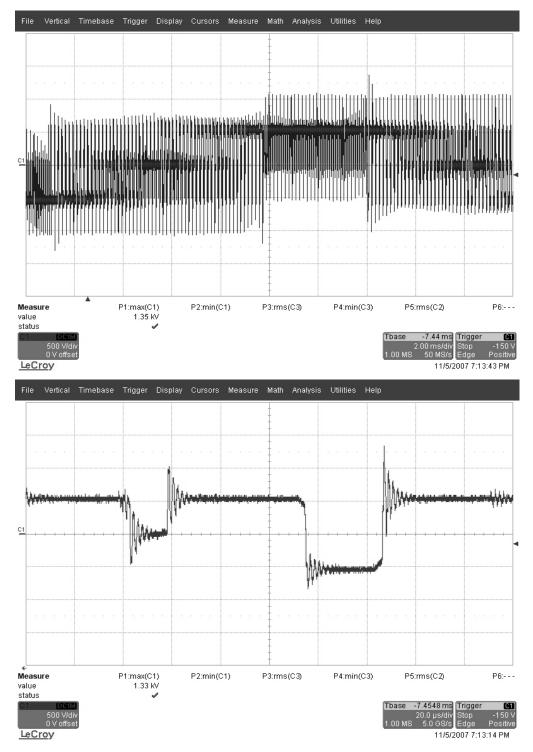

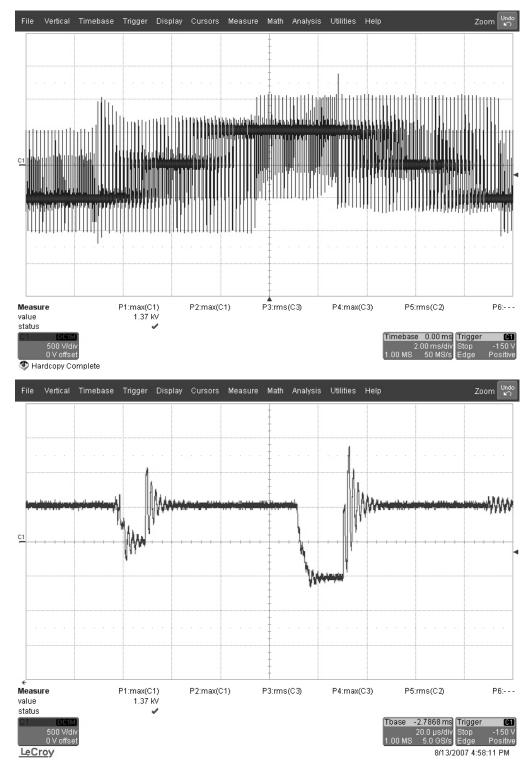

| 5.63 Line-to-line voltage waveform of AZSPWM1 (top) and its zoom-in view at its   |

| worst overshoot voltage region (bottom) for $M_i$ =0.8 and 70m cable201           |

| 5.64 Line-to-line voltage waveform of the commercial two-level VSI (top) and its  |

| zoom-in view at its worst overshoot voltage region (bottom) for $M_i$ =0.8 and    |

| 70m cable                                                                         |

| 5.65 Line-to-line voltage waveform of the commercial three-level NPC VSI (top)    |

| and its zoom-in view at its worst overshoot voltage region (bottom) for $M_i=0.8$ |

| and 70m cable                                                                     |

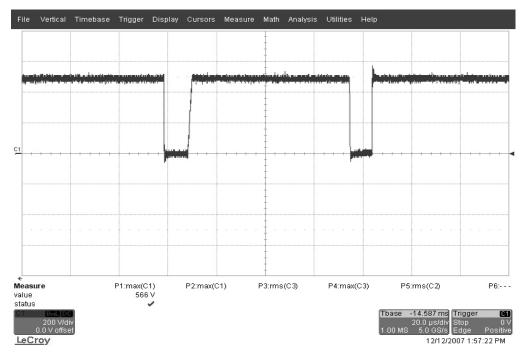

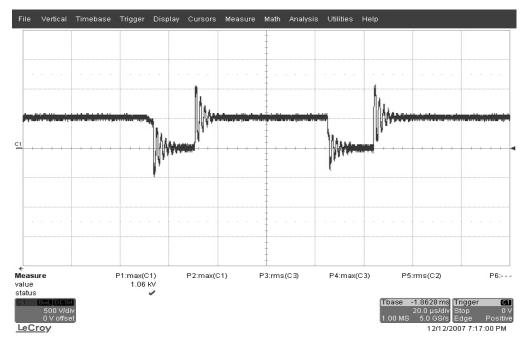

| 5.66 The zoom-in view of the line-to-line voltage waveform of SVPWM1 at its worst |

| overshoot voltage region for M <sub>i</sub> =0.8 and 2m cable 207                 |

| 5.67 The zoom-in view of the line-to-line voltage waveform of AZSPWM1 at its      |

| worst overshoot voltage region for M <sub>i</sub> =0.8 and 2m cable               |

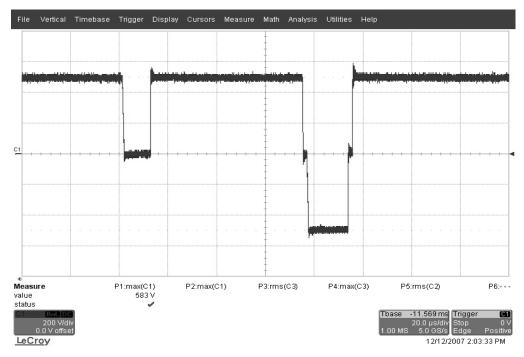

| 5.68 The zoom-in view of the line-to-line voltage waveform of SVPWM at its worst  |

| overshoot voltage region for M <sub>i</sub> =0.8, 2m cable, and CMI-2208          |

|                                                                                   |

| 5.69 The zoom-in view of the line-to-line voltage waveform of AZSPWM1 at its                 |  |  |

|----------------------------------------------------------------------------------------------|--|--|

| worst overshoot voltage region for M <sub>i</sub> =0.8, 2m cable, and CMI-2208               |  |  |

| 5.70 The zoom-in view of the line-to-line voltage waveform of SVPWM at its worst             |  |  |

| overshoot voltage region for M <sub>i</sub> =0.8, 70m cable, and CMI-2209                    |  |  |

| 5.71 The zoom-in view of the line-to-line voltage waveform of AZSPWM1 at its                 |  |  |

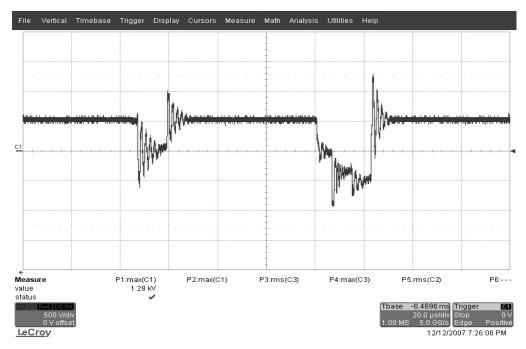

| worst overshoot voltage region for M <sub>i</sub> =0.8, 70m cable, and CMI-2209              |  |  |

| 5.72 Phase current (blue), CMC (yellow), and CMV (red) waveforms for DPWM1                   |  |  |

| $(M_i=0.8 \text{ and } f_s=10 \text{ kHz})$ (70m cable)                                      |  |  |

| 5.73 Phase current (blue), CMC (yellow), and CMV (red) waveforms for NSPWM                   |  |  |

| $(M_i=0.8 \text{ and } f_s=10 \text{ kHz})$ (70m cable)                                      |  |  |

| 5.74 Generation of the voltage vectors of MAZSPWM                                            |  |  |

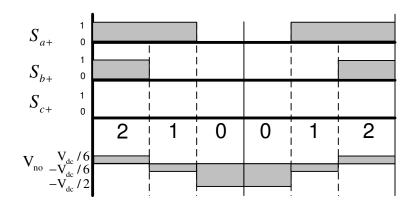

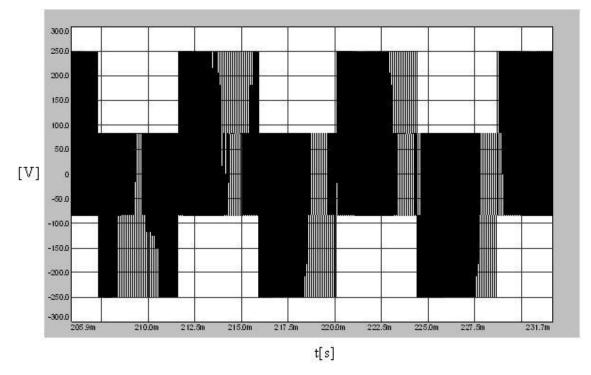

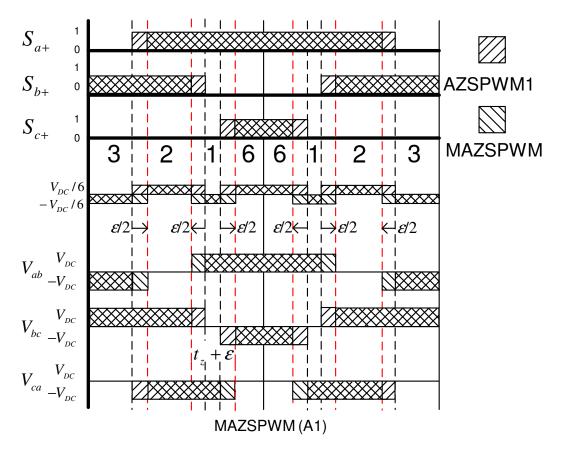

| 5.75 PWM pulse pattern, CMV, and line-to-line output voltages of MAZSPWM215                  |  |  |

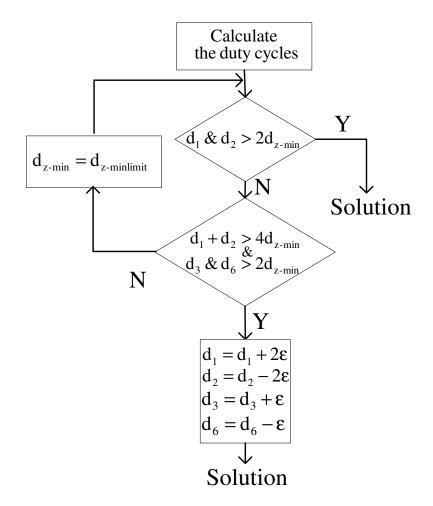

| 5.76 Decision flow chart of MAZSPWM                                                          |  |  |

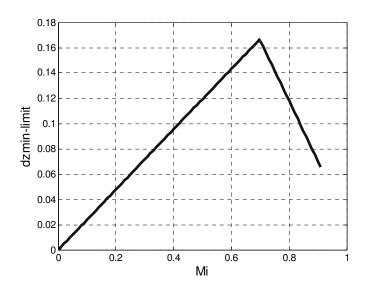

| 5.77 Maximum d <sub>z-min</sub> (d <sub>z-minlimit</sub> ) for various M <sub>i</sub> values |  |  |

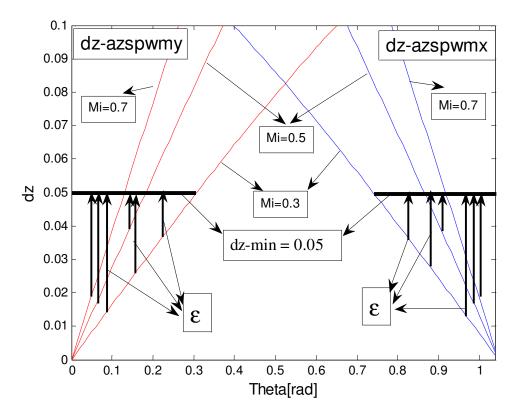

| 5.78 Epsilon "ε" modification of the zero-voltage time interval                              |  |  |

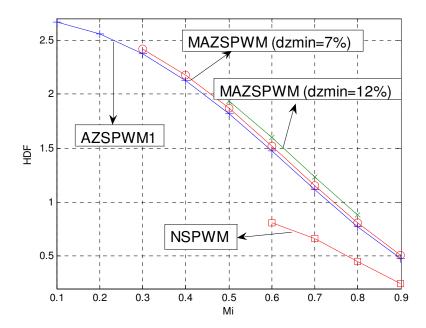

| 5.79 The HDF characteristics of NSPWM, AZSPWM1 and MAZSPWM with two                          |  |  |

| different d <sub>zmin</sub> values                                                           |  |  |

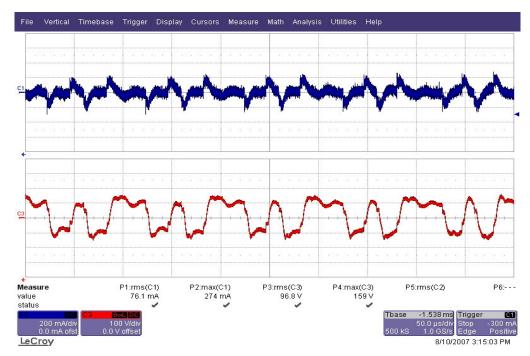

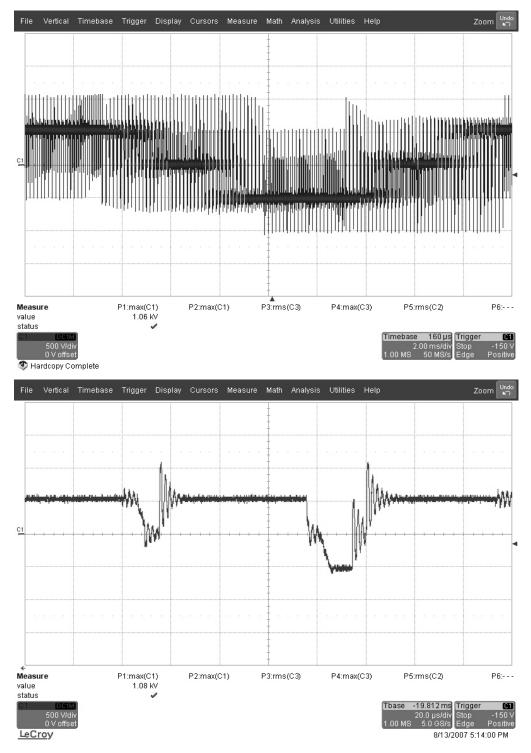

| 5.80 Line-to-line voltage waveform of MAZSPWM (top) and its zoom-in view at its              |  |  |

| worst overshoot voltage region (bottom) for $M_i$ =0.4 and 70m cable222                      |  |  |

| 5.81 Line-to-line voltage waveform of MAZSPWM (top) and its zoom-in view at its              |  |  |

| worst overshoot voltage region (bottom) for $M_i$ =0.61 and 70m cable223                     |  |  |

| 5.82 Line-to-line voltage waveform of MAZSPWM (top) and its zoom-in view at its              |  |  |

| worst overshoot voltage region (bottom) for $M_i$ =0.8 and 70m cable224                      |  |  |

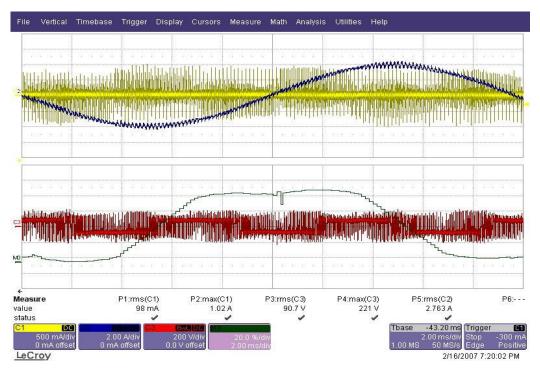

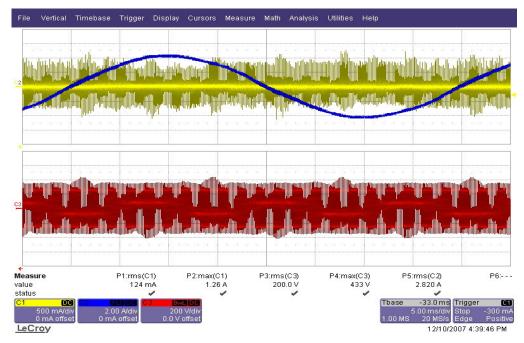

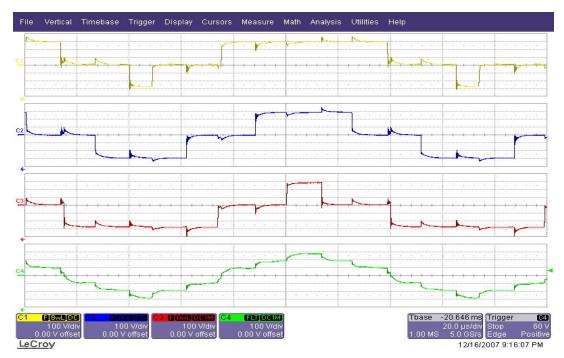

| 5.83 Phase current (blue), CMC (yellow) and CMV (red) waveforms for                          |  |  |

| MAZSPWM (M <sub>i</sub> =0.4 and f <sub>s</sub> =6.6kHz)                                     |  |  |

| 5.84 Phase current (blue), CMC (yellow) and CMV (red) waveforms for                          |  |  |

| MAZSPWM ( $M_i$ =0.61 and $f_s$ =6.6kHz)                                                     |  |  |

| 5.85 Phase current (blue), CMC (yellow) and CMV (red) waveforms for                          |  |  |

| MAZSPWM (M <sub>i</sub> =0.8 and f <sub>s</sub> =6.6kHz)                                     |  |  |

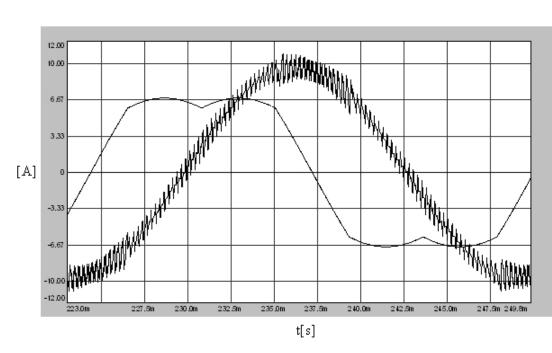

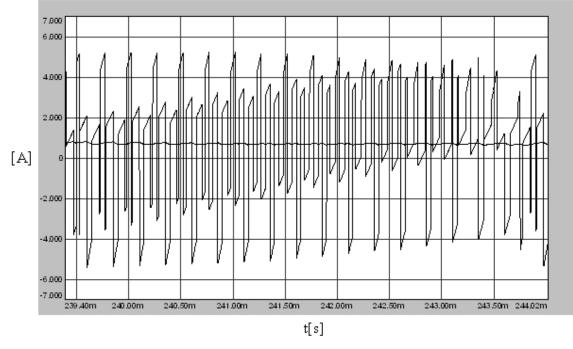

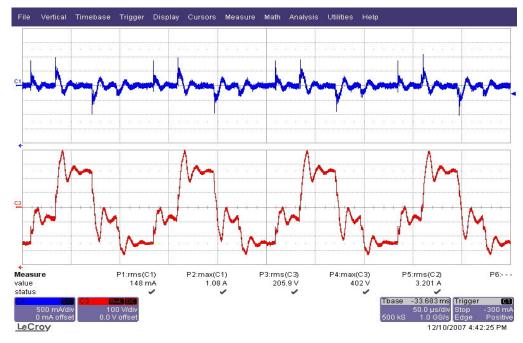

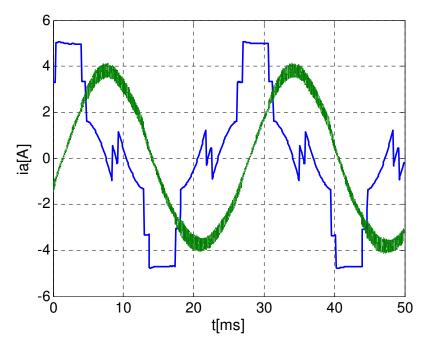

| 5.86 Phase current (green) and modulation signal $(x5)$ (blue) for the combined PWM          |  |  |

| algorithm (M <sub>i</sub> =0.58)                                                             |  |  |

|                                                                                              |  |  |

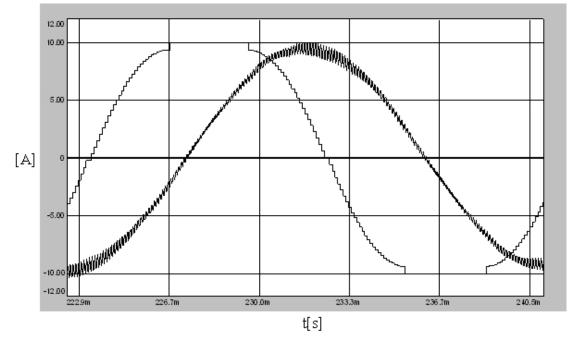

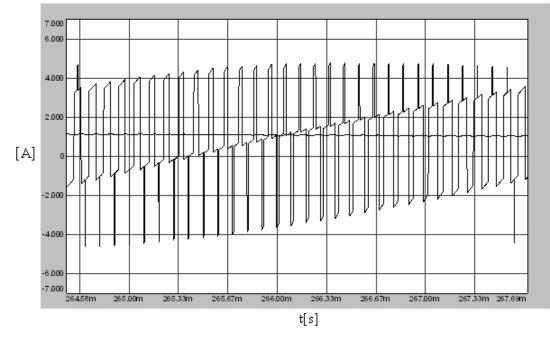

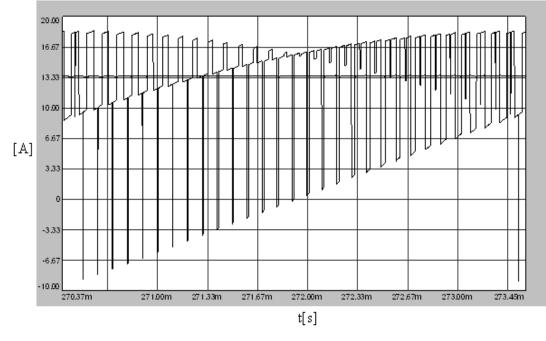

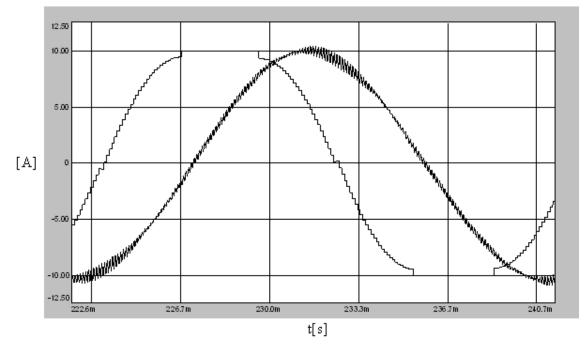

- 5.87 Phase current (blue), CMC (yellow), CMV (red), and modulation signal (green) waveforms for the combined PWM algorithm (M<sub>i</sub>=0.58).... 228

## LIST OF TABLES

## TABLES

| 2.1 Voltage vector sequences of AZSPWM methods                              | 24     |

|-----------------------------------------------------------------------------|--------|

| 2.2 Voltage vector sequences of RSPWM methods                               | 28     |

| 2.3 Common mode voltages of RSPWM methods                                   | 29     |

| 2.4 Voltage vector sequences of the NSPWM method                            | 32     |

| 2.5 NSPWM region dependent carrier signals                                  | 33     |

| 2.6 CMV characteristics of PWM methods.                                     | 36     |

| 2.7 The number of commutations per-carrier-cycle and K <sub>f</sub>         | 47     |

| 2.8 Performance attributes comparison of PWM methods (NA: not applicable).  | 62     |

| 3.1 Induction motor T equivalent circuit parameters.                        | 65     |

| 3.2 Magnitudes of largest peak-to-peak current ripples and HDF of PWM meth  | iods   |

|                                                                             | 111    |

| 3.3 Calculated $K_{dc}$ values compared to the simulation results           | 113    |

| 4.1 Two-level VSI switch states and CMV                                     | 114    |

| 5.1 Experimental Peak CMV measurements.                                     | 158    |

| 5.2 Experimental RMS CMV measurements                                       | 158    |

| 5.3 Experimental Peak CMC measurements                                      | 159    |

| 5.4 Experimental RMS CMC measurements.                                      | 159    |

| 5.5 Design parameters of the utilized CMIs                                  | 161    |

| 5.6 Properties of the magnetic materials of the utilized toroidal cores     | 162    |

| 5.7 Experimental Peak CMC measurements (M <sub>i</sub> =0.8).               | 175    |

| 5.8 Experimental RMS CMC measurements (M <sub>i</sub> =0.8)                 | 175    |

| 5.9 CMV/CMC performance comparison of the commercial VSIs and the proto     | otype  |

| VSI with/without CMI-2 for M <sub>i</sub> =0.8                              | 192    |

| 5.10 Measured peak line-to-line voltages (kV) for various PWM methods for v | arious |

| operating conditions (M <sub>i</sub> =0.8)                                  | 211    |

### **CHAPTER 1**

### **INTRODUCTION**

### **1.1. Adjustable Speed Drives**

In modern life, electrical motors are widely utilized to generate motion from electrical energy. There are many kinds of electrical motors available at a wide range of power ratings for various domestic and industrial applications. In the past DC motors were widely preferred since control of a DC motor is easy and its speed can be controlled by changing its terminal voltage. However they have disadvantages against AC induction motors such as their initial and maintenance costs. AC motors are economical but it is impossible to control an AC motor efficiently by directly feeding it from the AC grid. Therefore Adjustable Speed Drives (ASD) were developed. ASDs generate AC output voltage at required magnitude and frequency for the induction motor. They are widely utilized for driving AC motors especially in industrial processes where variable speed control and high energy efficiency are required [1] and in high quality motion control applications where precise torque, speed, and position control are required. With the development of ASDs, utilization of AC motors has spreaded widely and today the three-phase AC induction motor is the most common motor type utilized in industry and at long term great majority of AC motors are expected to be driven by ASDs.

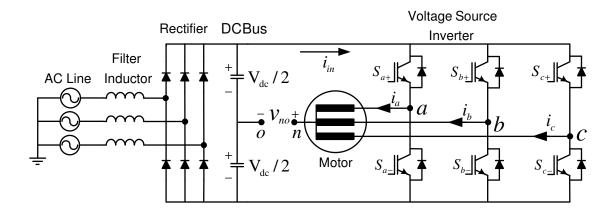

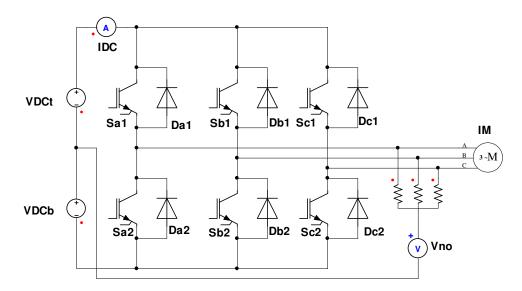

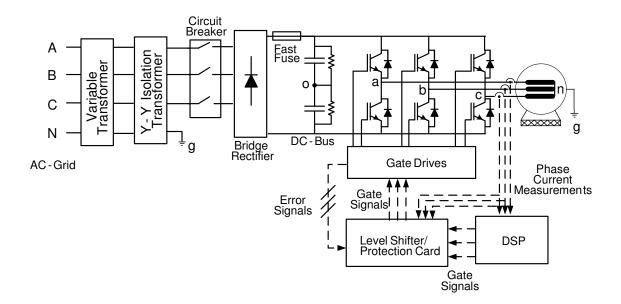

In Figure 1.1, a standard three-phase inverter drive circuit diagram is illustrated. In the drive illustrated in the figure between the rectifier and AC line, inductive filters are utilized to draw low harmonic distortion current from the AC grid. The DC voltage is obtained by rectifying the line voltage by a three-phase diode rectifier. In

order to decrease the voltage ripple over the DC bus, large electrolytic capacitors are utilized and smooth DC bus voltage is obtained. The DC bus voltage is converted from DC to AC by the two-level, three-wired, three-phase Voltage Source Inverter (VSI) and the AC output voltage is applied to the motor terminals [2]. VSIs are power electronic devices that can generate AC voltage at required magnitude and frequency, and they are utilized in AC motor Adjustable Speed Drives (ASD). In motor drive applications, VSIs increase the quality of motor speed control and motor efficiency by adjusting the frequency and magnitude of output voltage in a wide range with high accuracy. VSIs are composed of semi-conductor switches. In normal operation modes of circuit, these switches are either at conduction or cut-off just like ideal switches. Therefore output voltages of VSIs fed by constant DC bus voltage have rectangular waveform.

Figure 1.1 The circuit diagram of a three-phase inverter drive with diode rectifier front-end.

In order to obtain output voltage at desired magnitude and frequency, the VSI switches are turned on and off utilizing the required pulse pattern. When the switching frequency is low (lower than kHz) and the motor leakage inductance is small, the harmonic content of motor current is strong and results vibrations, noise, and losses. Therefore the switching frequency is increased as the switching losses permit [3]. In practical applications the switching frequency is typically 10-20 kHz for kW power levels, and 1-5 kHz at MW levels. The two-level inverter based ASD

circuit topology illustrated at Figure 1.1 is widely utilized in applications involving less than several MW power levels.

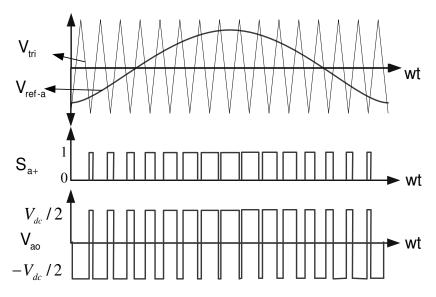

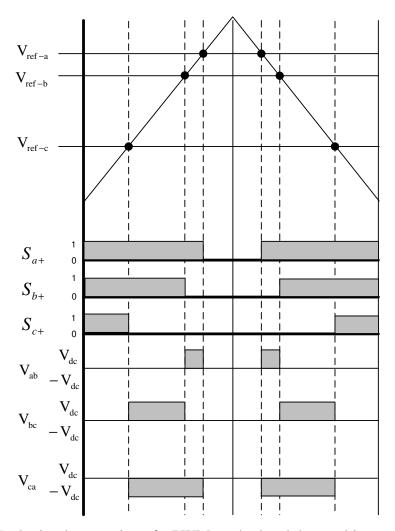

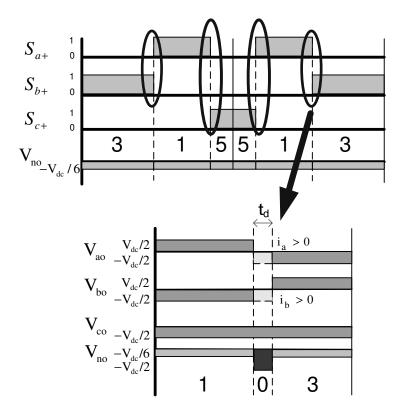

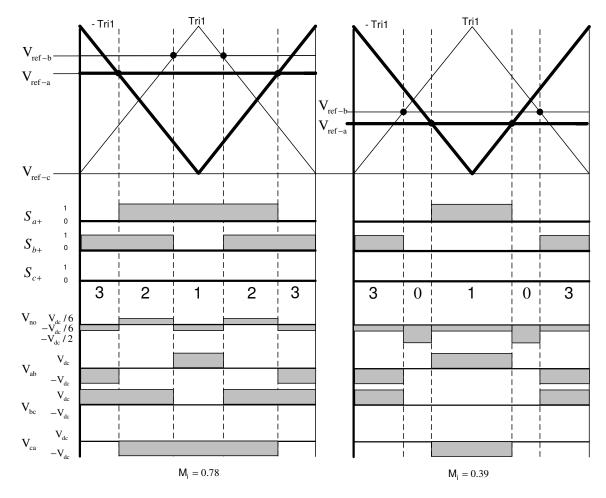

In the two-level VSI the most common switching method is Pulse Width Modulation (PWM). This method is based on the principle of generating a sinusoidal voltage at a fundamental frequency by adjusting the width of inverter output voltage pulses by utilizing constant switching frequency  $(f_s=1/T_s)$  [4]. In order to obtain these pulses, a triangular carrier wave at the switching frequency is compared with a modulation wave at the desired frequency and magnitude, and the coinciding points reveal the switching instants of switches (Figure 1.2). In high carrier frequency to fundamental frequency ratio applications (typically for a ratio larger than 20) there is no need to synchronize the modulation signal with the carrier wave [4]. Therefore there is one unique modulation wave for each leg, but the triangular carrier wave is common for all legs. The upper and lower switches of all legs complement each other ( $S_{a+}=1 \rightarrow$  $S_{a-}=0$ ). For  $S_{a+}=1$  the output voltage is  $+V_{dc}/2$ , and for  $S_{a+}=0$  output voltage ( $V_{ao}$ ) is -V<sub>dc</sub>/2. To prevent short-circuit faults, during switch state transitions logic signals of both switches are disabled (set to 0) for an interval named the dead-time, t<sub>d</sub>. During this period, the load current flows through the anti-parallel free-wheeling diodes instead of the semiconductor switches, and the polarity of the output current defines the output voltage polarity (if  $i_a > 0$ ,  $V_{ao} = -V_{dc}/2$  and if  $i_a < 0$ ,  $V_{ao} = V_{dc}/2$ ). By this way at the output of the VSI, rectangular voltage pulses are obtained. Since each phase output voltage can take 2 different values, a two-level three-phase VSI can take  $2^3$ =8 different states. The average of these voltage pulses over a T<sub>s</sub> PWM period forms a waveform which is equal to the reference (modulation) signal.

In the basic sinusoidal PWM method the reference signals of all phases are sinusoidal. However in other PWM methods the reference signal of each phase is shifted with an offset signal which is the same for all phases [5]. For these PWM methods, the average value of the output phase voltage pulses over a  $T_s$  switching period forms a waveform not equal to a pure sinusoidal signal (unless the offset signal is zero). However the average value of the line-to-line voltage pulses is sinusoidal since all phase signals are shifted (up or down) equally. Each PWM

method has unique performance attributes and the performance attributes of these PWM methods will be investigated in the following chapter.

Figure 1.2 Generation method of the PWM signals and the corresponding phase voltage waveform for phase "a".

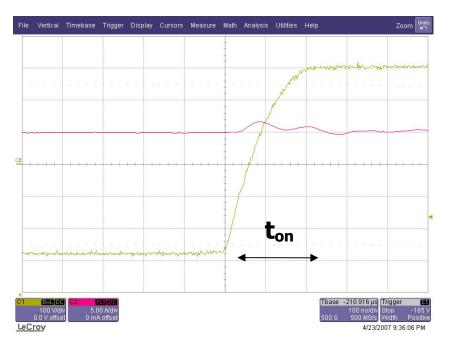

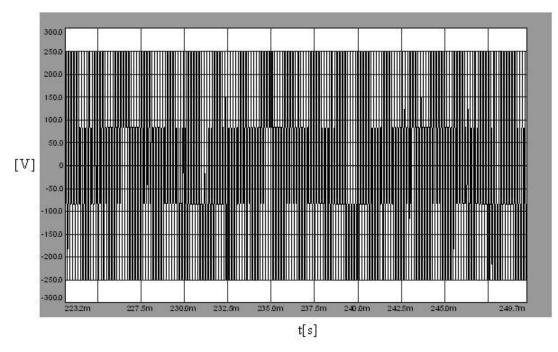

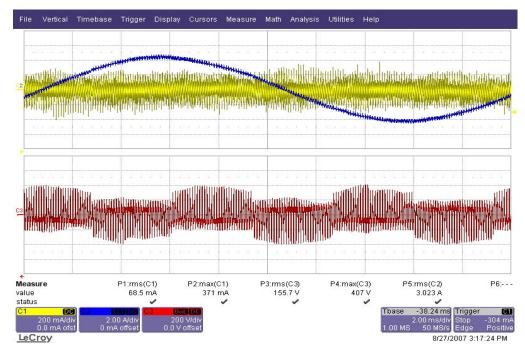

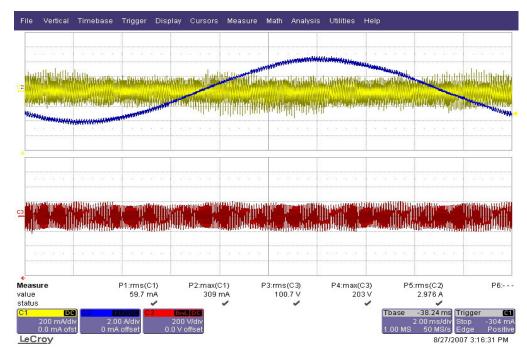

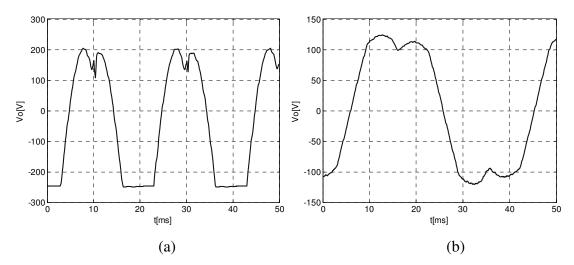

In the VSI, power semiconductor devices are utilized as switches. The controlled switch is typically a modern power transistor and the anti-parallel diode is a fast recovery diode. While in the early development stages of the VSI technology Darlington configuration based Bipolar Junction Transistors (BJTs) were employed, at later stages faster and therefore more efficient transistors have been developed. IGBTs (Insulated Gate Bipolar Transistor) and power MOSFETs (Metal Oxide Semiconductor Field Effect Transistor) have been invented and put to use in inverter drives over the last two decades. Reduction of the turn-on and turn-off transition times of the semiconductor switches, increases the efficiency and allows switchings at higher frequencies. Typically modern IGBTs have turn-on and turn-off times in the range of 0.1-1  $\mu$ s. The DC bus voltage is approximately 550 V for the drives fed by standard utility line-to-line voltage of 400 Vrms. For such conditions, the rate of change of the VSI output voltage is approximately 0.5-5 kV/ $\mu$ s. In Figure 1.3, the experimental inverter output phase voltage expanded waveform and the

corresponding phase current of a 4 kW VSI during the turn-on instant is illustrated. The phase current is nearly constant during turn on instant and has positive polarity with a magnitude of 5A. The inverter turn-on time is 200 ns in this application which results in a dv/dt of approximately 3 kV/ $\mu$ s. Due to this rapid change, the output voltage generated by a VSI is composed of pulses with sharp edges and these pulses result undesired effects on the motor.

Figure 1.3 The experimental inverter output phase voltage expanded waveform and the corresponding phase current of a 4 kW VSI during the turn-on instant.

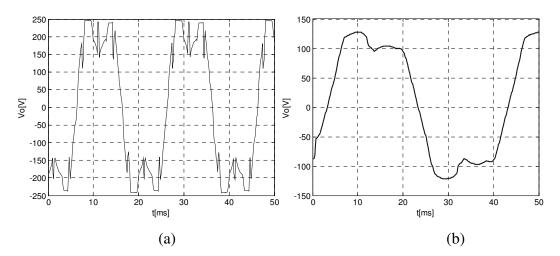

One of the important unwanted effects of the sharp edged PWM pulses is the overvoltage appearing across the motor terminals due to the voltage reflection in long cable applications. These overvoltages can have more damaging effect when there are instantaneous polarity reversals on the inverter output line-to-line voltages [6]. Due to these overvoltages, insulating breakdown occurs generally at the first coil of the stator phase windings and when this repeatedly occurs, it eventually leads to motor failure.

The Common Mode Voltage (CMV) and Common Mode Current (CMC) [7] are other important unwanted effects of the sharp edged PWM pulses and they are the main topics of this thesis and their effects and mitigation methods are investigated in detail.

#### 1.2. Common Mode Voltage and Current

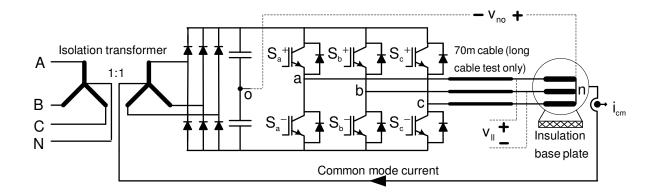

The common mode voltage is defined as the potential of the star point of the load with respect to the center of the DC bus of the VSI ( $V_{no}$  in Figure 1.1) and can be expressed in the following.

$$v_{no} = (v_{ao} + v_{bo} + v_{co})/3$$

(1.1)

Since the two-level three-phase VSI can not provide sinusoidal voltages and has discrete output voltages, the instantaneous value of the common mode potential is different from zero and may take the values of  $\pm V_{dc}/6$  or  $\pm V_{dc}/2$  depending on the state of the inverter switches [8]. During the switching instants the change of CMV has always magnitude of  $V_{dc}/3$ .

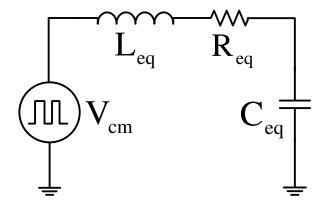

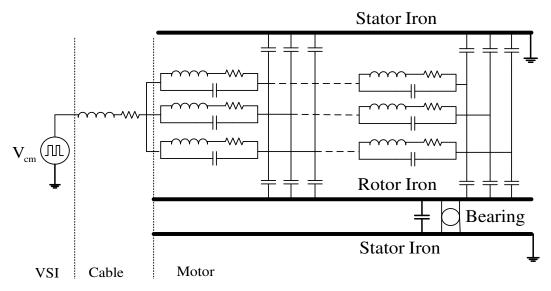

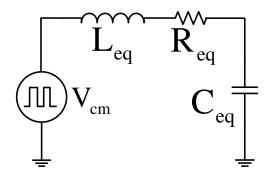

Since CMV is defined according to the switch states, during switching instants it shows a rapid change. This rapid change results catastrophic problems especially at the motor drive applications [7]. Since the distances between the motor windings, rotor frame and the motor chassis are short, there are equivalent parasitic capacitances existing between these layers which are effective at high frequencies. Simply, these capacitances can be modeled as an equivalent capacitance. In Figure 1.4 the simplified common mode equivalent circuit of an inverter drive and an induction motor is illustrated [9]. The equivalent parasitic capacitance of the motor ( $C_{eq}$ ) forms a RLC series resonant circuit together with the equivalent inductance ( $L_{eq}$ ) and resistance ( $R_{eq}$ ) parameters of the equivalent circuit of inverter drive [9]. In practical applications, for safety reasons the conductive motor chassis is grounded.

Therefore, high CMVs with high dv/dt result in parasitic CMC flowing through this parasitic capacitance from the motor to the ground at high frequencies.

Figure 1.4 Simplified common mode equivalent circuit of an inverter drive and an induction motor [9].

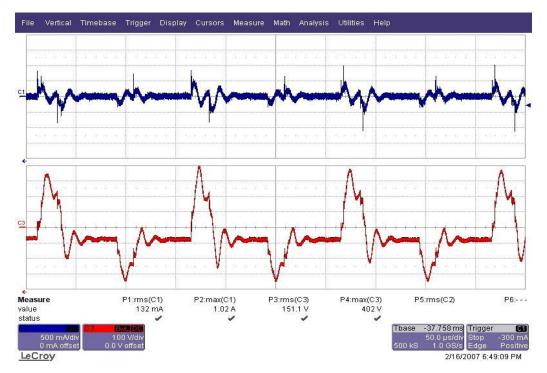

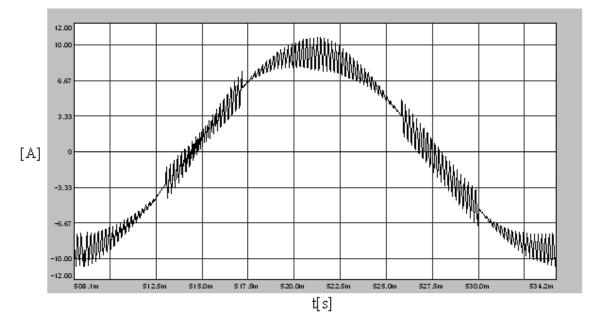

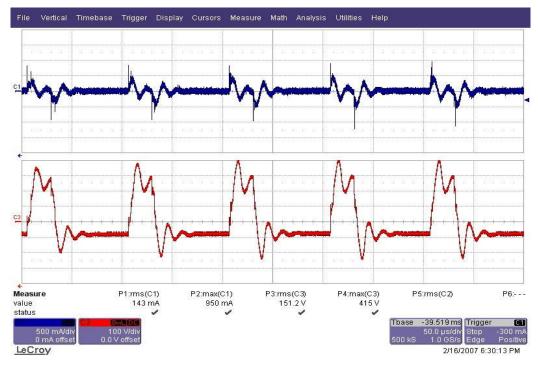

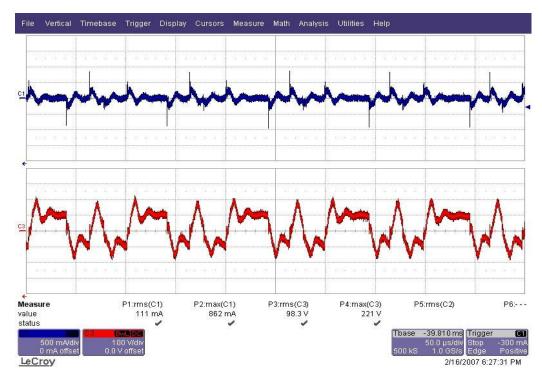

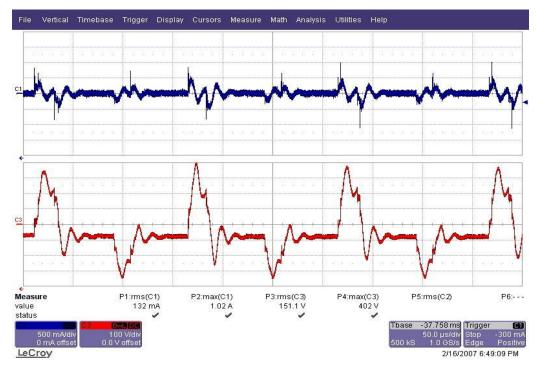

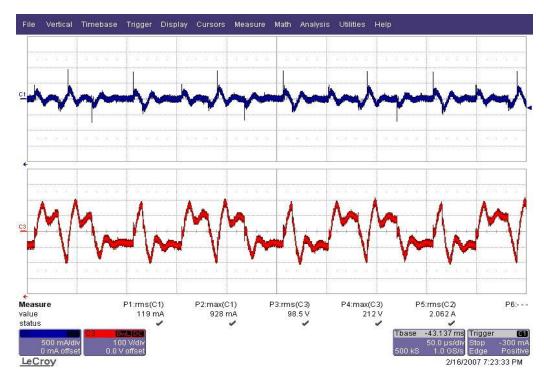

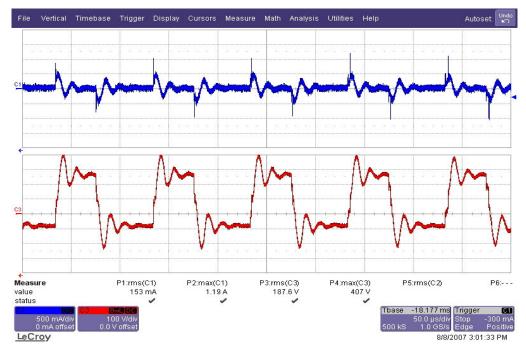

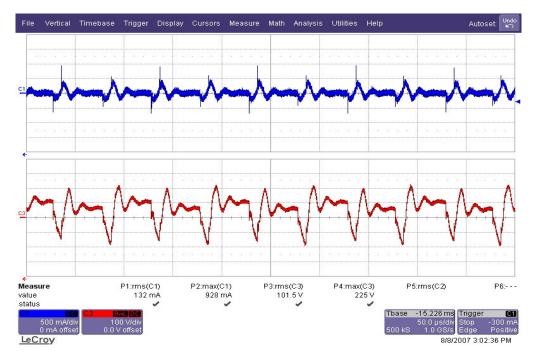

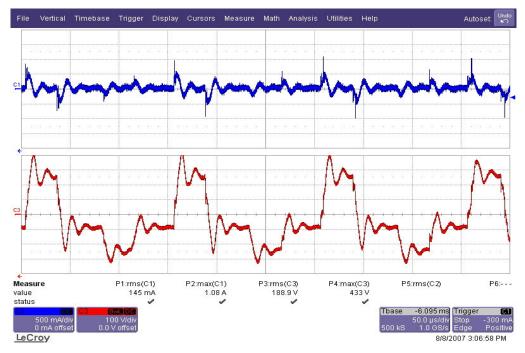

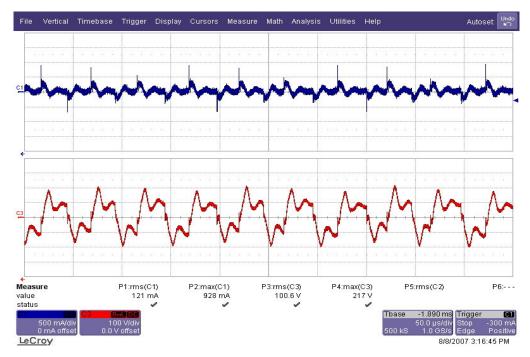

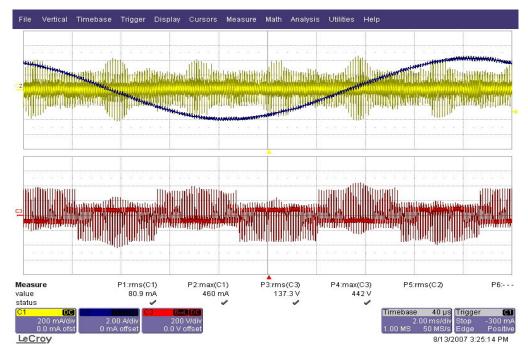

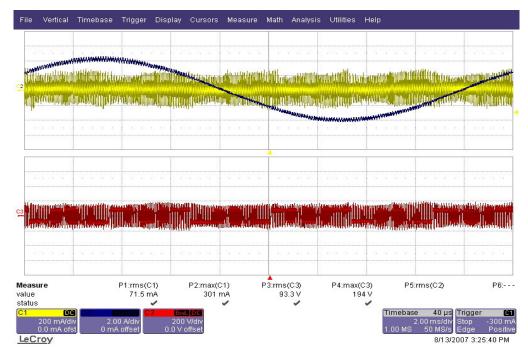

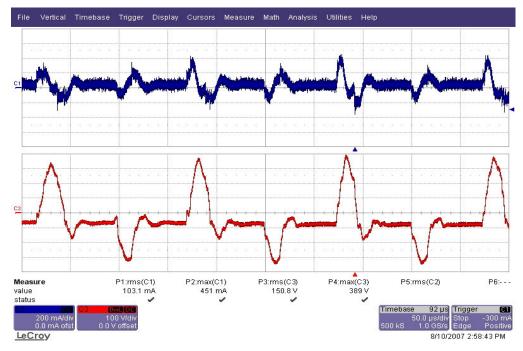

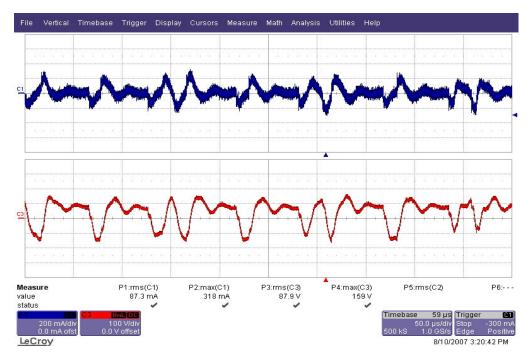

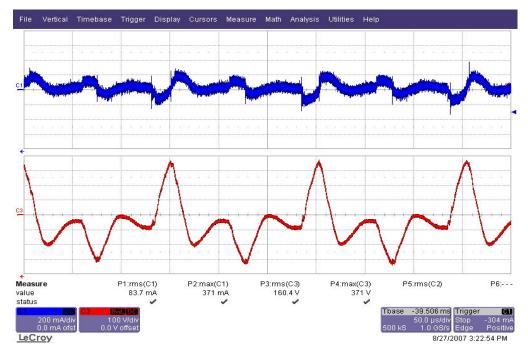

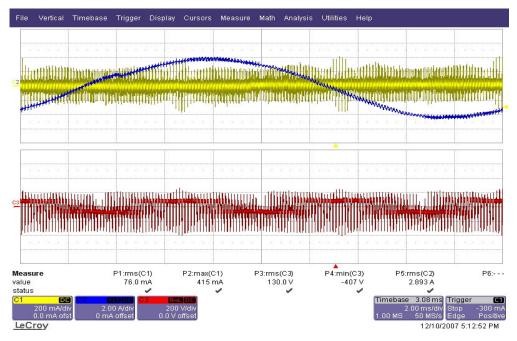

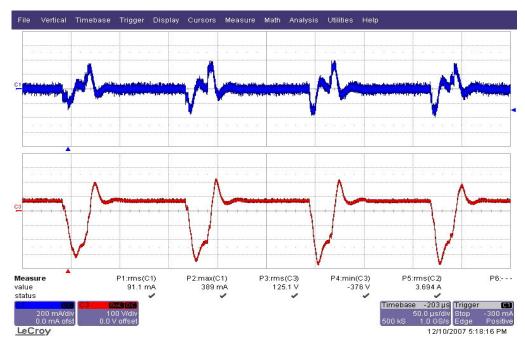

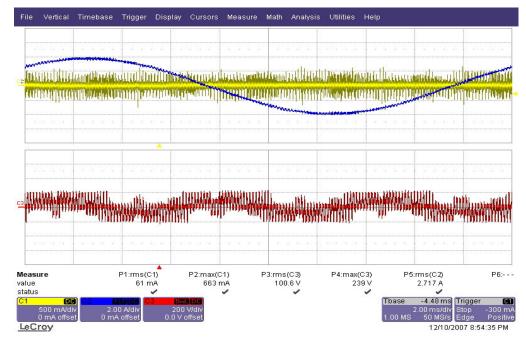

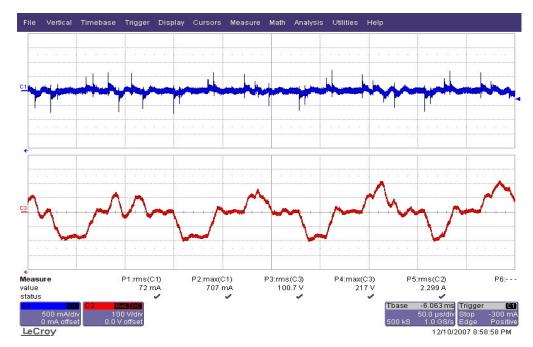

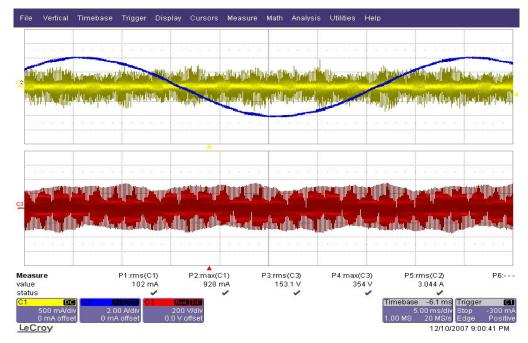

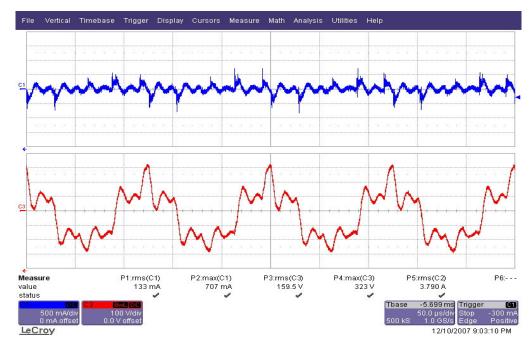

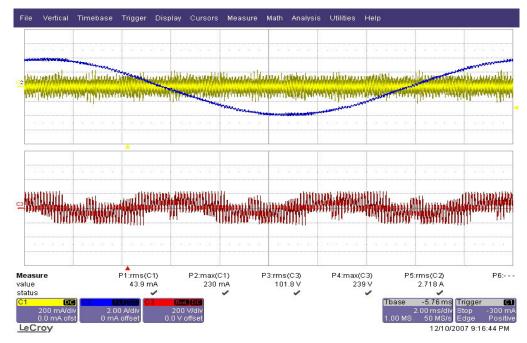

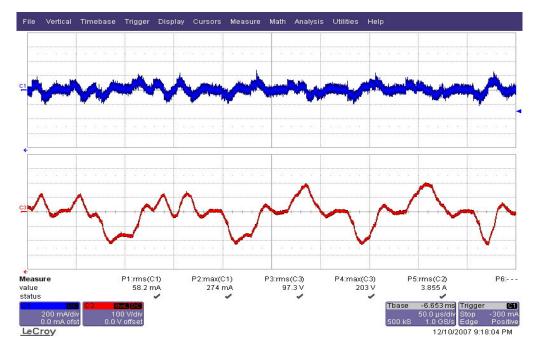

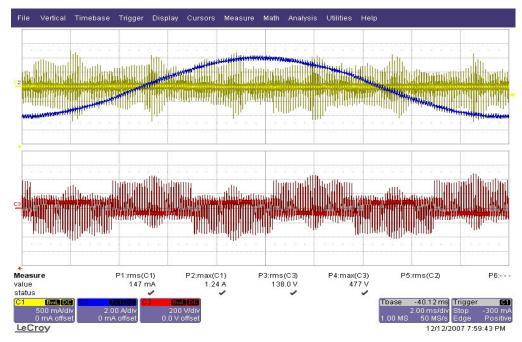

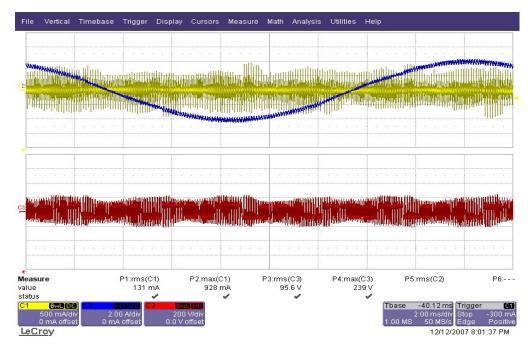

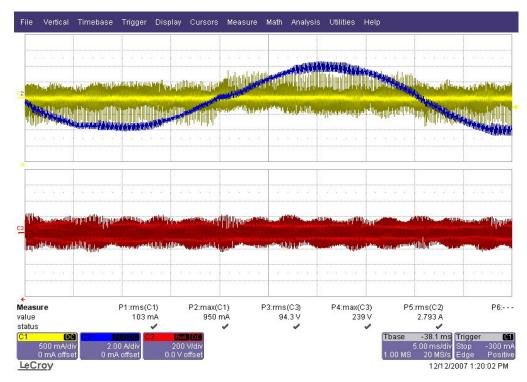

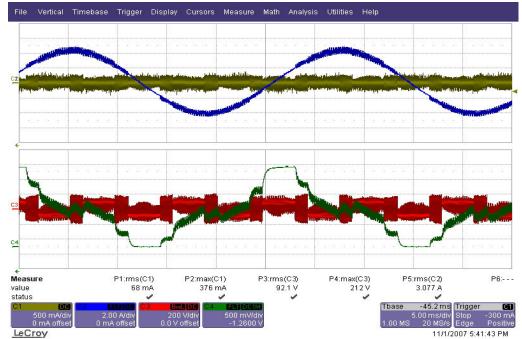

In some applications the peak value of the CMC can be comparable with the rated current of the motor [10]. In the example in Figure 1.5, experimental common mode voltage and leakage current (approximately equal to CMC) waveforms are illustrated, which are observed in a 4 kW induction motor driven by an ASD with 500V DC bus voltage and no mitigation method is applied. In this operation the rms value of the load current is approximately 3 A at no load while the leakage current is approximately 1 A peak which is very high. These large CMV/CMC values result fluting type bearing failures [7] in a short time. Since CMV and CMC create emission at high frequencies, they result in EMI at both the AC grid which feds the drive and the electronic circuits of the drive itself. Therefore unwanted nuisance trips (including at the drive itself) and failure of the electronic circuits may occur [7]. Due to these unwanted effects, reduction of the effects of CMV and CMC is necessary. Therefore various mitigation techniques have been developed.

Figure 1.5 Experimental CMV (red) and leakage current (blue) waveforms.

Adding active or passive filters [9], [11], [12] between the inverter drive and the motor is the most common technique to effectively reduce CMV and CMC. However there are some drawbacks to utilizing filters such as increasing size and cost.

Optimization of the PWM pulse pattern also reduces CMV and CMC but so far the developed PWM methods that reduce CMV/CMC [13], [14] have practical constraints and limited performance attributes. Although some methods are theoretically (ideally) viable, due to practical constraints, they result in performance degradation rather than improvement [13], [14]. The practical implementation of some methods is problematic as such methods result high harmonic content at load current [8]. Similarly some methods result high peak overshoots at line-to-line voltages at the motor phase winding terminals when the ASD and the AC motor are distant from each other (long cable applications) [15]. In this thesis a new PWM pulse pattern optimization technique is proposed without any practical constraints and with high PWM performance attributes. Utilizing this method reduces CMV and CMC partially and decreases filter requirement of the inverter drive.

#### **1.3. Scope of The Thesis**

This thesis mainly focuses on CMV/CMC reduction in three-phase two-level VSI based drives, by means of PWM pulse pattern optimization. The most important contribution of this thesis involves the development of a novel reduced common mode voltage PWM method, the Near State PWM (NSPWM) method for three-phase two-level VSIs which has no practical implementation constraints and yields superior PWM performance attributes such as resulting in low harmonic stresses at the AC and DC side of the VSI.

The second contribution involves investigation of the important performance attributes of Reduced Common Mode Voltage PWM (RCMV-PWM) methods and standard PWM methods by means of theoretical, analytical and numerical analysis, computer simulations and laboratory experiments.

The third contribution involves theoretical investigation of active and passive CMV/CMC mitigation methods and experimental investigation of the effects of passive filters on CMC. This study is for the purpose of comparing the passive and PWM pattern based CMV/CMC reduction methods and do a global evaluation.

The Active Zero State PWM (AZSPWM1) method [13] which is one of the most popular RCMV-PWM methods has a performance constraint, such that it has problematic line-to-line output voltage pulse pattern. The fourth contribution of this thesis involves the development of a modification algorithm for the AZSPWM1 method, which eliminates its performance constraint. This section also evaluates the overvoltage attributes of all discussed PWM methods.

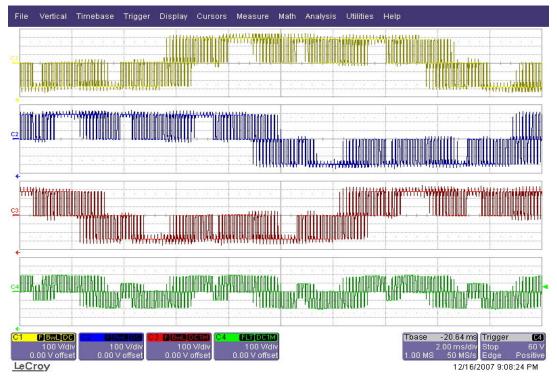

The final contribution of this thesis is the development of a PWM algorithm that combines various PWM methods and results in overall superior performance depending on the optimization criteria chosen by the user. It is illustrated that the algorithm combines various PWM methods and the combination involves seamless transition between methods such that the output performance is not disturbed. The organization of this thesis is as follows. In the second chapter, standard PWM methods and RCMV-PWM methods for the two-level three-phase VSI are reviewed and a novel RCMV-PWM method (NSPWM) is introduced. Important PWM performance characteristics, such as the voltage linearity and input/output ripple characteristics and practical applicability of NSPWM and other PWM methods are investigated.

In the third chapter, computer simulations of the PWM methods are provided to verify the theoretical and analytical results of the second chapter. In this chapter important performance characteristics such as inverter input and output harmonic content and CMV of all RCMV-PWM methods and standard PWM methods are compared.

In the fourth chapter, harmful effects of the common mode voltage and the common mode current are discussed. Generating mechanism and different types of CMC and bearing currents are discussed in detail. Active and passive common mode voltage and current suppression methods are reviewed. Effects of PWM pulse pattern optimization on CMV/CMC is compared with other mitigation methods.

In the fifth chapter, the laboratory experimental set-up which is used in this thesis and the implementation of the NSPWM are described. Experimental results composed of measurements of the CMV and CMC of important PWM methods are provided. The effects passive common mode filters on the CMC are investigated in this chapter. CMV/CMC performance of commercial two-level and three-level ASDs are studied and compared with the prototype VSI which is constructed in this thesis. Line-to-line voltage waveforms at the terminals of the motor are studied with the long cable test for important PWM methods. Finally the combination of CMV and CMC reduction techniques is proposed for optimum overall performance.

The sixth chapter summarizes research results related to this thesis.

### **CHAPTER 2**

### **PWM METHODS AND CHARACTERISTICS**

#### 2.1 Introduction

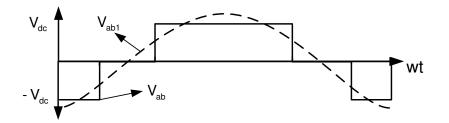

Voltage source inverters are utilized in practical motor drive applications since their invention. In the past, the voltage source inverters were operated in the square wave operation mode. In the square wave operation mode, the inverter phase and therefore line-to-line output voltages have square wave shapes. In Figure 2.1 the line-to-line output voltage of  $V_{ab}$  and its fundamental component in this operation mode is illustrated for the conventional three-phase two-level inverter [2]. This operation mode has drawbacks such that the inverter output voltage has low order harmonics with large magnitude (such as 5<sup>th</sup>, 7<sup>th</sup>) which are also seen at the motor currents. In spite of these drawbacks, the square wave operation was preferred in the early inverters because of its very low number of switchings, hence low switching losses. The semiconductor switches which were utilized in the early inverters had long turn-on and turn-off times resulting very high switching losses. Therefore by utilizing these switches, switching at high frequencies was practically impossible and instead of the PWM, the square wave operation was preferred.

Figure 2.1 Inverter output line-to-line voltage waveform and its fundamental component when square wave method is utilized.

As the semiconductor technology has evolved, faster semiconductor switches have been developed. Today IGBT switches with low turn-on and turn-off times are widely utilized in VSIs. Development of faster semiconductor switches significantly reduced the switching losses of the inverter drives and this reduction enabled operation at higher switching frequencies. Therefore utilization of PWM methods (Figure 1.2) in inverter drives had been possible at various power ratings and the square wave operation had been obsolete except at very high power ratings. Today PWM methods are widely preferred in three-phase motor drives due to their superior characteristics. In the PWM mode operation, an AC motor does not draw low order current harmonics (such as 5<sup>th</sup>, 7<sup>th</sup>, 11<sup>th</sup>, etc.). The lowest order harmonic on the motor current occurs at the switching frequency of the inverter. Since this frequency is practically high (order of kHz), current harmonics are damped by the motor windings and are not problematic as in the square wave operation case.

In the PWM approach, the inverter switches are turned on and off within a carrier period in an appropriate manner and switch pulse patterns are generated. Various PWM methods with unique switch state pulse patterns have been developed with unique characteristics. In this chapter conventional PWM methods are reviewed, new PWM methods are introduced and their performance attributes are theoretically and analytically investigated. Finally, a thorough performance comparison of all the discussed PWM methods is provided.

#### 2.2 PWM Basics, Scalar and Vector Implementations

Based on the implementation technique, PWM methods are classified as scalar or space vector PWM methods. In the scalar implementation, a modulation reference signal is compared with a triangular carrier signal and the intersections define the switching instants. PWM pulses of one phase were given in Figure 1.2 for a fundamental cycle. In Figure 2.2 the phase voltage reference signals, triangular carrier signal, inverter upper switch signals and output line-to-line voltage pulses of all phases are illustrated for a PWM period. In practice, PWM periods are very small (100 µs for 10 kHz operation) compared to the fundamental period (20 ms for 50 Hz operation). Therefore the reference signals can be assumed as constant throughout the PWM period. The magnitude of the reference signal ( $V_{ref}$ ) of any phase (phase-x) is proportional to the duty cycle of the upper switch of the corresponding phase ( $d_{x+}$ ) and defined as (2.1) where  $V_{dc}$  is the DC-bus voltage. [16].

$$d_{x+} = \frac{1}{2} \left( 1 + \frac{2V_{ref}}{V_{dc}} \right) \qquad x \in \{a, b, c\}$$

(2.1)

Since upper and lower switches of all phase legs complement each other and the duty cycle of the lower switch of the phase-x  $(d_{x-})$  is defined as (2.2).

$$d_{x-} = (1 - d_{x+}) \tag{2.2}$$

The performance characteristics of a modulation method are primarily dependent on the modulation index  $M_i$  (voltage utilization level) which is defined as (2.3) [5]

$$M_{i} = (\frac{2}{\pi}) \frac{V_{1m}}{V_{dc}}$$

(2.3)

where  $V_{1m}$  is the magnitude of the reference signal fundamental component.

Figure 2.2 Scalar implementation of a PWM method and the resulting output line-toline voltages.

When implementing the PWM methods and analyzing the VSI output voltages, the space vector approach can be utilized. In the space vector approach the reference and the inverter output voltages are transformed to space vectors via the following complex variable transformation [16].

$$V = (2/3) \times (V_a + aV_b + a^2 V_c)$$

(2.4)

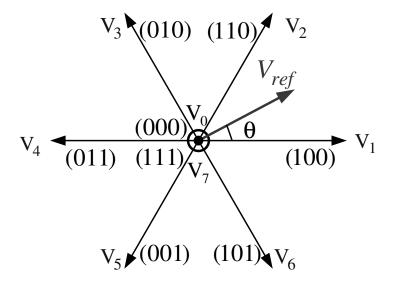

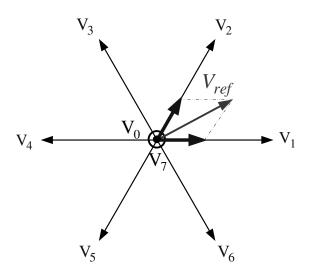

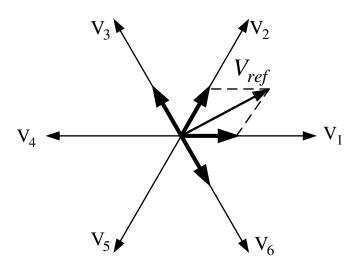

In the above equation  $a = e^{j2\pi/3}$  is the phase shift operator. Since there are eight possible inverter states available, the vector transformation yields eight voltage

vectors as shown in Figure 2.3. Of these voltage vectors, six of them  $(V_1, V_2, V_3, V_4, V_5, and V_6)$  are active voltage vectors, and two of them  $(V_0 and V_7)$  are zero voltage vectors. The active voltage vectors result in non-zero line-to-line voltage at least between two phases and the zero voltage vectors result in zero line-to-line voltage between all the phases. In the space vector analysis the duty cycles of the voltage vectors are calculated according to the vector volt-seconds balance rule defined in (2.5) and (2.6) and these voltage vectors are applied with the calculated duty-cycle.

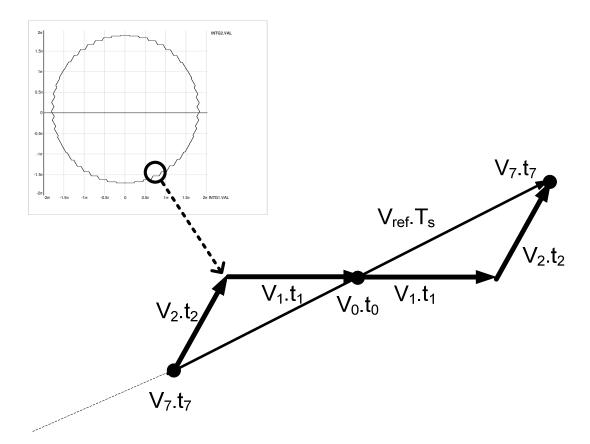

$$\mathbf{V}_{i}\mathbf{t}_{i} + \mathbf{V}_{j}\mathbf{t}_{j} + \mathbf{V}_{k}\mathbf{t}_{k} = \mathbf{V}_{ref}\mathbf{T}_{s}$$

$$(2.5)$$

$$\mathbf{t}_{i} + \mathbf{t}_{j} + \mathbf{t}_{k} = \mathbf{T}_{s} \tag{2.6}$$

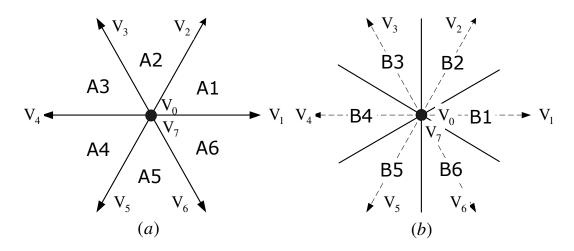

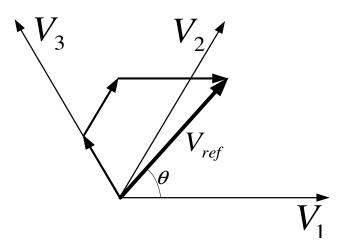

Figure 2.3 Voltage space vectors of the two-level inverter.

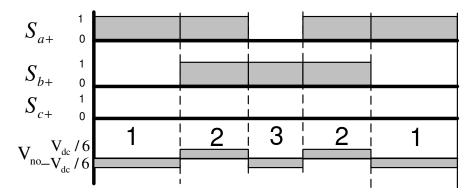

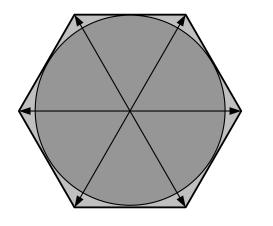

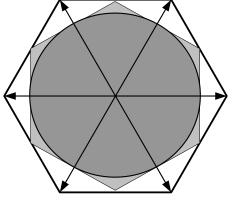

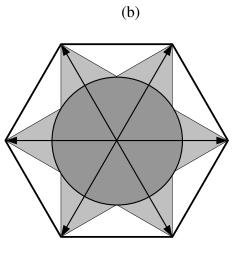

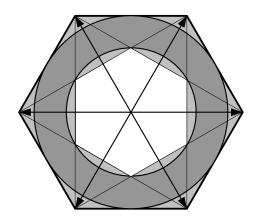

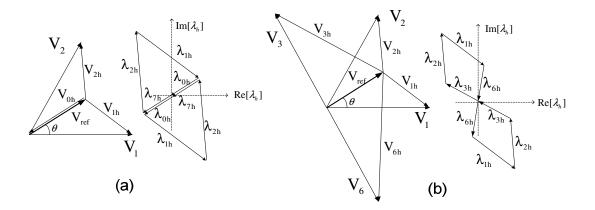

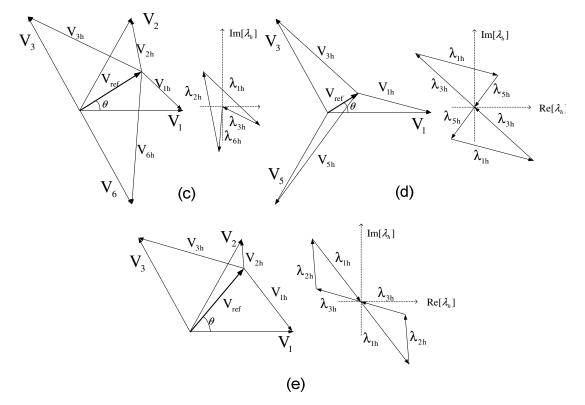

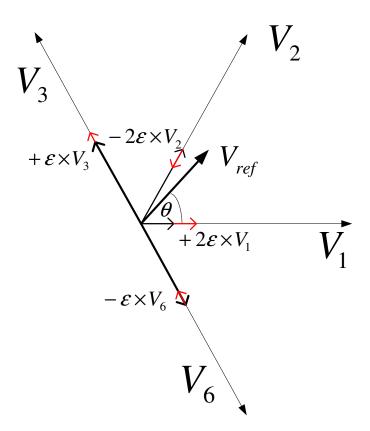

The sequence of the voltage vectors is selected based on a specified performance criterion such as the switching count and the vectors are programmed accordingly. Each PWM method utilizes different voltage vectors and sequences and the utilized voltage vectors alternate throughout the vector space. Therefore, the vector space is divided into segments. There are 6 A-type and 6 B-type segments available (Figure 2.4). Investigations reveal that all PWM methods utilize either A-type or B-type segments, and the utilized voltage vectors of these PWM methods alternate at the boundaries of the corresponding segments.

Figure 2.4 Voltage space vectors and 60° sector definitions: (a) A-type, (b) B-type regions.

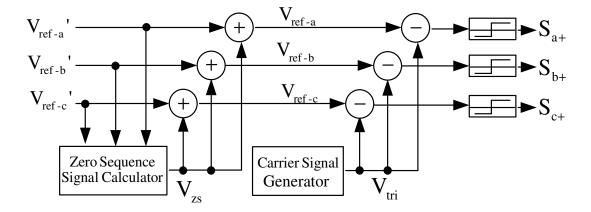

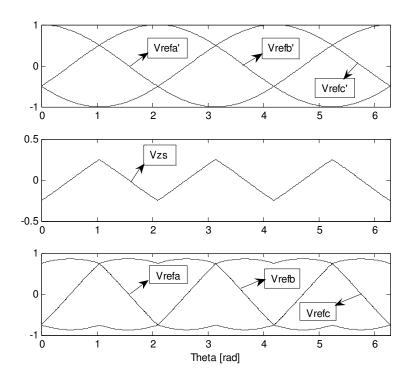

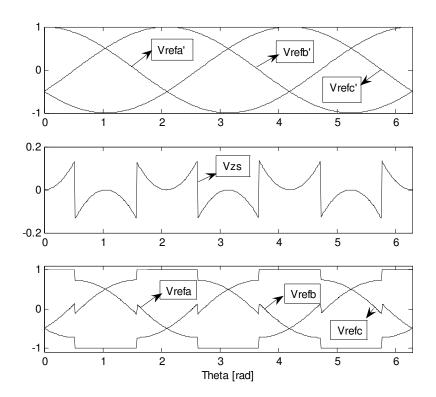

## 2.3 Standard PWM Methods

In PWM based VSIs, a reference signal is utilized and compared with the carrier triangular signal. The shape of this reference signal is equivalent to that of the corresponding required inverter output phase voltage with a proportional magnitude. In practice, the neutral point of the motor is always isolated. Therefore even the potential of the neutral point of the motor is non-zero; zero sequence currents can not flow since there exists no current path. This isolation allows the injection of a wide range of a zero-sequence voltage to the inverter phase voltages. In order to optimize the waveform quality, to decrease switching losses, or to provide wider voltage linearity range, zero-sequence signal injection is applied by shifting the reference signals of all phases up or down with a same amount as illustrated in Figure 2.5 [16]. In the given diagram  $V_{ref-a}$ ',  $V_{ref-b}$ ' and  $V_{ref-c}$ ' are the sinusoidal reference signals of phase-a, phase-b and phase-c respectively before zero sequence signal ( $V_{zs}$ ) is

injected. The zero sequence signal  $(V_{zs})$  is a function of the sinusoidal reference signals and is added to all phase reference signals equally. By this injection the reference signals of phases  $(V_{ref-a}, V_{ref-b} \text{ and } V_{ref-c})$  which are going to be compared with triangular carrier signal are obtained.

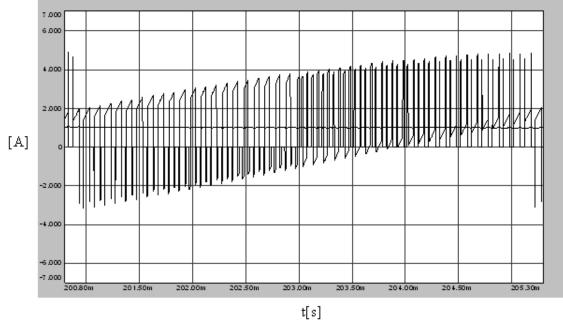

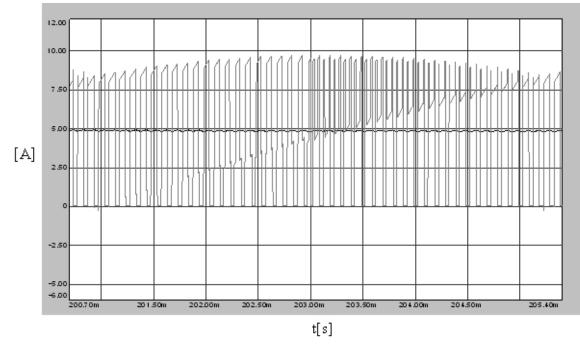

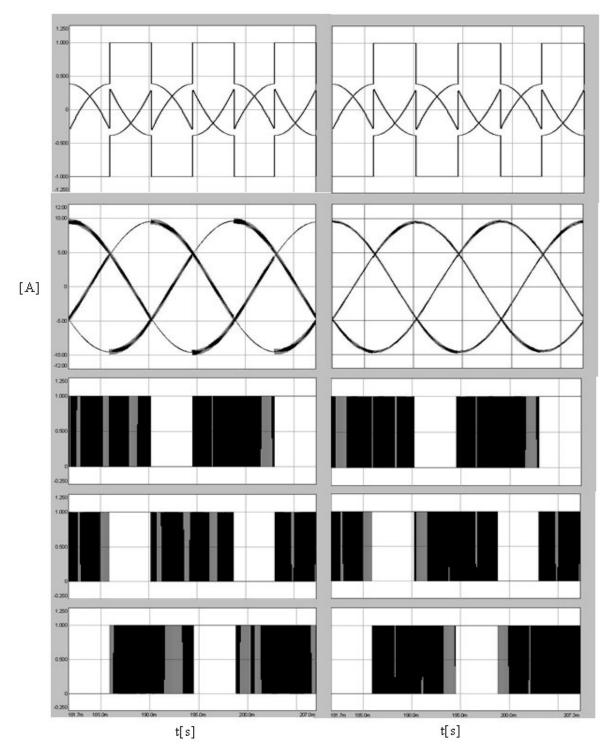

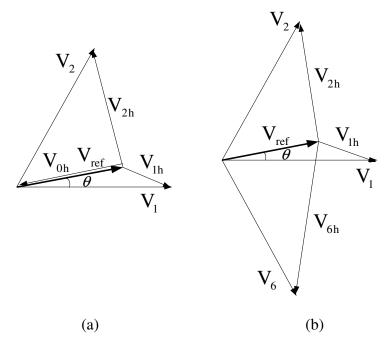

Figure 2.5 Zero sequence signal injection diagram for PWM methods [16].