# PIPELINED DESIGN APPROACH TO MICROPROCESSOR ARCHITECTURES A PARTIAL IMPLEMENTATION: MIPS™ PIPELINED ARCHITECTURE ON FPGA

## A THESIS SUBMITTED TO THE GRADUATE SCHOOL OF NATURAL AND APPLIED SCIENCES OF MIDDLE EAST TECHNICAL UNIVERSITY

ΒY

# MUZAFFER CAN ALTINİĞNELİ

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE IN ELECTRICAL AND ELECTRONICS ENGINEERING

DECEMBER 2005

Approval of the Graduate School of Natural and Applied Sciences

Prof. Dr. Canan ÖZGEN Director

I certify that this thesis satisfies all the requirements as a thesis for the degree of Master of Science.

Prof. Dr. İsmet ERKMEN Head of Department

This is to certify that we have read this thesis and that in our opinion it is fully adequate, in scope and quality, as a thesis for the degree of Master of Science.

Prof. Dr. Hasan GÜRAN Supervisor

| Examining Committee Members         |            |  |

|-------------------------------------|------------|--|

| Assist. Prof. Dr. Cüneyt BAZLAMAÇCI | (METU, EE) |  |

| Prof. Dr. Hasan GÜRAN               | (METU, EE) |  |

| Dr. Ece (GÜRAN) SCHMIDT             | (METU, EE) |  |

| Assist. Prof. Dr. İlkay ULUSOY      | (METU, EE) |  |

| M.S. Eng. Murat ŞANSAL              | (ASELSAN)  |  |

I hereby declare that all information in this document has been obtained and presented in accordance with academic rules and ethical conduct. I also declare that, as required by these rules and conduct, I have fully cited and referenced all material and results that are not original to this work.

Name, Last Name: Muzaffer Can ALTINİĞNELİ

Signature :

# ABSTRACT

#### PIPELINED DESIGN APPROACH TO MICROPROCESSOR ARCHITECTURES A PARTIAL IMPLEMENTATION: MIPS™ PIPELINED ARCHITECTURE ON FPGA

ALTINİĞNELİ, Muzaffer Can M.S, Department of Electrical and Electronics Engineering Supervisor: Prof. Dr. Hasan GÜRAN

September 2005, 120 Pages

This thesis demonstrate how pipelining in a RISC processor is achieved by implementing a subset of MIPS R2000 instructions on FPGA. Pipelining, which is one of the primary concepts to speed up a microprocessor is emphasized throughout this thesis. Pipelining is fundamentally invisible for high level programming language user and this work reveals the internals of microprocessor pipelining and the potential problems encountered while implementing pipelining. The comparative and quantitative flow of this thesis allows to understand why pipelining is preferred instead of other possible implementation schemes. The methodology for programmable logic development and the capabilities of programmable logic devices are also given as background information. This thesis can be the starting point and reference for programmers who are willing to get familiar with microprocessors and pipelining.

Keywords: Microprocessor, MIPS, Pipelining, FPGA

### MİKRO İŞLEMCİLERDE PIPELINED DİZAYN YAKLAŞIMI MIPS™ PIPELINED İŞLEMCİ MİMARİSİNİN FPGA ÜZERİNDE KISMI BİR UYGULAMASI

ALTINİĞNELİ, Muzaffer Can Yüksek Lisans, Elektrik Elektronik Mühendisliği Tez Yöneticisi: Prof. Dr. Hasan GÜRAN

Eylül 2005, 120 Sayfa

Bu çalışmada, RISC işlemcilerde "Pipelining" konusu, FPGA üzerinde MIPS R2000 komut setinin bir kısmı tamamlanarak açıklanmıştır. Çalışma boyunca, Mikro İşlemcilerin hızlarının arttırılması konusunda temel bir unsur olan "Pipelining" konusu üzerinde durulmuştur. Temel olarak "Pipelining" işlevi, yüksek seviyede programlama yapan kişilere görünmezdir. Bu çalışma "Pipelining" işlevinin ayrıntılarını ve bu işlev gerçekleştirilirken karşılaşılan problemleri ortaya koymaktadır. "Pipelining" dışındaki diğer tasarım yaklaşımlarının neden uygulanamaz oldukları, bu tezin karşılaştırmalı ve nicel akışı sayesinde anlaşılabilir. Donanım tasarımında temel alınan metodolojiler ve donanımların kabiliyetleri hakkında tez boyunca bir alt yapı oluşturulmaya da çalışılmıştır. Bu tez, Mikro İşlemciler ve "Pipelining" işlevi ile tanışıklık kazanmak isteyen programcılar için bir başlangıç ve referans noktası olabilir.

Anahtar Kelimeler: Mikro İşlemci, MIPS, Pipeline, FPGA

To My Generous Family

# ACKNOWLEDGMENTS

I owe much gratitude to my Advisor, Professor Dr. Hasan Güran, for inspiring me to carry out this thesis. His criticism and suggestions bring this work to this point and I am always aware during our work that this thesis is first of all for my benefit.

Everyone working at ASELSAN deserve my thanks, especially Erdinç Atılgan, Kemal Burak Codur and Murat Şansal. They guided me to right technical people, supported me technically and mentally during my work. This thesis ended up with an implementation because ASELSAN gave the hardware support without waiting any outcome despite it is a commercial organization.

I also owe lots to my father, mother and sister. They interested in all of my needs while I was embedded to my work. I also grasp the idea of being a family in addition to fundamentals of pipelining in microprocessors at the end of this work.

# TABLE OF CONTENTS

| PLAGIARISMi<br>ABSTRACTiv                                            |

|----------------------------------------------------------------------|

| ÖZ                                                                   |

| ACKNOWLEDGMENTS                                                      |

| TABLE OF CONTENTS                                                    |

| LIST OF TABLES                                                       |

| LIST OF FIGURES                                                      |

| LIST OF ABBREVIATIONS                                                |

| CHAPTER                                                              |

|                                                                      |

| 1. INTRODUCTION                                                      |

| 2. BACKGROUND AND MOTIVATION                                         |

| 2.1. Programmable Logic Design                                       |

| 2.1.1. History of Programmable Logic                                 |

| 2.1.1.1. Simple Programmable Logic Device (SPLD)                     |

| 2.1.1.1.1. Programmable Logic Array (PLA)                            |

| 2.1.1.1.2. Programmable Array Logic (PAL)                            |

| 2.1.1.2. Complex Programmable Logic Device (CPLD)                    |

| 2.1.1.3. Field Programmable Logic Gate Array (FPGA)                  |

| 2.1.2. Basic Design Process                                          |

| 2.2. Integrated Software Environment (ISE <sup>™</sup> ) 10          |

| 2.3. Virtex™ FPGA13                                                  |

| 2.3.1. Function Generation Capabilities of CLB                       |

| 2.3.2. Distributed (Shallow) Memory Usage of CLB 15                  |

| 2.3.3. Shift Register Configuration of CLB                           |

| 2.3.4. Arithmetic Capabilities of CLB 15                             |

| 2.4. PCI Host Software: In-Circuit Debugging of the Architecture 16  |

| 3. RELATED RESEARCH                                                  |

| 3.1. MIPS R2000 Instruction Set Architecture (ISA)                   |

| 3.2. MIPS Instructions and MIPS Assembly Language                    |

| 3.2.1. MIPS Instruction Format                                       |

| 3.2.2. MIPS Addressing Modes                                         |

| 3.2.3. MIPS Instruction Decoding                                     |

| 3.3. Survey of Instruction Set Architecture Implementation Scheme 24 |

| 3.3.1. Single Cycle Implementation Scheme                            |

| 3.3.2. Multi Cycle Implementation Scheme                             |

| 3.3.3. Pipelined Implementation Scheme                               |

| 3.3.4. Quantitative Comparison of Implementation Schemes 31          |

| 3.4. Problems and Solutions in Pipelined Architectures                       | 33  |

|------------------------------------------------------------------------------|-----|

| 3.4.1. Structural Hazards                                                    | 33  |

| 3.4.2. Brach Hazards                                                         |     |

| 3.4.3. Data Hazards                                                          |     |

| 3.4.4. Exception Hazard                                                      | 37  |

| 4. IMPLEMENTATION OF MIPS PIPELINED ARCHITECTURE                             |     |

| 4.1. Internal Structure of the Processor                                     |     |

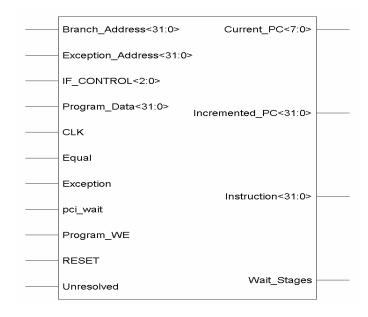

| 4.1.1. Instruction Fetch Unit                                                |     |

| 4.1.1.1. Input/Output Signals of Instruction Fetch Unit                      |     |

| 4.1.1.2. Function of Instruction Fetch Unit                                  |     |

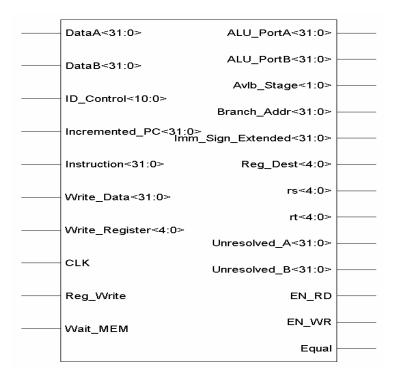

| 4.1.2. Instruction Decode Unit                                               |     |

| 4.1.2.1. Input/Output Signals of Instruction Decode Unit                     |     |

| 4.1.2.2. Function of Instruction Decode Unit                                 |     |

| 4.1.3. Forwarding and Hazard Detection Unit                                  | 49  |

| 4.1.3.1. Input/Output Signals of Forwarding and Hazard                       |     |

| Detection Unit                                                               |     |

| 4.1.3.2. Function of Forwarding and Hazard Detection Unit                    |     |

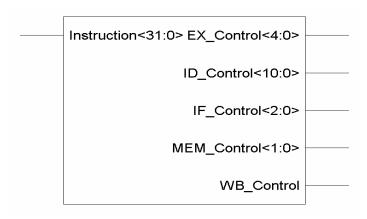

| 4.1.4. Control Unit                                                          |     |

| 4.1.4.1. Input/Output Signals of Control Unit                                |     |

| 4.1.4.2. Function of Control Unit                                            |     |

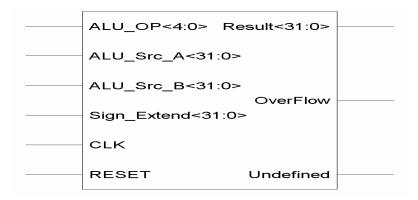

| 4.1.5. Execute Unit                                                          |     |

| 4.1.5.1. Input/Output Signals of Execute Unit                                |     |

| 4.1.5.2. Function of Execute Unit                                            |     |

| 4.1.6. Data Memory Unit<br>4.1.6.1. Input/Output Signals of Data Memory Unit | 57  |

| 4.1.6.2. Function of Data Memory Unit                                        |     |

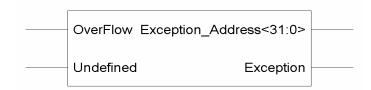

| 4.1.7. Exception Detection Unit                                              |     |

| 4.1.7.1. Input/Output Signals of Exception Detection Unit                    |     |

| 4.1.7.2. Function of Exception Detection Unit                                |     |

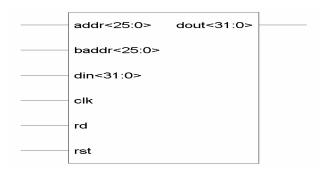

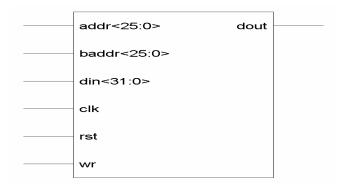

| 4.1.8. Register Blocks between Stages of Processor                           |     |

| 4.2. External Structure of the Processor                                     |     |

| 4.2.1. External Monitoring of the Processor                                  |     |

| 4.2.2. External Manipulation of the Processor                                |     |

| 5. VERIFICATION OF MIPS PIPELINED ARCHITECTURE                               |     |

| 5.1. Verification of Correct Operation of Instructions                       |     |

| 5.2. Verification of Hazard Detection and Handling                           |     |

| 5.3. Verification of Exception Handling                                      |     |

| 6. CONCLUSIONS AND FUTURE WORK                                               | 91  |

| REFERENCES                                                                   |     |

| APPENDICIES                                                                  |     |

| A. IMPLEMENTED SUBSET OF MIPS R2000 ISA                                      | 96  |

| B. MIPS MONITOR SOFTWARE                                                     | 105 |

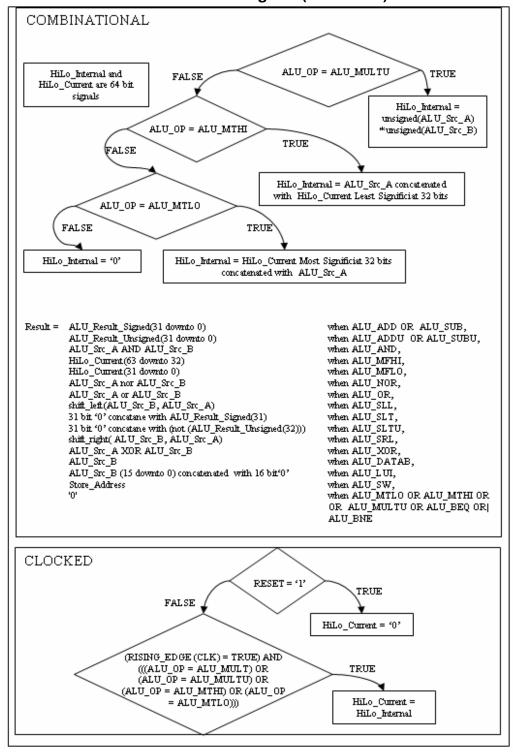

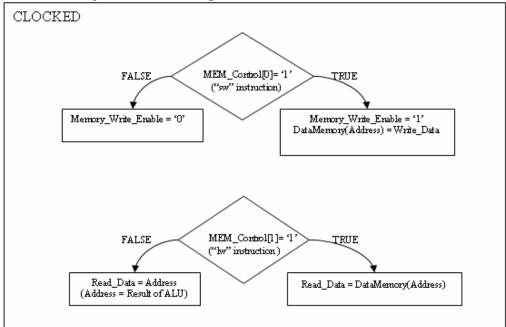

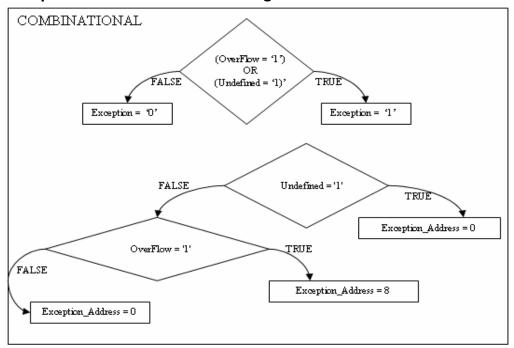

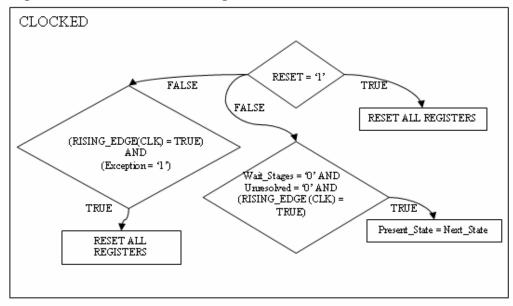

| C. FLOW DIAGRAMS ARCHITECTURE ELEMENTS            | 112 |

|---------------------------------------------------|-----|

| Instruction Fetch Unit Flow Diagram               | 112 |

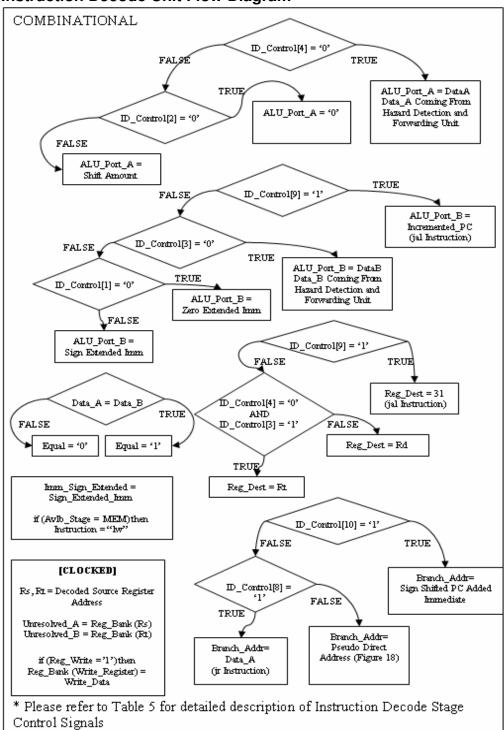

| Instruction Decode Unit Flow Diagram              | 113 |

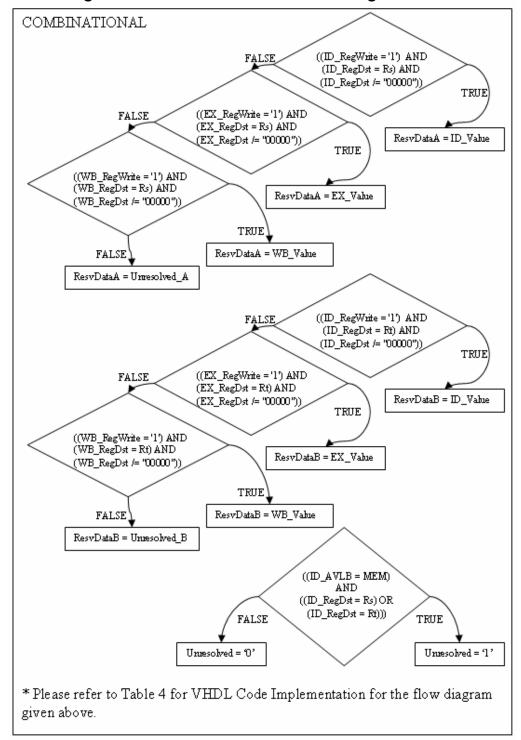

| Forwarding and Hazard Detection Unit Flow Diagram | 114 |

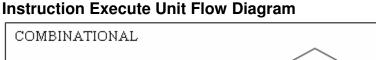

| Instruction Execute Unit Flow Diagram             | 115 |

| Instruction Execute Unit Flow Diagram (continued) | 116 |

| Data Memory Unit Flow Diagram                     | 117 |

| Exception Detection Unit Flow Diagram             | 117 |

| Register Block Unit Flow Diagram                  | 118 |

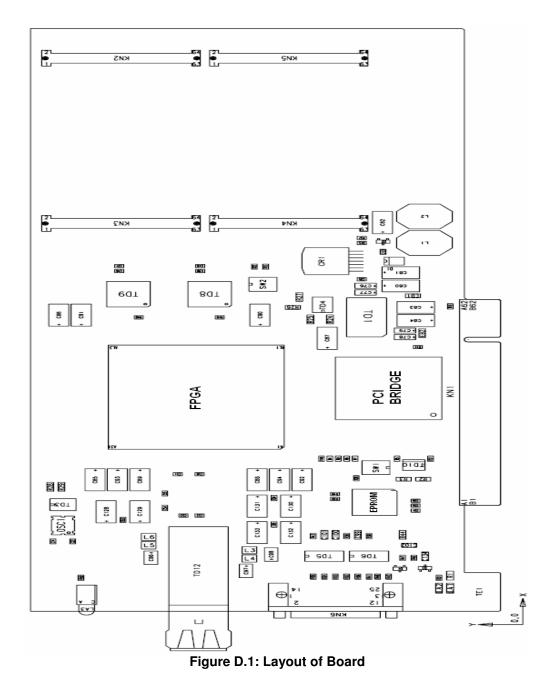

| D. LAYOUT OF BOARD                                | 119 |

| E. RESOURCES IN THIS THESIS                       | 120 |

# LIST OF TABLES

# TABLE

| 3.1: Calculation of CPI for Multi Cycle Implementation Scheme     | . 32 |

|-------------------------------------------------------------------|------|

| 3.2: Instruction Time Calculation for Implementation Schemes      | . 33 |

| 4.1: Forwarding Mechanism for Register Bank Primary Port          | . 50 |

| 4.2: Forwarding Mechanism for Register Bank Secondary Port        | . 50 |

| 4.3: ID_Control Signal Fields                                     | . 53 |

| 4.4: EX_Control ALUOp Signal Values                               | . 53 |

| 4.5: Base Addresses of Processor's Internal Signals               | . 63 |

| 5.1: Verification of Correct Instruction Operation                | . 68 |

| 5.2: Timing Diagram for Instruction Operation Verification        | . 70 |

| 5.3: Verification of Hazard Detection and Handling                | . 77 |

| 5.4: Timing Diagram for Handling Hazard Verification              | . 79 |

| 5.5: Verification of Exception Handling "ADDU" and "ADD"          | . 83 |

| 5.6: Timing Diagram for Exception Handling of ADDU and ADD        | . 84 |

| 5.7: Verification of Exception Handling "SUBU" and "SUB"          | . 85 |

| 5.8: Timing Diagram for Exception Handling of SUBU and SUB        | . 86 |

| 5.9: Verification of Exception Handling "ADDIU" and "ADDI"        | . 87 |

| 5.10: Timing Diagram for Exception Handling of ADDIU and ADDI     | . 88 |

| 5.11: Verification of Exception Handling Undefined Instructions   | . 89 |

| 5.12: Timing Diagram for Undefined Instruction Exception Handling | . 90 |

| A.1: MIPS Registers                                               | 104  |

|                                                                   |      |

# **LIST OF FIGURES**

# FIGURE

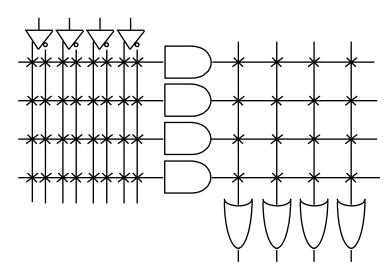

| 2.1: PLA Architecture                                             | 6    |

|-------------------------------------------------------------------|------|

| 2.2: PAL Architecture                                             |      |

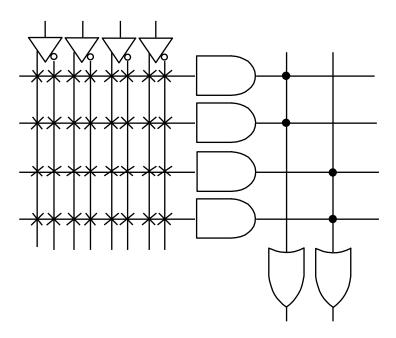

| 2.3: CPLD Architecture                                            |      |

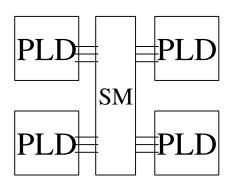

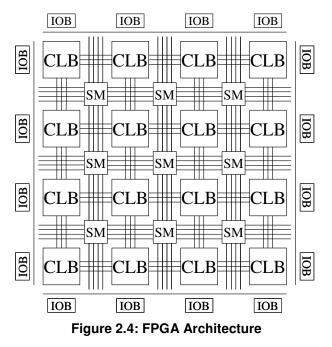

| 2.4: FPGA Architecture                                            |      |

| 2.5: Basic Design Flow in FPGAs, ©Xilinx                          |      |

| 2.6: MIPS Project Properties Window                               |      |

| 2.7: MIPS Project Source File Listing                             |      |

| 2.8: Virtex Architecture Overview ©Xilinx                         |      |

| 2.9: Function Generator Configuration of CLB.                     |      |

| 2.10: Carry Logic Diagram ©Xilinx                                 |      |

| 2.11: Multiplier Implementation ©Xilinx                           |      |

| 2.12: MIPS Monitor Software                                       |      |

| 3.1: MIPS Instruction Format                                      |      |

| 3.2: Immediate Addressing Mode                                    |      |

| 3.3: Register Addressing Mode                                     |      |

| 3.4: Base Addressing Mode                                         |      |

| 3.5: PC Relative Addressing Mode                                  | 23   |

| 3.6: Pseudo Direct Addressing Mode                                | 23   |

| 3.7: MIPS Opcode Map and Frequency of Instructions                | 24   |

| 3.8: Single Cycle Implementation Scheme ©[COD98]                  |      |

| 3.9: Multi Cycle Implementation Scheme ©[COD98]                   | . 28 |

| 3.10: State Flow Diagram of Multi Cycle Scheme Control Unit       |      |

| 3.11: Pipelined Implementation Scheme ©[COD98]                    | 30   |

| 3.12: Simultaneously Executing Instructions in Pipeline           | 31   |

| 3.13: Single and Multi Cycle Instruction Sequence                 |      |

| 3.14: Data Hazard Solution by Forwarding                          |      |

| 3.15: Data Hazard Solution by Stalling and Forwarding             |      |

| 3.16: Forwarding of the Most Recent Data                          |      |

| 4.1: Internal Structure of the Pipelined Processor                |      |

| 4.2: External Structure of the Pipelined Processor                |      |

| 4.3: Input/Output Signals of Instruction Fetch Unit               |      |

| 4.4: Input/Output Signals of Instruction Decode Unit              |      |

| 4.5: Input/Output Signals of Forwarding and Hazard Detection Unit | 51   |

| 4.6: Input/Output Signals of Control Unit                         | 55   |

| 4.7: Input/Output Signals of Execute Unit                         |      |

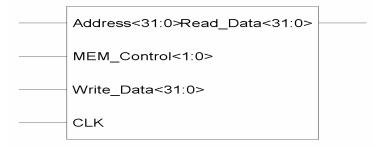

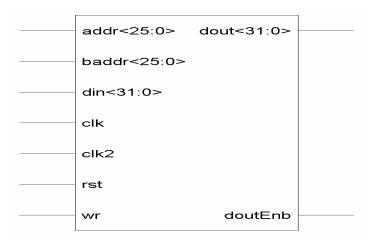

| 4.8: Input/Output Signals of Data Memory Unit                     | 58   |

| 4.9: Input/Output Signals of Exception Detection Unit             | 60   |

| 4.10: Input/Output Signals of Reg Unit                 |     |

|--------------------------------------------------------|-----|

| 4.11: Input/Output Signals of Reg_Wr Unit              |     |

| 4.12: StateCAD Diagram of Wait_Sm Unit                 | 65  |

| 4.13: Input/Output Signals of Reg_Prg Unit             | 66  |

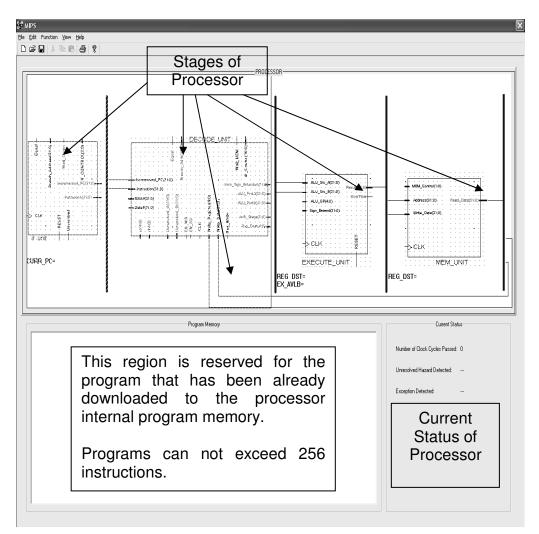

| B.1: Main Screen of MIPS Monitor Software              | 106 |

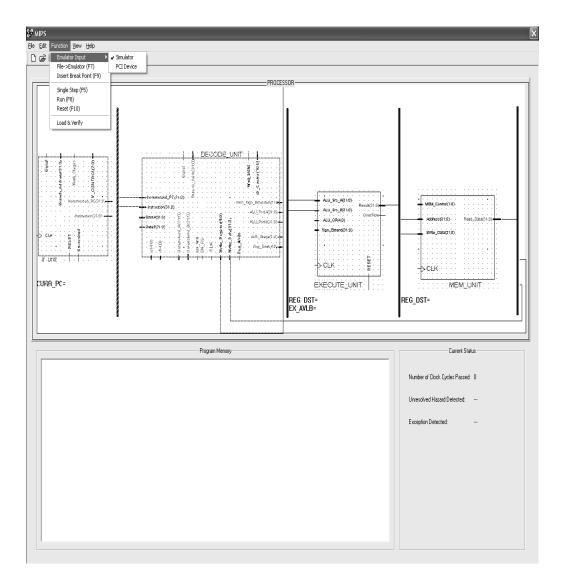

| B.2: Main Functions of MIPS Monitor Software           | 107 |

| B.3: PCI Device Selection Dialog                       | 108 |

| B.4: PCI Device Selection Dialog                       | 109 |

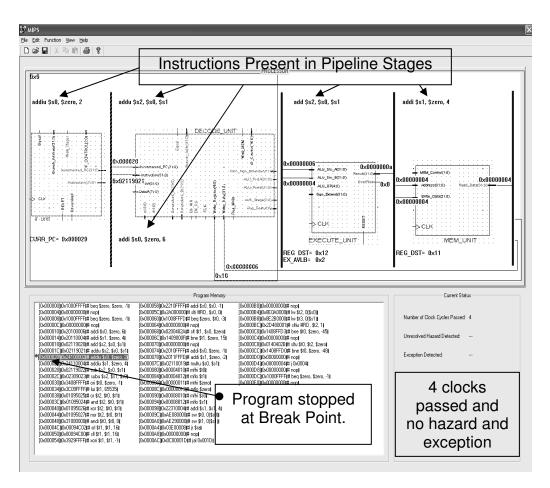

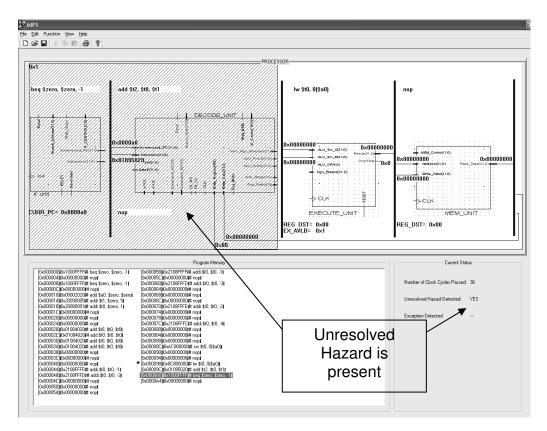

| B.5: Unresolved Hazards View                           | 110 |

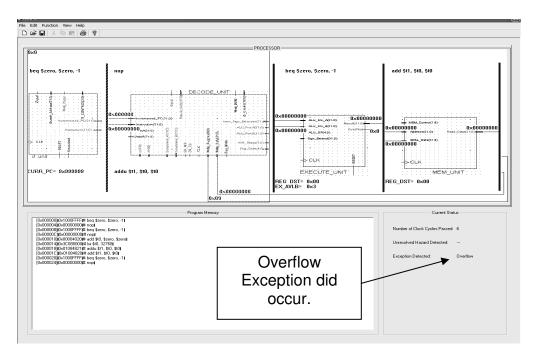

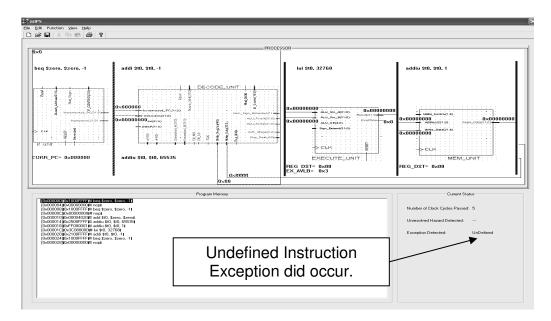

| B.6: Overflow Exception Detection View                 | 111 |

| B.7: Undefined Instruction Exception Detection View    | 111 |

| C.1: Instruction Fetch Unit Flow Diagram               |     |

| C.2: Instruction Decode Unit Flow Diagram              | 113 |

| C.3: Forwarding and Hazard Detection Unit Flow Diagram | 114 |

| C.4: Instruction Execute Unit Flow Diagram             | 115 |

| C.5: Instruction Execute Unit (continued) Flow Diagram | 116 |

| C.6: Data Memory Unit Flow Diagram                     | 117 |

| C.7: Exception Detection Unit Flow Diagram             | 117 |

| C.8: Register Block Unit Flow Diagram                  |     |

| D.1: Layout of Board                                   | 119 |

|                                                        |     |

# LIST OF ABBREVIATIONS

| ALU  | Arithmetic Logic Unit                              |

|------|----------------------------------------------------|

| API  | Application Interface                              |

| ASIC | Application Specific Integrated Circuit            |

| BRAM | Block Random Access Memory                         |

| CISC | Complex Instruction Set Computer                   |

| CLB  | Configurable Logic Block                           |

| CLK  | CLocK                                              |

| CPI  | Clock cycle Per Instruction                        |

| CPLD | Complex Programmable Logic Device                  |

| DLL  | Delay Locked Loop                                  |

| EX   | Execute (stage)                                    |

| FF   | Flip Flop                                          |

| FPGA | Field Programmable Gate Array                      |

| GCC  | Gnu C Compiler                                     |

| GPR  | General Purpose Register                           |

| HDL  | Hardware Description Language                      |

| ID   | Instruction Decode (stage)                         |

| IF   | Instruction Fetch (stage)                          |

| IOB  | Instruction Set Architecture                       |

| ISA  | Integrated Software Environment                    |

| ISE  | Look Up Table                                      |

| LUT  | Memory (stage)                                     |

| MEM  | Microprocessor without Interlocked Pipeline Stages |

| MIPS | MUItipIXer                                         |

| MUX  | No Operation (instruction)                         |

| NOP  | Programmable Array Logic                           |

| PAL  | Program Counter                                    |

| PC   | Printed Circuit Board                              |

| PCB  | Programmable Logic Array                           |

| PLA  | Programmable Logic Array                           |

| PROM | Programmable Read Only Memory                      |

| RISC | Reduced Instruction Set Computer                   |

| SoRC | System on Re-programmable Chip                     |

| SPLD | Simple Programmable Logic Device                   |

| RISC | Reduced Instruction Set Computer                   |

| SoRC | System on Re-programmable Chip                     |

|      |                                                    |

# **CHAPTER 1**

# INTRODUCTION

Faster execution of computer programs was the one of the most challenging concerns of engineers in the past and also will be much more challenging in the future. Increased demands of the industry for real time applications yield the presence of faster and deterministic processor architectures in years in the market.

Developers have always been under the effect of their era's restrictions while determining their architectural approach. This was the reason why Complex Instruction Set based computers (CISC) came before the much simpler counter parts, the Reduced Instruction Set (RISC) based computers. Developers constructed first more challenging CISC because of memory restrictions and little compiler support. Developments in memory technology in parallel with compiler enhancements resulted in emergence of RISC based computers. They are much simpler to build, much simpler to understand; hence open for improvements and maintenance.

The number of high level programming language compilers developed and specialized for RISC architectures grew rapidly. High level programming became more popular over years and programmers kept away from low level error prone long lasting assembly programming. Another reason for choosing high level programming is that different vendors proposed different architectures; hence it was not feasible to learn the architecture specific assembly code. Pipelining is one way of increasing the processor's performance. It was proposed for RISC based computers mainly because of their regularity. Pipelining accompanied with improved compiler support gave superior performance and further improvements made by scaling these architectures.

The primary goal of this thesis is to grasp the idea behind pipelining by partially developing RISC architecture, specifically Microprocessor without Interlocked Pipeline Stages (MIPS), because of its simplicity and rich documentation.

Understanding the pipelining is important because pipelining is transparent to high level programmer. Programmers are aware of Program Counter (PC), register bank and memory when they debug their programs, but they can not observe the internal register blocks used for pipelining. Programmers can not understand why the assembly code generated by different compiler vendors is different for the same high level software without knowing the internals of pipelining even they know the compiler well.

The secondary goal of this thesis is to understand the problems faced in pipelining, because it is the first step that comes before the superscalar speculative architectures. To go one step further, problems in pipelining must be solved.

The last goal of this thesis is to get familiarity with hardware design process cycle and grasp internals of programmable logic design especially for Field Programmable Gate Arrays (FPGAs). FPGAs promise parallelism which is the key concept for speed. FPGAs are reprogrammable and are becoming more popular in the market. They replace to application specific integrated circuit (ASIC) and discrete processors and they are also called as system on reprogrammable chip (SoRC).

2

This thesis is organized as follows: Chapter 2 serves to provide necessary background for development environment, programmable logic design and FPGAs. Chapter 3 describes the different implementation schemes for the same instruction set and clarifies why pipelining is the best quantitatively. It also describes the problems encountered in pipelining and solution proposals. Chapter 4 gives the details of particular subset of MIPS implementation. Chapter 5 is devoted for formal verification of the partially implemented architecture by using in circuit debugging at runtime via specially developed software, MIPS Monitor. Chapter 6 gives the conclusions and makes remarks for further future work. The appendices presents the implemented instruction set assembly codes, instruction descriptions and some screen shots to demonstrate the usage of MIPS Monitor software.

# **CHAPTER 2**

# **BACKGROUND AND MOTIVATION**

This chapter serves for the following purposes:

- providing the necessary background for understanding the rest of thesis,

- (2) motivations behind the usage of software and hardware development environments in thesis,

- (3) internals of platform FPGA which was preferred as design solution,

Readers, who are quite familiar with these concepts, can skip this chapter and start reading Chapter 3 first.

## 2.1. Programmable Logic Design

Since late 1970s, programmable logic circuits are greatly enhanced and dominated the electronics market. Developers had a tendency to use reprogrammable devices (simple and complex programmable logic devices), instead of application specific integrated circuits (ASIC) to develop large and interoperable systems because of their following characteristics [XDRM99]:

- Low cost per gate.

- Reduces Risk; engineers can make design changes in minutes.

- Faster Testing and Manufacturing.

- Ease in Verification.

- Ability participating in Hardware-Software Co-Design.

- Versatile support for Input/Output Standards.

# 2.1.1. History of Programmable Logic

By the late 1970s, standard logic components were exclusively used as standard building blocks of logic circuits. These components (e.g., 74XX series TTL parts) were located on printed circuit boards (PCBs) and any change in logic resulted corresponding revision in PCB layout. The side effects encountered, when some part of design changed, was able to be avoided by replacing these components with programmable logic devices (PLDs). Given that the design in PLDs was flexible, no rewiring on PCBs was required. In addition, less board area and power was consumed by PLDs. PLDs can be divided in two sets as simple and complex PLD.

## 2.1.1.1. Simple Programmable Logic Device (SPLD)

These devices are mainly used for address decoding [Barr99].

# 2.1.1.1.1. Programmable Logic Array (PLA)

Ron Cline from Signetics<sup>™</sup> put forward the idea of two programmable planes on 1975 [XPM04]. Any combinatorial logic can be expressed in the form of two level logics: as product of sums or sum of products. For that reason, by using PLA, any combinational logic can be implemented, if number of inputs and outputs are enough for required implementation. Despite the architecture is very flexible, because of

high fuse count, propagation delay is higher than PAL. Unwanted connections (fuse) are blown after programming.

Figure 2.1: PLA Architecture

## 2.1.1.1.2. Programmable Array Logic (PAL)

John Birkner from MMI proposed a second alternative for the PLA array on 1978. Instead of one programmable planes, the OR array was fixed after fabrication [XPM04]. PALs are more constrained than PLAs, but, because of fewer connections, they have lower propagation delay.

Figure 2.2: PAL Architecture

### 2.1.1.2. Complex Programmable Logic Device (CPLD)

Macrocells were obtained by extending PLDs with additional flip flops (FFs). CPLDs were simply combinations of these macrocells with programmable interconnects, switch matrix (SM). SM within CPLD may or may not be fully connected unlike the programmable interconnect within PLD. In other words, some of theoretically possible connections between PLDs may not actually be supported within a given CPLD. Therefore 100% utilization of macrocells is very difficult to achieve. Some designs will not fit a given CPLD, even though there are sufficient logic gates and FFs.

CPLDs can also be used as address decoders like PLDs, but more often as high performance control logic and finite state machines. Traditionally, CPLDs have been chosen over FPGAs, whenever high performance logic is required [Barr99].

Figure 2.3: CPLD Architecture

#### 2.1.1.3. Field Programmable Logic Gate Array (FPGA)

In 1985, a company called Xilinx<sup>™</sup> introduced FPGAs, composed of configurable logic blocks (CLBs), which are surrounded by programmable interconnects and comprise function generators or look up tables (LUTs) and flip flops (FFs). FPGAs can be one time programmable similar to PLD or SRAM based (or reprogrammable). [XPM04] [TRENZ01] [BZEID]

#### 2.1.2. Basic Design Process

Design entry or design specification can be in the form of schematic capture or hardware description language (HDL). In schematic form, after determining the capture tool and the manufacturer's library, designer can connect the gates from library with wires and then generates netlist, which is the textual description of the circuit. Schematic capture is not feasible for large designs because it is not scalable, not reusable, strongly vendor dependent and hard to maintain. In HDL design entry, the design is entered in high level description language emphasizing design's function or behavior and then synthesized by the vendor independent tool and netlist is generated. The design is more maintainable, scalable and reusable than schematic design entry.

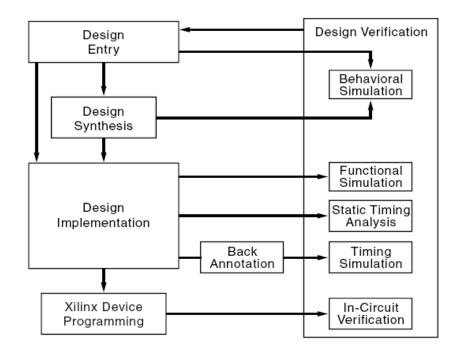

Figure 2.5: Basic Design Flow in FPGAs, ©Xilinx

In design implementation, the first step is translation of low level and generic netlist file into device specific resources. After translation step, mapping step checks the design according to device specific rules, add further logic or make replications to meet the timing requirements using device resources. At last, in place and route step, already allocated resources are distributed along FPGA taking into account the physical constraints and routing resources. At this point physical layout is determined and timing information for design entities and interconnects (Back Annotation) is available. After routing, the device is ready to be programmed.

In device programming stage, the SRAM based FPGA's configuration, which is volatile after power on and also defining the logic and interconnect, is programmed to a Programmable Read Only Memory (PROM) device with part name xc18v02.

Design verification is a parallel process to design development. Design entry in either schematic or HDL form can be simulated behaviorally, while it can be tested based on the code syntax. After synthesis phase, generated netlist format can be simulated functionally by providing test vectors and tested by checking the desired output vector. Timing simulation comes after the place and route phase using back annotation.

### 2.2. Integrated Software Environment (ISE™)

Integrated Software Environment is the environment provided by Xilinx<sup>™</sup> for Design Entry, Design Synthesis, Design Implementation, Design Verification and Device Programming phases (described in 2.1.2) of design development [XISE03]. MIPS project was created in ISE with the project properties given in Figure 2.6.

| Project Properties            | ×                  |

|-------------------------------|--------------------|

| Project Properties            |                    |

| Property Name                 | Value              |

| Device Family                 | Virtex 🔽           |

| Device                        | xcv300             |

| Package                       | bg432              |

| Speed Grade                   | -5                 |

|                               |                    |

| Top-Level Module Type         | Schematic          |

| Synthesis Tool                | XST (VHDL/Verilog) |

| Simulator                     | Modelsim           |

| Generated Simulation Language | VHDL               |

|                               |                    |

|                               |                    |

| OK Cance                      | el Default Help    |

Figure 2.6: MIPS Project Properties Window

Top-Level module for Design Entry is selected as Schematic Capture for visualization purposes. All other sub-modules are coded in hardware description language VHDL [CDVHDL] [Perry02]. XST (Xilinx Synthesis Technology) tool was used to synthesize netlist from VHDL code. Modelsim® simulator was selected for post-place and route simulation purposes.

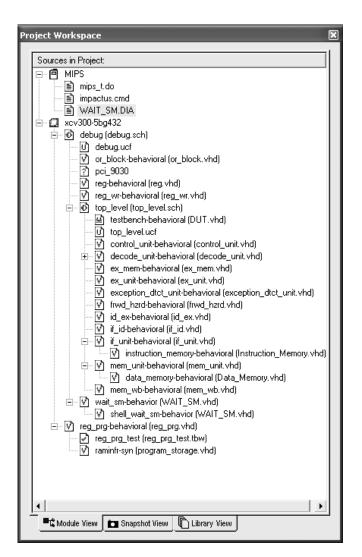

Figure 2.7: MIPS Project Source File Listing

MIPS project comprise source files describing the architecture of entities which are listed in (Figure 2.7) for the following purposes;

- Design Entry (e.g. file extensions \*.vhd and \*.sch )

- Physical and Timing user constraints files for Design Implementation (e.g. file extension \*.ucf)

- Test Bench files for Post-Place and Route Simulation (e.g. file extensions \*.vhd)

- Post-Place and Route simulation macro file which compiles the design and Test Bench files, invokes the simulator, loads signals to view windows and runs the simulation for specified time duration. (e.g. file extension \*.do)

- State Machine editor file (e.g. file extension \*.dia)

- Impactus command file for device programming (e.g. file extension \*.cmd)

# 2.3. Virtex<sup>™</sup> FPGA

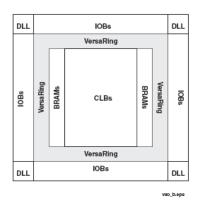

MIPS project is implemented on an xcv300-5bg432 Virtex FPGA device with the following properties and layout (Figure 2.8): [XDS003-2] [SYNP99] [XCNSTR] [Brown96]

- 32x48 CLB Array provide functional elements for constructing logic connected by global routing matrix or switch matrix (Figure 2.4),

- VersaRing<sup>™</sup> forms the interface between Input Output Blocks (IOBs) and CLBs,

- 16 Block Rams (BRAMs) each 4096x1 totally 65536x1 bits,

- 4 Delay-Locked Loops (DLLs) that eliminate the skew between the clock input pad and internal clock input pins throughout the device,

- Ball grid 432 package having 316 I/O pins reserved for users with speed grade -5 which yields system performance up to 200 MHz.

Figure 2.8: Virtex Architecture Overview ©Xilinx

### 2.3.1. Function Generation Capabilities of CLB

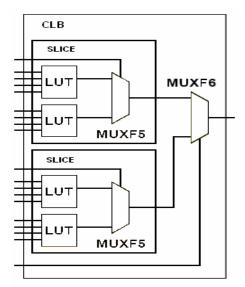

Each CLB comprises 4 function generator (LUTs) distributed into two slices. Each slice contains 2 function generators and additional logic that combines the outputs of LUTs and generates 5 (MUXF5) and 6 (MUXF6) input functions (Figure 2.9). Each slice can generate any functions of 5 inputs up to some functions of 9 inputs; hence any CLB can generate any functions of 6 inputs up to some functions of 19 inputs.

Figure 2.9: Function Generator Configuration of CLB

### 2.3.2. Distributed (Shallow) Memory Usage of CLB

Each LUT in a Slice can be configured as 16x1 bit synchronous RAM and two LUTs in a Slice can be configured as 16x2 bit or 16x1 bit dual port or 32x1 bit synchronous RAM.

### 2.3.3. Shift Register Configuration of CLB

Each LUT in a slice can be configured as dynamically addressable16 bit shift register.

#### 2.3.4. Arithmetic Capabilities of CLB

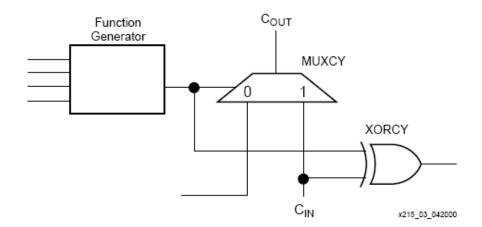

Each LUT in a slice has a dedicated XORCY gate for single bit sum to form a full adder and dedicated carry path (Figure 2.10) which is using also dedicated routing resources along vertically adjacent CLBs [XAPP215]. By introducing the additional XORCY gate, 2 inputs of LUT left as spare and these inputs can be used to implement additional logic thereby increasing cell functionality. [TW04] [KCHAP93] [DFMULT]

Figure 2.10: Carry Logic Diagram ©Xilinx

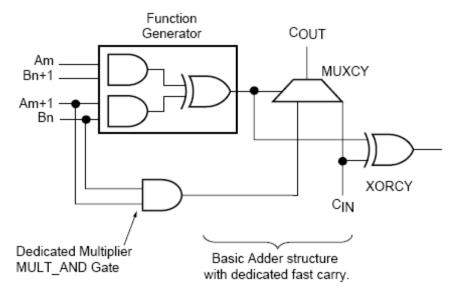

Multiplication in FPGA is performed by shifting and adding the partial products in parallel fashion. There exists 2 input AND gate per LUT to implement 1 bit multiplier [XAPP215] and this pattern repeats throughout the multiplier. In case of operands (partial products) are not equal to each other  $C_{IN}$  signal is propagated (Figure 2.11). Additional AND gate is essential to kill or generate  $C_{OUT}$  signal produced when the propagation of  $C_{IN}$  signal is stopped (when both operands equal) [HPCC].

Figure 2.11: Multiplier Implementation ©Xilinx

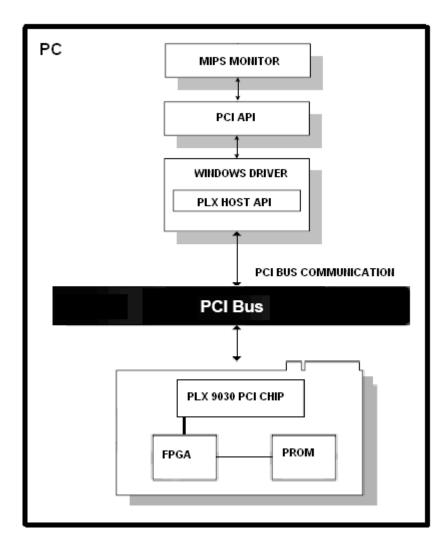

### 2.4. PCI Host Software: In-Circuit Debugging of the Architecture

The "MIPS Monitor" (Figure 2.12) software which is running on PC was developed to debug the architecture after generated configuration was programmed into the target PROM or a new program is ready to be programmed while Virtex FPGA was running [PLXSDK01].

"MIPS Monitor" uses PCI Application Interface (API) provided by PLX Technology<sup>™</sup> to read the FPGA's internal data and program memory, pipeline stage's inputs/outputs, pipeline register states and current PC. It also enables the user to observe stalls and exceptions. It reflects information read by using PCI API to its graphical user interface, hence to user.

"MIPS Monitor" uses PCI API provided by PLX Technology<sup>™</sup> to write the control signals to Virtex FPGA which resets the architecture or increment the PC by one thereby enabling single step operation.

"MIPS Monitor" graphical user interface enables the user by providing the following functionalities:

- Selecting the proper PCI 9030 device which is on the same board FPGA placed,

- Viewing the program which was already assembled and programmed to PROM,

- Viewing, loading and verifying a new program to local block instruction memory of FPGA.

- Inserting break points and running the architecture in single step or in free mode by using the graphical user interface of "MIPS Monitor".

Figure 2.12: MIPS Monitor Software

The layout of the board used during this thesis is given in APPENDIX D, Layout of Board.

# **CHAPTER 3**

# **RELATED RESEARCH**

### 3.1. MIPS R2000 Instruction Set Architecture (ISA)

MIPS R2000 was first produced in 1988 by MIPS Computer Systems and was one of the RISC processors designed at that time. MIPS stands for Microprocessor without Interlocked Pipeline Stages and as its name implies, by eliminating pipeline interlocks between stages, instruction conflicts are resolved. Next generations are: R2010, also includes floating point co-processor, R3000 with cache control and lastly R4000 a 64 bit version of architecture. MIPS 32- and 64-bit architectures are used in networking and consumer device markets, such as in car navigation systems, digital television and cameras, video game controllers, switches and routers.

Primary metric to compare performance of Architectures is execution time of a program and it is presented in the following equation [COD98]:

| Seconds _ | Instruction Count | v | Clock Cycles | v        | Seconds     |

|-----------|-------------------|---|--------------|----------|-------------|

| Program   | Program           | ~ | Instruction  | <u> </u> | Clock Cycle |

The multiplication factors on the right hand side of the equation do not determine performance individually, but have an affect. Selected ISA affects the instruction count. ISA Implementation scheme which will be described in section 3.3 affects clock cycles per instruction (CPI). The organization and technology of the architecture affects the clock rate.

These factors also depend on each other in inversely proportional relationship, making one better makes the other worse. For example making instructions complex reduces the instruction count but may decrease the clock rate. Good performance can be obtained by, first choosing ISA then determining the implementation scheme and last determining the technology.

MIPS (Microprocessor without interlocked Pipeline Stages) R2000 ISA has RISC based architecture obeying four design principles [COD98] [JGRAY00];

- Smaller is faster, MIPS have 32 general purpose register each 32 bits length. MIPS instructions operate only on registers. Registers are smaller hence faster than external memory.

- Simplicity favors regularity, MIPS's instructions have the same size each 32 bits length and the same number of operands, hence decoding and pipelining are simpler compared to variable length instructions present in CISC ISA.

- *Good design demand good compromises,* MIPS sticks to small number of instruction types and addressing modes.

- Make common case fast (corollary of Amdahl's law), implementing commonly used instructions in fast way makes the whole architecture faster.

#### 3.2. MIPS Instructions and MIPS Assembly Language

MIPS instructions can be grouped as Arithmetic, Transfer, Branch, Immediate and Jump instructions.

Arithmetic instructions operates on registers and requires three operands, two for source one for destination. The arithmetic or logical

operation takes place on two source operands and result is written back into destination register.

Transfer instructions are used for loading data from memory to registers or storing data from registers to memory. Transfer instructions require two operands. One register content is used as base address and the immediate field in the instruction as the offset from base, the other register is used either destination address of the value to be loaded or the source address of the value to be stored.

Branch instructions operate on two register operands, evaluate the condition and according the result continue execution or take the branch by modifying the PC.

Immediate instructions use the immediate field as an operand.

Jump instructions are use the immediate field to jump unconditionally by modifying the PC.

The detailed descriptions, functionalities and assembly language formats of MIPS R2000 instructions implemented and verified in this thesis are presented in APPENDIX A, Implemented Subset of MIPS R2000 ISA.

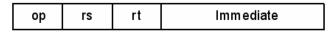

#### 3.2.1. MIPS Instruction Format

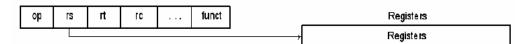

General instruction format is given in Figure 3.1.

| Field size | 6 bits | 5 bits     | 5 bits | 5 bits              | 5 bits | 6 bits                  | Comment                       |

|------------|--------|------------|--------|---------------------|--------|-------------------------|-------------------------------|

| R-format   | Op     | Rs         | Rt     | Rd                  | ShAmt  | Funct                   | Arithmetic instruction format |

| I-format   | Op     | Rs         | Rt     | Address / Immediate |        |                         | Branch, imm. format           |

| J-format   | Ор     | Target add | ress   |                     |        | Jump instruction format |                               |

#### Figure 3.1: MIPS Instruction Format

The Op field is the opcode of the instruction and used as the primary key in instruction decoding. Rs, Rt and Rd fields specify the address of

register in operation. ShAmt field specify the shift amount in operation. Funct field selects the specific variant of the operation in opcode field.

### 3.2.2. MIPS Addressing Modes

Immediate addressing (Figure 3.2) means the operand is constant within the instruction itself;

Figure 3.2: Immediate Addressing Mode

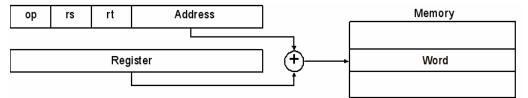

Register addressing (Figure 3.3) means where all operands are registers;

Figure 3.3: Register Addressing Mode

Base addressing (Figure 3.4) means where the operand is in memory whose address is calculated by adding base address in a register with an offset in immediate field. Addressing of memory is implemented as word (4 bytes) aligned.

Figure 3.4: Base Addressing Mode

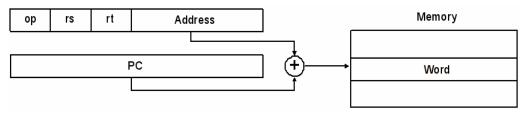

PC relative addressing (Figure 3.5) means that the instruction memory will be addressed by adding the present PC and the constant in the instruction.

Figure 3.5: PC Relative Addressing Mode

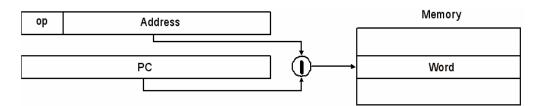

Pseudo direct addressing (Figure 3.6) means the Address field in the instruction is concatenated with the program counter and the instruction memory than addressed.

Figure 3.6: Pseudo Direct Addressing Mode

## 3.2.3. MIPS Instruction Decoding

MIPS R2000 instructions implemented and verified in this thesis were chosen according their frequency of usage in two totally different programs spice and gnu C compiler (gcc). These values were calculated from pixie which is an instruction measurement tool [COD98].

MIPS core instructions (all presented in Figure 3.7) cover 95% for gcc and 45% for spice. MIPS core instructions dominate gcc and integer plus floating point core instructions dominate spice. Instructions that did

not cover in this thesis constitute the remaining part 5% for gcc and 55% for spice. 49% of spice can be covered by simply adding a floating point arithmetic core to architecture, which results in 5% for gcc and 6% for spice as uncovered.

Instructions are decoded and control signals are generated based on Figure 3.7. Related procedures will be described in detail in 0.

| op(31:26) | Name     | gcc   | spice | func(5:0) | Name  | gcc      | spice |

|-----------|----------|-------|-------|-----------|-------|----------|-------|

| 0x00      |          |       |       |           |       | -        | l .   |

| 0x01      |          |       |       |           | sl    | 5%       | 5%    |

|           | <u> </u> |       |       | 0x02      | srl   | >0.5%    | 1%    |

| 0x02      | J        |       |       | 0x08      | jr    | 1%       | 1%    |

| 0x03      | jal      | 1%    | 1%    | 0x10      | mfhi  |          |       |

| 0x04      | beq      | 9%    | 3%    | 0x11      | mthi  |          |       |

| 0x05      | bne      | 8%    | 2%    |           |       |          |       |

| 0x08      | addi     | >0.5% | >0.5% | 0x12      | mflo  |          |       |

|           |          |       |       | 0x13      | mtio  |          |       |

| 0x09      | addiu    | 17%   | 1%    | 0x19      | multu | <u> </u> |       |

| 0x0A      | siti     | 1%    | >0.5% | 0x20      | add   | >0.5%    | >0.5% |

| 0x0B      | sltiu    | 1%    | >0.5% | 0x20      | addu  | 9%       | 10%   |

| 0x0C      | andi     | 2%    | 1%    |           |       | 8%       | 10%   |

| 0x0D      | ori      |       |       | 0x22      | sub   |          |       |

|           |          |       |       | 0x23      | subu  | >0.5%    | 1%    |

| 0x0E      | xori     |       |       | 0x24      | and   | 1%       | >0.5% |

| 0x0F      | lui      | 2%    | 6%    | 0x25      | or    |          |       |

| 0x23      | w        | 21%   | 7%    |           |       |          |       |

| 0x28      | SW       | 12%   | 2%    | 0x26      | xor   |          |       |

|           |          |       |       | 0x27      | nor   |          |       |

|           |          |       |       | 0x2A      | st    | 2%       | 0%    |

Figure 3.7: MIPS Opcode Map and Frequency of Instructions

0x2B

sttu

1%

0%

# 3.3. Survey of Instruction Set Architectures Implementation Schemes

The path which is followed by instructions and data and controlled by signals generated by control unit called data path. Each type of instruction follows different path trough architecture because the operands on which instruction operates differ.

Data path is formed by state and combinational logic elements. These elements are combined in different organizations and different implantation schemes emerge.

Building architecture requires some sequential decompose and re-unite iterations. It is necessary to decompose in order to understand, and it is necessary to re-unit in order to build. There exists a contradiction, because it is necessary to decompose in order to reunite. This contradiction was used as a methodology and followed throughout the survey of implementation schemes. Big picture is given first. Then it is decomposed and fully understood.

#### 3.3.1. Single Cycle Implementation Scheme

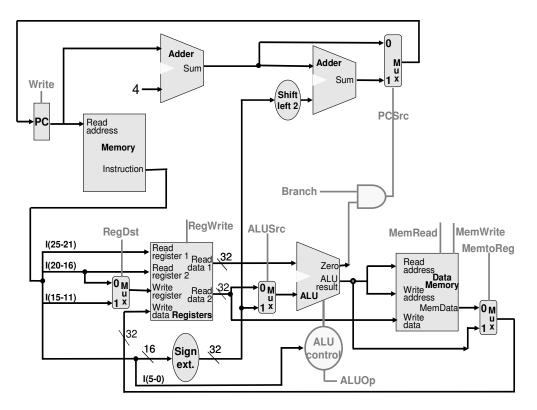

In this scheme (Figure 3.8) single instruction starts on clock edge and ends on the next clock edge. The clock rate is determined by the slowest instruction; in spite there exists faster instructions in ISA. Hence this scheme is impractical to implement but useful to understand. Each instruction irrespective of its instruction format is fetched from memory; the next PC is calculated by adding 4 byte offset to present PC and decoded according to its bit field based on Figure 3.1. The operation on registers is determined by the ALUOp control signal which depends on the Funct field of the instruction and determined in decode stage.

Figure 3.8: Single Cycle Implementation Scheme ©[COD98]

Multiplexers can be used to divide the architecture into smaller pieces. The presence of a multiplexer before an input element means that that element is used by as many different instruction types as the number of inputs of the multiplexer. The select signal, namely the instruction type determines the path of the data throughout the architecture for the present clock cycle. For instance, the multiplexer with control signal ALUSrc determines either ALU is used for address calculation for data memory load/store or arithmetic operation on register operands. In either case ALU can be used only by one instruction type in the same clock, hence some hardware duplications exist in the architecture for other calculations such as the adder for next program counter, despite the ALU can be used for this purpose. This is another fact which proves that this implementation scheme is impractical to implement and its

problems will be solved in multi cycle implementation scheme which will be described in section 3.3.2.

Similarly, the multiplexer with control signal MemtoReg determines which data will be written to the register bank either the result calculated by ALU or the data loaded from data memory.

The multiplexer with control signal RegDst differentiate R-type and Itype instructions because the destination register address field is different for these types. For R-type instructions, the destination address is specified in Rd field whereas in I-type instructions the destination address is specified in Rt field (Figure 3.1).

The multiplexer with control signal PCSrc determines the next PC. The next PC is PC+4 bytes for all instruction types except from conditional branch. For branch instructions (Branch control signal is asserted) if the condition is satisfied (e.g. for "branch on equal" instruction, when the operands are the same, their difference will be zero. Hence the ALU's zero output set to '1') the next PC is calculated according to Figure 3.5.

#### 3.3.2. Multi Cycle Implementation Scheme

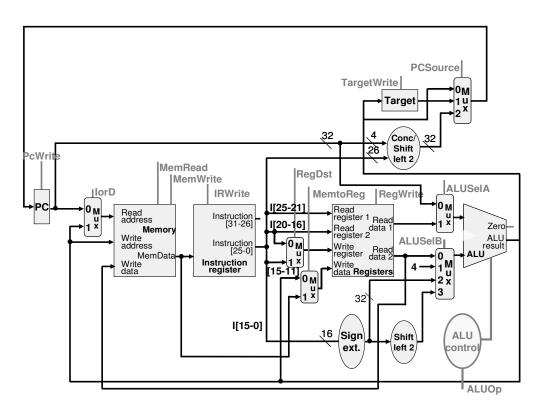

In this scheme (Figure 3.9) instructions are executed in multi clock cycles. Register Blocks are added between functional units to hold the temporal values for using on a later clock cycle. Clock rate is determined by the slowest functional unit and functional units can be used more than once per instruction (e.g. single ALU is used instead of an ALU and two adders Figure 3.8) as long as access to this unit occurs on different clock cycles. Single memory unit is used instead of separate instruction and data memories and multiplexer with control signal lorD determines data or instruction access.

Figure 3.9: Multi Cycle Implementation Scheme ©[COD98]

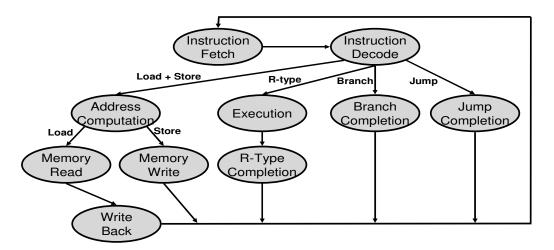

Jump instruction is also shown in the scheme. The multiplexer with control signal PCSource selects next program counter calculated based on Figure 3.6 when unconditional jump instruction was fetched from memory. A more complex control logic compared to single cycle implementation scheme is needed and the state flow diagram of control unit is given in Figure 3.10.

Figure 3.10: State Flow Diagram of Multi Cycle Scheme Control Unit

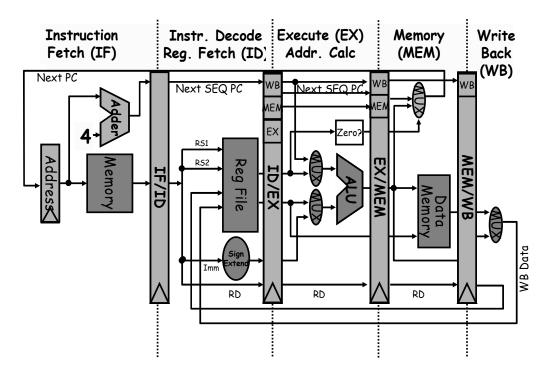

#### 3.3.3. Pipelined Implementation Scheme

In this scheme (Figure 3.11), there exists single clock cycle between subsequent instructions like single cycle implementation scheme.

Clock rate is as high as multi cycle implementation scheme and is determined by the slowest functional unit similar to multi cycle implementation scheme. There exist register blocks between functional units, which are responsible for storing the information for the next clock cycle.

The difference between multi cycle scheme and pipelined scheme is that the instruction does not wait for the previous instruction until the end of write back stage and directly fetched from instruction memory while the previous instruction is being decoded.

The same control signals which are valid for single and multi cycle schemes are also valid for pipelined scheme, but in contrast to multi cycle implementation scheme, special control unit implementation (flow diagram was given in Figure 3.10) is not necessary for generation of these control signals. Sequencing is inherently present in this scheme and control signals generated in decode stage go with the instruction throughout the pipeline and are wasted up until the last stage.

Figure 3.11: Pipelined Implementation Scheme ©[COD98]

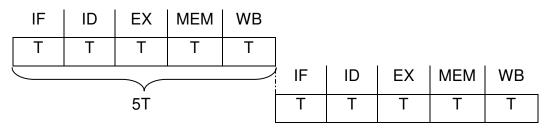

Pipelining does not improve or speed up the functional units in the architecture, instead increases the throughput by decreasing the time between instructions. There exist as much instructions as the number of stages in the pipeline simultaneously, e.g. while the fifth instruction is being fetched (IF) from memory, in the same time, first instruction is in write back (WB) stage following five clock cycles its IF stage (Figure 3.12).

|               | CLK1     | CLK2 | CLK3 | CLK4 | CLK5 |

|---------------|----------|------|------|------|------|

| Instruction 1 | IF       | ID   | EX   | MEM  | WB   |

| Instruction 2 | <u> </u> | IF   | ID   | EX   | MEM  |

| Instruction 3 |          |      | IF   | ID   | EX   |

| Instruction 4 |          |      |      | IF   | ID   |

| Instruction 5 |          |      |      |      | IF   |

Figure 3.12: Simultaneously Executing Instructions in Pipeline

#### 3.3.4. Quantitative Comparison of Implementation Schemes

Primary metric to compare performance of Architectures is execution time of a program as stated in section 3.1. Pipelined implementation scheme has the best features of other implementation schemes, low clock cycle per instruction like single cycle scheme which is optimally equal to 1 disregarding pipeline hazards described in section 3.4 and high clock rate like multi cycle implementation scheme; therefore it is expected to give the best performance. It will be a good practice to demonstrate the relative performances by giving a realistic example. MIPS instructions has the frequency of usage as stated in Figure 3.7 in gcc program and number of clock cycles as stated in Figure 3.10 which also summarized in Table 1.

CPI can be calculated by using this table adding the weighted sums of instructions in gcc program.

$CPI = 5 \times 0.23 + 4 \times 0.13 + 3 \times 0.19 + 3 \times 0.02 + 4 \times 0.43$ = 4.02

| Instruction Type | Frequency | Number of Clock |

|------------------|-----------|-----------------|

|                  |           | Cycles          |

| LOAD             | 23%       | 5               |

| STORE            | 13%       | 4               |

| BRANCH           | 19%       | 3               |

| JUMP             | 2%        | 3               |

| ALU              | 43%       | 4               |

Table 3.1: Calculation of CPI for Multi Cycle Implementation Scheme

The clock rate or clock cycle period is determined by the slowest stage in the pipeline. For second per instruction calculation, clock period shall be multiplied with CPI (equation given in section 3.1). Optimal speedup is obtained from pipelining by using balanced stages in pipeline. Say that each stage is balanced and takes T sec/clock cycle.

Figure 3.13: Single and Multi Cycle Instruction Sequence

For single cycle implementation scheme, single cycle clock period takes 5T seconds. For multi cycle implementation scheme, single cycle period takes T seconds similar to pipelined implementation scheme. Hence, the instruction times given in Table 3.2 were obtained. According to this table, it can be seen that, pipelined implementation is nearly 5 times faster than the other implementation schemes.

| Implementation | Seconds/Instruction (CPI x sec/clock) |

|----------------|---------------------------------------|

| Scheme         |                                       |

| Single Cycle   | 1 x 5T = 5T                           |

| Multi Cycle    | 4.02 x T = 4.02T                      |

| Pipelined      | 1 x T = T                             |

**Table 3.2: Instruction Time Calculation for Implementation Schemes**

## 3.4. Problems and Solutions in Pipelined Architectures

As stated in section 3.3.4, optimal performance and speedup can be obtained from pipelining by balancing the stages and full speed usage of the pipeline without stalls. In reality this can be not possible always. Even perfect balance between pipeline stages can not be adequate alone.

There may be existent restrictions;

- Dependencies between instructions,

- Some hardware restrictions to support pipelining,

- Branches can not be determined until Execute (EX) stage and following instructions can be fetched uselessly.

Detailed explanation how these cases are handled given in the following sections.

## 3.4.1. Structural Hazards

Structural hazards emerged because the underlying hardware does not support special instruction combinations which are simultaneously present in the pipeline. For example, the instructions 1 and 4 presented in Figure 3.12 access the memory in the same clock cycle, CLK4. If the instruction memory and the data memory are not separated physically, this architecture can not support this special combination. In clock cycle CLK5, both Instruction Decode (ID) and Write Back (WB) stages access the register bank, but in this case the hardware clash is avoided by using forwarding mechanism which will be described in the section 3.4.3.

#### 3.4.2. Brach Hazards

Branch hazards emerged because three instructions, following the branch instruction, are already in the pipeline in any case until branch condition is evaluated or unconditional jump address determined (according to Figure 3.11). In case of branches are taken, these fetched instructions must be discarded and the goal of using pipeline in its full speed one instruction per clock cycle can not be achieved. Three clock cycles are wasted effectively in case of taken branch; assuming branch is not taken always.

In this thesis, the decision making and address calculation mechanism moved to ID stage to reduce the wasted time to one clock cycle. The assumption which is called delayed branch mechanism, "braches are always not taken" is followed. In this case, the following instruction is always fetched. In case of taken branch, one slot is left as discarded and useless. If the decision is left to compiler as in case in high level programming, compilers usually fill this slot with useful instructions which are independent from the branch condition. If useful instruction can not be found, this slot is filled with well known No Operation (NOP) instruction which does not change the internal state of microprocessor. A NOP instruction is added manually after every branch in this thesis, because programming is done in assembly and compiler support is not present. There exists no special implementation in this thesis which detects this hazard and flushes the fetched instruction.

One delay slot can be easily filled with NOP or with useful instruction, but as the pipeline gets bigger, filling slots with useful instructions gets also harder. There exists other mechanism proposed in the literature to solve this problem. Dynamic prediction mechanism with additional hardware is one of them, which depends on the past statistics collected for that branch point. The decision is made based on this statistics which is changing in time with conditions.

## 3.4.3. Data Hazards

Data hazards emerged because an instruction which depends on the previous instruction is in the pipeline and previous instruction did not finish its work, for example does not write back the calculated result to destination register. In this type of hazard, the solution is not left to compilers entirely like the branch hazard described in 3.4.2 and tried be solved with hardware if possible. The hazard will appear when the destination register of the previous instruction in either EX, MEM or WB stage is the same as the one of the source registers of the current instruction which is in the ID stage. In Figure 26, data hazard is resolved by forwarding data from EX, MEM and WB stages of the first instruction to ID stages of following instructions which has a without waiting to complete first instruction to WB its destination register R1.

Figure 3.14: Data Hazard Solution by Forwarding

The data hazard must be resolved in ID stage before register bank access and branch decision. A NOP instruction is inserted into the instruction sequence, if hazard can not be solved and time is gained for resolution by using forwarding in the next clock cycles. In Figure 3.15, hazard can not be solved by just using forwarding, because the result for destination register R2 will be not available until memory access. Therefore, pipeline is stalled for one clock cycle and data hazard is resolved in the next clock cycle by forwarding data from Data Memory (MEM) stage of previous instruction to ID stage of the current instruction.

|                       | CLK1     | CLK2  | CLK3 | CLK4        | CLK5 | CLK6 |

|-----------------------|----------|-------|------|-------------|------|------|

| lw <b>R2</b> ,100(R1) | IF       | ID    | EX   | MEM<br>●    | WB   |      |

| and R4, <b>R2</b> ,R5 | <u> </u> | STALL | IF   | <b>▼</b> ID | EX   | MEM  |

| or R8, <b>R2</b> ,R6  |          |       |      | IF          | ID   | EX   |

Figure 3.15: Data Hazard Solution by Stalling and Forwarding

Some extra precautions must be taken into account while using forwarding mechanism. In Figure 3.16, the result obtained in clock cycle CLK4 from the addition of second instruction is forwarded from EX

stage instead of the result obtained in clock cycle CLK3 from MEM stage, because it is more recent.

|                               | CLK1 | CLK2 | CLK3 | CLK4   | CLK5 |

|-------------------------------|------|------|------|--------|------|

| add <b>R1</b> ,R1,R2          | IF   | ID   | ● EX | MEM    | WB   |

| add <b>R1</b> , <b>R1</b> ,R3 |      | IF   | ▼ ID | ● EX   | MEM  |

| add <b>R1,R1</b> ,R4          |      |      | IF   | ♥ ID ♥ | EX   |

Figure 3.16: Forwarding of the Most Recent Data

## 3.4.4. Exception Hazard

Hardware shall prevent completion of instructions which are following the instruction which cause exception and let all prior instructions to complete. Internal register blocks shall be flushed to prevent them to effect Register Bank and Data Memory. Program Counter shall be equated to special address like Branch or Jump instruction case. This address is generally called as interrupt or exception vector.

# **CHAPTER 4**

# IMPLEMENTATION OF MIPS PIPELINED ARCHITECTURE

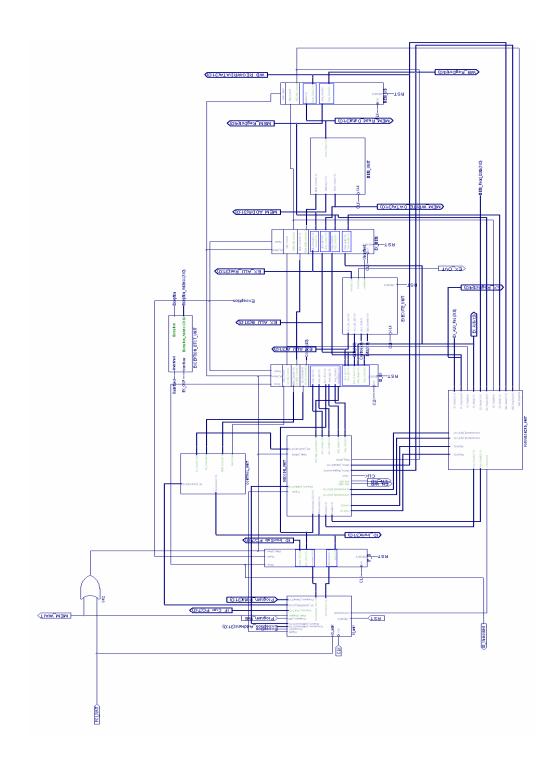

This chapter describes the internal structure of the processor and the auxiliary structures to monitor and manipulate the internal registers of the processor. Internal structures of the processor are constituted by combining the following primary units and their subunits. (Figure 4.1: Internal Structure of the Pipelined Processor)

- Instruction Fetch Unit (IF\_Unit)

- Instruction Memory (256x32bit block memory)

- Instruction Decode Unit (ID\_Unit)

- Register Bank (dual port 32x32bit block memory)

- Forwarding and Hazard detection Unit (FORWD\_HZRD Unit)

- Control Unit (CONTROL\_Unit)

- Execute Unit (EXECUTE\_Unit)

- Data Memory Unit (256x32bit block memory)

- Exception Detection Unit (EXCEPTION\_DTCT\_UNIT)

- Four register blocks responsible for storing information between clock cycles and located between Units;

- Instruction Fetch Instruction Decode (IF\_ID Unit)

- Instruction Decode Execute (ID\_EX Unit)

- Execute Data Memory (EX\_MEM Unit)

- Data Memory Instruction Decode (MEM\_WB Unit)

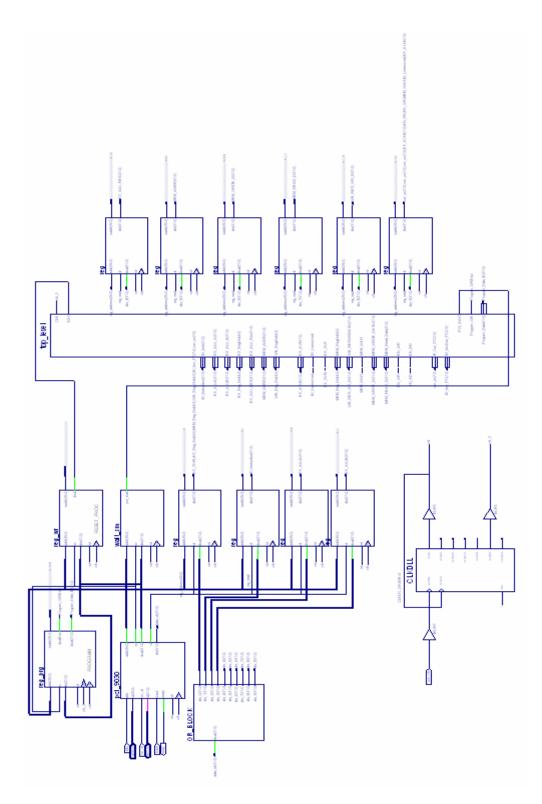

Auxiliary structures of the processor are constituted by combining the following units. Units and their interconnections are presented in Figure 4.2.

- Clock Delay Locked Loop to eliminate the skew between clock input pad and the internal clock input pins (CLKDLL Unit)

- Interface between the processor and the PCI Bridge (pci\_9030 Unit)

- External reset of the processor (reg\_wr Unit)

- External programming of the Instruction Memory (reg\_prg Unit)

- External single step execution of processor (wait\_sm Unit)

- External reading of internal state of register blocks (reg Units)

- Processor itself (top\_level Unit)

Figure 4.1: Internal Structure of the Pipelined Processor

Figure 4.2: External Structure of the Pipelined Processor

#### 4.1. Internal Structure of the Processor

In this section the primary building blocks are described in detail by stating their functions and input/output signals (in figures, inputs are placed on the left and outputs are placed on the right). General signals which are common for majority of building blocks are described here. Remaining signals are described in related building block sections. Every signal is described once that means the same input signal of various blocks is also an output signal of single block; therefore there will be a cross reference (links can be followed by CTRL + Click in this document) input signal definition section of each block to output signal definition section of source block of the signal in which the same signal is described in detail to avoid redefinition. During definition of signal levels, "set" means logic level 1 and reset means logic level 0.

<u>CLK (1 bit) and RESET (1 bit):</u> Internal clock (20 MHz) and internal reset signals. These signals are active high signals.

<u>Register Dest (5 bit)</u>: This signal is transferred across all pipelines for instructions which will write to Register Bank in WB stage.

#### 4.1.1. Instruction Fetch Unit

The design of the Instruction Fetch Unit is realized by using HDL Design entry method. Instruction Fetch Unit includes the subunit Instruction Memory (256x32bit block memory) from which instructions are fetched in every clock cycle except when an unresolved (load/store) hazard exists in the pipeline which ends up with pipeline stall. The hardware flow diagram of this building block is given in APPENDIX C, Figure C.1: Instruction Fetch Unit Flow Diagram.

## 4.1.1.1. Input/Output Signals of Instruction Fetch Unit

The connections of Instruction Fetch Unit with other units can be seen in Figure 4.1: Internal Structure of the Pipelined Processor. All Input/Output signals can be seen in Figure 4.3: Input/Output Signals of Instruction Fetch Unit.

Output signals are as the following;

<u>Current PC (8 bit):</u> Signal goes to auxiliary structures to monitor the present state of the Program Counter.

<u>Incremented PC (32 bit)</u>: Signal goes to Instruction Decode Unit and forwarded until WB stage for jal instruction, because this instruction writes the return address into Register Bank address 31 for later usage in return from subroutine (by using jr instruction). This signal is also used in instruction decode stage to calculate the branch and jump address.

<u>Instruction (32 bit)</u>: Signal which is fetched from instruction memory goes to Instruction Decode and Control Units. Instruction is parsed into fields according to Figure 3.1 in Instruction Decode unit and control signals are generated in Control Unit. These signals are passed to internal register blocks for further evaluation of the parsed fields in the following clock cycles after decode stage.

<u>Wait Stages (1 bit)</u>: Signal is OR'ed with pci\_wait signal and goes to all internal registers between building blocks. If this signal is set that means, memory access (instruction memory, data memory and Register Bank access requires one clock cycle) is taking place and all processor stages are stopped during this signal is set which corresponds to one clock cycle period. Program Counter is also not updated during this signal is set.

Figure 4.3: Input/Output Signals of Instruction Fetch Unit

Input Signals are as the following;

Exception (1 bit): Exception Detection Unit output signal.

Exception Address (32 bit): Exception Detection Unit output signal.

Branch Addr (32 bit): Instruction Decode Unit output signal.

Equal (1 bit): Instruction Decode Unit output signal.

IF Control (3 bit): Control Unit output signal.

<u>Program Data (31 bit) and Program WE (1 bit)</u>: Signals are fed from external sources and used when in external programming mode. These signals are useless in normal operating mode of the processor.

<u>Pci wait (1 bit)</u>: Signal comes from external source and used as single step execution trigger. Program Counter is updated during the clock rising edges if and only if this signal is not set.

<u>Unresolved (1 bit):</u> Forwarding and Hazard detection Unit output signal.

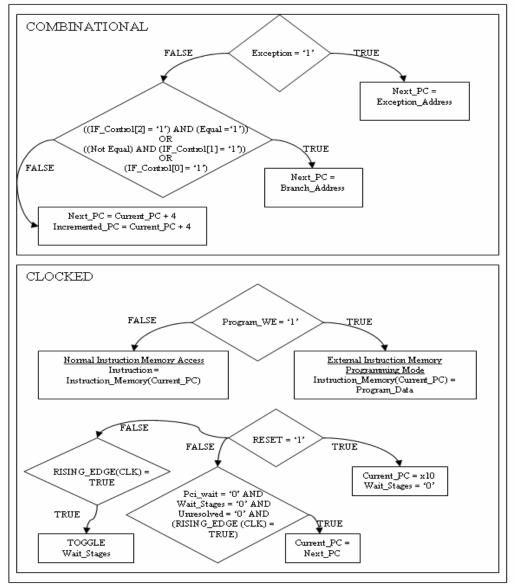

## 4.1.1.2. Function of Instruction Fetch Unit

The primary function of Instruction Fetch Unit is to fetch instructions from Instruction memory and send it to Control and Decode Units for processing. If Wait Stages or Pci wait or Unresolved signal is set, current program counter retains its value, hence the same instruction is fetched from memory on the next clock cycle. If a branch or jump instruction is in decode stage inspecting the IF CONTROL signal, next program counter is determined according to evaluation of Equal and Branch Address signals. During instruction memory access. Wait Stages signal is set and processor is stopped for one clock cycle. On the next clock cycle, Wait\_Stages signal will be in reset state and processor is allowed to run, hence during operation of processor Wait Stages signal toggles. This halves the processor's effective clock speed from 20 MHz to 10 MHz. If RESET signal is set, Program Counter is set to byte address 16 after overflow exception vector. In case of an exception PC is set to proper exception vector. If Program WE signal is set, Instruction memory enters in external programming mode and on every clock cycle Program Data signal is written to Instruction Memory sequentially.

#### 4.1.2. Instruction Decode Unit

The design of the Instruction Decode Unit is realized by using HDL Design entry method. Instruction Decode unit includes the subunit Register Bank (dual port 32x32bit block memory) from which operands on which operations take place are fetched and to which operation results or loaded data from data memory are stored in every clock cycle. The hardware flow diagram of this building block is given in APPENDIX C, Figure C.2: Instruction Decode Unit Flow Diagram.

## 4.1.2.1. Input/Output Signals of Instruction Decode Unit

The connections of Instruction Decode Unit with other units can be seen in Figure 4.1: Internal Structure of the Pipelined Processor. All Input/Output signals can be seen in Figure 4.4: Input/Output Signals of Instruction Decode Unit.

Output signals are as the following;

<u>ALU PORTA (32 bit)</u>: Signal goes to ALU port A for evaluation according to instruction present in EX stage. This signal can come from the other stages by forwarding or represents shift amount for sll and srl instructions.

<u>ALU PORTB (32 bit)</u>: Signal goes to ALU port B for evaluation according to instruction present in EX stage. This signal can come from the other stages by forwarding or represents Incremented Program Counter for jal instruction or zero or sign extended immediate field according to control signal. For memory store operation sw, this signal represents the data which will be stored to data memory and directly forwarded to MEM stage.

<u>Avlb Stage (2 bit)</u>: Signal goes to Forwarding and Hazard detection Unit and is used to determine if unresolved data hazard which ends up with pipeline stall is present. If the result of the instruction in EX stage will be available in MEM stage (lw instruction's Avlb\_Stage is equal to MEM) and the destination of the instruction is the same as the one of the source operands of the instruction present in ID stage then pipeline is stalled for one clock cycle and data hazard is resolved using forwarding mechanism. <u>Branch Addr (32 bit):</u> Signal goes to Instruction Fetch Unit and used to determine the value of next program counter if a conditional or unconditional branch instruction is present in instruction decode stage. <u>Imm Sign Extended (32 bit):</u> Signal goes to Execute Unit and used to calculate the destination register address for sw instruction. The base address is carried to Execute Unit via Port A like lw instruction, but the offset can not be carried via Port B. Port B represents the data which will be stored in data memory for this instruction hence this signal was needed to be transferred.

<u>Register Dest (5 bit)</u>: General signal which represents the destination register which will be used in WB stage.

rs (5 bit), rt (5 bit), Unresolved A (32 bit) and Unresolved B (32 bit): Signals go to Forwarding and Hazard detection Unit. Rs and Rt represent the source addresses of operand registers and are compared with instruction's destination register address in either EX, MEM or WB stages. Forwarding Unit will determine the data hazard is present. If no hazard is detected, the Unresolved\_A and Unresolved\_B which represent the values in register Bank addresses Rs and Rt will be forwarded to ALU ports.

<u>EN RD (1 bit) and EN WR (1 bit):</u> Signals go to auxiliary structures to monitor the present state of the read and write enable pins of Register Bank They were used during development and currently not used.

<u>Equal (1 bit)</u>: Signal goes to Instruction Fetch Unit and if set that means operands on which conditional branch instruction was applied are equal, if not set, inequality condition is true.

Figure 4.4: Input/Output Signals of Instruction Decode Unit

Input signals are as the following;

<u>DataA (32 bit) and DataB (32 bit):</u> Forwarding and Hazard detection Unit output signals. (ResvDataA and ResvDataB)

ID Control (11 bit): Control Unit output signal.

Incremented PC (32 bit): Instruction Fetch Unit output signal.

Instruction (32 bit): Instruction Fetch Unit output signal.

<u>Write Data (32 bit), Write Register (5 bit) and Reg Write (1 bit):</u> These signals are WB stage signals and Write\_Register determines the address of the Register Bank in which the Write\_Data will be written if Reg\_Write signal is set and Write\_Register (destination address) is not equal to 0, because the register address 0 is named as \$zero register and it is not allowed writing to this address.

<u>Wait MEM (1 bit)</u>: Signal is generated by OR'ing the output signal Wait\_Stages of Instruction Fetch Unit and the external one step execute

trigger signal Pci\_wait. If this signal is set, the EN\_WR signal is set and if this signal is reset EN\_RD signal is set, hence the Register Bank is written first and after that it is read.

## 4.1.2.2. Function of Instruction Decode Unit

The functions of Instruction Decode Unit are;

- Preparing the Register Bank addresses and register contents to determine final resolved values on which the instruction in ID stage will operate in following stages,

- Access the Register Bank for writing and reading,

- Make the evaluation of conditional branch and determine the final branch and jump address and fed it to Instruction Fetch Unit.

## 4.1.3. Forwarding and Hazard Detection Unit

The design of the Forwarding and Hazard Detection Unit is realized by using HDL Design entry method. The hardware flow diagram of this building block is given in APPENDIX C, Figure C.3: Forwarding and Hazard Detection Unit Flow Diagram.

## 4.1.3.1. Input/Output Signals of Forwarding and Hazard Detection Unit

The connections of Forwarding and Hazard Detection Unit with other units can be seen in Figure 4.1: Internal Structure of the Pipelined Processor. All Input/Output signals can be seen in Figure 4.5: Input/Output Signals of Forwarding and Hazard Detection Unit. Output signals are as the following; <u>ResvDataA (32 bit) and ResvDataB (32 bit)</u>: Signals go to the DataA and DataB inputs of Instruction Decode Unit and then forwarded to ALU ports taking into account the control signals. The final values of these signals are determined by using the input signals and VHDL code is given below;

#### Table 4.1: Forwarding Mechanism for Register Bank Primary Port

ResvDataA <= ID\_Value when ((ID\_RegWrite = '1') and (ID\_RegDst = Rs) and (ID\_RegDst /= "00000")) else EX\_Value when ((EX\_RegWrite = '1') and (EX\_RegDst = Rs) and (EX\_RegDst /= "00000")) else WB\_Value when ((WB\_RegWrite = '1') and (WB\_RegDst = Rs) and (WB\_RegDst /= "00000")) else Unresolved\_A;

#### Table 4.2: Forwarding Mechanism for Register Bank Secondary Port