## ELECTRICAL TRANSPORT IN METAL-OXIDE-SEMICONDUCTOR CAPACITORS

# A THESIS SUBMITTED TO THE GRADUATE SCHOOL OF NATURAL AND APPLIED SCIENCES OF THE MIDDLE EAST TECHNICAL UNIVERSITY

BY

## MUSTAFA ARIKAN

# IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE IN PHYSICS

SEPTEMBER 2004

Approval of the Graduate School of Natural and Applied Sciences

Prof. Dr. Canan Özgen Director

I certify that this thesis satisfies all the requirements as a thesis for the degree of Master of Science.

Prof. Dr. Sinan Bilikmen Head of Department

This is to certify that we have read this thesis and that in our opinion it is fully adequate, in scope and quality, as a thesis for the degree of Master of Science.

Prof. Dr. Raşit Turan Supervisor

**Examining Committee Members**

| Prof. Dr. Bülent Akınoğlu      | (METU, PHYS) |

|--------------------------------|--------------|

| Prof. Dr. Rașit TURAN          | (METU, PHYS) |

| Assoc. Prof. Dr. Mehmet PARLAK | (METU, PHYS) |

| Dr. Sadi TURGUT                | (METU, PHYS) |

| Dr. Orhan KARABULUT            | (PAU, PHYS)  |

"I hereby declare that all information in this document has been obtained and presented in accordance with academic rules and ethical conduct. I also declare that, as required by these rules and conduct, I have fully cited and referenced all material and results that are not original to this work."

Name- surname: Mustafa Arıkan

Signature :

## ABSTRACT

## ELECTRICAL TRANSPORT IN METAL-OXIDE-SEMICONDUCTOR CAPACITORS

Arıkan, Mustafa M. Sc., Department of Physics Supervisor: Prof. Dr. Raşit Turan

August 2004, 75 pages

The current transport mechanisms in metal-oxide-semiconductor (MOS) capacitors have been studied. The devices used in this study have characterized by current-voltage analyses. Physical parameter extractions and computer generated fit methods have been applied to experimental data. Two devices have been investigated: A relatively thick oxide (125 nm) and an ultra-thin oxide (3 nm) MOS structures. The voltage and temperature dependence of these devices have been explained by using present current transport models.

Keywords: Metal-Oxide-Semiconductor, ultra-thin oxide, Schottky emission, Fowler-Nordheim, Poole-Frenkel, trap.

ÖZ

## METAL-OKSİT-YARI İLETKEN KONDANSATÖRLERDE ELEKTRİKSEL TAŞIMA

Arıkan, Mustafa Yüksek Lisans, Fizik Bölümü Tez Yöneticisi: Prof. Dr. Raşit Turan

Ağustos 2004, 75 sayfa

Metal-Oksit-Yarı iletken (MOS) kondansatörlerdeki elektriksel taşıma mekanizmaları incelendi. Bu çalışmada kullanılan aygıtlar akım-gerilim yöntemleri kullanılarak karakterize edildi. Fiziksel katsayı çıkarımı ve bilgisayarla yaratılmış verilerin uyumu yöntemleri deneysel verilere uygulandı. İki aygıt incelendi: Göreceli kalın oksit (125 nm) ve aşırı ince oksit (3 nm) MOS yapıları. Bu aygıtların gerilim ve sıcaklık bağımlılıkları günümüzdeki akım-gerilim modelleri kullanılarak açıklandı.

Anahtar kelimeler: Metal-Oksit-Yarı iletken, aşırı ince oksit, Schottky salımı, Fowler-Nordheim, Poole-Frenkel, kapan..

v

## ACKNOWLEDGMENTS

I would like to express my deepest gratitude to my family for their "all-case" support and love. Nothing good would happen in my life without their support.

Bülent Aslan, my "co-supervisor", is greatly appreciated for his helps and friendship.

I would also like to thank Sadi Turgut and my colleagues at METU and my friends for the nice times we had during all my education.

The most special thanks go to my supervisor Raşit Turan for introducing me to microelectronics field. I have learned from him so much, not only about research but also about life.

## TABLE OF CONTENTS

| ABSTRACT          | iv  |

|-------------------|-----|

| ÖZ                | v   |

| ACKNOWLEDGMENTS   | vi  |

| TABLE OF CONTENTS | vii |

| LIST OF FIGURES   | ix  |

| LIST OF TABLES    | xi  |

## CHAPTER

| 1                                                  | METAL-OXIDE-SEMICONDUCTOR STRUCTURE AND |                                           |                                                |    |

|----------------------------------------------------|-----------------------------------------|-------------------------------------------|------------------------------------------------|----|

|                                                    | CON                                     | DUCTI                                     | ON MECHANISMS                                  | 1  |

|                                                    | 1.1                                     | Introdu                                   | uction                                         | 1  |

|                                                    | 1.2                                     | MOS                                       | Capacitor                                      | 2  |

|                                                    |                                         | 1.2.1                                     | Ideal MOS Capacitor                            | 2  |

|                                                    |                                         | 1.2.2                                     | Biasing the MOS Capacitor                      | 3  |

|                                                    |                                         |                                           | 1.2.2.1 Accumulation                           | 4  |

|                                                    |                                         |                                           | 1.2.2.2 Depletion                              | 4  |

|                                                    |                                         |                                           | 1.2.2.3 Inversion                              | 4  |

|                                                    |                                         | 1.2.3                                     | Surface Space Charge Region                    | 5  |

|                                                    |                                         | 1.2.4                                     | Work-function Difference and Flat-band Voltage | 6  |

|                                                    |                                         | 1.2.5                                     | Ideal MOS Capacitor Analysis                   | 7  |

|                                                    | 1.3                                     | MOS                                       | Capacitor and Oxide Charges                    | 9  |

| 1.4 Current Transport Mechanisms in MOS Capacitors |                                         | nt Transport Mechanisms in MOS Capacitors | 11                                             |    |

|                                                    |                                         | 1.4.1                                     | Fowler-Nordheim Tunneling                      | 11 |

|                                                    |                                         | 1.4.2                                     | Direct Tuneling                                | 12 |

|                                                    |                                         | 1.4.3                                     | Band-to-band Tunneling                         | 15 |

|                                                    |                                         | 1.4.4                                     | Trap Assisted Tunneling                        | 16 |

|       |               | 1.4.5                 | Poole-Frenkel Emission                          | 17 |

|-------|---------------|-----------------------|-------------------------------------------------|----|

|       |               | 1.4.6                 | Space-charge Limited Current                    |    |

|       |               | 1.4.7                 | Hopping Conduction                              | 19 |

|       |               | 1.4.8                 | Schottky-like Emission (Modified Poole-Frenkel) | 19 |

|       |               | 1.4.9                 | Surface-state Tunneling                         |    |

|       |               | 1.4.10                | Diffusion Current                               |    |

|       |               | 1.4.11                | Recombination-generation Current                | 23 |

| 2     | EXPE          | ERIMEN                | VTAL PROCEDURES                                 | 24 |

|       | 2.1.          | Al-SiO                | 2-Si MOS                                        | 24 |

|       |               | 2.1.1                 | Wafer Cleaning                                  | 25 |

|       |               | 2.1.2                 | Oxidation                                       |    |

|       | 2.2.          | PolySi-               | SiO <sub>2</sub> -Si MOS                        | 27 |

|       | 2.3.          | Electric              | cal Characterization Setup                      |    |

| 3     | ELEC          | CTRICA                | L TRANSPORT IN THICK SIO <sub>2</sub> FILM      |    |

|       | 3.1. <i>A</i> | Al-SiO <sub>2</sub> - | Si Capacitor                                    |    |

|       | 3.2. I        | Electrica             | l Characteristics                               |    |

|       |               | 3.2.1.                | C-V and G-V Curves                              | 31 |

|       |               | 3.2.2.                | I-V Curves                                      |    |

|       | 3.3. I        | Possible              | Current Transport Mechanisms                    |    |

|       |               | 3.3.1                 | Thermally Activated Current                     | 35 |

|       |               | 3.3.2                 | Field Activated Current                         | 40 |

|       | 3.4. <b>C</b> | Conclusi              | on                                              | 43 |

| 4     | ELEC          | CTRICA                | L RTANSPORT IN ULTRA-THIN SIO <sub>2</sub> FILM | 46 |

|       | 4.1.          | Introdu               | ction                                           | 45 |

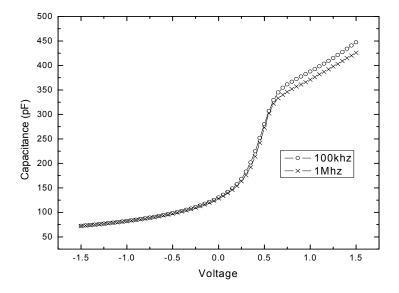

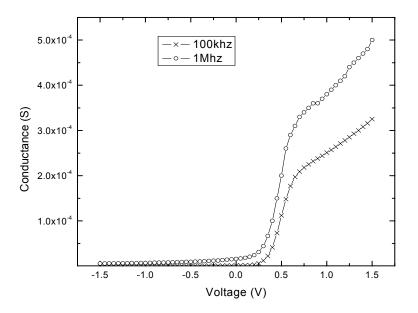

|       | 4.2.          | C-V and               | d G-V Characteristics                           | 47 |

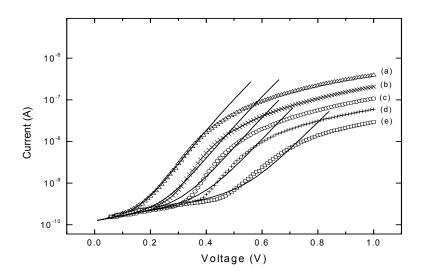

|       | 4.3.          | I-V Ch                | aracteristics                                   | 48 |

|       | 4.4.          | Possible              | e Current Transport Mechanisms                  | 49 |

|       | 4.5           | Descrip               | tion of I-V Curves                              | 53 |

|       | 4.6           | Conclus               | sion                                            | 64 |

| DEEED | ENCES         |                       |                                                 | 60 |

| KEFEK | LINCES        | •••••                 |                                                 |    |

## LIST OF FIGURES

## FIGURE

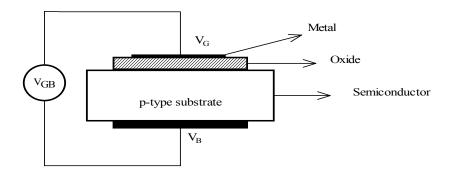

| 1.1 | Metal-Oxide-Semiconductor capacitor                                              | 2   |

|-----|----------------------------------------------------------------------------------|-----|

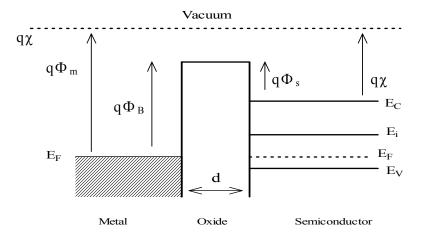

| 1.2 | Ideal Metal-Oxide-Semiconductor band diagram                                     | 3   |

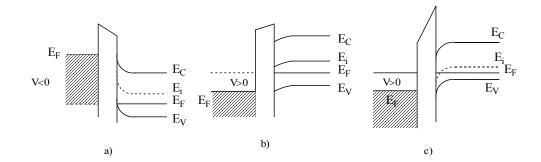

| 1.3 | Biasing Metal-Oxide-Semiconductor capacitor with p-type substrate:               |     |

|     | (a) accumulation; (b) depletion; (c) inversion                                   | 4   |

| 1.4 | Energy-band diagram at the surface of a p-type semiconductor                     | 5   |

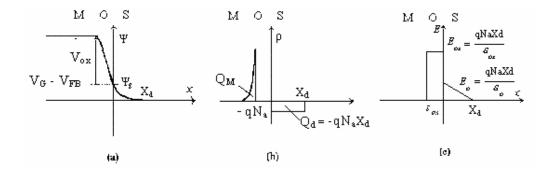

| 1.5 | (a) Potential; (b) charge; (c) electric field diagram at the surface of a p-type |     |

|     | semiconductor.                                                                   | 7   |

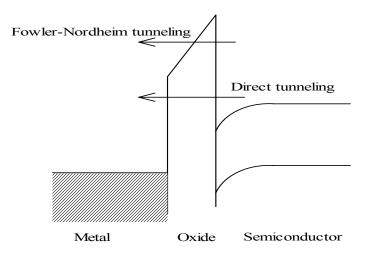

| 1.6 | Fowler-Nordheim and direct tunneling mechanisms                                  | .13 |

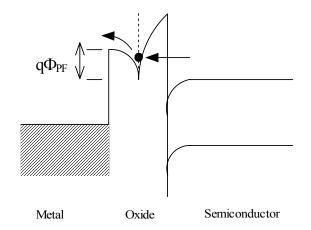

| 1.7 | Poole-Frenkel emission                                                           | .18 |

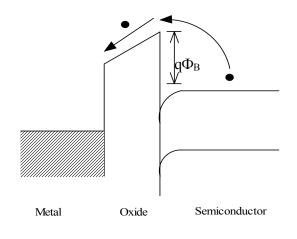

| 1.8 | Schottky emission                                                                | .19 |

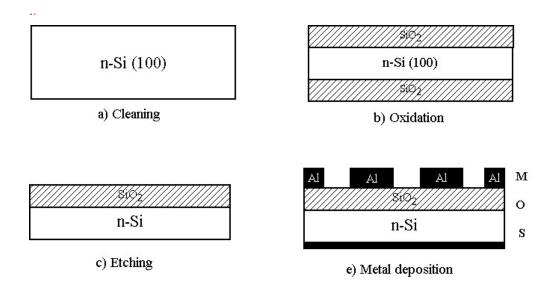

| 2.1 | Fabrication of MOS capacitor. a) Wafer cleaning; b) dry oxidation, c)            |     |

|     | etching, d) metal formation                                                      | .25 |

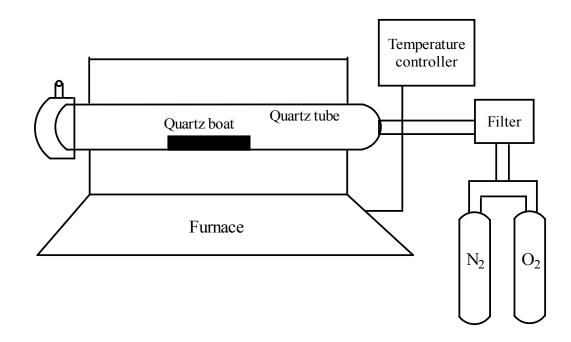

| 2.2 | Furnace system for oxidation                                                     | .27 |

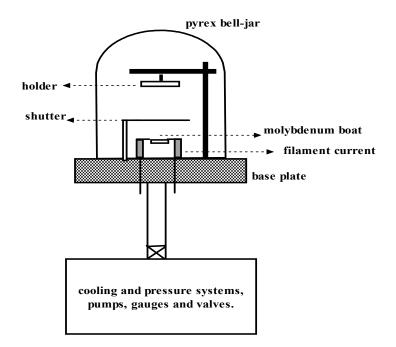

| 2.3 | Metal deposition system                                                          | .28 |

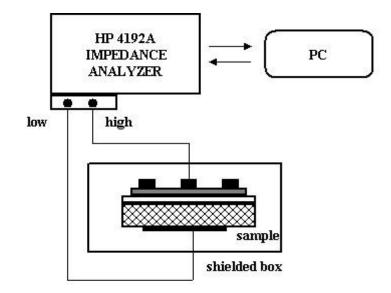

| 2.4 | C-V measurement system                                                           | .29 |

| 2.5 | Temperature dependent I-V measurement system                                     | .29 |

| 3.1 | Band structure of Al-SiO <sub>2</sub> -Si                                        | .30 |

| 3.2 | Quasi-Static (QS) capacitance-voltage curve                                      | .31 |

| 3.3 | High-frequency capacitance at 1 MHz and 100 kHz.                                 | .31 |

| 3.4 | Conductance vs. voltage curves at (a) 1 MHz and (b) 100 kHz                      | .32 |

| 3.5 | Current-Voltage graphics at different temperatures                               | .33 |

| 3.6 | Arrhenius plot for accumulation                                                  | .34 |

| 3.7 | Arrhenius plot for inversion                                                     | .34 |

| 3.8 | Current-Voltage characteristics at 270 K                                         | .35 |

| 3.9  | Poole-Frenkel plot for inversion regime at 270 K                                               | 36 |

|------|------------------------------------------------------------------------------------------------|----|

| 3.10 | Inversion regime Poole-Frenkel graphics at various temperatures                                | 37 |

| 3.11 | Poole-Frenkel plot for accumulation at 270 K                                                   | 38 |

| 3.12 | Accumulation regime Poole-Frenkel graphics at various temperatures                             | 39 |

| 3.13 | Fleischer-Lai's trap assisted tunneling model plots for accumulation at various temperatures   | 41 |

| 3.14 | -                                                                                              |    |

| 3.15 | Fleischer-Lai's trap assisted tunneling model plots for inversion at various temperatures      |    |

| 3.16 | Chang's trap assisted tunneling model plots for inversion at various temperatures              | 43 |

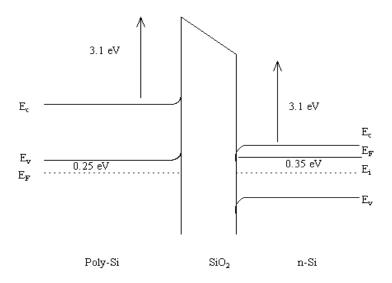

| 4.1  | Band structure of Poly-Si/SiO <sub>2</sub> /n-Si MOS capacitor                                 | 46 |

| 4.2  | High-frequency capacitance at 1 MHz and 100 kHz                                                | 47 |

| 4.3  | The conductance curves at 1MHz and 100 kHz                                                     | 47 |

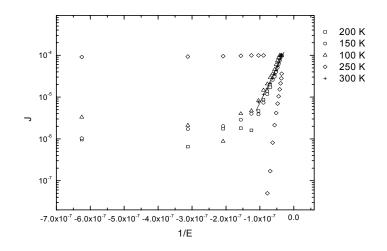

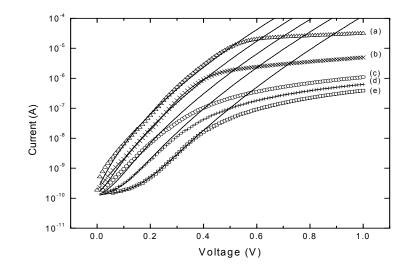

| 4.4  | Current-Voltage graphics at different temperatures                                             | 49 |

| 4.5  | Arrhenius plot at different gate voltages                                                      | 50 |

| 4.6  | (a) Experimental data at 30 K; (b) experimental data at 300 K; (c)                             |    |

|      | theoretical tunneling curve; (d) theoretical Schottky curve                                    | 54 |

| 4.7  | Experimental data at (a) 300 K; (b) 270 K; (c) 210 K; and computer                             |    |

|      | generated fits (d) 300 K; (e) 270 K; (f) 210 K                                                 | 55 |

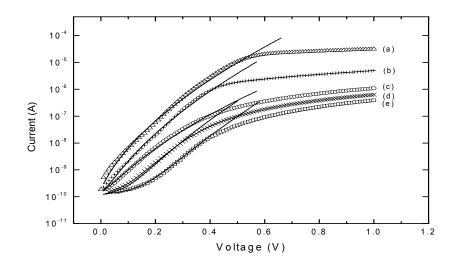

| 4.8  | Fits at (a) 300 K; (b) 270 K; (c) 210 K; (d) 180 K; (e) 150 K with                             |    |

|      | parameters of set1                                                                             | 57 |

| 4.9  | Fits at (a) 150 K; (b) 120 K; (c) 90 K; (d) 60 K; (e) 30 K with parameters of set1             | 57 |

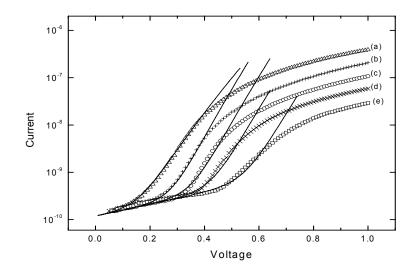

| 4.10 | Fit plots at (a) 300 K; (b) 270 K; (c) 210 K; (d) 180 K; (e) 150 K with parameters of set2     | 60 |

| 4.11 | Fits at (a) 150 K; (b) 120 K; (c) 90 K; (d) 60 K; (e) 30 K with parameters of set2             | 61 |

| 4.12 |                                                                                                |    |

| 4.13 |                                                                                                |    |

| 4.14 | The second type Arrhenius plots at (a) 1 v; (b) $0.6$ v; (c) $0.5$ v; (d) $0.4$ v; (e) $0.2$ v |    |

|      |                                                                                                |    |

## LIST OF TABLES

## TABLE

| 4.1 | The passive fit parameters for Set-1 | 56 |

|-----|--------------------------------------|----|

| 4.2 | The active fit parameters for Set-1  | 58 |

| 4.3 | The active fit parameters for Set-2  | 60 |

| 4.4 | The passive fit parameters for Set-2 | 60 |

| 4.5 | The active fit parameters for Set-2  | 61 |

| 4.6 | The passive fit parameters for Set-2 | 62 |

## **CHAPTER 1**

## METAL-OXIDE-SEMICONDUCTOR STRUCTURE AND CONDUCTION MECHANISMS

#### **1.1 Introduction**

In this introduction part of the thesis, mainly three books on semiconductor devices will be followed [1-4]. The information which is given as a summary of those books here can be found in those references and in many other books on semiconductor devices in a more detailed form.

There are a number of fundamental structures in today's microelectronics such as p-n junctions, metal-semiconductor contacts, MOS capacitors, MOSFETs, BJTs. Among them, the metal-oxide-semiconductor capacitors or MOS-Cs are very important because that the MOS capacitor is central to understanding the operation of MOSFETs since it uses an MOS capacitor structure as its control, or gate. Control of the electrical properties of the MOS system has been one of the major factors that have led to stable and high performance silicon integrated circuits. The MOS capacitors are also the most useful devices in semiconductor surface research. A MOS-C is also used as a basic device in many applications such as EEPROMs, DRAMs, optical sensors, solar cells etc. The simplicity of fabrication are among the main advantages of these structures.

The MOS structure was first proposed as a varactor in 1959 and its characteristics were then analyzed in 1961-62. The MOS diode was first employed in the study of a thermally oxidized silicon surface in 1962-63 [1, 2, and references therein].

### **1.2 MOS Capacitor**

The MOS capacitor consists of a Metal-Oxide-Semiconductor structure as illustrated by Figure 1.1. Shown is the semiconductor substrate with a thin insulating layer and a top metal contact, the gate. A second metal layer forms an ohmic contact to the back of the semiconductor, also referred to as the bulk. The structure shown has a p-type substrate. We will refer to this as an n-type MOS capacitor since the inversion layer contains electrons. In this thesis, we use the convention that the voltage V is positive when the metal plate is positively biased with respect to the ohmic contact, and V is negative when the metal plate is negatively biased with respect to the ohmic contact.

Fig.1.1 Metal-Oxide-Semiconductor capacitor [3].

## **1.2.1 Ideal MOS Capacitor**

The Energy-band diagram of an ideal MOS diode for zero bias is shown in Fig.1.2:

In Sze [1], an ideal MOS diode is defined as follow;

i. In case of zero applied bias, metal  $(\phi_m)$  and semiconductor  $(\phi_s)$  work-function difference  $(\phi_{ms})$  is zero. The band is flat (flat-band condition) when there is no voltage applied Eq.1.1. :

$$\phi_{\rm ms} \equiv \phi_{\rm m} - \left(\chi + \frac{E_{\rm g}}{2q} - \psi_{\rm B}\right) = 0 \tag{1.1}$$

- ii. The only charges that can exist in the structure under any biasing conditions are those in the semiconductor and those with the equal but opposite sign on the metal surface adjacent to the insulator.

- iii. There is no carrier transport through the insulator under dc biasing conditions, or the resistivity of the insulator is infinite.

Fig.1.2 Ideal Metal-Oxide-Semiconductor capacitor band diagram [1].

## 1.2.2 Biasing the MOS Capacitor

Accumulation, Depletion and inversion cases may occur when a MOS-C is biased depending on the thype of the substrate and bias direction. Here we review these modes of operation and the relationships between band-bending, charge, and electric field for a MOS capacitor on a p-type substrate. The analysis for an n-substrate MOS capacitor is similar, with obvious changes for different doping type, doping and fermi level etc.[3].

**Fig.1.3** Biasing Metal-Oxide-Semiconductor diode with p-type substrate: (a) accumulation; (b) depletion; (c) inversion [1].

To understand the different bias modes of an MOS capacitor we now consider three different bias voltages. These bias regimes are called the accumulation, depletion and inversion mode of operation [3].

### 1.2.2.1 Accumulation

Accumulation occurs when one applies a voltage, which is less than the flatband voltage. The minority carriers on the gate attract majority carriers from the substrate to the oxidesemiconductor interface. Only a small amount of band bending is needed to build up the accumulation charge so that almost all of the potential variation is within the oxide.

### 1.2.2.2 Depletion

As a more positive voltage than the flatband voltage is applied, a negative charge builds up in the semiconductor. Initially this charge is due to the depletion of the semiconductor starting from the oxide-semiconductor interface. The depletion layer width further increases with increasing gate voltage.

## 1.2.2.3 Inversion

As the potential across the semiconductor increases beyond twice the bulk potential, another type of negative charge emerges at the oxide-semiconductor interface: this charge is due to minority carriers, which form a so-called inversion layer. As one further increases the gate voltage, the depletion layer width barely increases further since the charge in the inversion layer increases exponentially with the surface potential.

## 1.2.3 Surface Space-Charge Region

In this subsection, the relations between the surface potential, space charge and the electric field are shown. These relations play important role in electrical characteristics of the ideal MOS structures.

Figure 1.4 shows a detailed band diagram at the surface of a p-type semiconductor. The potential  $\psi_s$  is defined as zero in the bulk of the semiconductor and is measured with respect to the intrinsic Fermi level E<sub>i</sub> as shown. At the semiconductor surface,  $\psi = \psi_s$  and  $\psi_s$  is called the surface potential. The electron and hole concentrations as a function of  $\psi$  are given by the following relations;

$$p_{p} = p_{p_{0}} \exp(-q\psi/kT) = p_{p_{0}} \exp(-\beta\psi)$$

$$n_{p} = n_{p_{0}} \exp(q\psi/kT) = n_{p_{0}} \exp(\beta\psi)$$

(1.2)

Fig.1.4 Energy-band diagram at the surface of a p-type semiconductor [1].

where  $\psi$  is positive when the band is bent downward (as shown in Fig.1.4),  $n_{p_0}$  and  $p_{p_0}$  are the equilibrium densities of electrons and holes, respectively, in the bulk of the semiconductor, k boltzmann constant, T temperature and  $\beta = q/kT$ . At the surface the densities are:

$$n_{s} = n_{p_{0}} \exp(\beta \psi_{s})$$

$$p_{p} = p_{p_{0}} \exp(-\beta \psi_{s})$$

(1.3)

From previous discussions and with the help of Eq.1.3, the following regions of surface potential can be distinguished:

| $\Psi_{\rm s}$ < 0            | accumulation of holes (band bends downward)             |

|-------------------------------|---------------------------------------------------------|

| $\Psi_{\rm s} = 0$            | flat-band condition                                     |

| $\Psi_B\!>\!\Psi_s\!>\!0$     | depletion of holes (band bends downward)                |

| $\Psi_{B}=\Psi_{s}$           | midgap with $n_s = p_s = n_i$ (intrinsic concentration) |

| $\Psi_{\rm B} < \Psi_{\rm s}$ | inversion (band bends downward, electron enhancement)   |

The potential  $\Psi$  as a function of distance can be obtained by using the one dimensional Poisson equation.

## 1.2.4. Work-Function Difference and Flat-band Voltage

For an ideal MOS diode, it is assumed that the work-function difference for an n-type semiconductor is zero. If the value of  $\phi_{ms}$  is not zero and if oxide charges  $Q_0$  exist in SiO<sub>2</sub>, the experimental capacitance-voltage curve will be shifted from the ideal theoretical curve by an amount;

$$V_{FB} = \phi_{ms} - \frac{Q_o}{C_i} = \phi_{ms} - \frac{Q_o + Q_f + Q_m + Q_{it}}{C_i}$$

(1.4)

where  $V_{FB}$  is called the flat-band voltage shift,  $Q_f$  fixed charges,  $Q_m$  mobile charges and  $Q_{it}$  interface states. If negligible interface traps, mobile ionic charges and oxide trapped charges exist, equation reduces to;

$$V_{FB} = \phi_{ms} - \frac{Q_f}{C_i}$$

(1.5)

#### **1.2.5 Ideal MOS Capacitor Analysis**

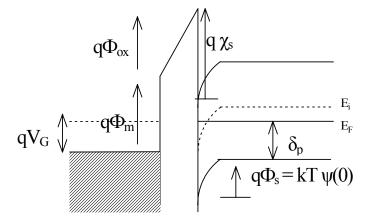

We now give the MOS parameters with the aid of Figure 1.4

**Fig.1.5** (a) Potential; (b) charge; (c) electric field diagram at the surface of a p-type semiconductor [3].

Two assumptions will be made to simplify the MOS analysis: i) the full depletion approximation can be used in a MOS-C and ii) inversion layer charge is zero below the threshold voltage. We also assume that inversion layer charge linearly changes with the gate voltage for voltages beyond the threshold. The derivation starts by examining the charge per unit area in the depletion layer,  $Q_d$ . As can be seen in Figure 1.5.b, this charge is given by:

$$Q_d = -qN_a X_d \tag{1.6}$$

Where  $X_d$  is the depletion layer width and  $N_a$  is the acceptor density in the substrate. The Electric field distribution which is obtained by integration of the charge density is shown in Fig. 1.5.c. The electric field in the semiconductor at the interface,  $E_s$ , and the field in the oxide  $E_{ox}$ , are equal:

$$E_s = \frac{qN_a X_d}{\varepsilon_s} \tag{1.7}$$

The difference in the dielectric constants of oxide and semiconductor causes an abrupt change in the electric field at the oxide-semiconductor interface. The dielectric constant for Silicon is  $11.9\varepsilon_0$  and for SiO<sub>2</sub> is  $3.9\varepsilon_0$ . Therefore the electric field is about three times larger

in the oxide side at the semiconductor-oxide interface. The electric field in the semiconductor changes linearly due to the constant doping density and is zero at the edge of the depletion region. The potential shown in Figure 1.5.a is obtained by integrating the electric field. The potential at the surface,  $\psi_{s}$ , equals:

$$\psi_s = \frac{qN_a X_d^2}{2\varepsilon_s} \tag{1.8}$$

The calculated field and potential is only valid in depletion. In accumulation, there is no depletion region and the full depletion approximation does not apply. In inversion, there is an additional charge in the inversion layer,  $Q_{inv}$ . This charge increases gradually as the gate voltage is increased. However, this charge is only significant once the electron density at the surface exceeds the hole density in the substrate,  $N_a$ . We therefore define the threshold voltage as the gate voltage for which the electron density at the surface equals  $N_a$ . This corresponds to the situation where the total potential across the surface equals twice the bulk potential,  $\psi_B$ .

$$\psi_B = V_T \ln \frac{N_a}{n_i} \tag{1.9}$$

The depletion layer in depletion is therefore restricted to this potential range;

$$X_{d} = \sqrt{\frac{2\varepsilon_{s}\psi_{s}}{qN_{a}}} \quad \text{for } 0 \le \psi_{s} \le 2\psi_{B}$$

(1.10)

For a surface potential larger than twice the bulk potential, the inversion layer charge change increases exponentially with the surface potential. Consequently, an increased gate voltage yields an increased voltage across the oxide while the surface potential remains almost constant. We will therefore assume that the surface potential and the depletion layer width at threshold equal those in inversion. The corresponding expressions for the depletion layer charge at threshold,  $Q_{d,T}$ , and the depletion layer width at threshold,  $X_{d,T}$ , are given as:

$$Q_{d,T} = -qN_a X_{d,T} \tag{1.11}$$

$$X_{d,T} = \sqrt{\frac{2\varepsilon_s(2\psi)}{qN_a}}$$

(1.12)

Beyond threshold, the total charge in the semiconductor has to balance the charge on the gate electrode,  $Q_M$ , or

$$Q_M = -(Q_d + Q_{inv})$$

(1.13)

where we define the charge in the inversion layer as a quantity which needs to determined but should be consistent with our basic assumption. This leads to the following expression for the gate voltage,  $V_G$ :

$$V_{G} = V_{FB} + \psi_{s} + \frac{Q_{M}}{C_{ox}} = V_{FB} + \psi_{s} - \frac{Q_{d} + Q_{inv}}{C_{ox}}$$

(1.14)

where  $C_{ox}$  is the oxide capacitance.

In depletion, the inversion layer charge is zero so that the gate voltage becomes:

$$V_{G} = V_{FB} + \psi_{s} + \frac{\sqrt{2\varepsilon_{s}qN_{a}\psi_{s}}}{C_{ox}} \quad \text{for } 0 \le \psi_{s} \le 2\psi_{B}$$

(1.15)

while in inversion this expression becomes:

$$V_G = V_{FB} + \psi_B + \frac{\sqrt{4\varepsilon_s q N_a \psi_s}}{C_{ox}} - \frac{Q_{inv}}{C_{ox}} = \Delta V_T - \frac{Q_{inv}}{C_{ox}}$$

(1.16)

the third term in Eq.1.16 states our basic assumption, namely that any change in gate voltage beyond the threshold requires a change of the inversion layer charge

### 1.3 MOS Capacitor and Oxide Charges

This section can be found in B. Van Zeghbroeck's book, "*Principles of Semiconductor Devices*" in a more detailed from [3]. The most important metal-insulator-semiconductor structure is metal-SiO<sub>2</sub>-Si by far and in this subsection, SiO<sub>2</sub>-Si system will be described briefly and the oxide and interface charges will be reviewed. A picture of the SiO<sub>2</sub>-Si

interface is that the chemical composition of the interfacial region, as a consequence of thermal oxidation, is single-crystal silicon followed by a monolayer of  $SiO_x$ , that is, incompletely oxidized silicon, then a strained region of  $SiO_2$  and the remainder stoichiometric, strain-free, amorphous  $SiO_2$ . For a practical MOS diode, interface traps and oxide charges exist that will, in one way or another, affect the ideal MOS characteristics. There are four general types charges associated with  $SiO_2$ -Si diodes :

- i. Fixed Oxide Charge ( $Q_f$ ,  $N_f$ ); these are positive charges due primarily to structural defects (ionized silicon) in the oxide layer. The density of this charge, whose origin is related to the oxidation process, depends on the oxidation ambient and temperature, cooling conditions, and silicon orientation. Because that the fixed oxide charges cannot be determined unambiguously in the presence of moderate densities of interface trapped charges, these are only measured after a low-temperature hydrogen or forming gas anneal, which minimizes interface trapped charge.

- ii. Oxide trapped charges (Q<sub>ot</sub>, N<sub>ot</sub>); these charges may be positive or negative due to holes or electrons trapped in the bulk of the oxide. Trapping may result from ionizing radiation, avalanche injection, tunneling or other mechanisms. Unlike fixed oxide charges, oxide trapped charges are sometimes annealed by lowtemperature treatments, although neutral traps remain.

- Mobile oxide charges (Q<sub>m</sub>, N<sub>m</sub>); these are caused primarily by ionic impurities such as Na<sup>+</sup>, Li<sup>+</sup>, K<sup>+</sup>, and possibly H<sup>+</sup>. Negative ions and heavy metals may contribute to this type of charges.

- iv. Interface trapped charge (Q<sub>it</sub>, Q<sub>ss</sub>, N<sub>it</sub>, N<sub>ss</sub> D<sub>it</sub>); this type of charge is also called surface states, fast states, interface states, and so on. These are positive or negative charges, due to structural defects, oxidation-induced defects, metal impurities, or other defects caused by radiation or similar bond-breaking processes. These charges are located at the SiO<sub>2</sub>-Si interface. Unlike fixed charges or trapped charges, they are in electrical communication with the underlying silicon. Interface traps can be charged or discharged, depending on the surface potential. Most of the interface states can be neutralized by low-temperature hydrogen or forming gas anneals. These localized states can affect the I-V characteristic of MOS capacitor. The effect of these states can be grouped into two categories: The first group is concerned with the electrostatic effects while the second with the dynamic effect [2]. The electrostatic effect can be xplained as follows; due to the charge storage in

the surface states, charge distrubition through and voltage drop over the oxide are affected strongly by interface state concentration  $D_{it}$ . There are two types of surface states; donor-like and acceptor-like states. The energy of donor states is less than the energy of surface state, which contributes a positive  $Q_{ss}$  when they are emptied while the energy of the latter is greater than  $E_{ss}$  which contributes a negative Qss, when they are occupied. The value of Qss and its sign can increase or decrease the band bending  $\psi_s$ . The dynamic effects of surface states are important at two points; first, they provide additional path for the carriers and secondly, they act as recombination centers.

#### 1.4. Current Mechanisms in MOS Capacitors

In this section we present an extensive list of several proposed MIS current models and we give brief descriptons of those models.

### 1.4.1 Fowler-Nordheim Tunneling

Fowler-Nordheim emission is one of the most important mechanisms in MOS structures. It is the tunneling of electrons between the gate and the conduction band of the bulk through a triangular barrier. This mechanism was first proposed by Fowler and Nordheim [5] and then named after them. In the last three decades the FN tunnelng in the MOS capacitor structure has been intensively studied by many researchers [6-18]. The tunnel current component is computed as;

$$J_{FN} = a |E|^2 \exp(-b/|E|)$$

(1.17)

where a and b are fitting parameters and E is the electric field in the oxide. Lenzlinger and Snow [6] generalized the model and obtained a more explicit analytical result. Their current density is given as:

$$J_{FN} = \frac{q^{3}m_{0}}{8m_{ox}h\phi_{b}\pi} \left| E^{2} \right| \cdot \exp(-\frac{4\sqrt{2m_{ox}\phi_{b}^{3}}}{3q\hbar|E|})$$

(1.18)

where  $m_{ox}$  is the mass of the carriers in the oxide,  $m_0$  is the free electron mass, h planck constant, q charge and  $\phi$  is the potential barrier height that a carrier tunnels through. The oxide mass and the barrier height are used as physically-based fitting parameters. This

emission occurs under high electric field (more than 8-10 MeV/cm) since the theory assumes the barrier to be triangular. A brief derivation of Fowler-Nordheim current density for simple case ,that is no image force lowering or no finite temperature effects, is as follows (in this derivation we follow Depas et. al. [19]):

The tunneling current between tha gate and the semiconductor is given by

$$J_{FN} = \frac{4\pi q m_t}{h^3} \int_{0}^{E_F} dE \int_{0}^{E} T_t dE_t$$

(1.19)

where  $E_t$  is the transversal energy component, E the energy of the tunneling electron measured from the semiconductor conduction band edge at the SiO<sub>2</sub>-Si interface and T<sub>t</sub> the tunneling probability. T<sub>t</sub> is given by WKB approximation as:

$$T_{t} = \exp(-2\int_{0}^{x_{1}} k_{ox}(x)dx)$$

(1.20)

where  $k_{ox}$  is the wave vector of the tunneling electron and x is the barrier length. After all the calculations performed, the tunneling probability is found as;

$$T_{t} = \exp(-\frac{4\sqrt{2m_{ox}}}{3qh}\frac{(\phi_{b} + E_{F} - E + \frac{m_{t}E_{t}}{m_{ox}})^{3/2}}{E_{ox}})$$

(1.21)

A first order Taylor expansion on T around  $E = E_F$  and  $E_t = 0$  leads to the Eq.1.18. A plot of ln (J/E<sup>2</sup>) vs. 1/E ,so called Fowler-Nordheim plot, should be straight line if the F-N mechanism is the dominant mechanism in conduction through the oxide. The intercept and the slope of this plot yield the oxide mass and the barrier height.

### **1.4.2 Direct Tunneling**

An accurate modeling of tunneling current in today's ultra-thin oxide MOS devices cannot be accomplished by widely used Lenzlinger-Snow FN model since it implies a metal as a gate and a triangular barrier. They are largely obsolete conditions for today's devices where very high tunneling probability due to ultra-thin oxides (less than 4-5 nm), quantization effects of both electrons and holes in both inversion and accumulation regime, poly-silicon depletion, several tunneling mechanisms besides conduction band electron tunneling and a trapezoidal barrier play fundamental role in conduction. For these reasons many authors have proposed new models to introduce these effects into current modeling [20-27]. In 1993, Schuegraf and Hu [28] introduced a tunneling model by taking the fact that the polysilicon gate and interface states at SiO<sub>2</sub>-Si cause a trapezoidal barrier rather than triangular barrier as in Fowler-Nordheim emission, into account. Their approach was the same as Snow and Lenzlinger's but their tunneling probability was modified approprietly with respect to new barrier shape:

Fig. 1.6. Fowler-Nordheim and direct tunneling mechanisms.

The tunneling probability is given as:

$$T_{t} = \exp\left(-\frac{4\sqrt{2m_{ox}}}{3qh}\frac{(\phi_{b} + E_{F} - E + \frac{m_{t}E_{t}}{m_{ox}})^{3/2} - (\phi_{b} + E_{F} - E + \frac{m_{t}E_{t}}{m_{ox}} - qV_{ox})^{3/2}}{E_{ox}}\right) \quad (1.22)$$

They computed the current density as:

$$J_{DT_{l}} = \frac{A \cdot |E^{2}|}{\left(1 - \sqrt{1 - qV_{ox}/\phi_{b}}\right)^{2}} \exp\left\{-\frac{B}{E_{ox}}\left[1 - (1 - qV_{ox}/\phi_{b})^{3/2}\right]\right\} \cdot \left\{1 - \exp\left[-\frac{3BE_{F}}{2E_{ox}} \cdot \phi_{b}(1 - \sqrt{1 - qV_{ox}/\phi_{b}})\right]\right\} (1.23)$$

with A and B, defined as:

$$A = \frac{q^{3}(m_{o} / m_{ox})}{8\pi h \phi_{b}} \text{ and } B = \frac{8\pi \sqrt{2m_{ox}\phi_{b}^{3}}}{3qh}$$

(1.24)

For accumulation case, where

$$E_F > \frac{4\phi_b^3}{3qBt_{\rm ex}} \tag{1.25}$$

the current density reduces to;

$$J_{DTt} = \frac{A|E^2|}{\left(1 - \sqrt{1 - qV_{ox} / \phi_b}}\right)^2} \exp\left\{-\frac{B}{E_{ox}} \left[1 - \left(1 - qV_{ox} / \phi_b\right)^{3/2}\right]\right\}.$$

(1.26)

In 2000, Lee and Hu [29], proposed a generalized direct tunneling model which is valid in both depletion and accumulation. The current density in their model is very similar to Schuegraf-Hu model except for the correction function;

$$J_{DTt} = \frac{q^3}{8\pi h \varepsilon_{ox} \phi_b} C(V_G, V_{ox}, t_{ox}, \phi_b) \cdot \exp\left\{-\frac{B}{E_{ox}} \left[1 - (1 - qV_{ox} / \phi_b)^{3/2}\right]\right\}$$

(1.27)

where  $C(V_G, V_{ox}, t_{ox}, \phi_b)$  is the correction function;

$$C(V_{G}, V_{ox}, t_{ox}, \phi_{b}) = \exp\left[-\frac{20}{\phi_{b}}\left(\frac{|V_{ox}| - \phi_{b}}{\phi_{off}} + 1\right)^{\alpha} \cdot \left(1 - \frac{|V_{ox}|}{\phi_{b}}\right)\right] \cdot \frac{V_{G}}{t_{ox}} \cdot N$$

(1.28)

$$N = \frac{\varepsilon_{ox}}{t_{ox}} \cdot \left\{ S \cdot \ln \left[ 1 + \exp\left(\frac{V_{eff} - V_T}{n_{inv}V_T}\right) \right] + V_T \cdot \ln \left[ 1 + \exp\left(-\frac{V_G - V_{FB}}{V_T}\right) \right] \right\}$$

(1.29)

where  $\alpha$  is a fitting parameter,  $t_{ox}$  is the tickness of the oxide, S is subtreshold swing,  $V_T$  is the thermal velocity.

The main difference between this model and Schuegraf's model is the correction factor. The exponential term accounts for secondary effects such as energy dependence of the densities of states at the electrode interface and effective masses in the dielectric, and that affects the curvature of the tunneling characteristic. N is an indicator of the density of either the tunneling carriers for electron conduction band tunneling (ECB) and hole valence band tunneling (HVB) or the receiving energy states for EVB. The rate of increase of the subtreshold carrier density with  $V_G$  is dictated by  $n=S/V_T$  (S is the subtreshold swing in inversion or accumulation). These effects were neglected in Schuegraf's approach altough that approach gives good results in accumulation and depletion modes.

There are also many other direct tunneling models proposed by different groups as brand new models or modification of Schuegraf-Hu model [29-48].

#### 1.4.3 Band-to-Band Tunneling

This model describes the current due to carriers tunneling between the band of the semiconductor to the band of the gate and vice versa. It describes the same physicsal process with Fowler-Nordheim and Direct tunneling do. The difference between this model and Fowler-Nordheim or Direct Tunneling model is the temperarture dependency. The difference comes from the handling of the systems. This model follows the same steps while deriving the final current density function but it uses the thermal velocity. This approach causes a second order temperature factor in the final form of current density. The derivation can be summarized as follows and the details can be found in Card-Rhoderick [49, 50]or Kumar-Dahlke [51]:

Starting from the Eq.1.19 and substituting the tunneling probability into that equation and evaluation of the integration over the energy range yields;

$$J_{BTB} = A^* T^2 \cdot \exp(-\beta \phi_b) \cdot \exp(-q \phi_s / kT) \cdot \left[\exp(q V_G / kT) - 1\right]$$

(1.30)

where  $A^*$  is the Richardson constant,  $exp(-\beta \varphi_b)$  the tunneling probability,  $\varphi_s$  the schottky barrier between the gate and the semiconductor. There is a significant similarity between this model and Schottky theory since the kinetic energy of the carriers is used in transport equations. In other words band-to-band tunneling can be approximated as Schottky model with a transmission probability through the oxide and this mechanism can be important for especially MOS diodes with very thin ( $\sim$  5-10 Angstrom) oxide.

### 1.4.4 Trap Assisted Tunneling

There are many models related with traps such as pure trap assisted tunnelings or Poole-Frenkel emission or hopping conduction etc. In this subsection, hovewer, we only present the pure trap assisted tunneling models in the oxide. The other mechanisms mentioned above will be given in subsequent sections.

The existance of electron trap levels in the dielectric layer of a metal-oxide-semicondcutor device can result in a considerable leakage current at electric fields well blow those needed for Fowler-Nordheim or direct tunneling, in which electrons gain sufficient energy to tunnel directly from the gate electrode to the inulator or semiconductor conduction band and vice versa. Trap assisted conduction is a two-step process in which electrons first tunnel directly into a trap, and then are able to tunnel into the conduction band of the insulator or semicondcutor, incorporating energy loss by phonon relaxation.

The electrical conduction mechanisms of thin trapped oxides and nitrides have attracted much attention over many years [52-67]. The basic trap assisted current density is given as;

$$J_{TAT} = q \int_{0}^{t_{ox}} \frac{C_t N_t P_1 P_2}{P_1 + P_2} \text{ or } J_{TAT} = \int_{0}^{t_{ox}} \frac{q N_t}{\tau_c + \tau_e} dx \text{ or } J_{TAT} = \int_{0}^{t_{ox}} \sigma N_t \frac{J_{in} J_{out}}{J_{in} + J_{out}} dx \quad (1.31)$$

or in similar forms. However the models employed in the form above work rely on the calculation and numeraical evaluation of integrals and hence are not readily applied to experimental data. There are also other TAT tunneling models that are ready to be applied to experimental data. We give a small description of those models in subsequent subsections.

## Fleischer`s TAT Model;

In 1992 Fleischer, Lai, and Cheng [55] proposed a trap assisted tuneling model in MOS devices. Their model is based on two-step tunneling. The current density is given as in Eq.1.31. This equation reduces to

$$J_{TAT} = \frac{\frac{2qC_{t}N_{t}\phi_{t}}{3E} \cdot \exp(-\frac{A\phi^{3/2}}{E})}{3E}$$

(1.32)

This equation makes it possible to extract the trap energy from the slope of the plot of ln (JE) vs. 1/E without heavy calculations;

$$\phi_t = \left(-\frac{slope}{A}\right)^{2/3} \tag{1.33}$$

The advantage of these appraoches is the easiness of data evaluation and reduced number of fit parameters. One doesn't need to make simulations or heavy computational calculations. Instead, by plotting ln (JE) vs 1/E, it i easy to determine the trap energy from the slope. By deriving trap energy as a first step, the fitting procedure can be expected to be easier and more accurate. It is necessary to either use both  $\varphi_t$  and N<sub>t</sub> as fitting parameters or to determine one of them by an independent method (such as C-V, avalanche injection, high-field injection or Poole-Frenkel evaluation etc.) when the numerical solution or simulation tools are used. Now both of these trap parameters can be extracted directly from the I-V measurements with respect to this theory.

#### Chang's TAT Model;

This model [65] employs a general trapezoidal barrier rather than a triangular barrier which is oftenly used in conventional trap assisted models. The derivation of an explicit analytical current density is the same as in Fleischer's model except the barrier function. The model predicts the current density as:

$$J_{TAT} \propto \exp(-\frac{4\sqrt{2qm_{ox}}\phi^{3/2}}{3\hbar E})$$

(1.34)

By plotting ln(J) vs 1/E, it is easy to determine the trap energy from the slope.

### 1.4.5. Poole-Frenkel Tunneling

This mechanism is due to field-enhanced thermal excitation of trapped electrons into the conduction band of  $SiO_2$ . The structural defects cause additional energy states close to the band-edge called traps. These traps restrict the current flow because of a capture and emission process. The current is a simple drift current described by

$$J_{PF} = nq\mu E \tag{1.35}$$

where n is the carrier density and  $\mu$  mobility [67]. While the carrier density depends exponentially on the depth of the trap which is corrected for the electric field

$$n = n_0 \exp\left[-\frac{q}{kT}\left(\phi_t - \sqrt{\frac{qE}{\pi\varepsilon_i}}\right)\right]$$

(1.36)

then current density becomes;

$$J_{PF} = q n_0 \mu E \cdot \exp\left[-\frac{q}{kT}\left(\phi_t - \sqrt{\frac{qE}{\pi\varepsilon_i}}\right)\right]$$

(1.37)

Fig. 1.7 Poole-Frenkel emission

## 1.4.6. Space-charge limited current

The space-charge limited current results from carrier injection into the insulator, where no compensating charge is present. For structures where carriers can readily enter the insulator and freely flow through the insulator one finds that the resulting current and carrier densities are much higher. The density of free carriers causes a field gradient, which limits the current density. This situation occurs in lowly doped semiconductors and vacuum tubes.

The well-known expression for space charge limited current, Eq. 1.38, is found by starting from an expression for the drift current and Gauss's law (it is assumed that the insulator contains no free carriers if no current flows). See for example [3] for details.

$$J = \frac{9\varepsilon \cdot \mu \cdot V^2}{8d^3} \tag{1.38}$$

where d is the thickness,  $\varepsilon$  is the permittivity and  $\mu$  is the mobility of the insulator.

#### **1.4.7. Hopping Conduction (Ohmic Conduction)**

At very low voltages and high temperatures, current is expected to be carried by thermally excited electrons hopping from one isolated state to the next. This mechanism yield an ohmic characteristic exponentially dependent on temperature. The current density is given as [1]:

$$J \propto E \cdot \exp(-\Delta E_a / kT) \tag{1.39}$$

where  $\Delta E_a$  is the activation energy.

## 1.4.8. Schottky-like Emission (Modified Poole-Frenkel Current)

This mechanism is similar to the thermionic emission in metal-semiconductor junctions. Thermal electrons which are emitted across the gate-oxide or semicondcutor-oxide interface are responsible for the carrier transport.

Fig. 1.8 Schottky emission

The thermionic emission theory by Bethe [68] is derived from the assumption that (i) the barrier height is much larger than kT and (ii) thermal equilibrium is established at the plane that determines emission, and (iii) the existance of net carrier flow does not affect this equilibrium. Because of these assumptions the shape of the barrier profile is immaterial and the current flow depends solely on the barrier height. The current density between the gate and the semiconductor is then given by the concentration of electrons with energies sufficient to overcome the potential barrier and traversing in the transport direction:

$$J = \int_{E_{F+q\phi_B}}^{\infty} q v_x dn \tag{1.40}$$

where  $E_F + q\Phi_B$  is the minimum energy required for thermionic emisson into the oxide, and  $v_x$  is the carrier velocity in the direction of transport. The electron density in an incremental energy range is given by :

$$dn = N(E)F(E)dE = \frac{4\pi (2m^*)^{3/2}}{h^3} \sqrt{E - E_c} \exp\left[-\left(E - E_c + qV_n\right)/kT\right] dE \quad (1.41)$$

where N(E) and F(E) are the density of states and the distribution function respectively and  $qV_n$  is  $(E_c-E_F)$ . If we postulate that all the energy of electrons is kinetic energy, then

$$E - E_c = \frac{1}{2}m^* v^2 \tag{1.42}$$

If the speed is resolved into its component along the axes with th x axis parallel to the transport direction, we have

$$v^2 = v_x^2 + v_y^2 + v_z^2 \tag{1.43}$$

With the required transformations, we obtain the thermionic current as;

$$J = A^*T^2 \exp\left(-qV_n / kT\right) \exp\left(-\frac{m^* v_{ox}^2}{2kT}\right)$$

(1.44)

where  $\mathbf{v}_{ox}$  is the minimum velocity required in the x direction to surmount the barrier and is given by

$$\frac{1}{2}m^* v_{ox}^2 = q(V_{bi} - V) \tag{1.45}$$

where V<sub>bi</sub> is the built-in potential at zero bias. Substituting Eq.1.45 into Eq.1.44 yields

$$J = A^*T^2 \exp\left(-q\phi_B / kT\right) \exp\left(\frac{qV}{kT}\right)$$

(1.46)

Since the barrier height for electrons moving into the oxide remains the same, the current flowing into the oxide is thus unaffected by the applied voltage. It must therefore be equal to the current flowing from the semiconductor into the metal when thermal equilibrium prevails (i.e. when V=0). The corresponding current density is obtained from Eq.1.46 by setting V=0 as;

$$J = A^*T^2 \exp\left(-q\phi_B / kT\right) \tag{1.47}$$

However, when the electron enters the oxide, charge is redistributed on the electrode to maintain the equipotential surfaces. The result is to produce a so-called image field that adds to the applied field and helps to round and lower the potential barrier. The image lowering is given as [1] :

$$\sqrt{\frac{qE}{4\pi\varepsilon}} \tag{1.48}$$

and the thermionic current for MOS devices becomes

$$J = A^* T^2 \exp\left[q\left(\phi_b - \sqrt{\frac{qE}{4\pi\varepsilon}}\right)/kT\right]$$

(1.49)

A plot of  $\ln(J/T^2)$  vs. 1/T yields a straight line with a slope determined by the permittivity of the oxide.

#### 1.4.9. Surface-State Tunneling

Following the approach of Freeman and Dahlke [69, 70], the electron current,  $J_{ns}$ , from the conduction band of the semiconductor to the surface states is given by:

$$J_{ns} = q D_{it} v_{th} \sigma_n [(1 - f_t) n_s - f_t n_1)$$

(1.50)

where  $v_{th}$  is the thermal velocity,  $D_{it}$  density of surface states,  $\sigma$  capture cross-section area for electrons,  $f_t$  surface state occupation probability with tunneling current through the surface states,  $n_s$  ( $p_s$ ) electron (hole) concentration at the semiconductor surface,  $n_1$  ( $p_1$ ) electron (hole) concentration if the electron (hole) Fermi level is at the trap energy level. The hole current,  $J_{ps}$ , from the valence band to the surface states can be written as:

$$J_{ps} = qD_{it}v_{th}\sigma_p[f_t p_s - (1 - f_t)p_1]$$

(1.51)

and the total current through the surface states,  $J_{ss}$ , is

$$J_{ss} = J_{ns} - J_{ps} = \frac{qD_{it}}{\tau_t} (f_t - f_m)$$

(1.52)

where  $f_m$  is the occupation probability of an energy level in the metal. By substituting the Eqn.1.50 and Eq.1.51 into Eq.1.52 one obtains the surface state tunneling density. See [45] for details. Surface states provide additional path for carriers and they act as recombination centers at the surface.

#### 1.4.10. Diffusion Current

Diffusion current can be calculated by following Hovel's approach [71] by solving the continuity equation and applying the appropriate boundary conditions. Diffusion current can behave a limiting current when all the carriers supplied to the substrate are able to pass to the gate. This mechanism can especially be important in thin oxides where the transmission probability through the oxide is very high and the current in the device will be governed by the substrate. Mathematical details can be found in many papers [70].

## 1.4.11. Recombination-Generation Current

The generation-recombination mechanism plays an important role in MOS devices due to oxide-semiconductor interface. The surface states can behave as a recombination centers. If the surface state density is high then recombination-generation current might be significant and descriptive for a MOS device. The recombination-generation current is given as:

$$J_{rg} = \frac{qn_i W}{\tau_n} (e^{\beta \phi_s / 2} - 1)$$

(1.53)

The derivation of this formula can be found in many books [1].

### **CHAPTER 2**

### **EXPERIMENTAL PROCEDURES**

We will briefly describe the basic fabrication steps of MOS capacitors. This chapter does not aim to explain all the process methods and details of a MOS capacitor but only main steps of fabrication of our samples. We will also give a short description of our measurement setup for current-voltage measurements.

One of the samples (Aliminum gate MOS) was prepared at our laboratory, and the other sample (PolySi gate MOS) was prepared at Physical Electronics & Photonics Laboratory at Chalmers, Sweden.

## 2.1 Al-SiO<sub>2</sub>-Si MOS

The first sample we worked on was a relatively thick oxide MOS capacitor (1250 Angstroms) with  $Al/SiO_2/n$ -Si structure. To produce this sample we basically followed the steps shown in the figure 2.1 below:

Our wafer was n-type Si (100) with a doping of  $1 \times 10^{16}$ . We applied a cleaning procedure to this wafer to reduce the contamination on the wafer (Fig.2.1.a). Then we used thermal oxidation (dry) method under N<sub>2</sub> atmosphere to coat the Si with SiO<sub>2</sub> (Fig.2.1.b). The oxidation was performed in a furnace at 1050  $^{0}$ C for 80 minutes. In this phase of the process, top and bottom surface of the Si-wafer was coated with SiO<sub>2</sub>. Then, the bottom oxide was etched with Hydrofluoric acid (HF, 10%) to be able to deposit metal (Al) onto Si for back contact (Fig.2.1.c). After etching, we formed the gate of our MOS-C by Aluminum deposition with the help of a shadow mask in a deposition chamber. Finally, we deposited Aluminum onto the back side of the Si-wafer to have the back contact (Fig.2.1.d).

We will present the Si-wafer cleaning procedure in detail and abrief summary of oxidation in In subsection 2.1.1. and 2.1.2.

**Figure.2.1.** Fabrication of a MOS capacitor: a) Wafer cleaning; b) dry oxidation, c) etching; d) Metal formation.

## 2.1.1 Wafer Cleaning

Wafer cleaning has a central role in semiconductor device production. Due to the fact that existing organic (dust, oil etc.) and inorganic (native oxide, metallic ions etc.) contaminations on the wafer can effect the characteristics of the devices, wafers must be cleaned before any processing.

The first sample we used in this study was cleaned before oxidation with the following chemical processes:

- 1. Boiling in trichloroethylene: Removes organic contaminants,

- 2. Ultrasonically agitation first in deionized water and later in acetone,

- 3. Boiling in the mixture of  $HCl : H_2O_2 : H_2O :$  Removes metallic impurities and prevents their displacement plating back onto the silicon,

- 4. Washing in deionized water for a few minutes: Cleans up the traces of the chemicals from the preceding treatment,

- Boiling in the mixture of H<sub>2</sub>SO<sub>4</sub> : H<sub>2</sub>O<sub>2</sub> : H<sub>2</sub>O : Removes both organic and metallic films,

- 6. Washing in deionized water : Removes the remnants coming from the previous step,

- Dipping a solution of HF: H<sub>2</sub>O: Strips the thin native oxide layer on the sample (silicon atoms bond with the hydrogen atoms after the removing of oxide on the surface and this prevents the wafer from new oxidation for a while).

- 8. Washing in deionized water,

- 9. Drying by using N<sub>2</sub>.

### 2.1.2 Oxidation

An oxide layer is rapidly formed when silicon wafer is exposed to an oxidizing ambient since silicon surface has a high affinity for oxygen. Two techniques are commonly used for oxidation: Thermal oxidation and chemical vapor deposition (CVD).

The deposition of  $SiO_2$  using a CVD process is one where two gases, silane and oxygen, react to form silicon dioxide, which then sublimes onto any solid surface. The wafers are heated to 200 - 400°C yielding high quality oxides.

The thermal oxidation of silicon is obtained by heating the wafer in an oxygen or water vapor ambient. Typical temperatures range from 800 to 1200°C. The oxidation of a silicon surface also occurs at room temperature but the resulting 3 nm layer of oxide limits any further oxidation. At high temperatures, oxygen or water molecules can diffuse through the oxide so that further oxidation takes place. The oxidation in oxygen ambient is called a dry oxidation. The one in water vapor is a wet oxidation. The thermal oxidation provides a high quality interface and oxide. It is used less these days because of the high process temperatures [3].

Finally Aluminum deposition process was performed for front and back contacts. Fig. 2.3 below shows our metallization setup.

Fig. 2.2 Furnace system for oxidation

#### 2.2. PolySi-SiO<sub>2</sub>-Si MOS

This sample was prepared at Physical Electronics and Photonics Laboratory of Chalmers University of Technology, Gothenburg, Sweden. The structure is p-polysilicon/SiO<sub>2</sub>/n-Si. The details are as follows:

The capacitor (PMOS) was fabricated on (100) n-type Silicon wafers from Wacker Silctronic. Ultrathin nitrided gate dielectric structure was grown at 750-800  $^{0}$ C by using an ASM A400 vertical furnace. The gate electrode p+-poly-Si (p-type, Boron doped greater than  $1 \times 10^{20}$  cm<sup>-3</sup> and its thickness is 200 nm) was deposited in a low pressure chemical vapor deposition (LPCVD) ASM chamber using SiH<sub>4</sub> at a pressure of  $5.3 \times 10^{3}$  pa and temperature of 615  $^{0}$ C. In order to facilitate nucleation of poly-Si on the SiO<sub>2</sub> an undoped Si seed layer with a nominal thickness of 1 nm was deposited at 615  $^{0}$ C prior to poly-Si layer deposition [3].

Fig. 2.3 Metal deposition system

#### 2.3. Electrical Characterization Setup

In this thesis two different electrical measurements were performed; current-voltage (I-V) and capacitance-voltage (C-V). The aim of this thesis is to investigate the electrical transport in MOS structures based on I-V methods. Therefore C-V investigation is out of the scope of this thesis and will not be discussed in detail in this thesis, but we will give the basic C-V curves of our samples for the sake of completeness of electrical characterization. Only I-V measurements were performed as temperature dependent due to the same reason and C-V measurements were performed at  $300^{0}$ K.

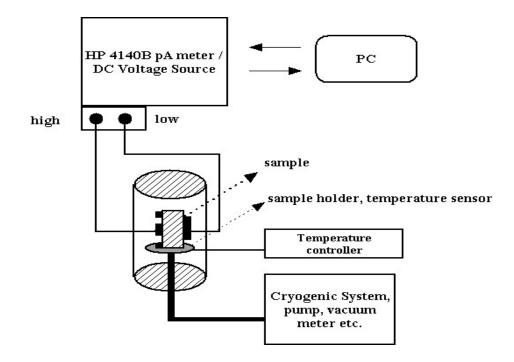

We used Hewlett- Packard (HP) 4140B pA meter / DC voltage source for I-V measurement and HP 4192 LF impedance analyzer for C-V measurements. Basic schematics of these setups are as follows:

Fig.2.4 C-V measurement system.

Figure 2.5 Temperature dependent I-V measurement system.

### **CHAPTER 3**

## ELECTRICAL TRANSPORT IN THICK SIO<sub>2</sub> FILM

### 3.1. Al-SiO<sub>2</sub>-Si Capacitor

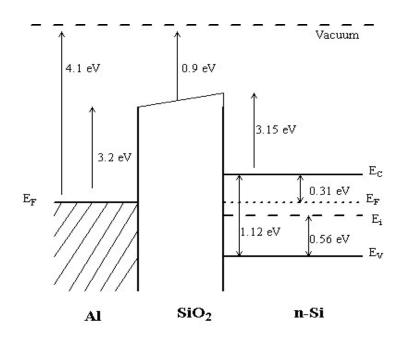

In this part of the thesis, we present our work on MOS capacitor fabricated on a thick  $SiO_2$  layer. The oxide thickness is  $1250 \pm 10$  Angstroms. The gate material is Aluminum and the substrate is n-type Silicon (100). Fabrication processes were described in the previous chapter. The band diagram of this structure is as follows:

Fig. 3.1 Band structure of Al-SiO<sub>2</sub>-Si

### **3.2. Electrical Characteristics:**

### 3.2.1. C-V and G-V Curves:

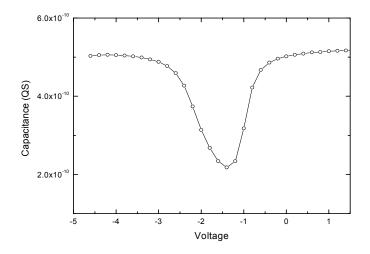

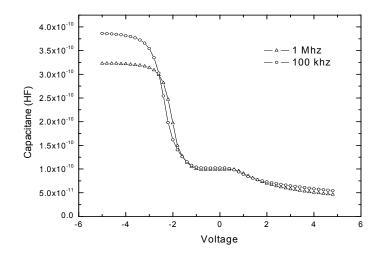

The C-V curves of the sample are as follows:

Fig. 3.2 Quasi-Static (QS) capacitance-voltage curve of sample-1

Fig.3.3 High-frequency capacitance at 1 MHz and 100 kHz.

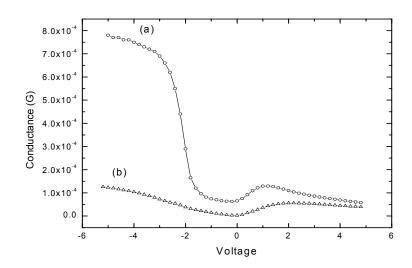

Fig. 3.4 shows the conductance-voltage curves we measured at the same frequancies:

Fig.3.4 Conductance vs. voltage curves at (a) 1 MHz and (b) 100 kHz.

The quasi-static and high frequency curves indicate a certain MOS structure but they also show a leakage current in the oxide. The conductance-voltage curve shows a minimum at almost V=0. G-V curve also reveals that there is a leakage in the accumulation regime. This means that the carriers are able to pass through the oxide and the conductance increases due to these carriers. However, the saturation in the high frequency capacitance in accumulation indicates that the ratio of the leakage carriers is small compared to total carriers.

A thick oxide contains traps and these traps help carriers to leak in the oxide. Flat band voltage value ( $\sim$ -2.3 V) also supports these basic conclusions about our oxide.

#### 3.2.2. I-V Curves

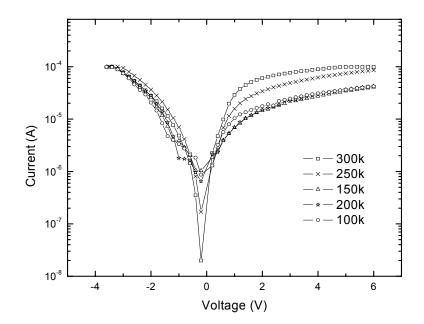

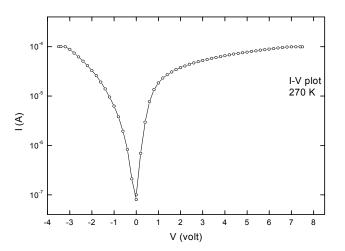

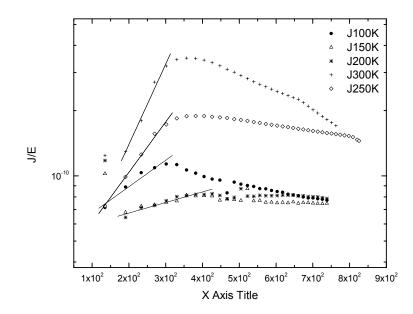

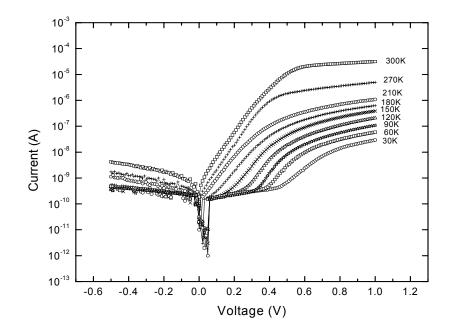

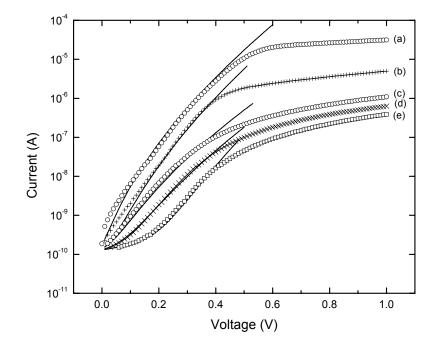

Current-Voltage measurements were performed in a broad temperature range from 20 K to 300 K. The I-V curves at selected temperatures are shown in figure 3.5:

Fig. 3.5 Current-Voltage graphics at different temperatures.

In the accumulation regime, an explicit temperature dependence can easily be observed. Also a series resistance effect is seen in the figure 3.5, after about 1 volts at all temperatures. In the inversion, however, a weaker dependence on temperature is seen in the figure above. To find out which current mechanisms are responsible for this kind of behavior, we plotted the Arrhenius plots for both positive and negative voltage regimes.

#### 3.3. Possible Current Transport Mechanisms:

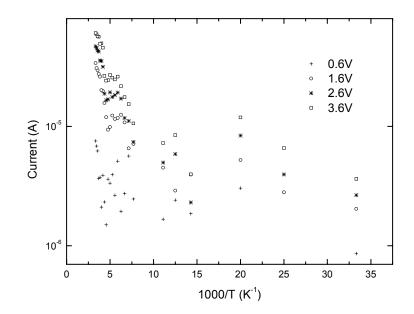

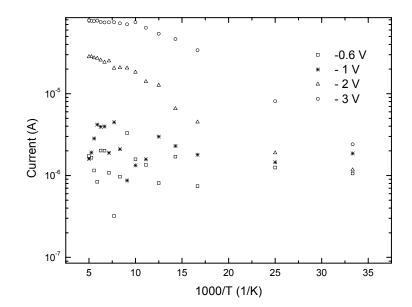

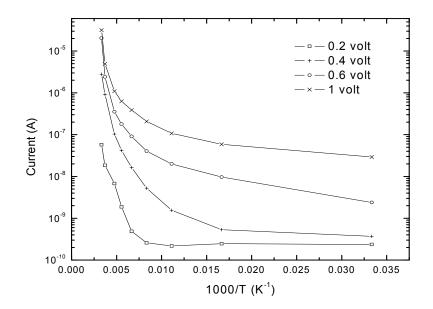

We observed mainly two different characteristics in the Arrhenius plots for accumulation. As seen in Fig. 3.6, there is a strong temperature dependence at high temperatures. We observe a field activated process at medium and low temperatures. The same observation can easily be done by studying the I-V curve, shown in Fig. 3.5. One can easily realize that the current does not change significantly with the temperature (100 K and 200 K). At higher temperatures, an explicit increase in current is observed as the temperature increases (250 K and 300 K). The dependence on temperature also shows differences at different fields.

Fig. 3.6 Arrhenius plot for accumulation

Fig. 3.7 Arrhenius plot for inversion

In the inversion regime, Arrhenius plot shows two different behaviors as a function of temperature and field, but in a different way than the Arrhenius plot for accumulation does. The temperature dependence is only seen at higher fields and at low fields we see a noisy data. At high fields, for example -3 V or -2 V, the current depends exponentially on temperature. The weak temperature dependence of the current at -1 V and temperature independence at lower fields suggest the existence of another mechanism.

As we presented in the first chapter, there are mainly four conduction mechanisms which are temperature dependent. These mechanisms are Schottky emission, band-to-band tunneling, Poole-Frenkel emission and ohmic conduction.

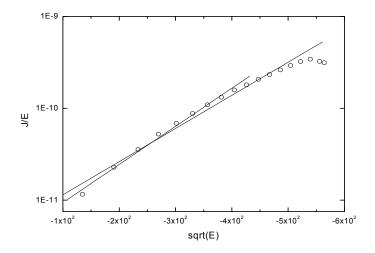

We plotted Poole-Frenkel curves at various temperatures and calculated the permittivity from those plots. We did this procedure for 270 K at first and then for all temperatures since we expect the Poole-Frenkel conduction to occur at higher temperatures: In the next section we will present the I-V and Poole-Frenkel plots [ln (J/E) vs.  $E^{1/2}$ ] for accumulation and inversion at 270 K.

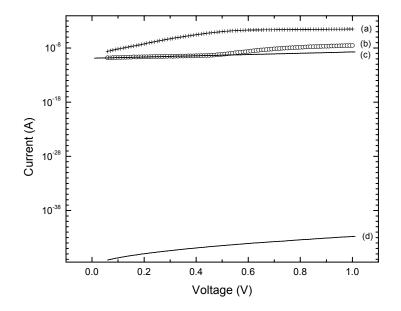

#### 3.3.1. Thermally Activated Current

Fig. 3.8 Current-Voltage characteristics at 270 K.

In the Fig. 3.5 and Fig. 3.8, we can see that series resistance affects the current-voltage characteristics of the device at voltages higher than approximately 1.5 V in accumulation regime. For this reason, we expect Poole-Frenkel curves to give good results below this threshold.

Fig. 3.9 Poole-Frenkel plot at 270 K for inversion.

In Fig. 3.9, Poole-Frenkel curve obtained from the experimental data at 270 K (circles) and two linear fits (black lines) to the curve are shown. Since the slope of Poole-Frenkel plot gives a function of temperature and permittivity, extracting the value of the permittivity from the slope is a simple algebraic procedure.

The Poole-Frenkel current density expression is given as:

$$J_{PF} = q n_0 \mu E \cdot \exp\left[-\frac{q}{kT}\left(\phi_t - \sqrt{\frac{qE}{\pi\varepsilon_i}}\right)\right]$$

(1.37)

And the slope of the Poole-Frenkel curve is:

$$slope = -\frac{q}{kT}\sqrt{\frac{q}{\pi\varepsilon_i}}$$

(3.1)

where q is the electron charge, k is Boltzmann constant, T is temperature and  $\varepsilon_i$  is the permittivity of the oxide.

One of the slopes (the upper one) in the Fig. 3.9 produced the permittivity as  $0.85 \varepsilon_0$  where  $\varepsilon_0$  is the vacuum permittivity. The permittivity was found as 9.8  $\varepsilon_0$  for the other fit to the slope. It is clear that a better fit, which might give a permittivity value close to the commonly accepted 3.9  $\varepsilon_0$  value, can be found by making a fit between these two lines. The trap depth changes between 0.69 eV and 0.75 eV with respect to these permittivity values.

These two results when they are considered with the discussion above lead to the conclusion that the transport mechanism of the device is dominated by the Poole-Frenkel conduction at 270 K for inversion. Actually one does not have to extract perfect permittivity values from Poole-Frenkel plots since oxides include a lot of deficiencies such as oxide traps, mobile ions, localizations in the matrix an so on. These imperfections cause permittivity deflect from  $3.9 \varepsilon_0$ . Therefore values found in the above analysis are good signs to assure us about the dominance of the Poole-Frenkel emission.

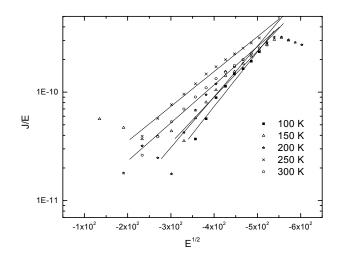

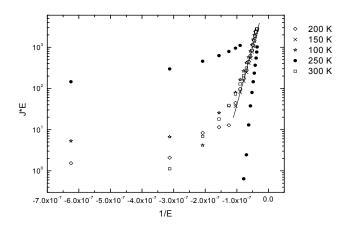

Therefore our conclusion for the conductivity in the device for inversion regime is Poole-Frenkel type trap assisted conduction. In order to be sure of this conclusion we plotted Poole-Frenkel curves at other temperatures. The results and the fits to the slopes of those curves are shown in figure 3.10 below:

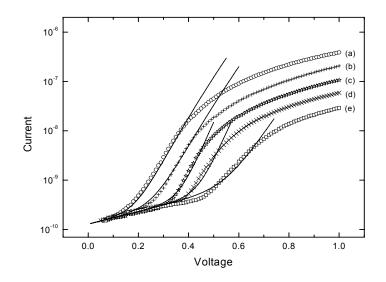

Fig. 3.10 Inversion regime Poole-Frenkel graphics at various temperatures.

The permittivity values extracted from these slopes are acceptable for high temperatures. For example at 300 K, the permittivity was found as 6.8  $\varepsilon_0$  and this value goes away from 3.9  $\varepsilon_0$  as the temperature decreases. This increase in permittivity values indicates that the second conduction mechanism, which was mentioned during the Arrhenius plot discussion above, becomes more effective at lower temperatures. The trap depths change from 0.56 eV to 0.60 eV. Trap depth decreases as the temperature increases. This is expected since as the temperature increases carriers will have more average energy and therefore they will be able to jump to higher trap states.

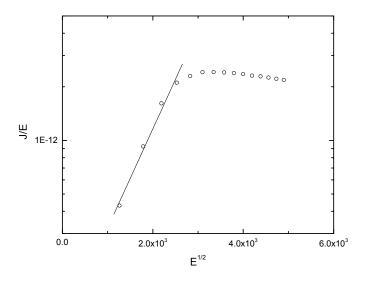

The Poole-Frenkel curve yielded a 6.49  $\varepsilon_0$  value for the accumulation regime. The Poole-Frenkel curve and the fit to the linear region of the curve are shown in Fig.3.11:

Fig. 3.11 Poole-Frenkel plot at 270 K for accumulation.

The permittivity value was found to be 6.49  $\varepsilon_0$  from the slope of the fit. This value is convincing enough to reach to the conclusion that Poole-Frenkel conduction governs the device at 270 K. The trap depth of 0.67 eV corresponds to 6.49  $\varepsilon_0$ .

The Poole-Frenkel plots for other temperatures are shown in Fig. 3.12 below. From the slopes of the fits seen in the figure 3.12, we extracted different permittivity values as  $5.5 \varepsilon_0$

for 300 K, 13.2  $\varepsilon_0$  for 200 K and 262.5  $\varepsilon_0$  for 100 K. It is seen that the permittivity values become less and less acceptable as the temperature decreases. This behavior again indicates the two-component conduction we described before. As the temperature decreases Poole-Frenkel conduction loses its dominance and the other mechanism starts to show up more. The trap depth for 250 K was found as 0.51 eV. The trap depth decreases as the temperature increases again. Unlike the inversion regime in which traps show minor differences in depth (0.56 eV to 0.60 eV), the trap depth changes more significantly in accumulation. It is 0.51 eV for 250 K and 0.67 eV for 270 K. This drastic change in accumulation is understandable since a change in the conduction mechanism occurs at these temperatures. Current becomes dominated by Poole-Frenkel emission rather than the field activation.

Fig. 3.12 Accumulation regime Poole-Frenkel graphics at various temperatures.

Up to now temperature dependent component of the total current has been discussed in detail and the field activated component was mentioned several times. We will discuss the

field activated constituent of the total device current in the next section.

#### 3.3.2. Field Activated Current:

There are different current models related to field activation. For example Fowler-Nordheim emission, direct tunneling, trap assisted tunneling, space-charge limited current, diffusion current, recombination generation current and surface state tunneling. However most of these models are not applicable to our device since it contains a relatively thick oxide about 1250 Angstroms. This oxide is very thick for substrate currents to limit the total current in the device. Such a thing only happens when all the carriers injected to substrate pass to the gate. And the device must be ready for new more carriers. It is obvious that our oxide is too thick by far for such a thing. Surface state tunneling and recombination-generation models do not work due to the same reason. It is also commonly accepted that direct tunneling occurs in 4-5 nm oxides and Fowler-Nordheim tunneling is not expected to be seen before 9-10 MV/cm fields. The field we applied is much less than this value. The most appropriate model seems to be trap assisted tunneling in this case. There are mainly two approaches to trap assisted tunneling: Numerical models and analytical solutions. The trap assisted tunneling is given as:

$$J_{TAT} = q \int_{0}^{t_{at}} \frac{C_{t} N_{t} P_{1} P_{2}}{P_{1} + P_{2}}$$

(1.31)

or

$$J_{TAT} = \int_{0}^{t_{ex}} \frac{qN_t}{\tau_c + \tau_e} dx$$

(1.31)

where  $t_{ox}$  is the oxide thickness,  $C_t$  is a slowly varying function of electron energy,  $N_t$  is the trap density,  $P_1$  and  $P_2$  are the electron tunneling probabilities and  $\tau_c$  and  $\tau_e$  are the caption and emission times of the traps.

One needs several physical quantities such as life times, trap depths or trap distributions to evaluate these integrals. However, these parameters can be found by other characterization methods than current-voltage analysis. This is however outside the scope of this thesis.

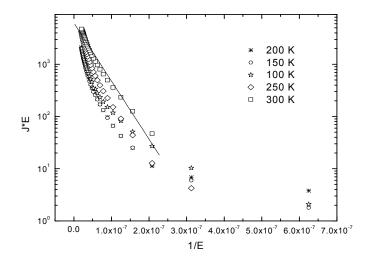

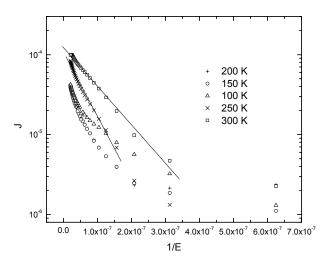

The analytical approaches have been developed to investigate the pure trap assisted conduction by using the I-V data by different researchers. There are mainly two methods by Fleisher-Lai and Chang et. al. [55, 65].

These two methods are very similar to each other although Chang's method is more generalized. Fleischer-Lai (4.5) and Chang (4.6) models are formulated as:

$$J_{TAT} = \frac{\frac{2qC_t N_t \phi_t}{3E} \cdot \exp(-\frac{A\phi^{3/2}}{E})}{3E}$$

(1.32)

$$J_{TAT} \propto \exp(-\frac{4\sqrt{2qm_{ox}}\phi^{3/2}}{3\hbar E})$$

(1.34)

where  $\Phi_t$  is the trap depth.

One has to plot ln (J•E) vs. 1/E in Fleischer-Lai model and ln J vs. 1/E in Chang's model. Both plots give a slope of  $(-A\Phi_t^{3/2})$  where A=4(2qm<sup>\*</sup>)<sup>1/2</sup>/3ħ.

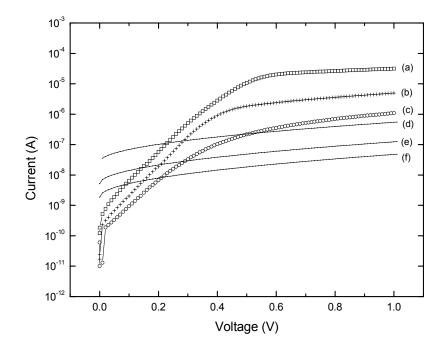

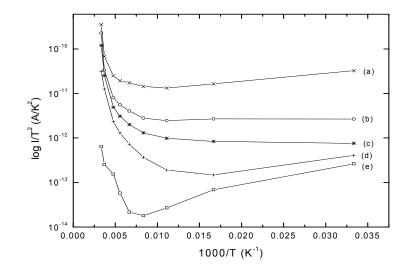

**Fig. 3.13** Fleischer-Lai trap assisted tunneling model plots for accumulation at various temperatures.

**Fig. 3.14** Chang trap assisted tunneling model plots for accumulation at various temperatures.

In Fig. 3.13, Fig. 3.14, Fig. 3.15 and 3.16, the current vs. electric field characteristics are plotted according to both models. The results by these models are very alike and comparable. Both models indicate that trap assisted tunneling exists in the device for both accumulation and inversion regimes.

The trap depths we extracted from the slopes of fit lines (black lines in the Fig. 3.13 and Fig. 3.14) show variations with respect to temperature.

**Fig. 3.15** Fleischer-Lai trap assisted tunneling model plots for inversion at various temperatures.

**Fig. 3.16** Chang trap assisted tunneling model plots for inversion at various temperatures.

These plots indicate that trap assisted tunneling occurs in the device at all temperatures. This actually is expected for a thick oxide since it contains different type of defects. As it was explained in sec.3.2.2, the oxide is too thick to let most of the transport mechanisms occur at low and medium fields. Trap assisted tunneling however can occur at these fields.

The trap depths were extracted as 0.23 eV (Chang's model) and 0.32 eV (Fleisher's model) for inversion, 0.1 - 0.21 eV (Chang) and 0.17 - 0.26 eV (Fleischer) for accumulation.

### **3.4. Conclusion:**

A more detailed analysis of the TAT plots presented above indicates that in the inversion regime, trap assisted tunneling current density doesn't change so much and the trap depths are almost the same at different temperatures. We found trap depths as 0.23 eV for 300 K and 0.26 eV for 50 K with respect to Chang's model and 0.32 eV for almost all temperatures with respect to Fleischer-Lai model. When

we combine these results and the conclusion which we reached for thermally activated current, we realize that the trap assisted current and Poole-Frenkel current are competing with each other to dominate the total device current for inversion regime at all the temperatures and the total current is the sum of these two components. The total current increases with the temperature due to the increase in Poole-Frenkel current with temperature. This increase is more significant at higher voltages since Poole-Frenkel emission is not a function of only temperature but also field. Therefore our conclusion for inversion regime current is that the current is divided into two components as base and active components. Base component is the pure trap assisted current occuring due to the traps in the oxide. These traps behave as centers for conduction in the oxide. Carriers jump into the trap by field activation and they leave the trap for the substrate when they are excited. The excitation might be due to field activation or collision with a free carrier in the SiO<sub>2</sub> or etc. The other component which we call active one is the Poole-Frenkel emission and we conclude that Poole-Frenkel emission is the main constituent of the total current since the Poole-Frenkel curves give acceptable permittivity values at all the temperatures. The trap assisted tunneling mechanism participates in the total current with Poole-Frenkel emission but it never becomes the dominant contributor.

The situation in the accumulation regime is similar to the situation in the inversion case with minor differences. In accumulation, the current is constituted by two different mechanisms again but this time both of these mechanisms become dominant at different temperatures. At higher temperatures the Poole-Frenkel emission becomes the first mechanism with a contribution of trap assisted tunneling to total current. Poole-Frenkel emission fades out at lower temperatures and trap assisted tunneling becomes more effective in determination of device characteristics.