# A NOVEL APPROACH FOR SYNTHESISING SINUS WAVEFORMS AT POWER LEVEL

# A THESIS SUBMITTED TO THE GRADUATE SCHOOL OF NATURAL AND APPLIED SCIENCES OF THE MIDDLE EAST TECHNICAL UNIVERSITY

BY

#### SERKAN PAKİ ŞEDELE

# IN PARTIAL FULFILMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE

IN

THE DEPARTMENT OF ELECTRICAL AND ELECTRONICS ENGINEERING

JANUARY 2004

Approval of the Graduate School of Natural and Applied Sciences

Prof.Dr. Canan ÖZGEN Director

I certify that this thesis satisfies all the requirements as a thesis for the degree of Master of Science.

Prof.Dr. Mübeccel DEMİREKLER Head of Department

This is to certify that we have read this thesis and that in our opinion it is fully adequate, in scope and quality, as a thesis for the degree of Master of Science.

Prof.Dr. H.Bülent ERTAN Supervisor

**Examining Committee Members**

Prof. Dr. Muammer ERMİŞ (chairman)

Prof. Dr. H.Bülent ERTAN

Prof. Dr. Aydın ERSAK

Assist Prof. Dr. M. Timur AYDEMİR

Assist Prof. Dr. Ahmet M. HAVA

#### ABSTRACT

# A NOVEL APPROACH FOR SYNTHESISING SINUS WAVEFORMS AT POWER LEVEL

ŞEDELE, Serkan Paki M.Sc., Department of Electrical and Electronics Engineering Supervisor: Prof. Dr. H. Bülent ERTAN

January 2004, 142 pages

In variable speed motor drive and uninterruptible power supply (UPS) applications, taditional method is to employ some kind of a modulation technique at a high frequency typically 6 kHz to 20 kHz range. In these modulation techniques, the switches are hard switched. The result is application of a series of pulses to the load, and if the load is inductive, sine wave current flows into the load. Hard and rapid switching causes a voltage waveform with a very high dv/dt (rate of change in voltage) causing high EMI problems, reduced life expectancy of the motor and additional losses. So a power supply generating pure sinusoidal voltage waveform is very desirable. In industry some low pass filters called sinusoidal filters, are used at the output of the inverters but this comes with additional cost and bulky filter elements.

In this study, a novel approach for generating power level sinusoidal waveforms is proposed. The basic structure is a DC-DC converter that produces a

rectified DC-link at its output and an H-bridge inverter that inverts the rectified sinusoids to form a sinusoidal voltage. Main advantages of the circuit are that the H-bridge inverter switches have no switching stresses, they are switched at low frequency so the reliability is increased.

Throughout the study different circuit topologies have been investigated and the analysis of the chosen topologies is supported with computer simulations. The system is then set up in the laboratory. In order to prove of the concept, only a single phase inverter has been investigated at steady state conditions. Efficiency, distortion level, magnitude error and device stresses have been obtained. The results indicate that the proposed configuration is very promising.

Keywords: Pure Sinusoidal voltage waveform, complementary switching DC-DC buck converter, rectified DC-link.

### ÖΖ

# GÜÇ SEVİYESİNDEKİ SİNÜS DALGA ŞEKİLLERİNİN SENTEZLENMESİNDE YENİ BİR YAKLAŞIM

ŞEDELE, Serkan Paki Yüksek Lisans, Elektrik Elektronik Mühendisliği Bölümü Tez Danışmanı: Prof. Dr. H. Bülent ERTAN

Ocak 2004, 142 sayfa

Değişken hızlı motor sürücüleri ve kesintisiz güç kaynakları, kısaca "yüksek frekanslı eviriciler", çıkış gerilimini oluşturmak için hızlı anahtarlama yapabilen transistörler (genellikle FET veya IGBT) kullanırlar. Bu anahtarlar çok ani açılıp kapanırlar ve bu işlem açık ve kapalı olmak üzere iki durumdan oluşur ve ara durumlar içermez. Bunun sonucu olarak bir dizi darbeden meydana gelen bir gerilim oluşur ve de eğer yük endüktif ise motora sinüs dalga şekilli bir akım akar. Voltaj geçişleri çok anidir. Bu ani anahtarlamalar çok yüksek dv/dt (gerilimdeki değişim oranı) ye sahip olan bir gerilim dalga şekli meydana getirir ki bu da yüksek elektromagnetik kirlilik, motor ömründe azalma ve ekstra kayıplara neden olur. Bunlardan kurtulmak için motor sürücüleri ve güç kaynaklarının çıkışlarında saf sinüs bir gerilim elde etmek gerekir.

Bu çalışmada sinüzoidal dalga şekilleri üretmek için yeni bir yaklaşım ortaya atıldı. çıkışı saf sinüzoidal dalga şekilleri olan ve böylece yüksek frekanslı elemanları

ve dv/dt problemlerini ortadan kaldıran bir üreteç fikri ortaya atıldı. Önerilen devre topolojisi iki bölümden oluşmaktadır. Giriş bölümü doğrultulmuş sinüs dalga şekilleri üretmekte, çıkış ise bunları evirip sinüsoidal bir dalga şekli üretmektedir. Bu tez çalışmasında değişik devre topolojileri araştırıldı ve seçilen topolojinin detaylı dizyn prosedürü ve bilgisayar simülasyonu sunuldu. Ayrıca sistem labaratuvarda kurularak çalıştırıldı ve teorik çalışmaların sonuçları deneylerle doğrulandı.

Anahtar Kelimeler: Saf sinüs dalga şekli, tamamlayıcı anhtarlayan DC-DC çevirici, Doğrultulmuş Doğru Akım Barası.

To My Family...

#### ACKNOWLEDGEMENTS

I express sincere appreciation to my thesis supervisor Prof. Dr. H. Bülent Ertan for his guidance throughout all stages of this study, which made it possible.

I would like to express my special thanks to Asst. Prof. M. Timur Aydemir and Asst. Prof Ahmet M. Hava for their precious suggestions and for their continuous encouragements during my studies.

I wish to thank to my roommates and my dear friends Cüneyt Karacan and Tolga İnan for their deep understanding, suggestions and supports.

I also wish to thank Çağlar Hakkı Özyurt, Akın Acar, Erdal Bizkevelci, and all Tübitak-Bilten Intelligent Energy Conversion Group staff for their support. My special thanks also goes to Gökçen Baş for her deep support and possitivity.

Finally I thank to my father, mother, brother and grandmother for their precious support and help against all difficulties.

# TABLE OF CONTENTS

| ABSTRACT          | .iii  |

|-------------------|-------|

| ÖZ                | .v    |

| ACKNOWLEDGMENTS   | .vii  |

| TABLE OF CONTENTS | ix    |

| LIST OF TABLES    | .xiii |

| LIST OF FIGURES   | xiv   |

| LIST OF SYMBOLSx  | viii  |

# CHAPTER

| 1 | INTRODUCTION                                             | . 1  |

|---|----------------------------------------------------------|------|

| 2 | THEORETICAL STUDY                                        | .6   |

|   | 2.1 General Overview of the Proposed System              | . 6  |

|   | 2.2 Output Stage (Inverter Stage)                        | 6    |

|   | 2.3 Input Stage                                          | 7    |

|   | 2.3.1 Determination of Suitable Topology for Input Stage | . 7  |

|   | 2.3.2 DC-DC Converter Basics                             | 8    |

|   | 2.3.3 Step Down (Buck) Converter                         | .9   |

|   | 2.3.3.1 Continuous Conduction Mode                       | 10   |

|   | 2.3.3.1.1 Mode 1: switch is on                           | 10   |

|   | 2.3.3.1.2 Mode 1: switch is off                          | 11   |

|   | 2.3.3.1.3 Steady-State Analysis and Volt-Second Balan    | ce   |

|   | on Inductor                                              | .12  |

|   | 2.3.3.1.4 Output Voltage Ripple of Buck Converter for    |      |

|   | Continuous Conduction Mode (Approximate                  |      |

|   | Analysis)                                                | . 13 |

|   | 2.3.3.2 Boundary between Continuous and Discontin                           | uous  |

|---|-----------------------------------------------------------------------------|-------|

|   | Conduction Modes                                                            | 15    |

|   | 2.3.3.3 Discontinuous Conduction Mode                                       | 17    |

|   | 2.3.3.1 Subinterval 1: switch is on                                         | 18    |

|   | 2.3.3.2 Subinterval 2: switch is off                                        | 18    |

|   | 2.3.3.3 Subinterval 3: switch is off and inductor cu                        | rrent |

|   | is 0                                                                        | 18    |

|   | 2.3.3.4 Steady-State Analysis and Volt-Second Bala                          | nce   |

|   | on Inductor                                                                 | 19    |

|   | 2.3.3.3.5 Output Voltage Ripple of the Buck Conv                            | erter |

|   | Operating in Discontinuous Conduc                                           | ction |

|   | Mode                                                                        | 20    |

|   | 2.4 Combination of Input and Output Stages                                  | . 23  |

|   | 2.4.1 Analysis of the Basic Topology In Terms of Operation                  | ating |

|   | Conditions                                                                  | . 24  |

|   | 2.4.2 Analysis of the Basic Topology In Terms of Load Types                 | 27    |

|   | 2.4.2.1 Feed Forward Control                                                | 28    |

|   | 2.4.2.2 Closed Loop Control                                                 | 32    |

|   | 2.4.2.2.1 Determination of the Control Circuit Param                        | eters |

|   | Used for Closed loop Operation                                              | 32    |

|   | 2.4.3 Modified Circuit Topology                                             | 39    |

|   |                                                                             |       |

| 3 | DETERMINATION OF THE DC-DC CONVERTER PARAMETERS                             | 43    |

|   | 3.1 Introduction                                                            | 43    |

|   | 3.2 Inductance Design                                                       | 44    |

|   | 3.2.1 Inductance Design Software                                            | 46    |

|   | 3.2.2 Calculation of $L_{max}$ , Possible With the Selected Core and Specif | ying  |

|   | the Inductance Value                                                        | 50    |

|   | 3.2.3 Calculation of Winding Loss                                           | . 52  |

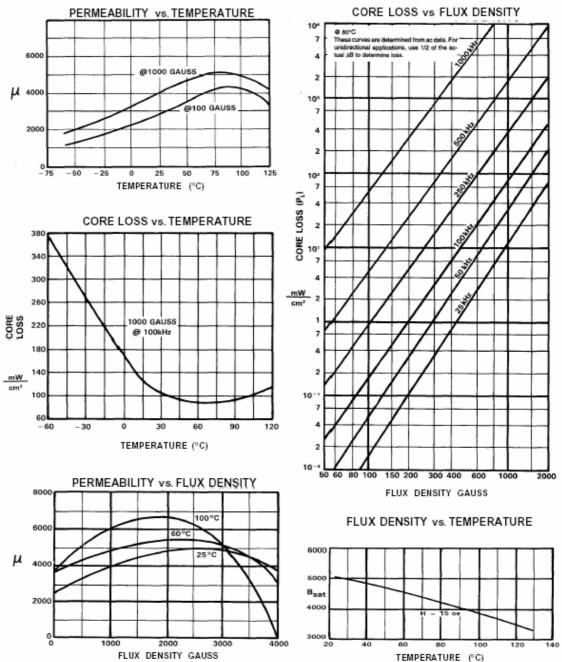

|   | 3.2.4 Calculation of Core Loss                                              | . 52  |

|   | 3.2.5 Thermal Analysis                                                      | . 53  |

|   | 3.2.5.1 Thermal Resistance Due to Radiative Heat Transfer                   | . 54  |

|   | 3.2.5.2 Thermal Resistance Due To Convective Heat Transfer.         | 55   |

|---|---------------------------------------------------------------------|------|

|   | 3.2.5.3 Temperature Rise in the Inductor                            | 56   |

|   | 3.2.6 Specifying the Air gap Length                                 | 57   |

|   | 3.3. Determination of the Capacitance (Value and type)              | .60  |

| 4 | HARDWARE AND SOFTWARE IMPLEMENTATION                                | . 62 |

|   | 4.1 Introduction                                                    | .62  |

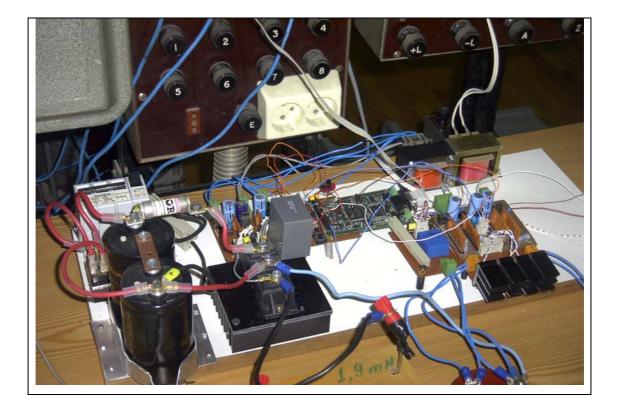

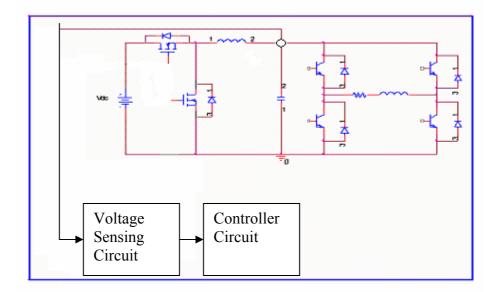

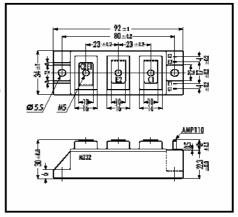

|   | 4.2 Hardware                                                        | .68  |

|   | 4.2.1 Power Stage of the Circuit                                    | . 69 |

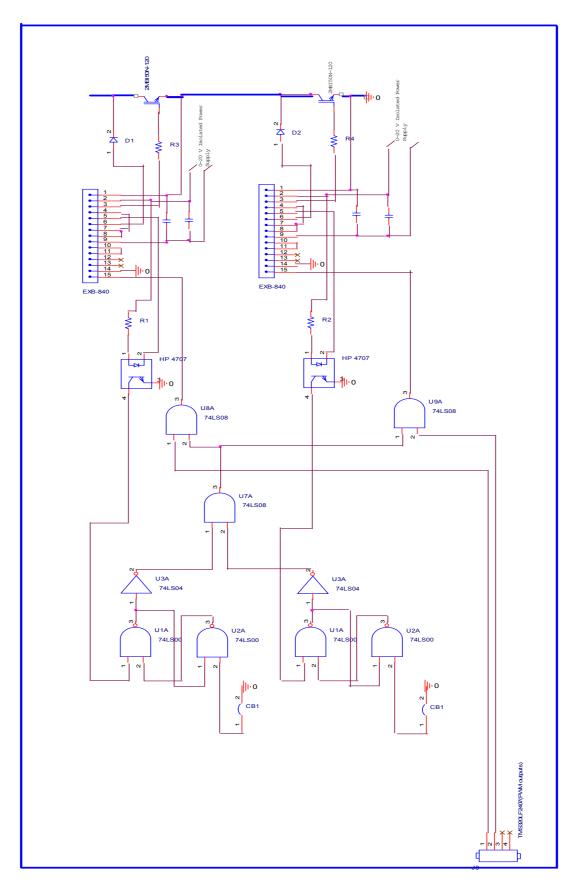

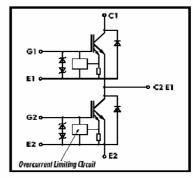

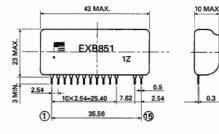

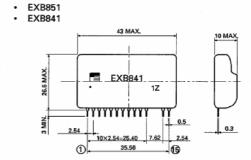

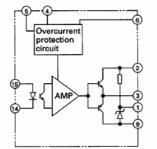

|   | 4.2.2 Gate Driver and Protection Circuits                           | .71  |

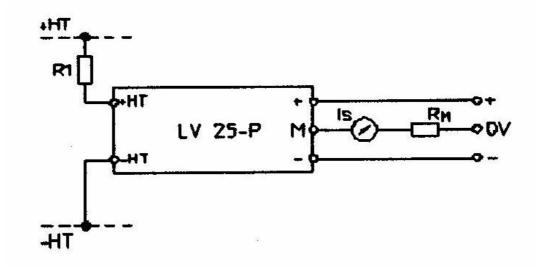

|   | 4.2.3 Voltage Sensing Circuit                                       | 74   |

|   | 4.2.4 The Controller                                                | 75   |

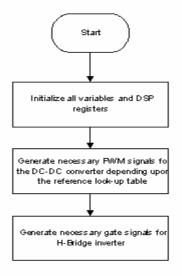

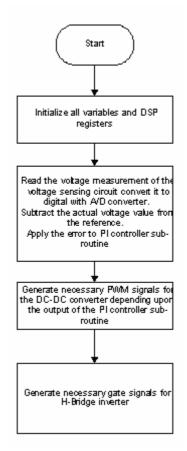

|   | 4.3 Software                                                        | . 77 |

|   | 4.4 Experimental Study and Verification of Theoretical Calculations | . 78 |

|   | 4.4.1 Experimental Results of Feed Forward Control Operation        | . 79 |

|   | 4.4.1.1 Experimental Results for No-Load Operation                  | . 80 |

|   | 4.4.1.2 Experimental Results for Full load Operation                | . 81 |

|   | 4.4.2 Experimental Results of Closed Loop Control Operation         | . 83 |

|   | 4.4.2.1 Experimental Results for No-Load Operation                  | . 84 |

|   | 4.4.2.2 Experimental Results for Full load Operation                | . 85 |

|   | 4.4.3 Determination of the Level of the Minimum Achievable Voltage  | . 88 |

|   | 4.4.4 The Effect of Power Factor on Inverter Operation              | 89   |

|   | 4.4.5 Stresses on the Semiconductor Switch                          | .92  |

|   | 4.4.6 Inductor Losses at 15000 Hz                                   | 94   |

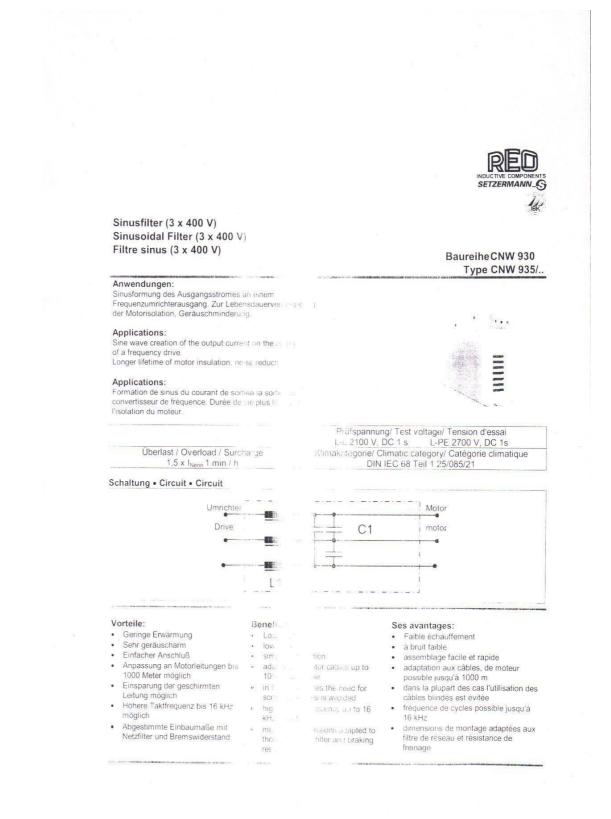

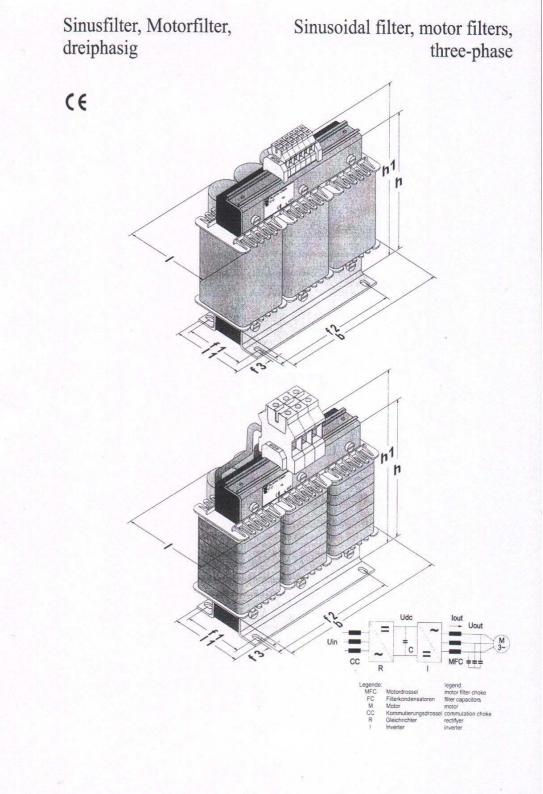

|   | 4.4.7 Sinusoidal Power Filters in the Market                        | . 96 |

|   | 4.4.8 Conclusions                                                   | .96  |

| 5 | CONCLUSION                                                          | 98   |

|   | 5.1 General                                                         | . 98 |

|   | 5.2 Experimental Results                                            | 100  |

|   | 5.3 Conclusion and Future Work                                      | 101  |

| REFERENCES | 103 |

|------------|-----|

|------------|-----|

# APPENDIX A. DATA SHEETS OF THE COMPONENTS AND FULL PROGRAM С

| CODES | 105 |

|-------|-----|

|       |     |

| A.1 Flow Charts and Source Codes Written in C language106        |

|------------------------------------------------------------------|

| A.2 Source Code of The Inductor Design Software114               |

| A.3 Data Sheets of the Components                                |

| A.4 Simulation model                                             |

| A.5 Determination of Suitable Topology for the Output Stage 128  |

| A.5.1 Full Controlled Bridge Inverters                           |

| A.5.1.1 Topology One of the Full Controlled Bridge Inverter. 129 |

| A.5.1.2 Topology Two of the Full Controlled Bridge Inverter129   |

| A.5.1.3 Topology Three of the Full Controlled Bridge Inverter130 |

| A.5.1.4 Topology Four of the Full Controlled Bridge Inverter131  |

| A.5.1.5 Topology Five of the Full Controlled Bridge Inverter134  |

| A.6 Sinusoidal Filters Available in the Market                   |

### LIST OF TABLES

# TABLE

| 3.1 Properties of Ferrite E shaped cores for medium power applications | . 44 |

|------------------------------------------------------------------------|------|

| 3.2 Coefficients applied to core loss formula                          | . 52 |

| 4.1 Performance Analysis for Feed Forward Control Operation            | 83   |

| 4.2 Performance Analysis for Closed Control Operation                  | . 87 |

| 4.3 Performance Analysis at different Load power factor values         | . 92 |

| 4.4 Expected and Measured Efficiency Values for Closed Loop Control    |      |

| Operation                                                              | 95   |

| 4.5 Physical Dimensions of the filter Inductors                        | .96  |

### LIST OF FIGURES

#### FIGURES

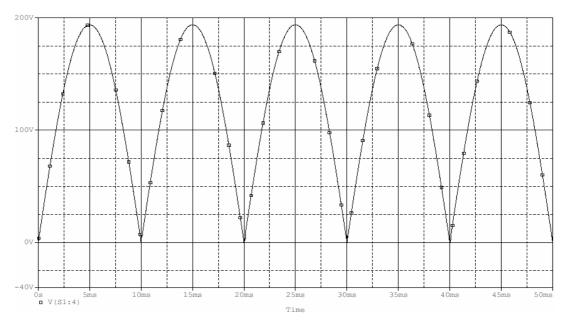

| 1.1 Full-rectified sinusoids                                              | 4     |

|---------------------------------------------------------------------------|-------|

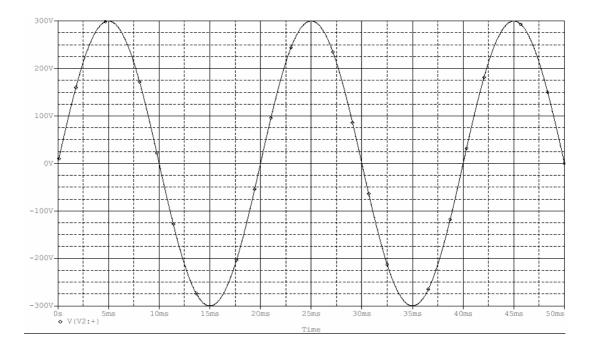

| 1.2 Sinusoidal waveform inverted from full-rectified sinusoids            | 5     |

| 2.1 Full controlled H-Bridge inverter with back diodes (output stage)     | . 7   |

| 2.2 Output of the input stage                                             | 7     |

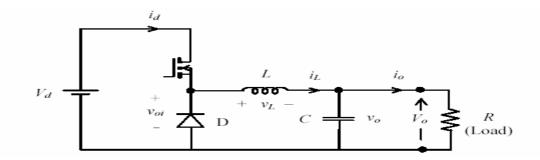

| 2.3 Step Down (Buck) converter.                                           | 9     |

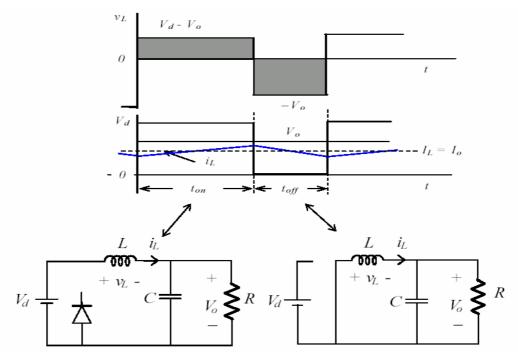

| 2.4 Buck converter waveforms and circuit states                           | 10    |

| 2.5 Equivalent circuit for switch is on                                   | . 10  |

| 2.6 Equivalent circuit for switch is off                                  | . 11  |

| 2.7 Inductor voltage                                                      | . 13  |

| 2.8 Actual Output Voltage Waveform of a Buck Converter                    | 13    |

| 2.9 inductor current ripple(stored charge)                                | 14    |

| 2.10 Inductor voltage and current waveforms at the boundary of continuous | s and |

| discontinuous conduction                                                  | 15    |

| 2.11 Converter characteristics with duty-cycle and load                   | 16    |

| 2.12 vL and iL waveforms with discontinuous conduction                    | 17    |

| 2.13 Switch is on (discontinuous conduction)                              | 18    |

| 2.14 Switch is off (discontinuous conduction)                             | 18    |

| 2.15 Switch is off, Inductor current is 0 (discontinuous conduction)      | 18    |

| 2.16 Converter characteristics with discontinuous conduction              | 20    |

| 2.17 Capacitor current waveform (stored charge)                           | 20    |

| 2.18 Inductance current waveform for discontinuous conduction mode        | 21    |

| 2.19 Basic circuit diagram of the overall system                          | 24    |

| 2.20 Circuit diagram for open loop analysis                               | 28    |

| 2.21 Output voltage for full resistive load with open loop control        | 29    |

| 2.22 Harmonic Spectrum of the output voltage (open loop control, resistive     |

|--------------------------------------------------------------------------------|

| load)                                                                          |

| 2.23 Output voltage for inductive load with open loop control                  |

| 2.24 Harmonic spectrum of the output voltage (open loop control, inductive     |

| load)                                                                          |

| 2.25 Buck converter inductor current for inductive load (open loop)            |

| 2.26 Buck converter inductor current for inductive load (open loop,            |

| magnified)                                                                     |

| 2.27 Circuit diagram for closed loop analysis                                  |

| 2.28 Type 2 compensated error amplifier (PI Controller)                        |

| 2.29 Frequency response of the uncompensated system                            |

| 2.30 Output voltage for full resistive load with closed loop control           |

| 2.31 Harmonic Spectrum of the output voltage (closed loop control, resistive   |

| load)                                                                          |

| 2.32 Output voltage for inductive load with closed loop control                |

| 2.33 Output current for inductive load with closed loop control                |

| 2.34 Harmonic Spectrum of the output voltage and current (closed loop          |

| control, inductive load)                                                       |

| 2.35 Output voltage and gate signal of the buck converter                      |

| 2.36 Modified Circuit Topology                                                 |

| 2.37 Output voltage and load current for inductive load with closed loop       |

| control                                                                        |

| 2.38 Harmonic Spectrum of output voltage and load current for inductive load   |

| with closed loop control                                                       |

| 2.39 Inductance current (modified topology))                                   |

| 2.40 Inductance current (magnified version of Fig.2.60) (modified topology).42 |

| 3.1 Conventional Buck Converter                                                |

|                                                                                |

| 3.2 Complementary Switching Buck Converter                                     |

| 3.2 Complementary Switching Buck Converter                                     |

|                                                                                |

| 3.3 Inductor current over one period47                                         |

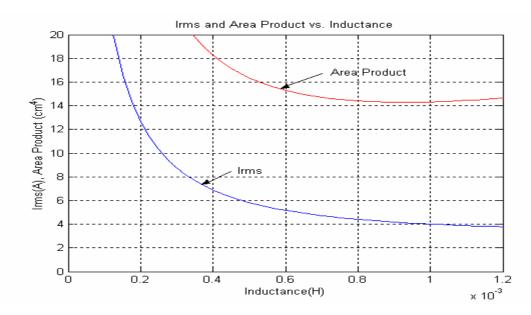

| 3.7 Area Product and I <sub>rms</sub> versus Inductance                | 50         |

|------------------------------------------------------------------------|------------|

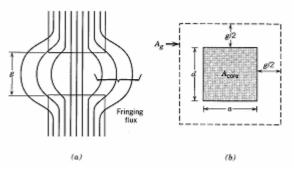

| 3.8 Fringing fields in the air-gap of an inductor (a), effective cross | -sectional |

| area of the gap (b)                                                    | 57         |

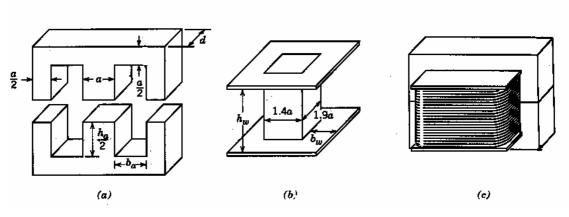

| 3.9 Double E-core, its bobbin and an assembled inductor                | 58         |

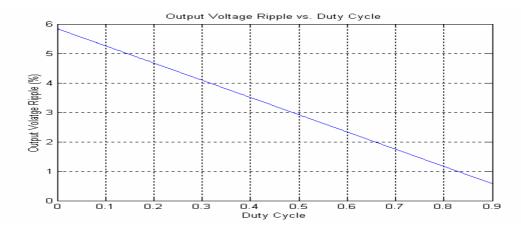

| 3.10 Capacitance vs. Duty cycle for $\Delta V_o = 7V$                  | 61         |

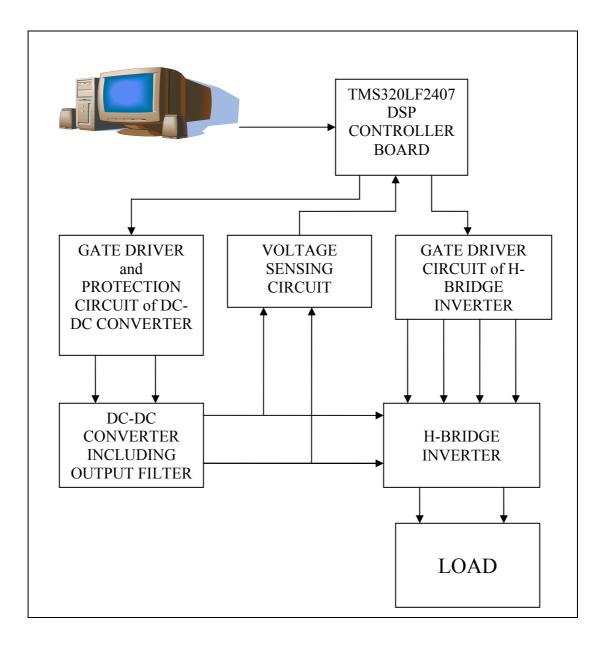

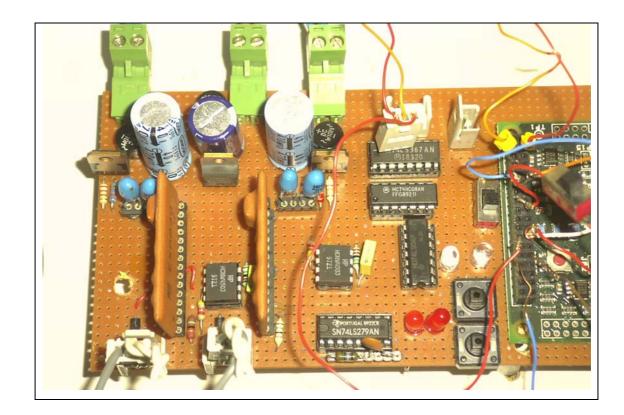

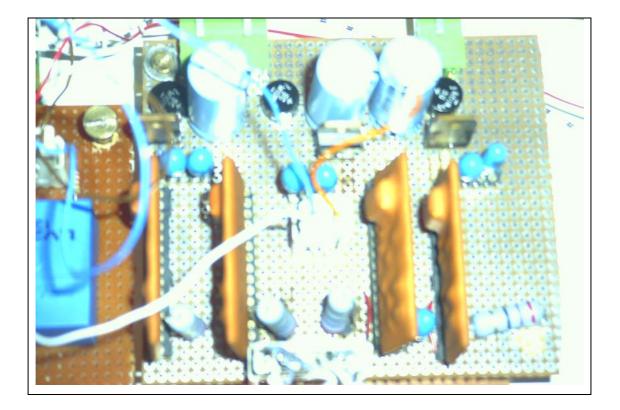

| 4.1 Block diagram of the hardware setup                                | 63         |

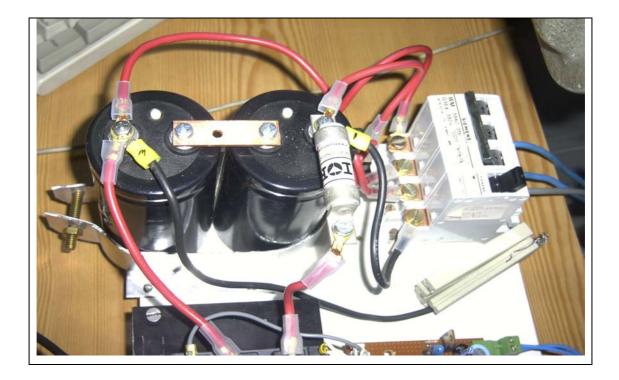

| 4.2 Input DC link and Filter Capacitors                                | 64         |

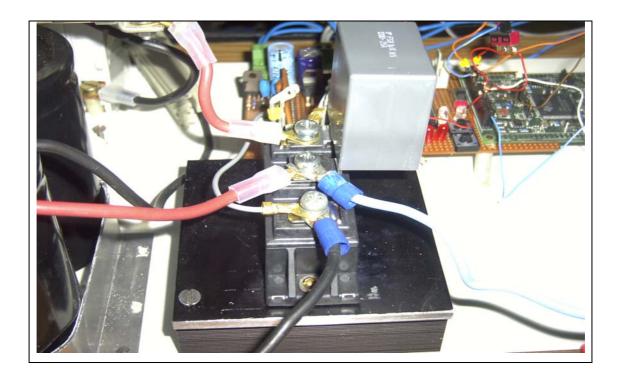

| 4.3.DC-DC Converter Power Stage (2MBI50N120 IGBT and                   | Snubber    |

| Capacitance)                                                           | 64         |

| 4.4 Output Inverter Power Stage (IRF 740 Mosfets)                      |            |

| 4.5 DC-DC Converter IGBT Gate Drivers and Protection Circuit           | 65         |

| 4.6 Output Inverter Mosfet Gate Driver Circuit                         | 66         |

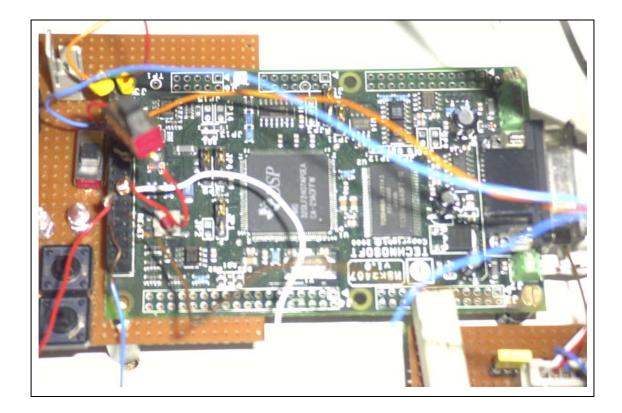

| 4.7 Voltage Sensing Circuit                                            |            |

| 4.8 TMS320LF2407A DSP Controller Circuit                               | 67         |

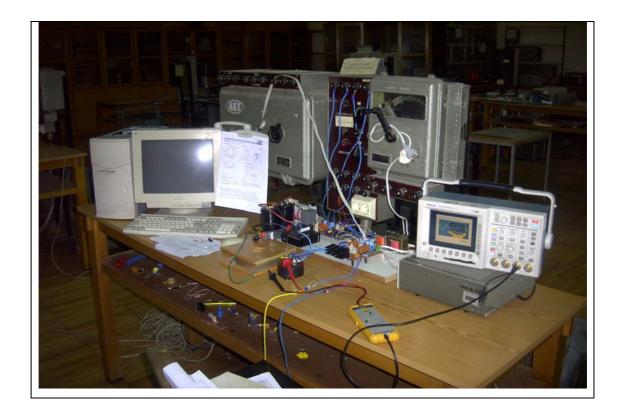

| 4.9 Experiment Setup                                                   | 67         |

| 4.10 Experiment Setup.                                                 | 68         |

| 4.11 Power Stage of the Circuit                                        |            |

| 4.12 Circuit schematic of the protection and gate driver circuit       | 73         |

| 4.13 Connection of the Voltage Sensing Circuit                         |            |

| 4.14 Schematic of the voltage Sensing Circuit                          |            |

| 4.15 Basic flow-chart of the software for feed-forward control         | 77         |

| 4.16 Basic flow-chart of the software for closed loop control          | 78         |

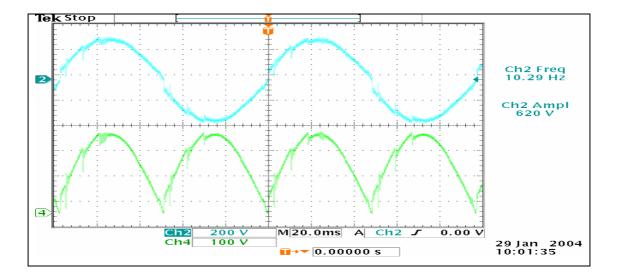

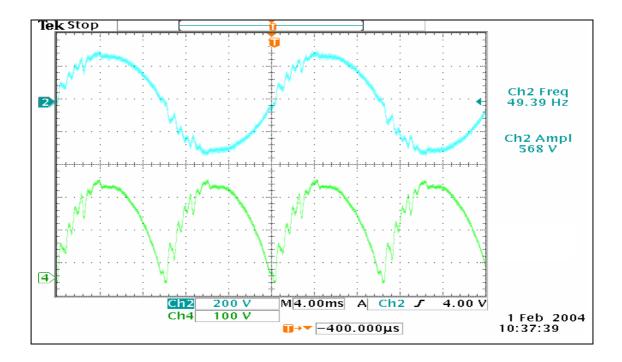

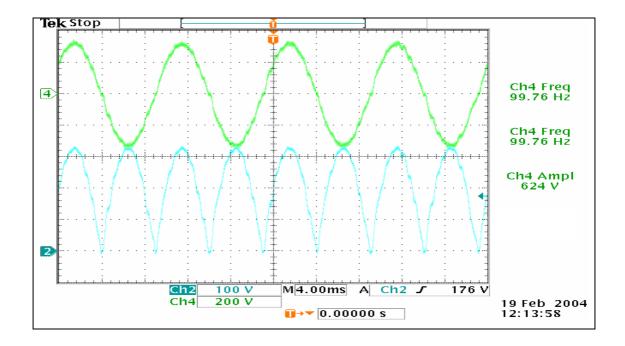

| 4.17 Rectified DC-link (upper waveform) and load voltages (lower w     | vaveform)  |

| at 10 Hz                                                               | 80         |

| 4.18 Rectified DC-link (upper waveform) and load voltages (lower w     | vaveform)  |

| at 50 Hz                                                               | 80         |

| 4.19 Rectified DC-link (upper waveform) and load voltages (lower w     | vaveform)  |

| at 100 Hz                                                              | 81         |

| 4.20 Rectified DC-link (upper waveform) and load voltages (lower w     | vaveform)  |

| at 10 Hz                                                               | 81         |

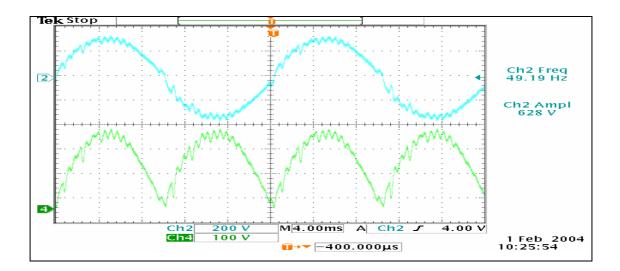

| 4.21 Rectified DC-link (upper waveform) and load voltages (lower w     | vaveform)  |

| at 50 Hz                                                               | 82         |

| 4.22 Rectified DC-link (upper waveform) and load voltages (lower waveform)   |

|------------------------------------------------------------------------------|

| at 100 Hz                                                                    |

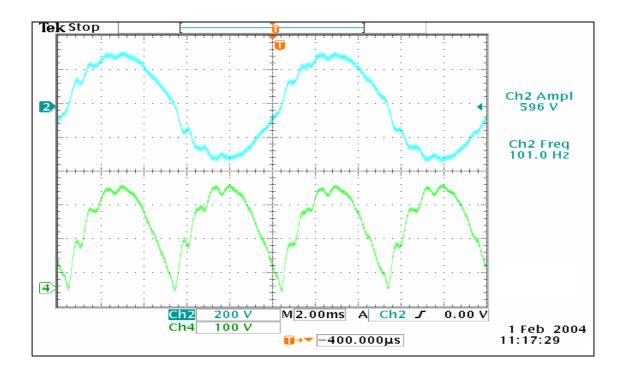

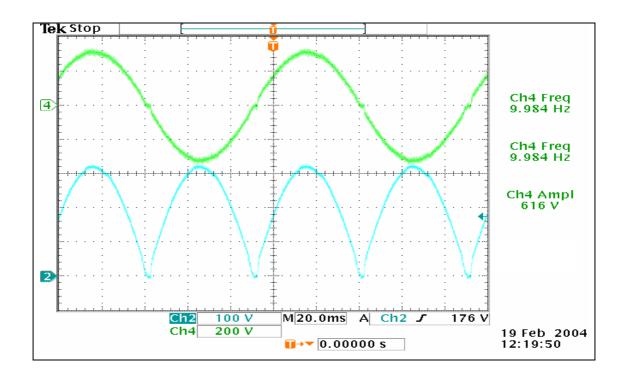

| 4.23 Rectified DC-link (upper waveform) and load voltages (lower waveform)   |

| at 10 Hz                                                                     |

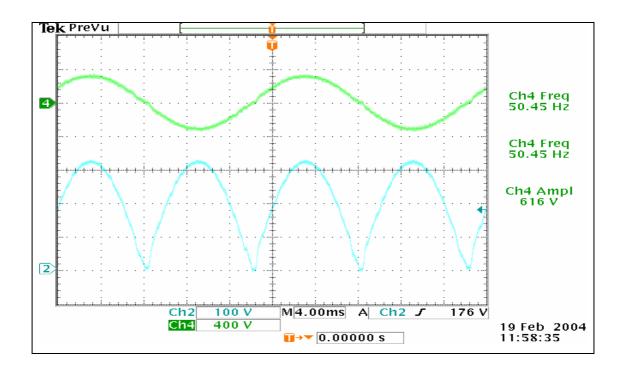

| 4.24 Rectified DC-link (upper waveform) and load voltages (lower waveform)   |

| at 50 Hz                                                                     |

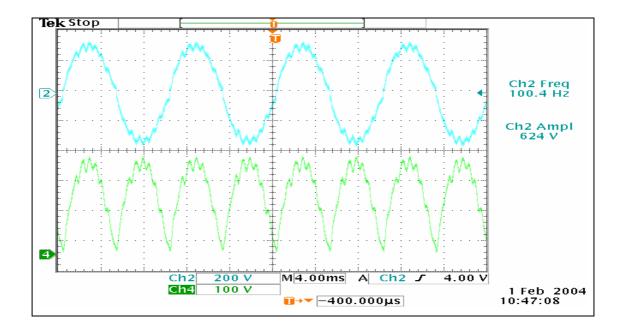

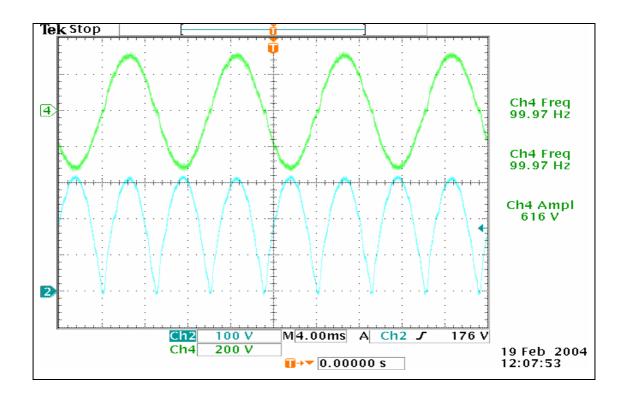

| 4.25 Rectified DC-link (upper waveform) and load voltages (lower waveform)   |

| at 100 Hz                                                                    |

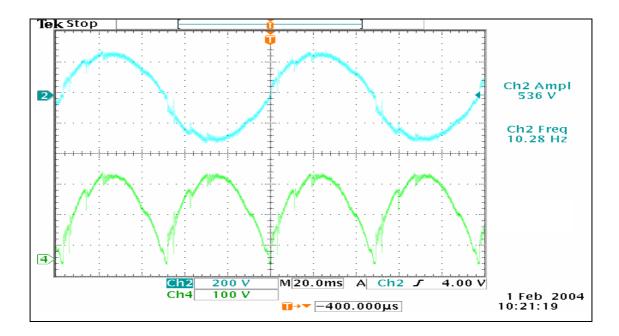

| 4.26 Rectified DC-link (upper waveform) and load voltages (lower waveform)   |

| at 10 Hz 85                                                                  |

| 4.27 Rectified DC-link (upper waveform) and load voltages (lower waveform)   |

| at 50 Hz                                                                     |

| 4.28 Rectified DC-link (upper waveform) and load voltages (lower waveform)   |

| at 100 Hz                                                                    |

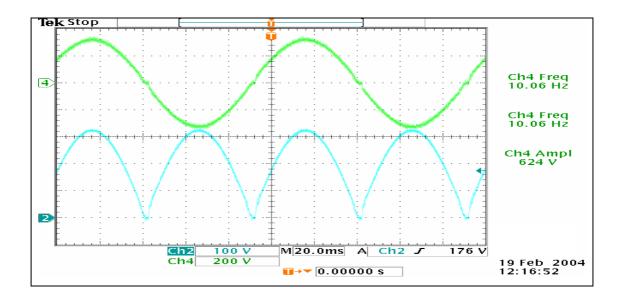

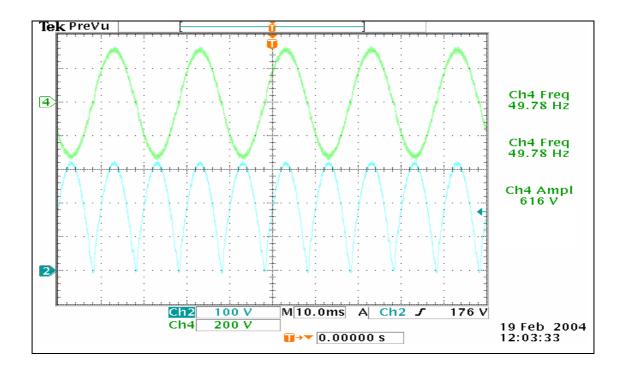

| 4.29 Input DC-Link capacitor current                                         |

| 4.30 Constant V/f operation for 5 Hz. Upper waveform is load voltage and the |

| lower one is rectified DC-link voltage                                       |

| 4.31 Constant V/f operation for 10 Hz.Upper waveform is load voltage and the |

| lower one is rectified DC-link voltage                                       |

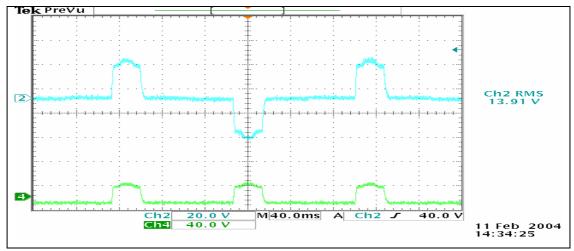

| 4.32 Load Voltage and current at 1 kVA with $pf = 0$                         |

| 4.33 Load Voltage and current at 1 kVA with $pf = 0$                         |

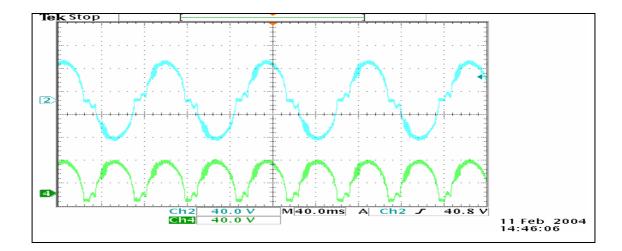

| 4.34 Load Voltage and current at 1 kVA with $pf = 0.8$                       |

| 4.35 Load Voltage and current at 1 kVA with pf = 1                           |

| 4.36 Voltage and Current on the DC-DC converter IGBT92                       |

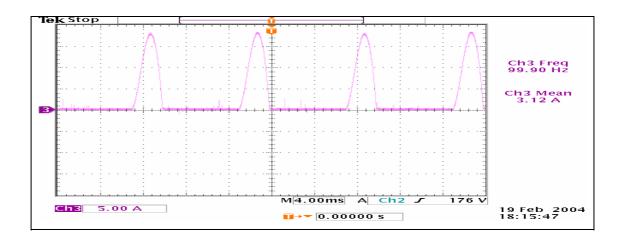

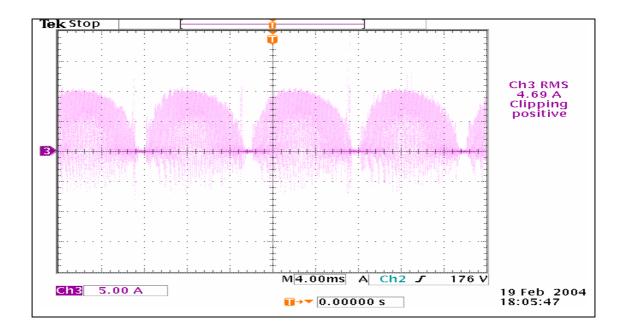

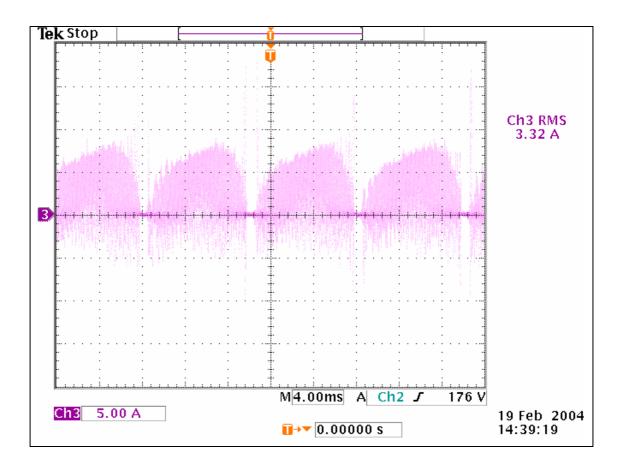

| 4.37 IGBT Current for full load (1 kVA) at pf = 193                          |

| 4.38 IGBT Current for full load (1 kVA) at pf = 0.893                        |

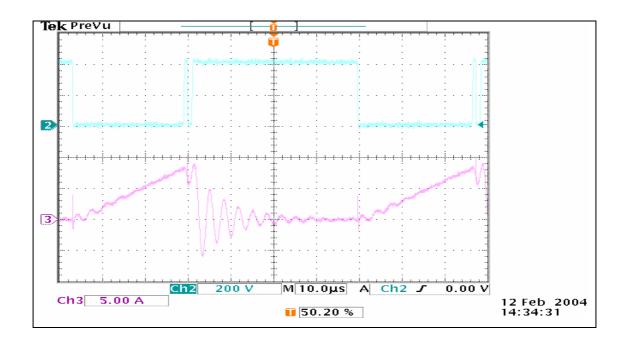

| 4.39 Turn on and turn off characteristics of the DC-DC converter             |

| IGBT                                                                         |

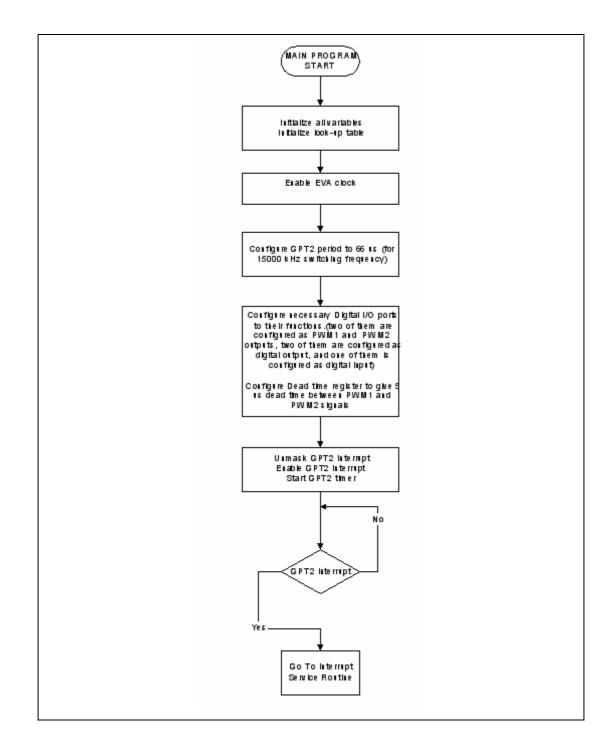

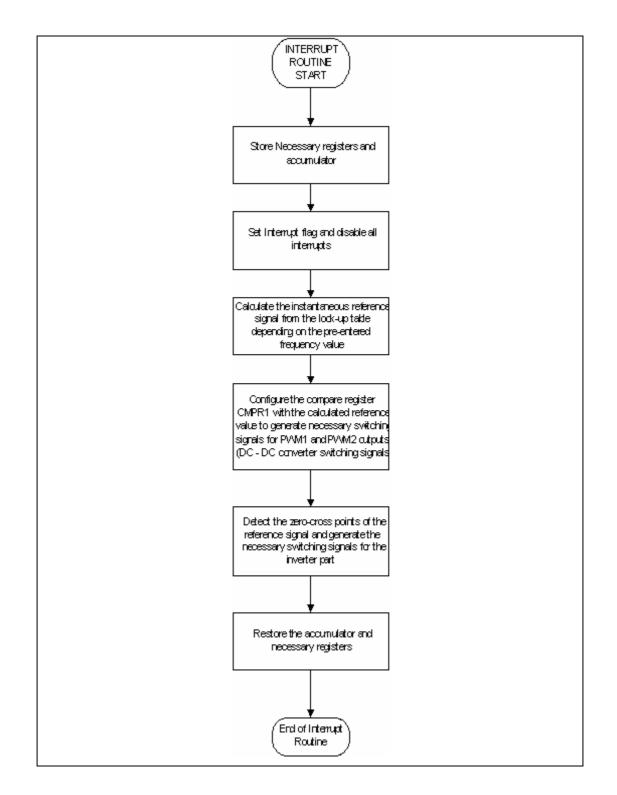

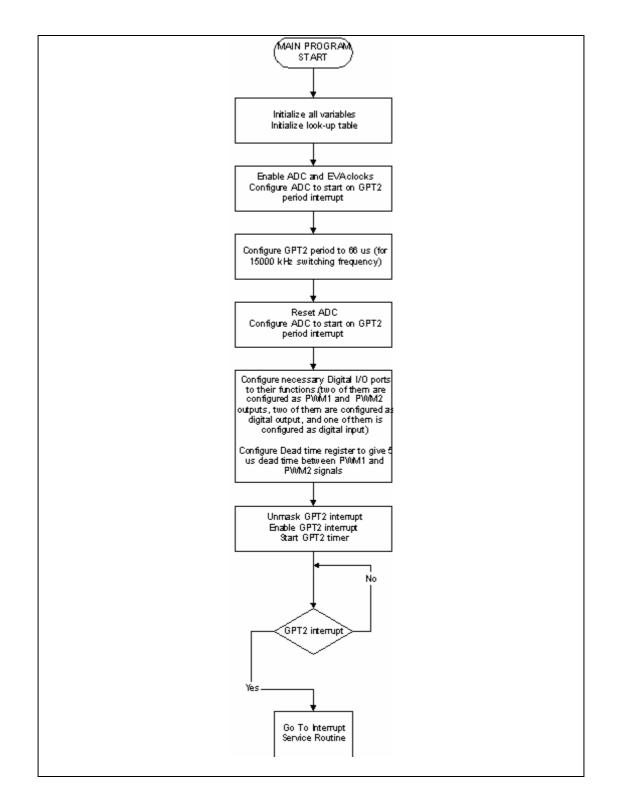

| A.1 Flow Chart of the main program for open loop control 106                 |

| A.2 Flow Chart of the interrupt service routine for open loop control 107    |

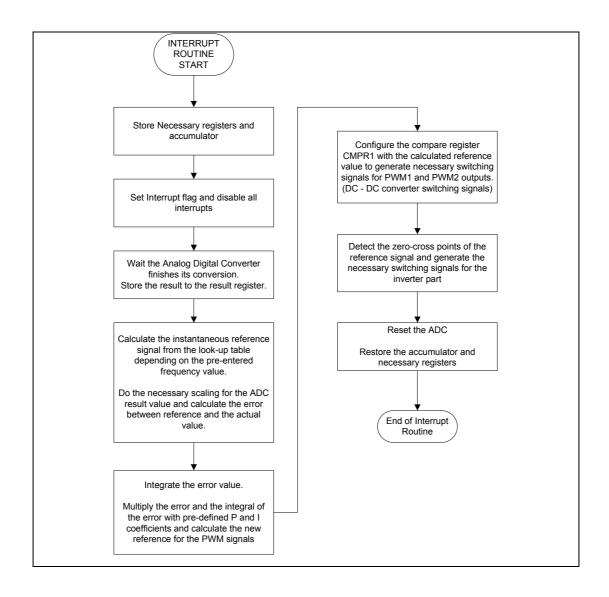

| A.3 Flow Chart of the main program for closed loop control 108               |

| A.4 Flow Chart of the interrupt service routine for closed loop control109   |

| A.5 Simulation Model                                                         | 127  |

|------------------------------------------------------------------------------|------|

| A.6 First topology consists of four tyristors                                | 129  |

| A.7 Four anti-parallel diodes are added to topology one                      | .129 |

| A.8 Third topology consists of two tyristors and two transistors             | 130  |

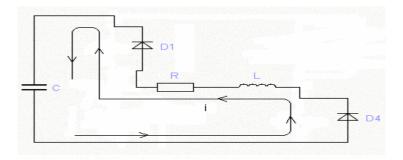

| A.9 T1 and TR2 are turned on                                                 | .130 |

| A.10 Load current closes its path through D2                                 | .131 |

| A.11 Fourth topology consists of four transistors                            | 132  |

| A.12 Anti-parallel diodes connected to topology shown in figure A.11         | 132  |

| A.13 TR1 and TR4 are on                                                      | .132 |

| A.14 D2 and D3 are on                                                        | 133  |

| A.15 TR2 and TR3 are on.                                                     | .133 |

| A.16 D1 and D4 are on                                                        | .134 |

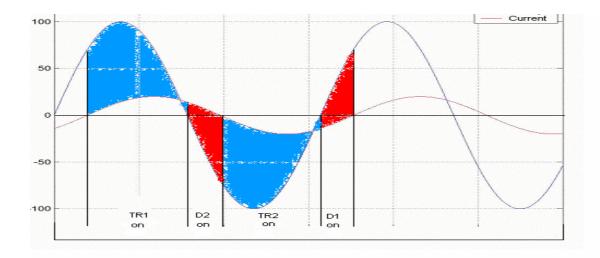

| A.17 Theoretical voltage and current waveforms indicating the operation      |      |

| modes for inductive load                                                     | 134  |

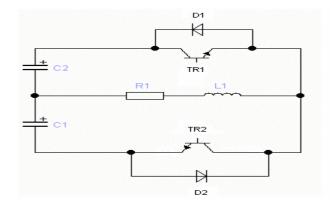

| A.18 Fifth topology consists of two transistors, two capacitors at the input | 135  |

| A.19 TR1 is on                                                               | 135  |

| A.20 D2 is on                                                                | 136  |

| A.21 TR2 is on.                                                              | 136  |

| A.22 D1 is on                                                                | 136  |

| A.23 Theoretical voltage and current waveforms indicating the operation      |      |

| modes for inductive load                                                     | 137  |

## LIST OF SYMBOLS

| $V_d$                                       | DC-DC Converter input voltage                          |

|---------------------------------------------|--------------------------------------------------------|

| Vo                                          | DC-DC Converter output voltage                         |

| $V_{L}$                                     | DC-DC Converter inductance voltage                     |

| $i_L$                                       | DC-DC Converter inductance current                     |

| ton                                         | Turn-on duration of the switch of the DC-DC Converter  |

| toff                                        | Turn-off duration of the switch of the DC-DC Converter |

| T <sub>s</sub>                              | Switching period of the switch of the DC-DC Converter  |

| $\mathbf{f}_{\mathbf{s}}$                   | Switching frequency                                    |

| D                                           | Duty cycle                                             |

| $\Delta V$                                  | DC-DC Converter output voltage ripple                  |

| ΔQ                                          | Stored charge on DC-DC Converter output capacitor      |

| $\mathbf{f}_{\mathbf{c}}$                   | Cut-off frequency                                      |

| $I_{LB}$                                    | Average inductor current at boundry                    |

| I <sub>oB</sub>                             | DC-DC converter output current at boundry              |

| L                                           | DC-DC Converter filter inductance                      |

| С                                           | DC-DC Converter                                        |

| $\hat{I}$                                   | Maximum inductance current                             |

| Ν                                           | Number of turns                                        |

| $\stackrel{\scriptscriptstyle\wedge}{\Phi}$ | Peak flux in the inductor                              |

|                                             |                                                        |

| k <sub>cu</sub>                             | Winding factor                                         |

| $A_w$                                       | effective winding area                                 |

| A <sub>cu</sub>                             | Conductor area.                                        |

| A <sub>core</sub>                           | effective core area                                    |

| $\overset{{}_\circ}{B}$                     | Maximum flux density                                   |

| rms value of the inductor current              |

|------------------------------------------------|

| rms current density                            |

| DC-DC converter output impedance               |

| Area Product                                   |

| Saturation flux density                        |

| Copper loss                                    |

| Core loss                                      |

| core volume                                    |

| Surface-to-ambient thermal resistance          |

| Radiative thermal resistance                   |

| Convective thermal resistance                  |

| Radiated power                                 |

| Heat power lost via convection                 |

| Magnetic flux path length in the core material |

| Total reluctance of the magnetic flux path     |

|                                                |

#### **CHAPTER 1**

#### INTRODUCTION

In variable-speed ac drives which utilize voltage-fed inverters, control of the voltage and frequency output of the inverter feeding the ac motor is essential for torque and speed control of the motor. Similarly in ac power supplies which utilize uninterruptible power supplies, again control of the output voltage and frequency of the supply feeding the load is essential for supplying regulated voltage to the load without any distortion. The early approach has been to use a voltage-fed square wave inverter fed by a variable DC voltage source. Variable DC voltage is required since the only way to change the fundamental voltage of a square-wave inverter is to change its amplitude. The variable DC-link voltage is obtained from a phase-controlled rectifier. This system has a big drawback. The output of a square-wave inverter contains high-amplitude low frequency harmonics. Therefore, the losses of a motor (in the case of a motor drive application) due to the resulting harmonic currents tend to be high.

With the recent developments in power electronic devices and controller circuits, different techniques have been developed called Pulse-Width Modulation (PWM) techniques, which carry the harmonics of the output voltage to higher frequency levels eliminating lower order harmonics. Also these techniques make possible both voltage and frequency control within the inverter itself. There are some advantages of these techniques. First, a variable DC-link is not essential. A PWM

inverter is usually fed by an uncontrolled diode bridge rectifier. Secondly, high amplitude low frequency harmonics are eliminated.

Various PWM strategies have been introduced for controlling inverters. The common principle in all these strategies is to introduce notches in the basic squarewave pole voltage, such that the resulting periodic waveform has the desired fundamental frequency and amplitude. [1]

PWM techniques can be classified into the following categories:

- Square-wave modulation

- The sampling method

- Optimized PWM

- Selected Harmonic Elimination

- Delta Modulation

- Space-vector based PWM

Beside the advantages of the PWM techniques, some drawbacks occur with the increasing frequency levels. The switches in the inverter are rapidly switched and are either turned hard ON or OFF with no in between state. The result is that the sine wave current is generated if the load is inductive by using pulse width modulated switching. However as discussed before the voltage wave form is a series of pulses in the output of the inverter, and the voltage transitions are very rapid. This rapid switching causes a voltage waveform with a very high dv/dt (rate of change in voltage).

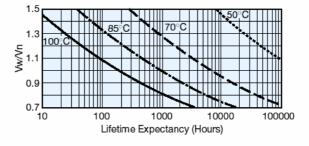

In recent studies it has been proven that these pulses introduce some additional drawbacks to the system. First, the losses especially copper and core losses are increased. Secondly, in motor drive applications motors have parasitic capacitances of the electrically conducting components with respect to the ground potential. If the available DC voltage is chopped in the inverter, then, during the potential jumps of the voltage, considerable pulse currents flow across the parasitic capacitance's to the earth. If the grounding of the motor is inadequate, the potentials at the parasitic capacitances increase sharply. The values of the bearing currents also increase massively, and flow fully through the bearings to the earth. In that case, the life expectancy of the ball bearings, and hence of the entire motor is reduced. Also the insulation of the motor is affected by these pulses. Thirdly, even the load current is sinusoidal, high dv/dt can cause high radiated energy causing EMC problems as well.

Under these circumstances, synthesizing a pure sinusoidal waveform at the output of the inverter seems to be an important concept and demand in order to further increase the performance of inverter-load systems.

With the developments in power electronic devices and magnetic materials a novel idea is proposed by the supervisor of this thesis in order to synthesize pure sinusoidal waveform. Basic idea is a DC-DC converter which can track a high frequency sinusoidal reference and create a DC bus of rectified sinusoids at desired frequency as shown in figure 1.1. By inverting the rectified sinusoids at the DC-DC converter's output, a pure sinusoidal output voltage can be obtained as shown in figure 1.2. An added advantage of this technique is that the input current can be also made sinusoidal without additional cost. Hence, injection of harmonic currents to the mains can be avoided.

Throughout this thesis study, proper topologies for DC-DC converter and the inverter part are analyzed in detail. Necessary basic theoretical information is given about the selected topologies. Some modifications made on topologies in order to improve the performance. Also detailed design procedures are given for the magnetic parts. Practical results are obtained in the laboratory environment.

Second chapter includes the choice of the best topologies necessary for the proposed idea. In this section some candidate topologies are examined and the chosen topologies are supplied with detailed theoretical background information. Also this chapter includes the integration of chosen topologies and computer simulations. The modifications on the topologies and further computer simulations including different control approaches are given in chapter 2 as well.

In chapter 3, determination of DC-DC converter parameters are examined. This is followed by an evoluation of how the output filter parameters L, and C should be chosen. The inductance value and size minimization is specially emphasized, which has a vital role in our application. A computer program is developed in order to calculate the proper value of the inductor depending on the current and size parameters. Then thermal analysis of the inductor is given in order to guarantee the operation.

Chapter 4 includes the practical implementation of the proposed system. The hardware and control software are introduced in this chapter. Also detailed experimental results are given in this chapter.

Finally conclusions and proposals for future studies are given in chapter 5.

Fig.1.1 Full-rectified sinusoids

Figure.1.2 Sinusoidal waveform inverted from full-rectified sinusoids

## CHAPTER 2

#### **THEORETICAL STUDY**

#### 2.1 General Overview of the Proposed System

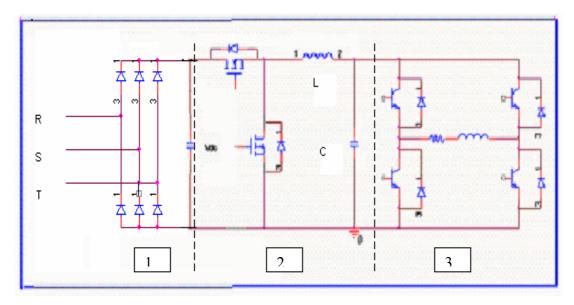

In chapter 1 the problem has been defined. As discussed in the introduction, the overall system is supposed to be composed of two discrete stages that are the input stage which generates rectified sinusoidal voltages in other words which produces a DC- link has a voltage waveform of rectified sinusoids that can be called as "Rectified DC-Link". And the output stage that forms the sinusoidal output voltage from the rectified sinusoids in other words inverts the rectified sinusoids of the output of the first stage.

In this chapter, first of all the suitable circuit topologies for input and output stages are reviewed and analyzed.

Subsequently, integration of two discrete stages will be analyzed. At that section the drawbacks of the proposed basic circuit configuration will be given.

Consequently the modifications proposed on the circuit topology and their effects on the performance are investigated. Also detailed computer simulations of the resultant circuit will be examined.

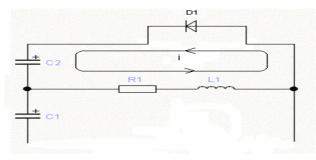

#### 2.2 Output Stage (Inverter Stage)

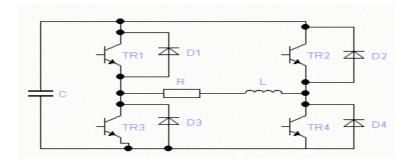

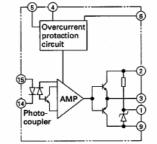

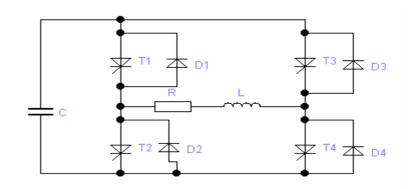

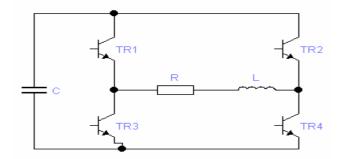

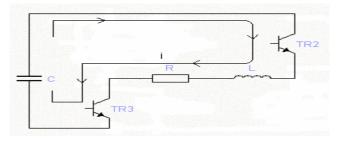

The inversion capabilities of different topologies, under two types of load

(purely resistive, inductive), are examined and detailed mode by mode analysis are given in Appendix A5. The chosen topology is given below

Figure 2.1 Full controlled H-Bridge inverter with back diodes (output stage)

#### 2.3 Input Stage

In this section, the best and feasible topology for the input stage is determined and analyzed in detail.

#### 2.3.1 Determination of Suitable Topology for the Input Stage

The input of the input stage is a constant DC bus voltage, and the output should be rectified sinusoidal voltage as shown in figure 2.2. Also the frequency and the magnitude of the output voltage should be variable. The output of this circuit is called as "Rectified DC-Link"

Figure 2.2 Output of the input stage (Rectified DC-Link voltage)

The waveform shown in figure 2.2 is a variable DC voltage waveform. So it can be said that both the input and the output of the circuit is DC quantities.

Consequently a DC-DC converter will be suitable for the application. But contrary to conventional operation of a DC-DC converter which operates in steadystate, the operation must be always in transient region for the proposed application. In another words, DC-DC converter should be operated to track a rectified sinusoidal reference voltage, but not a constant one as usual.

Due to its simplicity and linearity, in this thesis, a DC-DC step down (buck) converter is chosen as the input stage of the overall topology. It has the advantage of linear input output voltage relation and also has the ability of control the voltage down to 0 volts as well. Detailed information about DC-DC converters focusing on the step down (buck) type is given in the next section.

#### 2.3.2 DC-DC Converter Basics

A DC-to-DC converter is a device that accepts a DC input voltage and produces a DC output voltage. Typically the output produced is at a different voltage level than the input.[2,3]

Two alternatives for delivery of electric power from a dc source to a load in a controllable manner are linear and switched mode power conversion.

Linear power conversion relies on the presence of a series linear element, especially a semiconductor device used in the linear region such that the total load current passes through the linear element. Therefore, the greater the difference between the input and the output voltages, the more power is lost in the element. So this type of conversion is very dissipative and inefficient.

In switched mode power conversion, the controlling device is a switch which is either closed or open. By controlling the duty cycle, the power flow to the load can be controlled in a very efficient way. The only losses may be the element losses( semiconductor, inductor and capacitor). However, the output voltage is not a pure dc as in the linear case, and pulsed power is delivered to the load. The power flow to the load may be easily smoothed out by implementing a low-pass LC filter.

#### 2.3.3 Step Down (Buck) Converter

The basics of the single quadrant buck converter is given in [2,3] in detail. In this section only brief information and necessary equations are given also some equations which are not available in the literature such as output voltage ripple equations for discontinuous conduction mode.

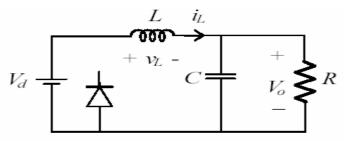

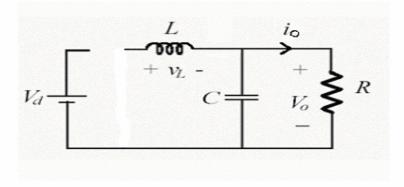

The simplest configuration of the converter is given in the figure 2.3 below.

Figure 2.3 Step Down (Buck) converter

During  $0 < t < t_{on}$ , voltage across the inductor L is  $V_d - V_o$ ;  $i_L$  rises to  $I_{Lmax}$ . During ton  $< t < T_s$ , voltage across the inductor L is  $-V_o$ , and  $i_L$  falls to  $I_{Lmin}$ . In the steady state, the inductor current must return to  $I_{Lmin}$  at the end of the switching period  $T_s$ , and the integral of the inductor voltage (i.e., the dc voltage supported across the inductor) must be zero. In the following we assume that the output voltage ripple is negligible.

Depending on the inductor current waveform, the operation of the step down (buck) converter will be examined in 2 different modes. These are:

- Continuous Conduction Mode

- Discontinuous Conduction Mode

#### 2.3.3.1 Continuous Conduction Mode

For continuous conduction mode of operation, there are two circuit states as shown in figure 2.4. The circuit is analyzed mode-by-mode for continuous conduction mode.

Figure 2.4. Buck converter waveforms and circuit states

#### 2.3.3.1.1 Mode 1: switch is on

The equivalent circuit diagram is shown in Figure 2.5

Figure 2.5 Equivalent circuit for switch is on

Inductor voltage

$$v_{\rm L}(t) = V_{\rm d} - v_{\rm o}(t) \qquad 2.1$$

Small ripple approximation

$$v_{\rm L}(t) \approx V_{\rm d} - V_{\rm o}$$

2.2

Knowing the inductor voltage, now the inductor current can be found via Faraday's Law

$$v_L(t) = L \frac{di_L(t)}{dt}$$

2.3

Solve for the slope of the inductor current:

$$\frac{di_L(t)}{dt} = \frac{v_L(t)}{L} \approx \frac{V_d - V_o}{L}$$

2.4

#### 2.3.3.1.2 Mode 2: switch is off

The equivalent circuit diagram is shown in Figure 2.6

Figure 2.6.Equivalent circuit for switch is off

Inductor voltage

$$\mathbf{v}_{\mathrm{L}}(t) = -\mathbf{v}_{\mathrm{o}}(t) \qquad 2.5$$

Small ripple approximation

$$v_{\rm L}(t) \approx -V_{\rm o}$$

2.6

Knowing the inductor voltage, we can again find the inductor current via

$$v_L(t) = L \frac{di_L(t)}{dt} \Rightarrow \frac{di_L(t)}{dt} \approx -\frac{V_o}{L}$$

2.7

#### 2.3.3.1.3 Steady-State Analysis and Volt-Second Balance on Inductor

From Faraday's law for the inductor voltage,

$$v_L(t) = L \frac{di_L(t)}{dt}$$

2.8

Integrating over one complete switching period:

$$i_{L}(T_{s}) - i_{L}(0) = \frac{1}{L} \int_{0}^{T_{s}} v_{L}(t) dt \qquad 2.9$$

In periodic steady state, the net change in inductor current is zero

$$0 = \int_0^{T_s} v_L(t) dt \qquad 2.10$$

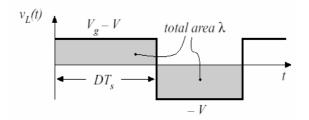

Hence, the total area (or volt-seconds) under the inductor voltage waveform, shown in figure 2.7, is zero whenever the converter operates in steady state. An equivalent form

$$0 = \frac{1}{T_s} \int_0^{T_s} v_L(t) dt = \langle v_L \rangle$$

2.11

The average inductor voltage for one cycle is zero at steady state. Using this statement and figure 2.7

$$(V_d - V_o) D Ts = V_d (1-D) Ts \implies \frac{V_o}{V_d} = D$$

2.12

Eq 2.12 equation is called the conversion ratio equation for continuous conduction mode.

Figure 2.7. Inductor voltage

In ideal cases, voltage control range of a buck converter operating in continuous conduction mode, is from 0 V to  $V_d$ .

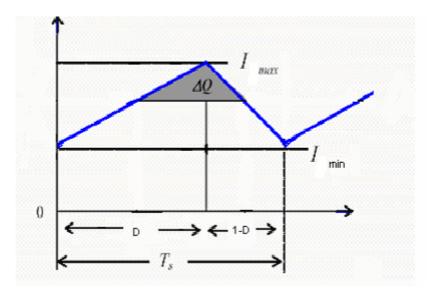

# 2.3.3.1.4 Output Voltage Ripple of Buck Converter for Continuous Conduction Mode (Approximate Analysis)

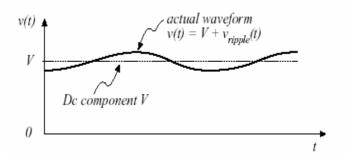

Actually the output of a buck converter is not a pure DC voltage. It has a small ripple on a DC component as shown in figure 2.8. In order to calculate the switching output voltage ripple  $\Delta V$ , it is assumed that the inductor current ripple  $\Delta i_L$  flows into the output capacitor to generate the voltage ripple. The total voltage ripple  $\Delta V$  is obtained from the stored charge  $\Delta Q$ , which is the area under inductor current ripple as shown in figure 2.9

Figure 2.8. Actual Output Voltage Waveform of a Buck Converter

Figure 2.9. inductor current ripple(stored charge)

Hence,

$$\Delta \mathbf{Q} = \frac{1}{2} \frac{T_s}{2} \frac{\Delta i_L}{2} = \frac{1}{8} T_s \Delta i_L, \qquad 2.13$$

$$\Delta V_{\rm O} = \frac{\Delta Q}{C} = \frac{1}{C} \frac{1}{8} T s \Delta i_L, \qquad 2.14$$

$$\Delta \mathbf{i}_L = \frac{Vo}{L} (1 - D)Ts \qquad 2.15$$

$$\Delta V_{O} = \frac{Ts}{8C} \frac{VO}{L} (1-D)Ts \implies \frac{\Delta V_{O}}{VO} = \frac{1}{8} \frac{Ts^{2}(1-D)}{LC} = \frac{1}{8} \frac{(1-D)}{LCf_{s}^{2}}$$

2.16

Eq. 2.16 can also be expressed in terms of switching and cut-off frequencies as,

$$\frac{\Delta V_o}{Vo} = \frac{\pi^2}{2} (1 - D) \left(\frac{fc}{fs}\right)^2$$

2.17

where fs = 1/Ts and

$$fc = \frac{1}{2\pi\sqrt{LC}}$$

2.18

The output voltage ripple can be minimized if fs >> fc. Also it is obviously seen that the output voltage ripple of a buck converter operating in continuous conduction mode, is independent from load. It is only a function of constant parameters such as L, C,  $f_s$ , and D.

#### 2.3.3.2 Boundary between Continuous and Discontinuous Conduction Modes

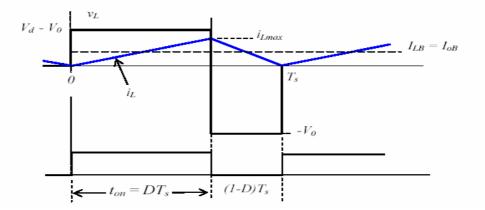

In this section, the boundary condition for the inductor current is investigated. Figure 2.10 shows this condition for inductor current and voltage.

Figure 2.10. Inductor voltage and current waveforms at the boundary of continuous and discontinuous conduction.

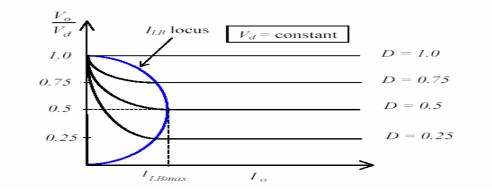

From figure 2.10, average inductor current  $I_{LB}$ , where subscript B refers to the boundary, is found as a function of duty cycle as,

$$I_{LB} = \frac{1}{2}i_{L\max} = \frac{1}{2}\frac{V_d - V_O}{L}t_{on} = I_{oB}$$

2.19

$$= \frac{DT_s}{2L} (V_d - V_O) = \frac{DT_s}{2L} (V_d - DV_d) = \frac{T_s V_d D(1 - D)}{2L}$$

2.20

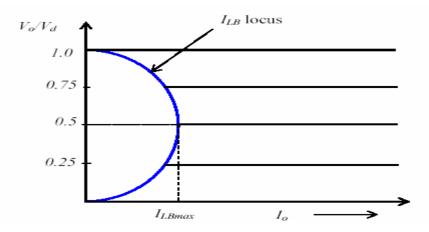

$I_{LB}$  becomes maximum when D = 0.5 (this is found by differentiating  $I_{LB}$  with respect to D and equating the derivative to zero). For D = 0.5,

$$I_{LB\max} = \frac{T_s V_d}{8L}$$

2.21

And,

$$I_{IB} = 4I_{IB\max} D(1-D)$$

2.22

Using Eq. 2.21 and 2.22  $I_{LB}$  loci for duty cycles between 0-1 can be plotted as shown in figure 2.11

Figure 2.11.Converter characteristics with duty-cycle and load

During normal operation,  $I_{LB}$  should be smaller than the lowest load current, so that the converter operates in continuous conduction mode (i.e., in the linear mode with Vo = DVd). The minimum inductance L and the switching frequency  $f_s$  for this condition of operation are obtained from the following consideration. In periodic steady state, the net change in inductor current is zero

$$\int_{0}^{T_{s}} \frac{v_{L}}{L} dt = \int_{(0)}^{(T_{s})} di = 0$$

2.23

$$\frac{V_d - V_o}{L} DT_s - \frac{V_o}{L} (1 - D)T_s = 0$$

2.24

The first term in Eq.2.24 is  $.i_L$  (rise) and the second term is  $.i_L$  (fall). For a given load resistance R,

$$i_{L \max} = \frac{V_o}{R} + \frac{\Delta i_L}{2} = \frac{V_o}{R} + \frac{V_o}{2L} (1 - D) T_s$$

2.25

$$i_{L\min} = \frac{V_o}{R} - \frac{\Delta i_L}{2} = \frac{V_o}{R} - \frac{V_o}{2L} (1 - D)T_s$$

2.26

At the boundary of continuous-discontinuous conduction,  $i_{Lmin} = 0$ , so that

$$\left(Lf_s\right)_{\min} = \frac{(1-D)R}{2}$$

2.27

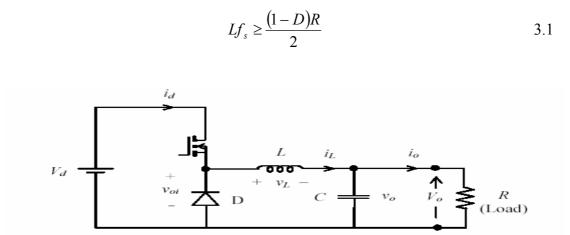

Hence, for continuous conduction,

$$Lf_s \ge \frac{(1-D)R}{2} \tag{2.28}$$

#### 2.3.3.3 Discontinuous Conduction Mode

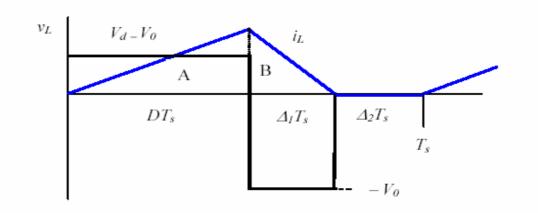

In practice load current may change over a wide range, from no load to full load. Increase of load resistance leads to a decrease of load current. Hence a new operation region is encountered, termed discontinuous conduction mode. The load current and consequently the inductor current cheases before the next cycle begins. Inductor current and voltage waveform is shown in figure 2.12.

Figure 2.12 vL and iL waveforms with discontinuous conduction.

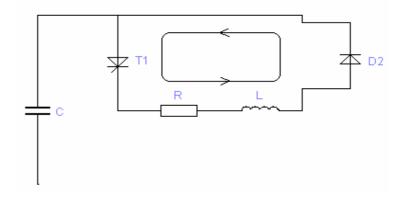

For discontinuous conduction mode of operation, there are three circuit states as shown in figure 2.13, 2.14, and 2.15.

#### 2.3.3.3.1 Subinterval 1: switch is on

Figure 2.13 Switch is on (discontinuous conduction)

#### 2.3.3.3.2 Subinterval 2: switch is off

Figure 2.14 Switch is off (discontinuous conduction)

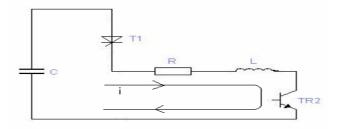

#### 2.3.3.3 Subinterval 3: switch is off and inductor current is 0

Figure 2.15 Switch is off, Inductor current is 0 (discontinuous conduction)

## 2.3.3.3.4 Steady-State Analysis and Volt-Second Balance on Inductor

The average inductor voltage for one cycle is zero at steady state. Using this statement and Fig 2.12

$$(V_{d} - V_{o})DT_{s} - V_{o}\Delta_{1}T_{s} = 0 2.29$$

Thus input output voltage relationship becomes

$$\frac{V_o}{V_d} = \frac{D}{D + \Delta_1}$$

2.30

Where  $D + \Delta_1 < 1$ . Now

$$i_{L\max} = \frac{V_o}{L} \Delta_1 T_s$$

2.31

And,

$$I_{o} = \frac{\left\{ i_{L \max} \frac{DT_{s}}{2} + i_{L \max} \frac{\Delta_{1}T_{s}}{2} \right\}}{T_{s}} = i_{L \max} \frac{(D + \Delta 1)}{2}$$

2.32

Using Eq.2.31

$$=\frac{V_o}{L}\Delta 1T_s \frac{D+\Delta_1}{2}$$

2.33

Using Eq.2.30

$$=\frac{V_d}{L}\frac{D}{D+\Delta_1}\times\Delta_1T_s\times\frac{D+\Delta_1}{2}$$

2.34

$$=\frac{V_d}{2L}T_s D\Delta_1$$

2.35

Using Eq. 2.21

$$=4I_{LB\max}D\Delta_1$$

2.36

$$\Delta_1 = \frac{I_o}{4I_{LB\,\mathrm{max}}D} \qquad 2.37$$

Using Eq.2.30

$$\frac{V_o}{V_d} = \frac{D^2}{D^2 + \frac{1}{4} (I_o / I_{LB \max})}$$

2.38

Figure 2.16 Converter characteristics with discontinuous conduction.

Note that  $V_o$  falls sharply with load when the inductor current is discontinuous. Note also that with discontinuous conduction, the  $V_o/V_d$  ratio becomes higher than D, implying loss of voltage gain of the converter.

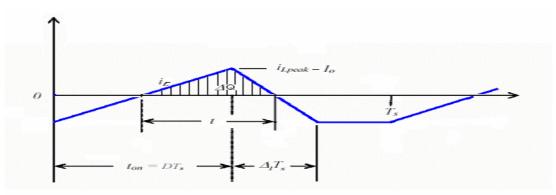

## 2.3.3.5 Output Voltage Ripple of the Buck Converter Operating in Discontinuous Conduction Mode

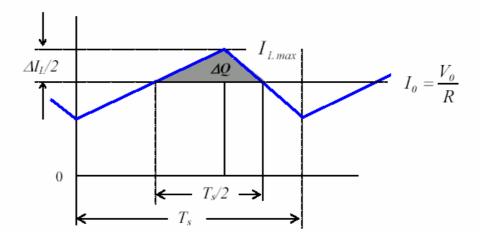

The same approach followed for Continuous Conduction mode of operation is applicable for discontinuous conduction mode of operation. The total voltage ripple  $\Delta V$  is obtained from the stored charge  $\Delta Q$ , which is the area under inductor current ripple as shown in figure 2.17

Figure 2.17. Capacitor current waveform (stored charge)

$$\Delta Q = C \Delta V_o = \frac{t(I_{peak} - I_o)}{2}$$

2.39

$$(I_{\text{peak}} - I_{\text{o}}) = \left(\frac{(V_s - V_o)DT}{L} - I_o\right) = \frac{(V_s - V_o)DT - I_oL}{L}$$

2.40

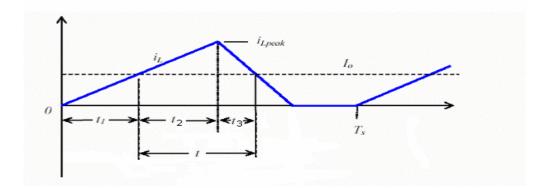

Time t can be calculated from inductance current waveform given in figure 2.18

Figure 2.18 Inductance current waveform for discontinuous conduction mode

$$t = t_2 + t_3,$$

2.41

And

$$t_2 = DT - t_1 \tag{2.42}$$

By using the slope of the inductance current for  $t < t_2$

$$\left(\frac{V_s - V_o}{L}\right) t_1 = I_o$$

2.43

Yields,

$$t_1 = \left(\frac{I_o L}{V_s - V_o}\right)$$

2.44

Thus using Eq. 2.42

$$t_2 = DT - \left(\frac{I_o}{V_s - V_o}\right)$$

2.45

On the other hand using the slope of the inductance current waveform for  $t > t_3$ ,

$$I_{peak} - t_3 \frac{V_O}{L} = I_O$$

2.46

I<sub>peak</sub> can be expressed as,

$$\left(\frac{V_s - V_o}{L}\right)DT - t_3 \frac{V_o}{L} = I_o$$

2.47

Therefore,

$$t_3 = \left(\frac{V_s - V_o}{V_o}\right) DT - \frac{LI_o}{V_o}$$

2.48

Using Eqs. 2.42, 2.44 and 2.48 in Eq. 2.41 yields,

$$t = DT - \left(\frac{I_o L}{V_s - V_o}\right) + \left(\frac{(V_s - V_o)}{V_o}\right) DT - \frac{LI_o}{V_o}$$

2.49

Finally using Eq.2.49 in Eq.2.39 gives

$$C\Delta V_{o} = \left[\frac{\left[DT(V_{s} - V_{o}) - LI_{o}\right]\left[DT(V_{s} - V_{o})V_{o} - LI_{o}V_{o} + \left[(V_{s} - V_{o})(DT(V_{s} - V_{o}) - LI_{o})\right]\right]}{2LV_{o}(V_{s} - V_{o})}\right] 2.50$$

Thus the output voltage ripple is expressed as

$$\Delta V_{o} = \left[\frac{\left[DT(V_{s} - V_{o}) - LI_{o}\right]\left[DT(V_{s} - V_{o})V_{o} - LI_{o}V_{o} + \left[(V_{s} - V_{o})(DT(V_{s} - V_{o}) - LI_{o})\right]\right]}{2LCV_{o}(V_{s} - V_{o})}\right] 2.51$$

It is obviously seen from equations 2.38 and 2.51 that both buck converter's input output voltage relationship and output voltage ripple functions are depending on load. This has some disadvantages in terms of both control of the converter output

voltage and also selection of the circuit parameters especially the output filter capacitor for specific applications.

#### 2.4 Combination of Input and Output Stages

In this section, the two discrete circuits, which are the buck converter and the H-bridge inverter, are connected together to form a sinusoidal wave shape and the performance of the resultant circuit will be investigated.

As discussed in previous sections, input stage will generate rectified sinusoids and the output stage will invert this waveform. And also proper circuit topologies have been determined that can separately do necessary operations. This section of the study investigates the combinational operation of discrete stages and will analyze the effects of each stage on the other. If necessary, modifications will be proposed.

Performance of the combined circuit will be investigated in terms of

- Operating conditions of the DC-DC converter filter inductance (continuous and discontinuous conduction modes)

- Under load conditions (resistive and inductive load)

During the analysis of the DC-DC filter inductance operating conditions, minimum inductance values will be calculated which satisfy the continuous conduction mode of operation. With these values necessary comments will be done for the performance of the system.

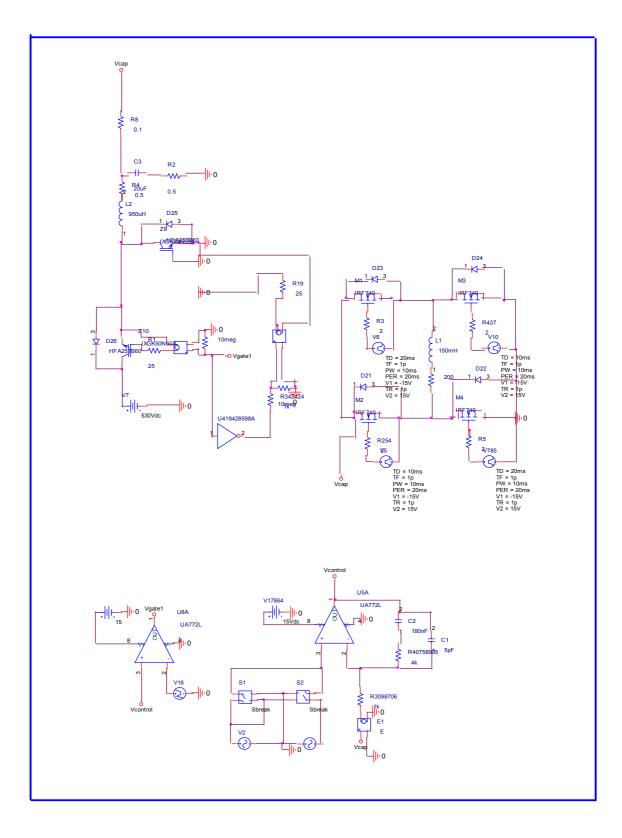

For the load analysis, first of all feed forward control for DC-DC converter will be analyzed. Than if necessary closed loop control will be applied to the system. For all load analysis, system performance will be evaluated by output voltage FFT (Fast Fourier Transform) results and also THD (Total Harmonic Distortion) of the output voltage. During the analysis, the parameters that is calculated for the filter elements (capacitor and inductor) in chapter 3, is used in foregoing analysis in this section.  $L = 950 \ \mu\text{H}$  and  $C = 10 \ \mu\text{F}$ .

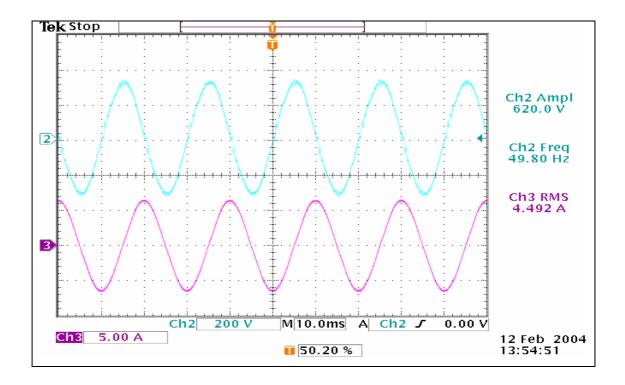

The basic proposed topology of the circuit is shown in figure 2.19. The maximum output power and voltage of the system is desired to be 1kVA and 220  $V_{rms}$  respectively. Full load current is approximately 4.5 A. So for full load, load impedance is approximately 50 $\Omega$ .

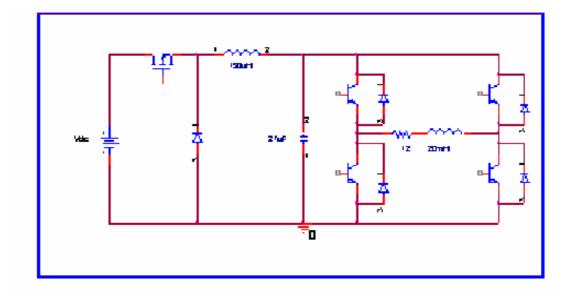

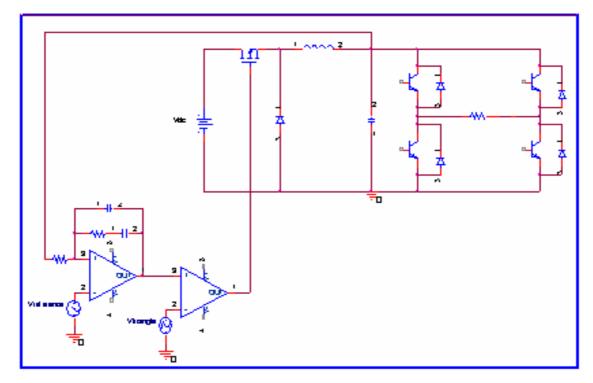

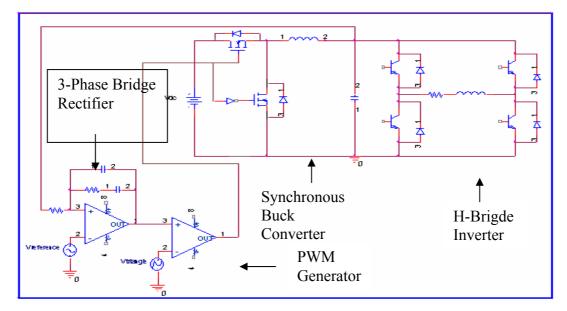

Figure 2.19 Basic circuit diagram of the overall system

# 2.4.1 Analysis of the Operating Conditions of the DC-DC Converter Filter Inductance

In this section the operating conditions of the buck converter used in our application will be examined. The circuit will be analyzed whether it operates in continuous conduction mode or in discontinuous conduction mode.

As discussed before the output voltage of the DC-DC Converter used in this thesis, is supposed to be rectified sinusoidal voltages. In other words, the amplitude of this voltage is changing between 0 and  $V_{out,peak}$ . Thus, duty cycle is changing between 0 and  $D_{max}$ .

Boundary operation condition (boundary condition between continuous and discontinuous inductor current) for a buck converter is given by equation 2.28

$$Lf_s \ge \frac{(1-D)R}{2}$$

Maximum output power of the circuit is desired to be in the range 750VA - 1 KVA. Maximum Output Voltage is 311  $V_{peak}$ , 220 $V_{rms}$ . For an input voltage of 530  $V_{dc}$ , Dmax  $\cong 0.6$ ,  $f_s = 15.000$  Hz.

So the minimum inductance that satisfies continuous conduction mode for an output voltage of  $310V_{peak}$  and for full load impedance (50 $\Omega$ ) is

$$L_{\min, fullload, D=0.6} \cong \frac{(1-0.6)50}{30000} \Longrightarrow L_{\min} \cong 670 \,\mu H$$

In our application, even if the circuit operates at full load, and at maximum operating voltage, the inductance value is just satisfies the necessary condition for continuous inductor current just for the higher instantaneous voltages of the sinus curve. Because as it is said before the actual inductance value is 950  $\mu$ H (calculated in chapter 3).

As the output voltage is sinusoidal and in one cycle its magnitude already changes between 0 and 310 at rated conditions. That mean duty cycle gets a value of range 0-0.6.

For voltage values near 0, let's say  $D \cong 0.1$ , then again for full load, the minimum inductance value necessary for continuous conduction operation is,

$$L_{\min, fullload, D=0.1} \cong \frac{(1-0.1)50}{30000} \Longrightarrow L \cong 1.5 mH$$

Consequently it is obvious that even if the output voltage is max (220  $V_{rms}$ ), and the circuit operates at full load, the inductor current is essentially both continuous and discontinuous in one period, in our application.

The equations for a buck converter show that, for discontinuous operation mode, the system is nonlinear in terms of input-output voltage relationship as shown in equation 2.30. As a result of this nonlinearity, two problems occur.

- Proper voltage regulation can not be achieved with linear control techniques such as PI control. Because, as it is discussed in DC-DC buck converter basics, for discontinuous conduction mode of operation, the circuit is out of control of the switches as the inductor current vanishes, as was shown in figure 2.36. There will be no switching in this period and the variation of the output voltage is directly proportional with the time constant of the output capacitor and the load. Thus the system is operates in this region uncontrollably with its own nature.

- Secondly, the output voltage ripple relation with the converter operating characteristics must be analyzed especially for determining the value of the output filter capacitance of the DC-DC buck converter.

For continuous conduction mode of operation, the output voltage ripple is given by Eq.2.16 as

$$\Delta V_O = \frac{(1-D)V_O}{8CLf_s^2}$$

Solving Eq.2.16 for C gives,

$$C = \frac{(1-D)V_o}{\Delta V_o 8L {f_s}^2}$$

For constant values of DC-DC converter input voltage, inductance, switching frequency, and for a specified value of output voltage ripple, capacitance value can be determined as a function of duty cycle, independent of the load and if the highest possible value of the inductance is chosen, the desired low output voltage ripple level will be guarantied.

On the other hand, for continuous conduction mode of operation, the output voltage ripple is given by Eq.2.51 as

$$\Delta V_{O} = \left[\frac{\left[DT(V_{S} - V_{O}) - LI_{O}\right]\left[DT(V_{S} - V_{O})V_{O} - LI_{O}V_{O} + \left[(V_{S} - V_{O})(DT(V_{S} - V_{O}) - LI_{O})\right]\right]}{2LCV_{O}(V_{S} - V_{O})}\right] 2.51$$

Solving Eq.2.51 for C gives,

$$C = \left[\frac{\left[DT(V_{S} - V_{O}) - LI_{O}\right]\left[DT(V_{S} - V_{O})V_{O} - LI_{O}V_{O} + \left[(V_{S} - V_{O})(DT(V_{S} - V_{O}) - LI_{O})\right]\right]}{\Delta V_{O} 2LV_{O}(V_{S} - V_{O})}\right] 2.52$$

As it is seen in Eq.2.52, capacitance value is dependent to the load. As a result of this for specified circuit parameters it is impossible to obtain constant output voltage ripple for dynamic loads. Such as in the application in this thesis, output voltage is always varying to form rectified sinusoidal wave shape so it always operates in transient region. Therefore discontinuous conduction mode is undesirable.

#### 2.4.2 Analysis of the Proposed Circuit under Load Conditions

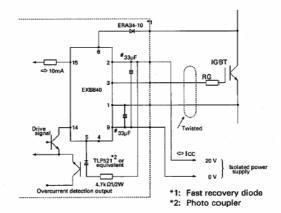

The analysis is done with ORCAD's PSpice version 9.2 [5]. Throughout the simulations, non-ideal (actual) semiconductor switches and diodes are used for buck converter and H-bridge inverter. In closed loop control case, an analog PI controller is used composed of analog comparators. In order to prevent convergence problems of the analysis, small series resistances added to the passive elements as discussed in [5, 22]. Simulation model is given in appendix A.4

The system is first simulated using feed-forward control. A reference voltage that is rectified sinusoids is applied to the buck converter and then the signal at the output of the buck converter is inverted by the output stage. Secondly the system is simulated using closed loop control by taking feedback from the output of the buck converter. The output voltage of the buck converter is compared with the reference and the error is applied to a PI controller. The output of the controller is applied to the buck converter.

Load analysis is done at rated output voltage and at full load (Load impedance =  $50\Omega$ ) conditions.

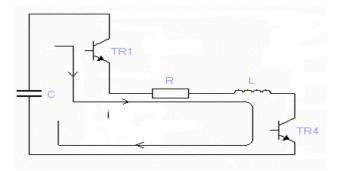

#### 2.4.2.1 Feed-Forward Control

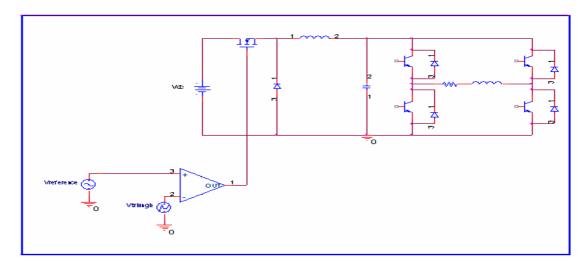

The schematic of the simulated circuit with open loop control is shown in figure 2.20 below. Firstly the resistive load and then inductive load is used in the simulations.

Figure 2.20 Circuit diagram for open loop analysis

The input of the circuit is rectified line voltage of 530V DC. Output is desired to be  $220V_{rms}$ , 50 Hz, sinusoidal voltage without any low or high frequency harmonics.

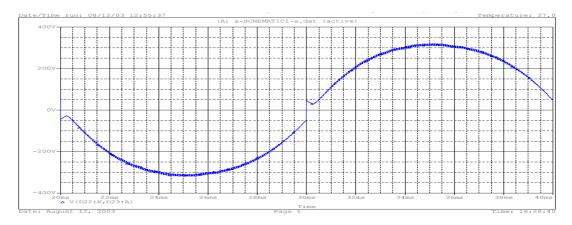

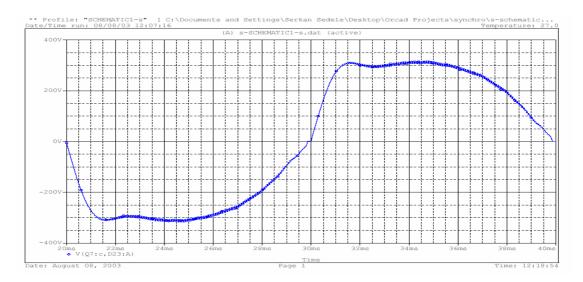

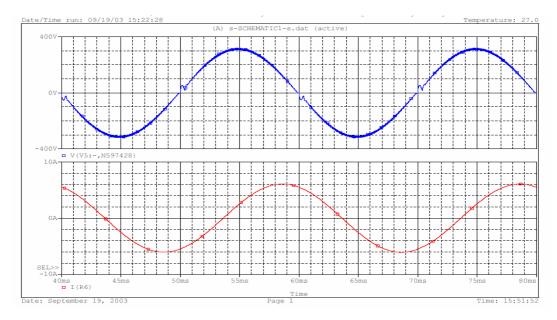

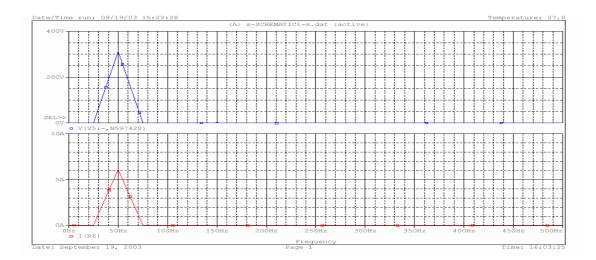

For a rectified sinusoidal reference voltage (feed-forward control) and for a purely resistive load of 50 $\Omega$ , the output voltage of the system for one period is shown in figure 2.21

Figure 2.21 Output voltage for full resistive load with open loop control

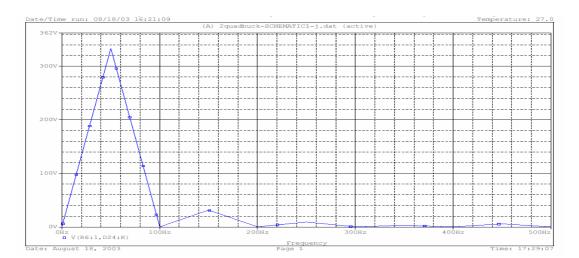

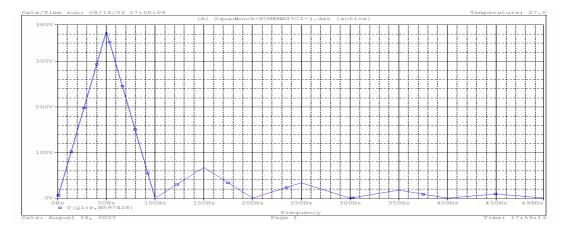

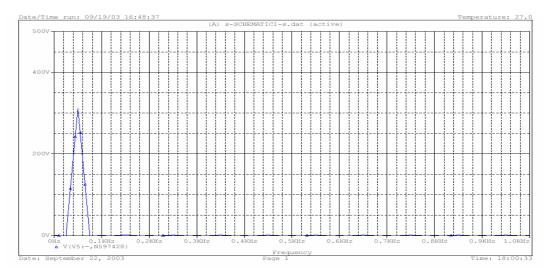

It is seen from the figure that, for purely resistive load, the output voltage tends to follow the reference sinusoidal input voltage. But it is obvious that the response of the system is not very well at lower voltage regions depending on the circuit dynamics. The harmonic diagram is shown in the figure 2.22. The representation of FFT in PSpice 9.0 is in the form of triangles with only their peak values indicate the amplitude of related harmonics. THD of the waveform shown in figure 2.21 is calculated approximately 11.37%.

Figure 2.22 Harmonic Spectrum of the output voltage (open loop control, resistive load).

The system shown in figure 2.20 is now simulated for inductive load. The load is now a combination of resistance and an inductance and is specified as  $50 \angle 20^{\circ}$  during the simulations.

The simulation has been run for inductive load and results are obtained. Output voltage and harmonic spectrum of the system with open loop control and with inductive load, is shown in Figs.2.23 and 2.24 respectively.

Figure 2.23 Output voltage for inductive load with open loop control

As it is seen in figure 2.23, the output voltage is far from being sinusoidal. As the load becomes inductive, a distortion occurs on the output voltage of the buck converter due to the inductive current flowing back to the capacitor. This phenomenon was discussed in section A.5.1.4 (choosing the best topology for output stage). Harmonic spectrum is shown in figure 2.24. THD of the waveform shown in figure 2.23 is calculated approximately 19.5%.

Figure 2.24 Harmonic Spectrum of the output voltage (open loop control, inductive load).

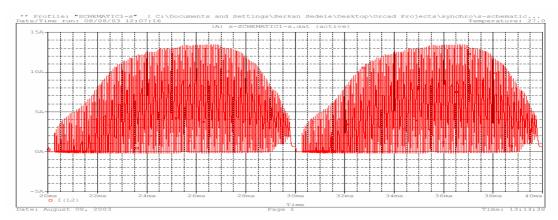

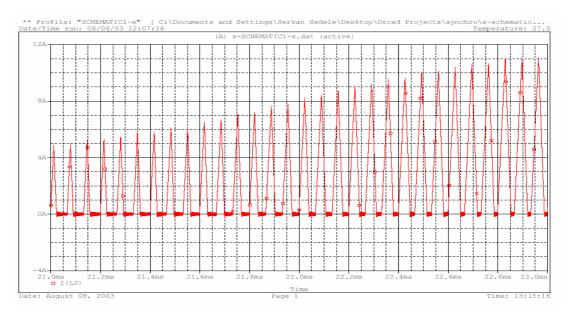

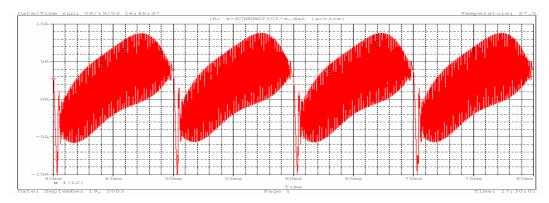

The inductor current for one period is shown in figure 2.25. Also a magnified version of figure 2.25 is given in figure 2.26. These waveforms show that the inductor current is both continuous and discontinuous in one period of operation.

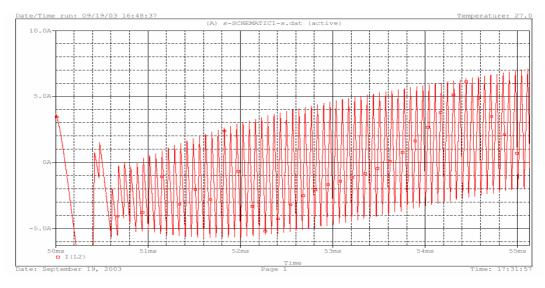

Figure 2.25 Buck Converter Inductor current for inductive load (open loop)

Figure 2.26 Buck Converter Inductor current for inductive load (open loop) Magnified.

Output voltages include lower order harmonics for both load types as seen in figures 2.22 and 2.24 resulting from inadequate dynamic response and in addition the distortion for inductive load case.

Another disadvantage of the open loop is poor voltage regulation capability resulting from the voltage drops of the semiconductor switches.

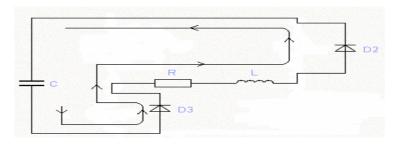

#### 2.4.2.2 Closed Loop Control

As a result of the feed-forward control technique gave unsatisfactory results, closed loop control is decided to be used in order to regulate the output voltage. Voltage feed-back is taken from the output filter capacitance of the DC-DC converter. Circuit schematic is shown in figure 2.27. System is again first simulated for resistive load and than for inductive load.

Figure 2.27 Circuit diagram for closed loop analysis

# 2.4.2.2.1 Determination of the Control Circuit Parameters Used for Closed loop Operation

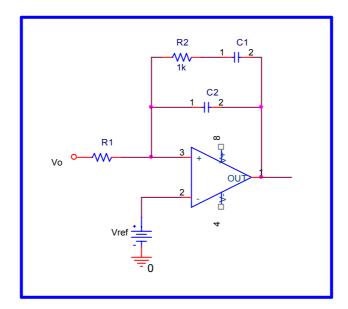

The buck converter output capacitor voltage, should track the reference voltage which is full-rectified sinusoids. So the capacitor voltage and the reference voltage are compared. Then the error is compensated by PI controller. An amplifier circuit used as PI regulator is shown in figure 2.28. The control signal is then applied to a PWM generator and the resultant signals become the switching signals of the buck converter's controllable switch. Determination of control circuit parameters for

a buck converter is discussed in [21] in detail. The foregoing analysis for the control circuit design is taken from [21].

Figure 2.28 Type 2 compensated error amplifier (PI Controller)

In order to determine the controller parameters, transfer function of the overall system must be obtained from the small signal averaged circuit. The transfer function is given in [21, 2] by Eq.2.52

$$\frac{Vo(s)}{Vc(s)} = \frac{Vs}{Vp \times L \times C} \left[ \frac{1 + sr_c C}{s^2 + s \left( \frac{1}{|X_L| \times C} + \frac{r_c + r_L}{L} \right) + \frac{1}{L \times C}} \right]$$

2.52

The crossover frequency can be calculated using the DC-DC converter inductance and the capacitance values in Eq.2.18 as

$$fc = \frac{1}{2\pi\sqrt{950 \times 10^{-6} \times 10 \times 10^{-6}}} = 1650 Hz$$

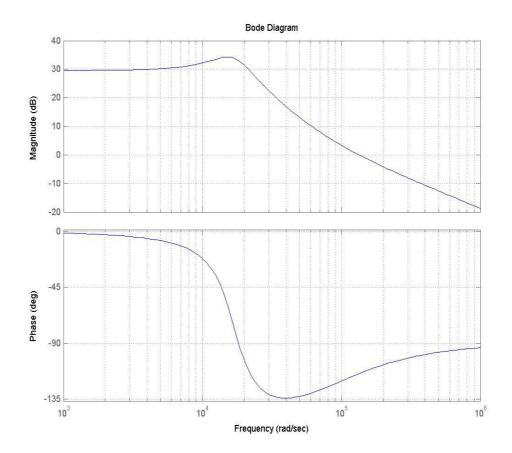

The frequency characteristics of the system is obtained with MATLAB as

#### shown in figure 2.29

Figure 2.29 Frequency response of the uncompensated system.

From the bode diagram it is seen that, the system gain at 1.65 kHz (10367 rad/s) is 4 dB with a phase angle of  $-120^{\circ}$ . The compensated error amplifier should have a gain of -4 dB at 1.65 kHz in order to make the loop gain 0 dB. Also phase margin is adjusted to be  $\cong 46^{\circ}$  in order to assure the stability [2, 21]

Therefore the resistance and the capacitance values of the compensated error amplifier shown in figure 2.28 are obtained as, R1= 1k $\Omega$ , R2= 6k $\Omega$ , C1=8nF, C2=1nF [21]

Using these parameters, the simulation has been run and results are obtained. Output voltage and harmonic spectrum of the system with closed loop control and purely resistive load is shown in Figs.2.30 and 2.31 respectively.

Figure 2.30. Output voltage for full resistive load with closed loop control

Figure 2.31 Harmonic Spectrum of the output voltage (closed loop control, resistive load).

For purely resistive load, THD of the waveform shown in figure 2.30 is calculated as 1.78%.

The system is now simulated for inductive load. The load is now a combination of resistance and an inductance and is specified as  $50 \angle 20^{\circ}$  during the simulations.

The simulation has been run and results are obtained. Output voltage, output current and harmonic spectrum of the system with closed loop control and with inductive load, is shown in Figs.2.32, 2.33 and 2.34 respectively.

Figure 2.32 Output voltage for inductive load with closed loop control

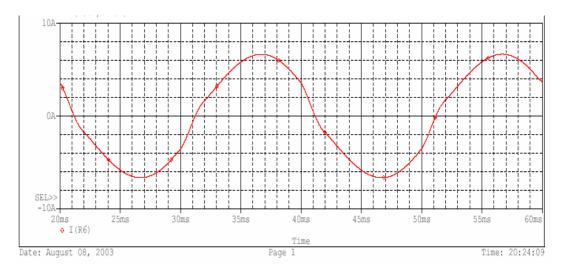

Figure 2.33 Output current for inductive load with closed loop control

Figure 2.34 Harmonic Spectrum of the output voltage and current (closed loop control, inductive load).

The distortion of the voltage is reduced but still exists in serious levels. During reactive current flowing, the control circuit turns off the switch at the DC-DC converter as shown in figure 2.35 but this could not be sufficient to suppress the over voltage. In figure 2.35, upper waveform in blue is output voltage, and the lower waveform in red is gate signals of the switch of the DC-DC converter.

THD of the waveform shown in figure 2.32 (output voltage), is calculated as 10%.

Figure 2.35 Output voltage and gate signal of the buck converter for closed loop control and inductive load.

To sum up, the simulations show that the reactive current distorts the sinusoidal shape of the output voltage. It was expected that, the closed loop control circuit would solve this problem. But even with the feed-back control, the overcharge could not be removed but decreased to a lower value than that obtained with open loop control, as shown in figure 2.32.

The problem is the nonlinear reactive current flowing through the capacitor, pumping up the capacitor voltage beyond the reference voltage.

The solution must be to provide an alternative path to the reactive current to prevent the over voltage on the capacitor. This can be done by some modifications on the conventional buck converter topology.

As conclusion, it is obvious that the proposed circuit topology is not sufficient especially for inductive loads and also for control point of view it is undesirable to operate the circuit in discontinuous conduction mode. The inverter part works properly but DC-DC buck converter part fails. The next section is devoted to solving this problem and a modified circuit topology for the DC-DC converter is proposed.

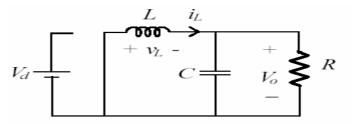

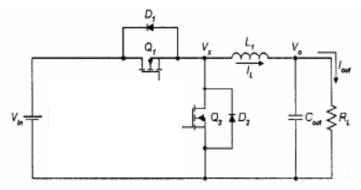

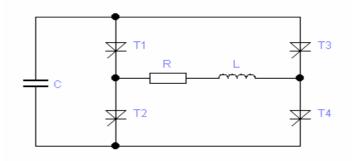

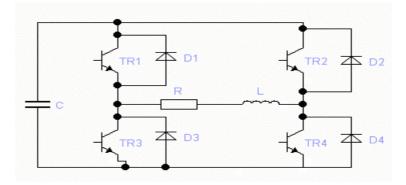

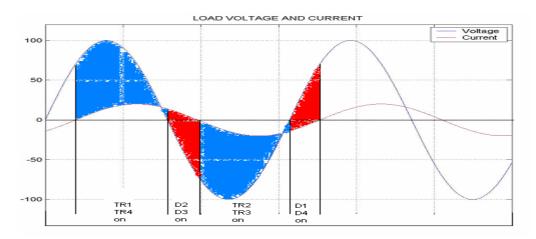

#### 2.4.3 Modified Circuit Topology

Two main drawbacks of the proposed system are defined in the previous section.

- The distortion of the "rectified DC-link" voltage.

- Control Complexity for discontinuous conduction mode.

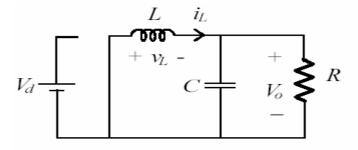

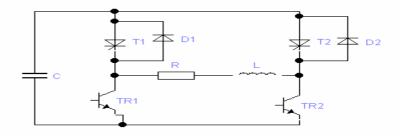

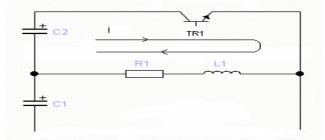

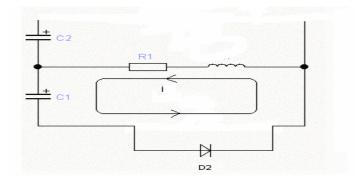

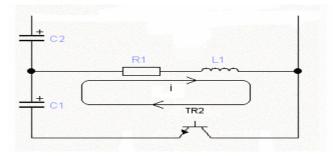

The circuit called complementary switching Buck Converter or two quadrant Buck Converter or so-called Synchronous Buck Rectifier is supposed to solve these two problems. The circuit schematic is shown in figure 2.36

Figure 2.36. Modified Circuit Topology

The advantage of this circuit is the inductance current of the synchronous buck rectifier will flow in both directions. So the circuit always operates in continuous conduction region. If the voltage on the output capacitor of the input stage tends to increase more then the reference voltage (as seen in previous sections) due to the inductive current flowing through it, the additional switch turns on and provides an alternative path for that current. So the distortion will be prevented

As a result of this, all conventional Buck Converter equations for continuous conduction mode of operation are valid for complementary switching Buck converter.

Since this circuit never operates in discontinuous region, the linear relationship between the input and output voltages of the input stage is guarantied for all type of loads.

Also the modified topology provides fast response to a load transient which is demanded by this application. [12]

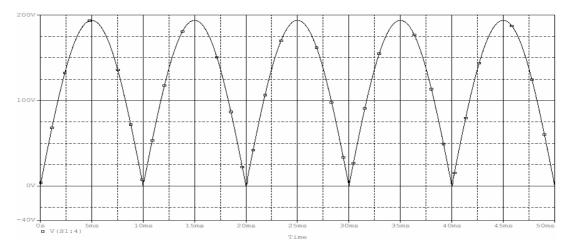

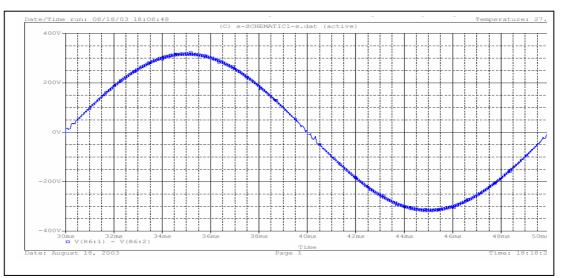

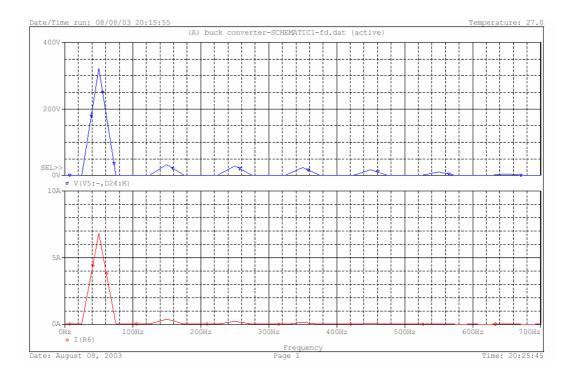

The modified topology is simulated for inductive load and the results are given in the figures below. The output voltage and current waveforms are shown in figure 2.37. Upper waveform is voltage and the lower one is current.

Figure 2.37 Output voltage and load current for inductive load with closed loop control. (Upper waveform is voltage and the lower one is the current).

Figure 2.38 Harmonic Spectrum of output voltage and load current for inductive load with closed loop control. (Upper waveform is voltage and the lower one is the current).

The FFT results shown in figure 2.38 show that the fundamentals of both voltage and current are at 50 Hz, beside these there are significantly small (negligible) lower order harmonics. Also figure 2.37 proves that the modified topology has solved the control complexity problem and the undesirable distortion on the rectified DC-link is eliminated.

THD of the waveform shown in figure 2.32 (output voltage), is calculated as 10%.

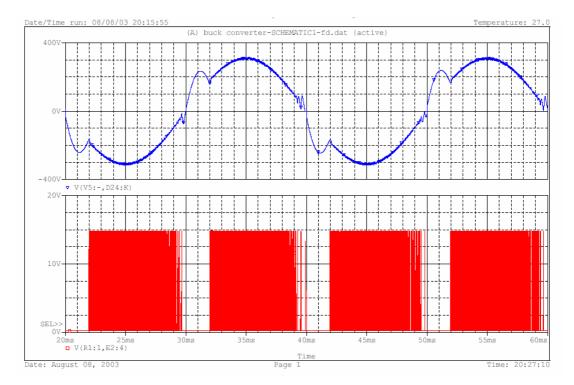

Fig 2.39 shows the inductance current of the buck converter. Also a magnified version of figure 2.39 is shown in figure 2.40.

Figure 2.39 Inductance current (modified topology)

Figure 2.40 Inductance current (magnified version of figure 2.60) (modified topology)

The advantage of the new modified topology can be clearly seen from figures.2.39 and 2.40. The inductance current can be bidirectional due to the additional switch. As a result of this, the reverse inductive current pumped from the output stage to the in put stage can be directed through this switch to either ground or to the input DC-link instead of it flows into the DC-DC converter filter capacitance. Thus the distortion is avoided.

### **CHAPTER 3**

## DETERMINATION OF THE DC-DC CONVERTER PARAMETERS

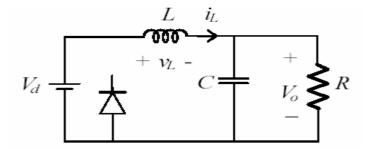

#### **3.1 Introduction**

In conventional buck converter (figure 3.1) design procedures, except for special applications, the inductance value L is chosen such that the inductance current is continuous. A minimum value of the inductance that satisfies the continuous conduction mode of operation can be calculated and selected as the criteria for the design, as discussed in section 2.3.3.2 and given by the formula

Figure 3.1 Conventional Buck Converter

However in our application the system always operates in continuous conduction mode as a result of the additional switch connected in parallel with diode D in figure 3.1, thus providing a path for the inductance current to flow in both directions as shown in figure 3.2 as discussed in section 2.4.3. So a "minimum

inductance value for continuous conduction mode" definition does not exist for the case. Another criterion should be defined for the inductance value.

Figure 3.2 Complementary Switching Buck Converter

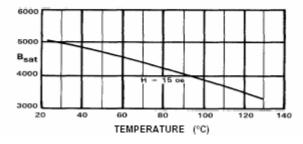

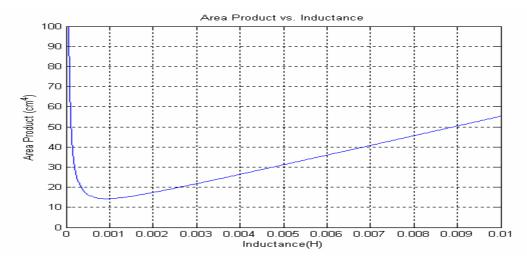

In this thesis study this criteria is defined as the physical volume of the inductor. After determining the inductance value, the capacitance value will be determined depending on the output voltage ripple specification.

#### **3.2 Inductance Design**

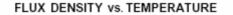

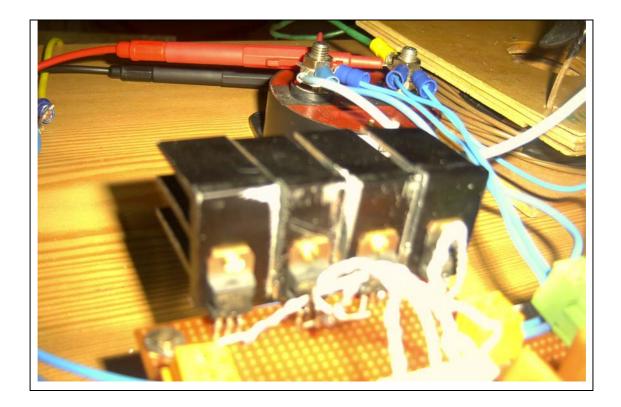

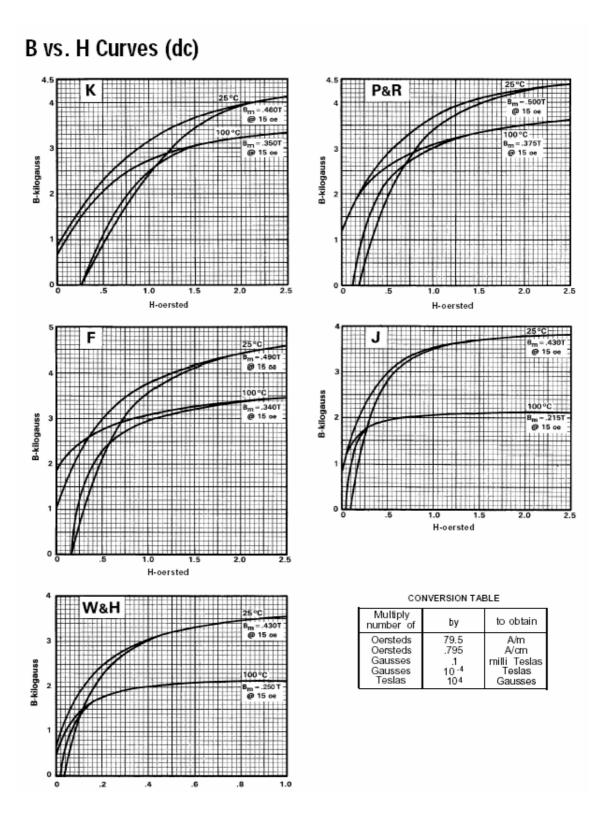

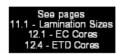

While starting the inductance design, the operating conditions of the circuit should be considered. The inductance used in this thesis is operating at high frequencies such as 15 kHz. In manufacturers application notes and data sheets [13, 14], ferrite E shaped cores are recommended for high frequency and medium power inductance and transformer design applications. The properties of some of E shaped ferrite cores that will be proper for our application are shown in table 3.1.

| to order<br>see Note<br>∳ | AL VALUES<br>MH/1000 Turns |                        |                        |                     |                       |                 |                         |               |                          |                       |                                      |                                        |

|---------------------------|----------------------------|------------------------|------------------------|---------------------|-----------------------|-----------------|-------------------------|---------------|--------------------------|-----------------------|--------------------------------------|----------------------------------------|

| PART                      | COMBI-                     |                        |                        | MATE                |                       |                 |                         | MINIMUM       |                          | SET                   | BOBBIN                               |                                        |

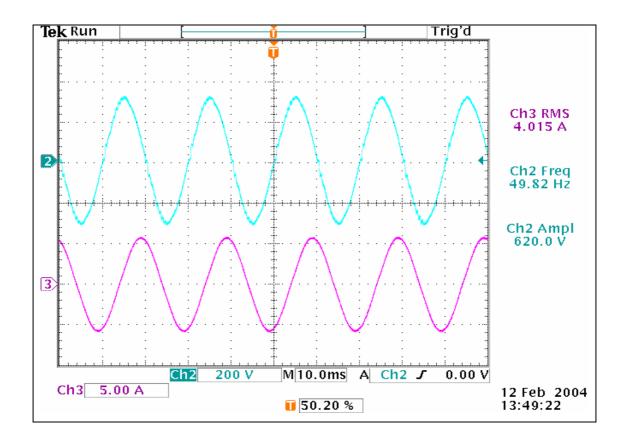

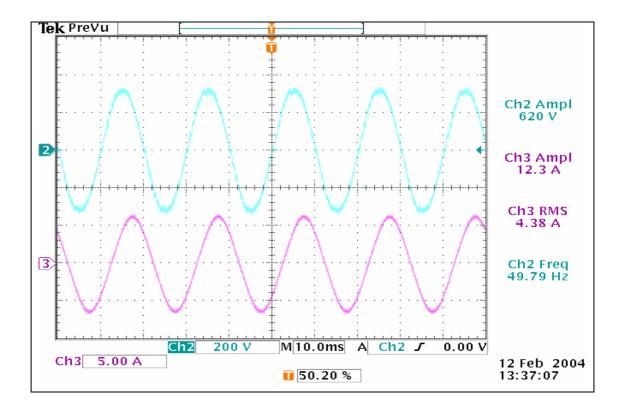

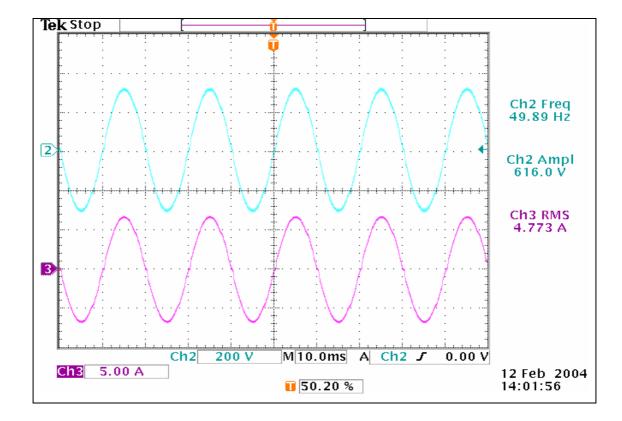

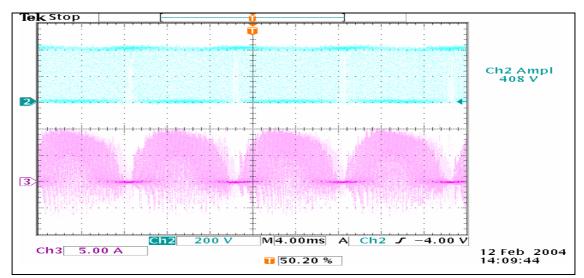

| NUMBER<br>(Note 1)        | NATION                     | μ μ2300<br>R<br>(min.) | μ μ2500<br>P<br>(min.) | μµ3000<br>F<br>±25% | μμ5000<br>J<br>(min.) | µ<br>İ₀<br>(cm) | A <sub>e</sub><br>(cm²) | AREA<br>(cm²) | Ve<br>(cm <sup>3</sup> ) | NOM.<br>Wit.<br>(gms) | WINDOW<br>AREA<br>(cm <sup>2</sup> ) | WaAc<br>(cm <sup>4</sup> )<br>(Note 2) |