# A REAL-TIME, LOW-LATENCY, FPGA IMPLEMENTATION OF THE TWO DIMENSIONAL DISCRETE WAVELET TRANSFORM

A THESIS SUBMITTED TO

### THE GRADUATE SCHOOL OF NATURAL AND APPLIED SCIENCES

OF

### THE MIDDLE EAST TECHNICAL UNIVERSITY

$\mathbf{B}\mathbf{Y}$

### OĞUZ BENDERLİ

# IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE

IN

### THE DEPARTMENT OF ELECTRICAL AND ELECTRONICS ENGINEERING

AUGUST 2003

Approval of the Graduate School of Natural and Applied Sciences

Prof. Dr. Canan Özgen Director

I certify that this thesis satisfies all the requirements as a thesis for the degree of Master of Science.

Prof. Dr. Mübeccel Demirekler Head of Department

This is to certify that we have read this thesis and that in our opinion it is fully adequate in scope and quality, as a thesis for the degree of Master of Science.

Assist. Prof. Dr. Yusuf Çağatay Tekmen Supervisor

**Examining Committee Members**

Prof. Dr. Murat Aşkar (Chairman)

Assoc. Prof. Dr. Tayfun Akın

Assoc. Prof. Dr. Aydın Alatan

Assist. Prof. Dr. Yusuf Çağatay Tekmen

A. Neslin İsmailoğlu M.S. in EE

### ABSTRACT

# A REAL-TIME, LOW-LATENCY, FPGA IMPLEMENTATION OF THE TWO DIMENSIONAL DISCRETE WAVELET TRANSFORM

Benderli, Oğuz

M.S., Department of Electrical and Electronics Engineering

Supervisor: Assist. Prof. Dr. Yusuf Çağatay Tekmen

August 2003, 146 pages

This thesis presents an architecture and an FPGA implementation of the two dimensional discrete wavelet transformation (DWT) for applications where rowbased raw image data is streamed in at high bandwidths and local buffering of the entire image is not feasible. The architecture is especially suited for multi-spectral imager systems, such as on board an imaging satellite, however can be used in any application where time to next image constraints require real-time processing of multiple images. The latency that is introduced as the images stream through the DWT module and the amount of locally stored image data, is a function of the image and tile size. For an  $n_1 \times n_2$  size image processed using  $(n_1/k_1) \times (n_2/k_2)$  sized tiles the latency is equal to the time elapsed to accumulate a  $(1/k_1)$  portion of one image. In addition, a  $(2/k_1)$  portion of each image is buffered locally. The proposed hardware has been implemented on an FPGA and is part of a JPEG 2000 compression system designed as a payload for a low earth orbit (LEO) microsatellite to be launched in September 2003. The architecture can achieve a throughput of up to 160Mbit/s. The latency introduced is 0.105 sec (6.25% of total transmission time) for tile sizes of 256×256. The local storage size required for the tiling operation is 2 MB. The internal storage requirement is 1536 pixels. Equivalent gate count for the design is 292,447.

Keywords: JPEG 2000, Wavelet Transform, FPGA, Multispectral Imaging, Image Processing

# İKİ BOYUTLU AYRIK DALGACIK DÖNÜŞÜMÜNÜN, GERÇEK ZAMANLI VE DÜŞÜK GECİKMELİ OLARAK, FPGA UZERINDE GERÇEKLEŞTİRİLMESİ

Benderli, Oğuz

Yüksek Lisans, Elektrik ve Elektronik Mühendisliği Bölümü

Tez Yöneticisi: Yrd. Doç. Dr. Yusuf Çağatay Tekmen

Ağustos 2003, 146 sayfa

Bu tezde, satır tabanlı ham görüntü verisinin yüksek bant genişliğinde duraksız iletildiği ve tüm veriyi yerel bellekte saklamanın mümkün olmadığı uygulamalara yönelik, iki boyutlu ayrık dalgacık dönüşümü (ADD) mimarisi ve FPGA gerçekleştirimi sunulmaktadır. Mimari, özellikle görüntüleme uydusu üzerinde bulunan çok bantlı görüntüleme sistemleri için uygun olup, birden fazla görüntünün gerçek zamanlı işlenmesini gerektiren ve görüntüler arası zamanlama kısıtının

ÖZ

olduğu uygulamalar için de kullanılabilir. Görüntüler ADD modülünden geçerken oluşan gecikme ve yerel olarak saklanması gereken görüntü verisi miktarı, görüntü ve parsel büyüklüğünün bir fonksiyonudur.  $(n_1/k_1) \times (n_2/k_2)$  büyüklüğündeki parsellerle işlenen  $n_1 \times n_2$  büyüklüğündeki bir görüntü için, gecikme zamanı, tüm resmin  $(1/k_1)$  kadarlık bölümünün biriktirilmesi için geçen zaman kadardır. Ayrıca, tüm resmin  $(2/k_1)$  kadarlık bölümü yerel olarak saklanmaktadır. Önerilen donanım, bir FPGA üzerinde gerçekleştirilmiştir ve Eylül 2003 tarihinde fırlatılıcak olan alçak yörüngeli bir mikro uydu için faydalı yük olarak tasarlanmış bir JPEG 2000 resim sıkıştırma sisteminin parçasıdır. Mimari 160 Mbits/s'e kadar veri işleyişi sağlayabilmektedir. 256×256'lık parsel boyutu için eklenen gecikme zamanı 0.105 saniyedir (Tüm iletim zamanının %6.25'i). Parselleme işlemi için gereken yerel bellek miktarı 2 MB'dir. İç bellek ihtiyacı ise 1536 pikseldir. Tasarımın eşdeğer geçit sayısı 292,447'dir.

Anahtar Kelimeler: JPEG 2000, Dalgacık Dönüşümü, FPGA, Çok Bantlı Görüntüleme, Görüntü İşleme

### ACKNOWLEDGMENTS

This thesis would never have been written without the generous help and support that I received from numerous people along the way. I would now like to take this opportunity to express my sincerest thanks to these individuals.

First, I would like to express my appreciation to my supervisor Assist. Prof. Dr. Çağatay TEKMEN for his guidance and helpful comments in the development of this thesis. He has always been patient and supportive. Most of all, however, I would like to thank him for always having confidence in me and my abilities, even when I did not.

I would also like to express my acknowledgements and gratitude to Prof. Dr. Murat Aşkar, especially for his initiative role in the micro satellite and micro satellite payload projects of TÜBİTAK – BİLTEN. If it were not for him, this thesis would never have been started.

I would be remiss if I also did not thank my colleagues in TÜBİTAK – BİLTEN; first of all to my coordinator Neslin İsmailoğlu for her support and understanding throughout my thesis; to Soner Yeşil, Taner Kolçak, Ilgaz Korkmaz, Hacer Sunay and Refik Sever, who shared their bests in the GEZGIN project. I also wish to thank to TÜBİTAK-BİLTEN for facilities provided for the completion of this thesis.

I would also like to express my deep gratitude to my sincere friends, and my family for their continuous support, patience and encouragement.

to the memory of M. Emin Özkan

# **TABLE OF CONTENTS**

| ABS  | <b>FRA</b> | СТ                                                          | iii  |

|------|------------|-------------------------------------------------------------|------|

| ÖZ   | •••••      |                                                             | V    |

| ACK  | NOV        | VLEDGMENTS                                                  | vii  |

| TAB  | LE O       | DF CONTENTS                                                 | ix   |

| LIST | OF         | TABLES                                                      | xiii |

| LIST | OF         | FIGURES                                                     | XV   |

| LIST | OF         | ABBREVIATIONS                                               | xxi  |

| CHA  | РТЕ        | R                                                           |      |

| 1.   | INT        | RODUCTION                                                   | 1    |

|      | 1.1        | Image Compression                                           | 3    |

|      | 1.2        | Wavelet Basics                                              | 6    |

|      |            | 1.2.1 Application of Wavelet Transform in Image Compression | 8    |

|      |            | 1.2.2 Factoring Wavelet Transforms into Lifting Steps       | 15   |

|      | 1.3        | A New Image Compression Standard : JPEG 2000                | 17   |

|      |            | 1.3.1 JPEG 2000 Coding Algorithm                            | 19   |

|      | 1.4        | GEZGIN: A JPEG 2000 Compression Sub-system On-board         |      |

|      |            | BILSAT-1                                                    | 21   |

| 2.   | HAF        | RDWARE IMPLEMENTATIONS OF 2-D DISCRETE WAVELI               | ET   |

|      | TRA        | ANSFORMS, A LITERATURE REVIEW                               | 23   |

|      | 2.1        | 1-D DWT Architectures                                       | 23   |

|    |     | 2.1.1   | Recursive Pyramid Algorithm Implementations       | 24 |

|----|-----|---------|---------------------------------------------------|----|

|    |     | 2.1.2   | One Dimensional RPA Architectures                 | 25 |

|    |     |         | 2.1.2.1. Systolic/Semi-systolic Architectures     | 26 |

|    |     |         | 2.1.2.2. Memory-Based Implementations             | 28 |

|    |     |         | 2.1.2.3. Parallel Filtering                       |    |

|    | 2.2 | 2-D N   | Iallat Tree Decomposition Architectures           | 29 |

|    |     | 2.2.1   | Whole Image Storing Structures                    | 30 |

|    |     |         | 2.2.1.1. Direct Approach                          | 30 |

|    |     |         | 2.2.1.2. Single Instruction Multiple Data (SIMD)  |    |

|    |     |         | Architectures                                     | 31 |

|    |     | 2.2.2   | Memory Optimized Architectures                    | 33 |

|    |     |         | 2.2.2.1. Parallel Filter Algorithms               | 33 |

|    |     |         | 2.2.2.2. Non-Separable Filtering Architectures    | 37 |

|    |     |         | 2.2.2.3. Systolic-Parallel Architectures          |    |

|    |     |         | 2.2.2.4. Row-parallel RPA Architectures           |    |

|    |     |         | 2.2.2.5. Lattice Architecture                     | 41 |

|    |     |         | 2.2.2.6. Level-by-level transforming              | 42 |

|    |     |         | 2.2.2.7. Quadri-filter                            | 44 |

|    | 2.3 | Summ    | nary and Comparisons on Mallat Tree Architectures | 48 |

| 3. | AR  | EAL-T   | IME, LOW-LATENCY FPGA IMPLEMENTATION              | OF |

|    | THE | E 2-D V | VAVELET TRANSFORM                                 | 55 |

|    | 3.1 | Input   | Data Stream Format and Notation                   | 56 |

|    | 3.2 | DC-L    | evel Shift                                        | 57 |

|    | 3.3 | Color   | Transform                                         | 57 |

|    | 3.4 | Liftin  | g Implementation                                  | 59 |

|    | 3.5 | Symm    | netric Extension in Lifting Steps                 | 68 |

|    | 3.6 | Tiling  |                                                   | 73 |

|    | 3.7 | Casca   | de Filter Structure                               | 80 |

|    |     | 3.7.1   | Horizontal Filter                                 | 81 |

|    |     | 3.7.2   | Vertical Filter                                   | 83 |

|    |     | 3.7.3   | Memory Requirements                               | 85 |

|     | 3.7.4                                                                                   | Output Bandwidth Considerations                                                                                                                                                                                                                                                                                            | 87                                                       |

|-----|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| 3.8 | Precis                                                                                  | sion and Channel Constraints                                                                                                                                                                                                                                                                                               | 89                                                       |

| IMP | LEME                                                                                    | ENTATION AND EXPERIMENTAL RESULTS                                                                                                                                                                                                                                                                                          | 92                                                       |

| 4.1 | FPGA                                                                                    | A Implementation                                                                                                                                                                                                                                                                                                           | 92                                                       |

|     | 4.1.1                                                                                   | Specifications                                                                                                                                                                                                                                                                                                             | 93                                                       |

|     | 4.1.2                                                                                   | FPGA Operation Environment                                                                                                                                                                                                                                                                                                 | 94                                                       |

|     | 4.1.3                                                                                   | Design                                                                                                                                                                                                                                                                                                                     | 95                                                       |

|     |                                                                                         | 4.1.3.1. Design Environment                                                                                                                                                                                                                                                                                                | 95                                                       |

|     |                                                                                         | 4.1.3.2. Synthesized Chip                                                                                                                                                                                                                                                                                                  | 95                                                       |

|     | 4.1.4                                                                                   | Overall Architecture                                                                                                                                                                                                                                                                                                       | 97                                                       |

|     | 4.1.5                                                                                   | Power, Timing and Test Subjecting                                                                                                                                                                                                                                                                                          | 100                                                      |

| 4.2 | Comp                                                                                    | parisons                                                                                                                                                                                                                                                                                                                   | 102                                                      |

|     | 4.2.1                                                                                   | Resource Used                                                                                                                                                                                                                                                                                                              | 102                                                      |

|     | 4.2.2                                                                                   | JPEG 2000 Achievement                                                                                                                                                                                                                                                                                                      | 103                                                      |

| 4.3 | Resul                                                                                   | ts                                                                                                                                                                                                                                                                                                                         | 108                                                      |

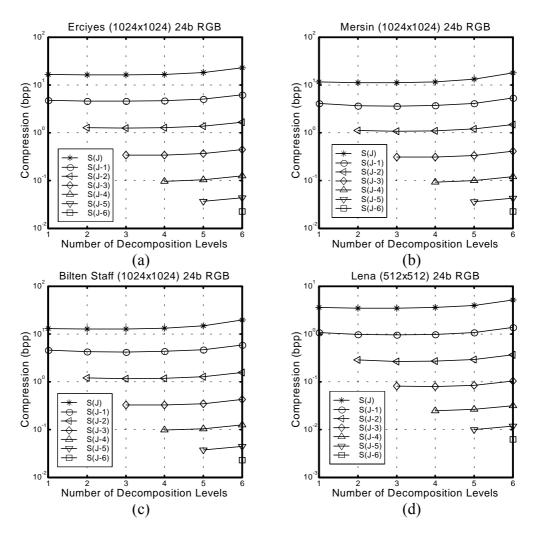

|     | 4.3.1                                                                                   | Levels of Sub-band decomposition                                                                                                                                                                                                                                                                                           | 108                                                      |

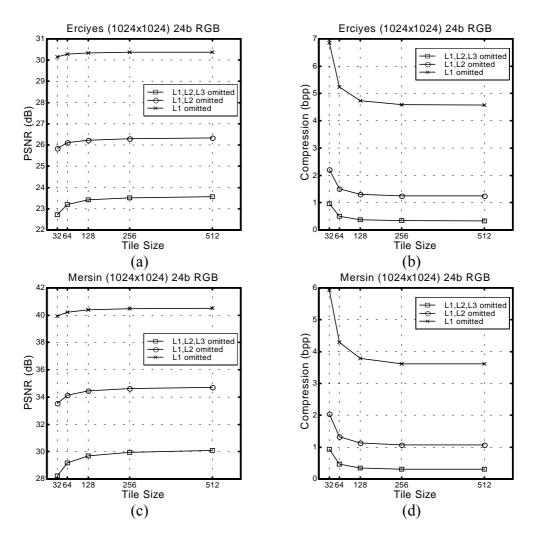

|     | 4.3.2                                                                                   | Tile Size                                                                                                                                                                                                                                                                                                                  | 109                                                      |

|     | 4.3.3                                                                                   | Coefficient Truncation                                                                                                                                                                                                                                                                                                     | 111                                                      |

|     | 4.3.4                                                                                   | Compression Time Experiments                                                                                                                                                                                                                                                                                               | 113                                                      |

|     | 4.3.5                                                                                   | Dynamic Range Expansion at the RCT output                                                                                                                                                                                                                                                                                  | 116                                                      |

|     | 4.3.6                                                                                   | Blocking Artifacts                                                                                                                                                                                                                                                                                                         | 117                                                      |

| COI | NCLUS                                                                                   | SION                                                                                                                                                                                                                                                                                                                       | 124                                                      |

| ERE | NCES.                                                                                   |                                                                                                                                                                                                                                                                                                                            |                                                          |

|     |                                                                                         |                                                                                                                                                                                                                                                                                                                            |                                                          |

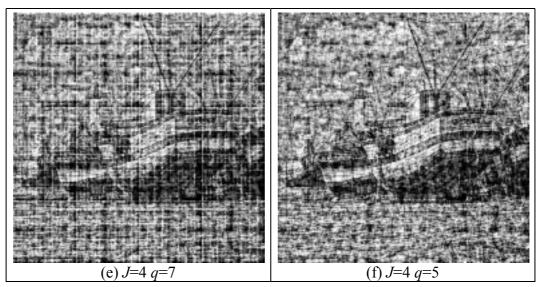

| DES | SIGN H                                                                                  | IIEARCHY                                                                                                                                                                                                                                                                                                                   | 136                                                      |

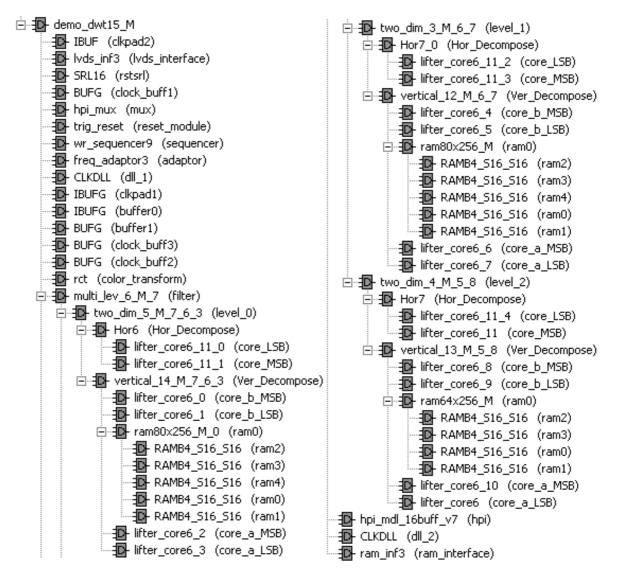

| VIR | TEX-E                                                                                   | C RESOURCES                                                                                                                                                                                                                                                                                                                | 139                                                      |

| B.1 |                                                                                         |                                                                                                                                                                                                                                                                                                                            |                                                          |

| B.2 |                                                                                         |                                                                                                                                                                                                                                                                                                                            |                                                          |

| B.3 |                                                                                         | · · /                                                                                                                                                                                                                                                                                                                      |                                                          |

| B.4 |                                                                                         |                                                                                                                                                                                                                                                                                                                            |                                                          |

|     | IMP<br>4.1<br>4.2<br>4.2<br>4.3<br>CON<br>ERE<br>END<br>DES<br>VIR<br>B.1<br>B.2<br>B.3 | 3.8 Precis<br>IMPLEMH<br>4.1 FPGA<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>4.1.3<br>4.1.4<br>4.1.5<br>4.2 Comp<br>4.2.1<br>4.2.2<br>4.3 Resul<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.3.5<br>4.3.3<br>4.3.4<br>4.3.5<br>4.3.6<br>CONCLUS<br>ERENCES<br>ENDIX<br>DESIGN H<br>VIRTEX-H<br>B.1 Archi<br>B.2 Confi<br>B.3 Looks | <ul> <li>3.8 Precision and Channel Constraints</li></ul> |

| B.5 | Arithmetic Logic (CYs)                    | .143 |

|-----|-------------------------------------------|------|

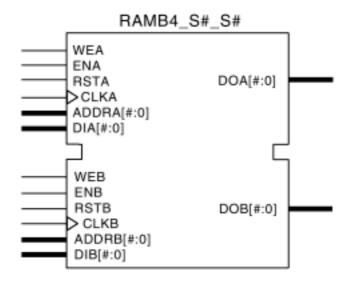

| B.6 | Block SelectRAM (BRAM)                    | .143 |

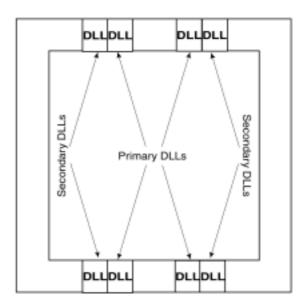

| B.7 | Digital Delay-Locked Loop (DLL)           | .144 |

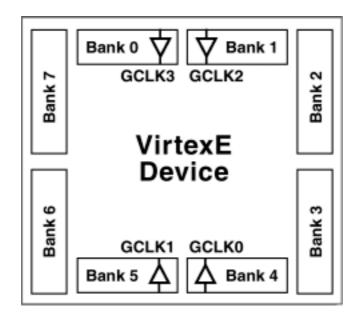

| B.8 | Global Clock Routing (GCLKs and GCLKIOBs) | .145 |

# LIST OF TABLES

## TABLE

| 2.1 | Comparisons of 2-D DWT Architectures (I)                                                          |

|-----|---------------------------------------------------------------------------------------------------|

| 2.2 | Comparisons of 2-D DWT Architectures (II)                                                         |

| 2.3 | Comparisons of 2-D DWT Architectures (III)                                                        |

| 4.1 | Resources used in DWT module and resources available in XCV300EPQ240 chip                         |

| 4.2 | Detailed resource usage of the hierarchical modules                                               |

| 4.3 | BRAM modules required in each level for various implementations for $n_1/n_2=n_2/k_2=N$ and $P=2$ |

| 4.4 | Clock groups                                                                                      |

| 4.5 | Maximum path delays for clock groups101                                                           |

| 4.6 | Estimated power consumption                                                                       |

| 4.7 | Resource used by 2-D DWT processor implemented for GEZGİN and various 2-D DWT architectures       |

| 4.8  | Lossless compression performance of PNG, LS and JPEG 2000.                                               |

|------|----------------------------------------------------------------------------------------------------------|

|      | JPEG2000 results are obtained using GEZGIN Test and Decoder Suite                                        |

|      | v1.0 [67]                                                                                                |

| 4.9  | Time required to process image and achieved distortion, bit-rate for various options available in GEZGIN |

| 4.10 | Quality achievement of quantizing and clamping of color transformed samples                              |

| B.1  | Depth and width aspect ratios available for the RAM blocks                                               |

# LIST OF FIGURES

### FIGURE

| 1.1. | One dimensional forward and inverse wavelet transform. Each QMF pair        |

|------|-----------------------------------------------------------------------------|

|      | consists of a low-pass filter, H, and a high-pass filter, G which split the |

|      | input signal's bandwidth in half                                            |

| 1.2. | Two dimensional separable forward wavelet transform                         |

| 1.3. | Dyadic (Mallat Tree) Wavelet Transform. In wavelet compression, the         |

|      | average signal is usually recursively transformed to higher levels          |

| 1.4. | Pass-band structure of Sub-bands for three level wavelet transform          |

| 1.5. | 2-D Wavelet Transform outputs: (a) A natural image, (b) A checkerboard      |

|      | test pattern. The vertical edges and temporal changes along horizontal      |

|      | direction are emphasized in HL sub-band, whereas horizontal edges and       |

|      | temporal changes along vertical direction are emphasized in LH sub-         |

|      | band. The LL sub-band, the average signal, contains the coarse              |

|      | information of the image                                                    |

| 1.6. | Two dimensional inverse wavelet transform14                                 |

| 1.7. | Polyphase representation of wavelet transform. The input signal s is first  |

|      | split into even and odd parts, then the polyphase matrix is applied to the  |

|      | signals                                                                     |

|      |                                                                             |

| 1.8.  | Lifting steps implementation of wavelet transform                        | 17 |

|-------|--------------------------------------------------------------------------|----|

| 1.9.  | Block diagram of JPEG 2000 coding algorithm                              | 19 |

| 2.1.  | Pseudo code for RPA                                                      | 25 |

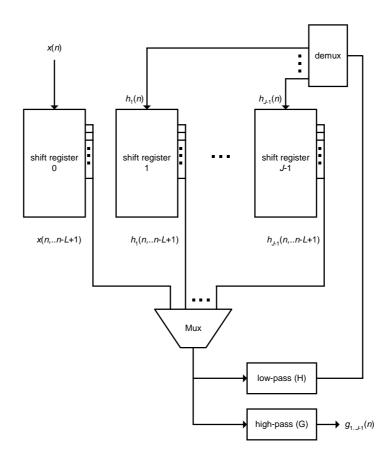

| 2.2.  | One dimensional RPA Architecture proposed by Knowles                     | 26 |

| 2.3.  | Systolic Architecture of Vishvanath                                      | 27 |

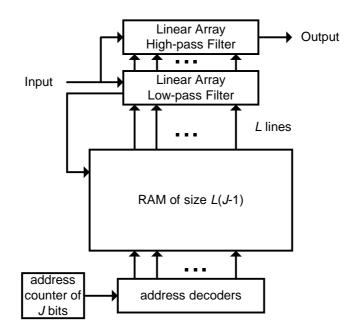

| 2.4.  | RAM based implementation of systolic architecture                        | 28 |

| 2.5.  | Parallel filter architecture                                             | 29 |

| 2.6.  | Direct Approach                                                          | 31 |

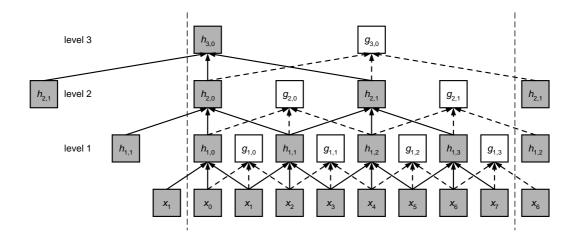

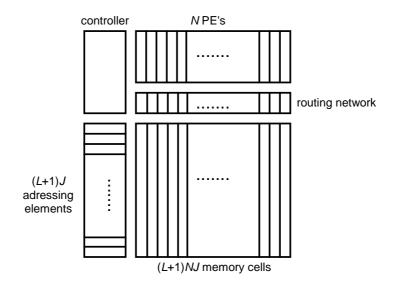

| 2.7.  | Interconnections of the 'active' processors for three stages where $N=8$ | 32 |

| 2.8.  | Intermediate outputs of the processors                                   | 33 |

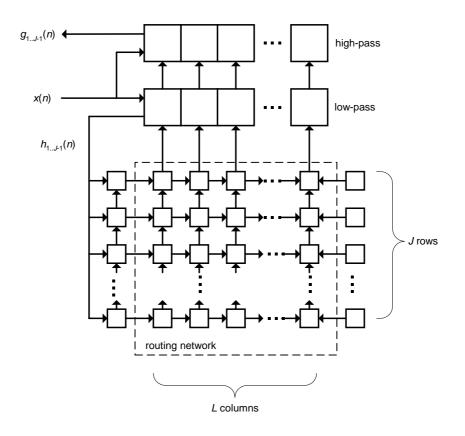

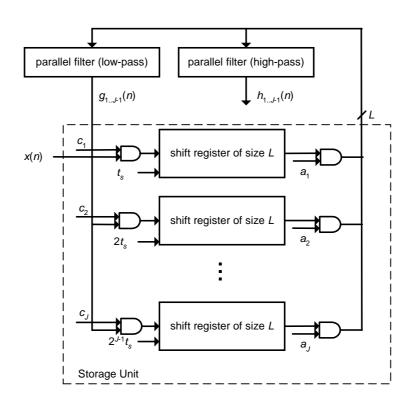

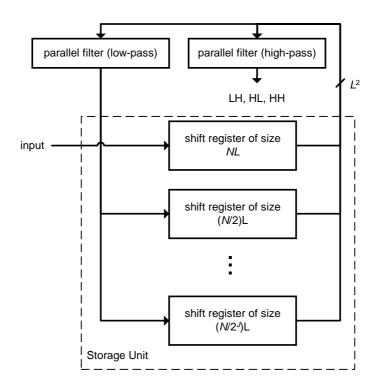

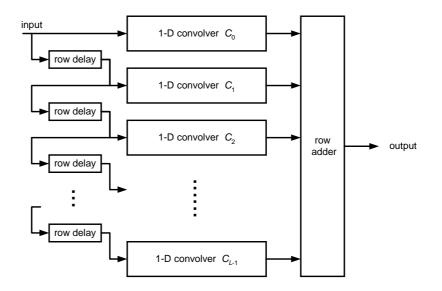

| 2.9.  | Two dimensional parallel filter architecture I of Chakrabarti et al      | 34 |

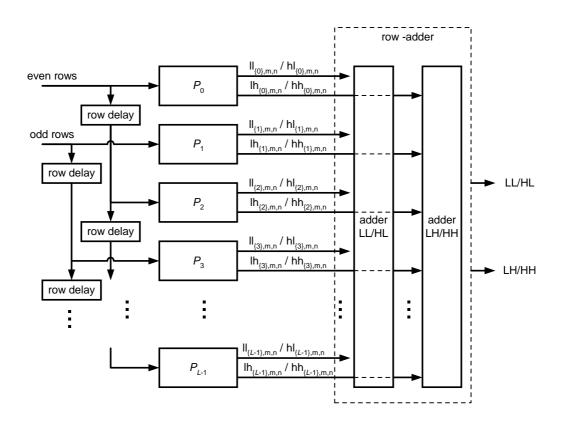

| 2.10. | Two dimensional parallel filter architecture II of Chakrabarti et al     | 35 |

| 2.11. | Semi-recursive pyramid algorithm architecture of Masud <i>et al</i>      | 36 |

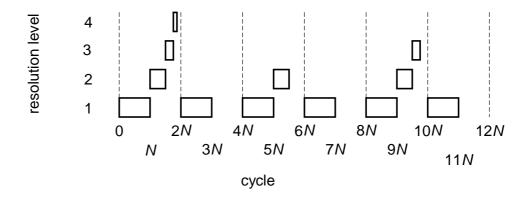

| 2.12. | Scheduling of semi-recursive architecture                                | 37 |

| 2.13. | Non-separable filter architecture                                        | 38 |

| 2.14. | Systolic-parallel architecture                                           | 39 |

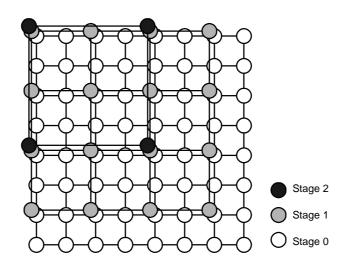

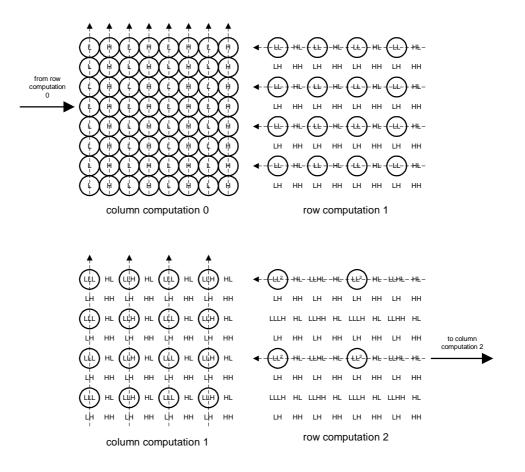

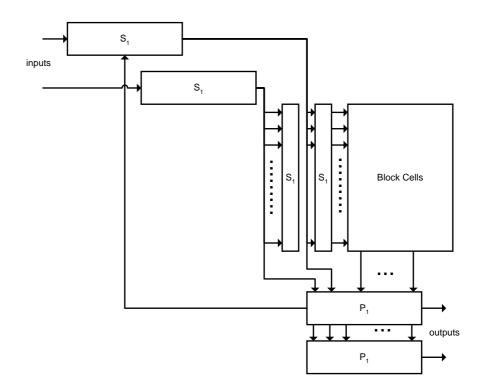

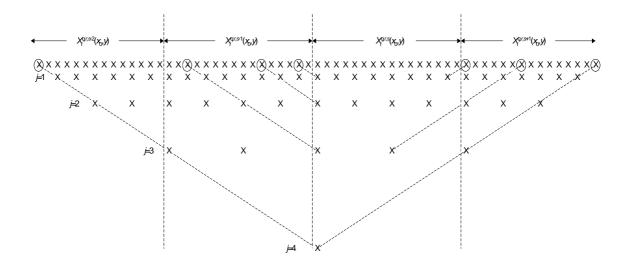

| 2.15. | Row-parallel processing for three levels and image size of 8             | 40 |

| 2.16. | Row-parallel architecture                                                | 41 |

| 2.17. | (a) Lattice architecture. (b) Processing element.                        | 42 |

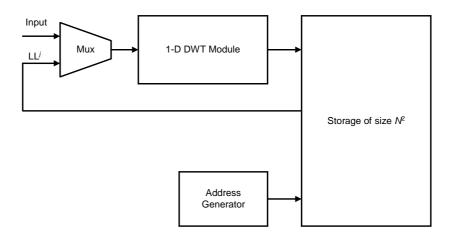

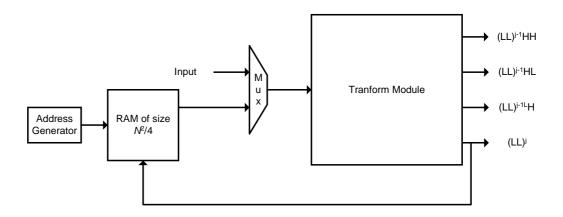

| 2.18. | Level-by-level transforming architecture                                 | 43 |

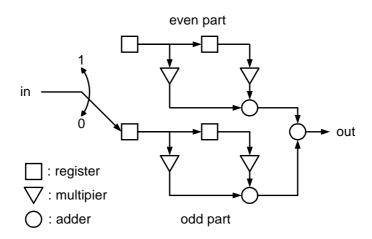

| 2.19. | Splitted signal implementation                                                                                                                                                        | .44  |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 2.20. | 2-D convolver having $L \times M$ taps                                                                                                                                                | .45  |

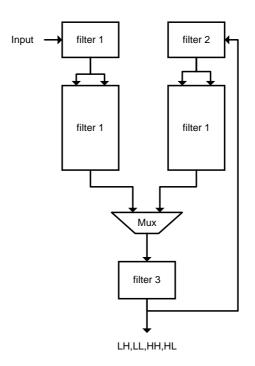

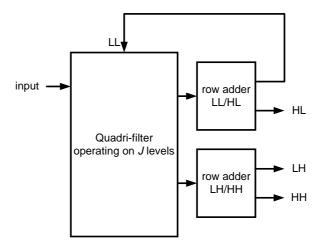

| 2.21. | Quadri-filter structure                                                                                                                                                               | .46  |

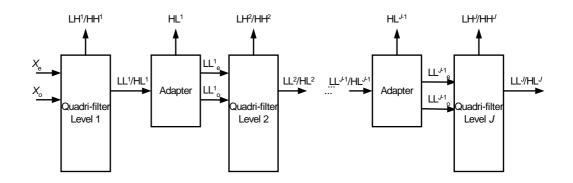

| 2.22. | Folded architecture with quadri-filters                                                                                                                                               | .47  |

| 2.23. | Pipe-lined architecture with quadri-filters                                                                                                                                           | .48  |

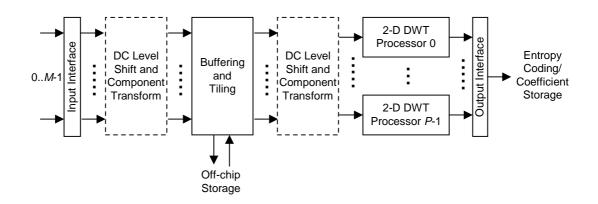

| 3.1.  | Block diagram of the DWT processor                                                                                                                                                    | . 55 |

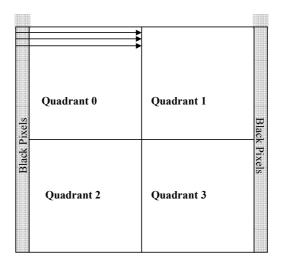

| 3.2.  | Image data acquisition with quadrants. On both sides of the image there are $\beta$ pixels wide stripes which contain no information other than black pixels.                         | . 56 |

| 3.3.  | Lifting realization with causal filters                                                                                                                                               | . 62 |

| 3.4.  | Delay lines of lifting implementation                                                                                                                                                 | .63  |

| 3.5.  | Modified delay line structure                                                                                                                                                         | . 64 |

| 3.6.  | Lifting structure of 5/3 filtering. (a) Odd samples lag even samples, (b) Even samples lag odd samples                                                                                | .67  |

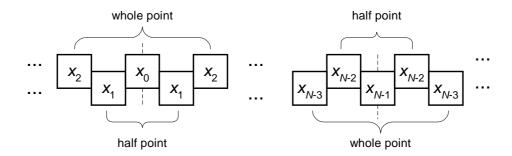

| 3.7.  | Symmetric extensions: (a) Whole point (b) Half point                                                                                                                                  | .68  |

| 3.8.  | Application of symmetric extension to even-length signals                                                                                                                             | . 69 |

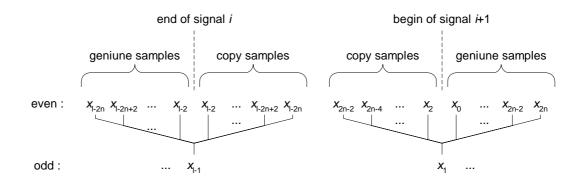

| 3.9.  | Symmetric extension applied to consecutive signals                                                                                                                                    | .71  |

| 3.10  | The buffer content at the joint of two consecutive signals where $l=16$ and $2n=8$                                                                                                    | .72  |

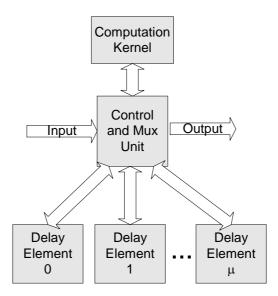

| 3.11. | The elements of a filter architecture for lifting                                                                                                                                     | .73  |

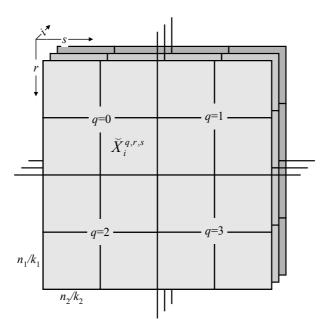

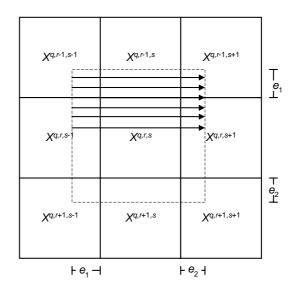

| 3.12. | Application of tiling to the image components. Each frame $\breve{X}_i$ is divided into tiles forming a tile matrix. The tile $\breve{X}_i^{q,r,s}$ , which is on the <i>r</i> th row |      |

| and sth column of the qth quadrant (if quadrants are used) of the tile<br>matrix, is assigned a global-tile index g and is equal to a portion $\pi$ of a<br>"global-tile", $T_g(\pi=0P-1)$ |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.13. Overlap reading for one-dimensional transform for $r=16$ , $a=2$ and $b=1$ 78                                                                                                        |

| 3.14. Overlap reading for two dimensional transform                                                                                                                                        |

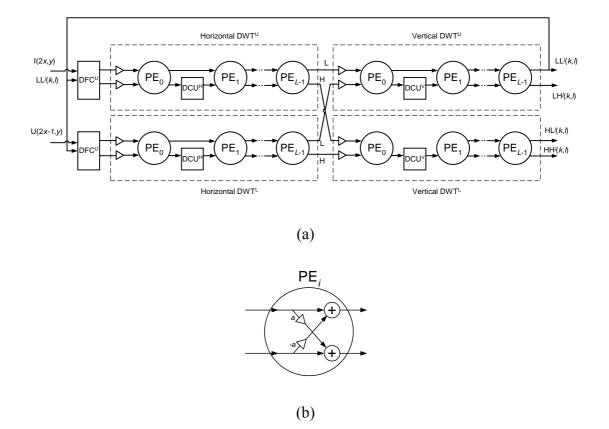

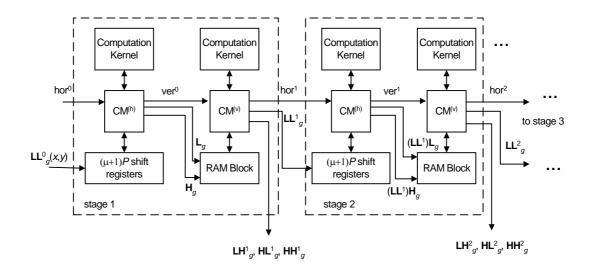

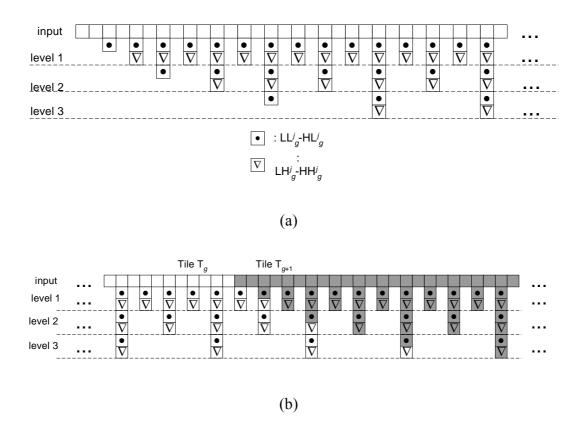

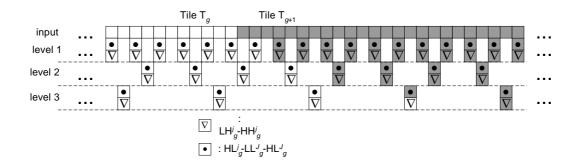

| 3.15. Proposed cascaded filter architecture                                                                                                                                                |

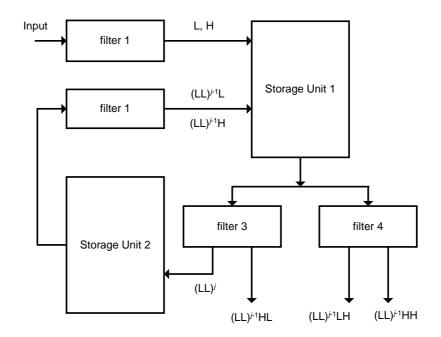

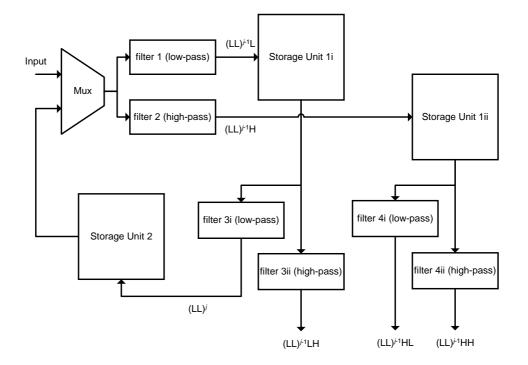

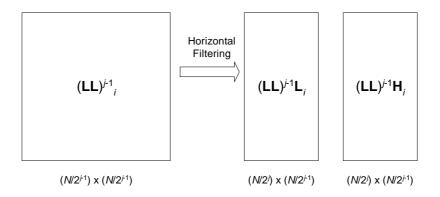

| 3.16. Horizontal filtering and decomposition of LL subband                                                                                                                                 |

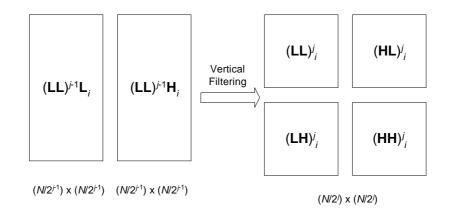

| 3.17. Vertical filtering and decomposition of (LL)H and (LL)L subbands                                                                                                                     |

| 3.18. Output timing diagrams of three cascaded 2-D filters. (a) for $g=0$ , (b)                                                                                                            |

| for 0< <i>g</i> < <i>Z</i>                                                                                                                                                                 |

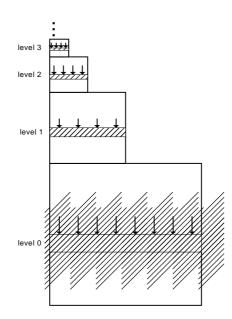

| 3.19. Part of the image allocated in filter memories                                                                                                                                       |

| 3.20. "Burst-free" output timing diagram for the modified structure                                                                                                                        |

| 4.1. Photograph of GEZGİN, the image compression system which is designed as a payload for a LEO micro-satellite, BILSAT-1. (The photograph is provided by the courtesy of TÜBİTAK-BİLTEN) |

| 4.2. Block diagram of the image compression system                                                                                                                                         |

| 4.3. The schematic of the synthesized computation kernel, which implements four 10-bit adders and one 2's complementor                                                                     |

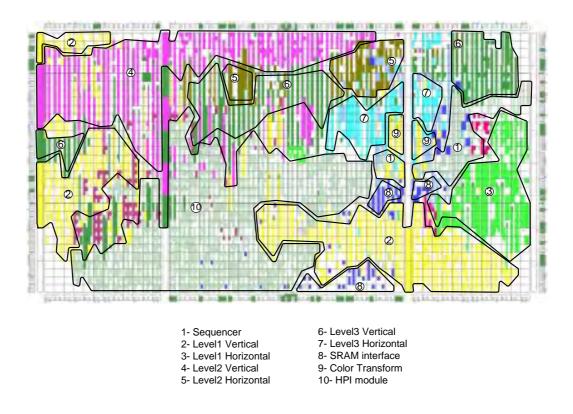

| 4.4. The floorplan of the design. Area consuming modules are contoured and numbered                                                                                                        |

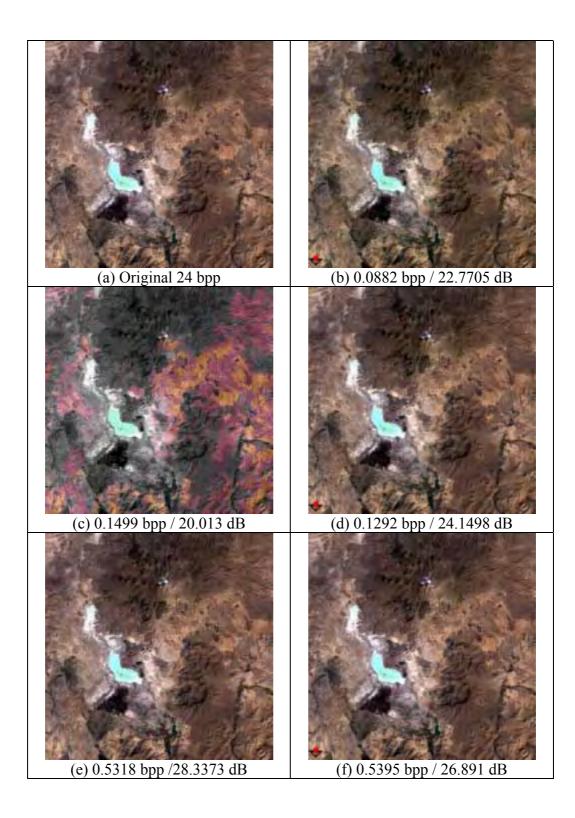

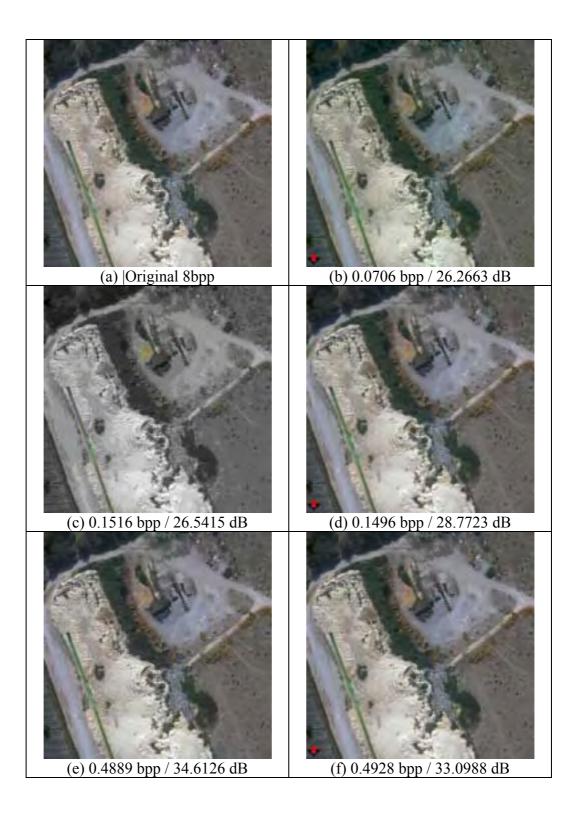

| 4.5. The outputs of conventional JPEG and the outputs of GEZGIN for the original image of ERCIYES 2048×2048 24 bpp RGB. Images on the                                                      |

|       | right hand side are provided from the GEZGIN test bench with the courtesy of TÜBİTAK-BİLTEN                                                                                                                                                                    |     |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

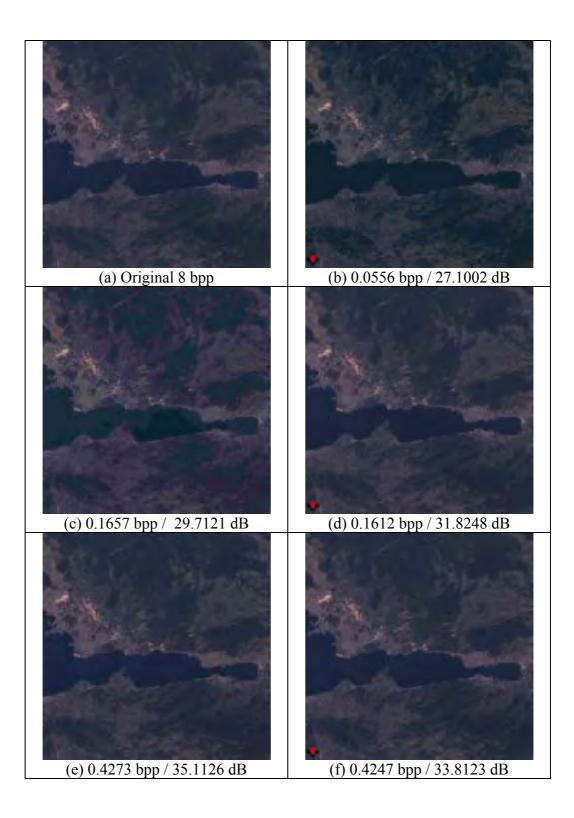

| 4.6.  | The outputs of conventional JPEG and the outputs of GEZGIN for the original image of MERSIN 2048×2048 24 bpp RGB. Images on the right hand side are provided from the GEZGIN test bench with the courtesy of TÜBİTAK-BİLTEN                                    |     |

| 4.7.  | The outputs of conventional JPEG and the outputs of GEZGIN for the original image of GOLCUK 2048×2048 24 bpp RGB. Images on the right hand side are provided from the GEZGIN test bench with the courtesy of TÜBİTAK-BİLTEN                                    |     |

| 4.8.  | Compression ratios achieved for various number of decomposition levels<br>and reconstruction resolutions                                                                                                                                                       |     |

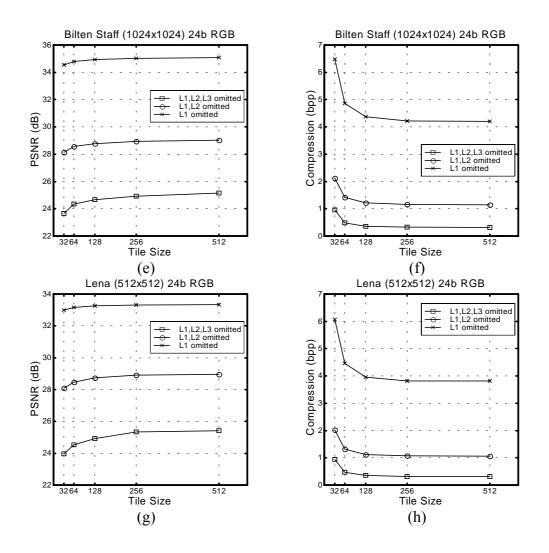

| 4.9.  | PSNR variation with tile size for 3 levels of sub-band decomposition and the corresponding compression achievements                                                                                                                                            |     |

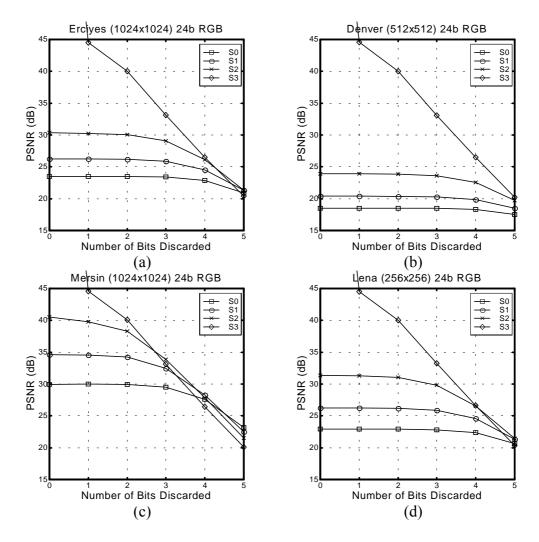

| 4.10. | PSNR versus the number of bits discarded for various cases of sub-band decomposition.                                                                                                                                                                          |     |

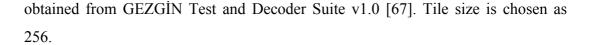

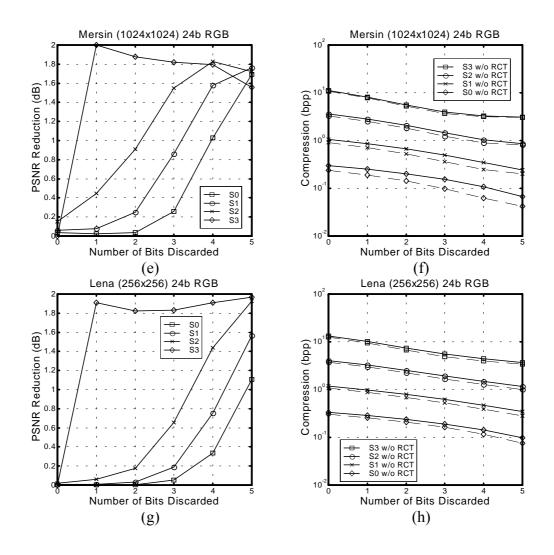

| 4.11. | PSNR reduction introduced due to RCT and the corresponding bit rate achievement for different cases. Tile size is chosen as 256                                                                                                                                |     |

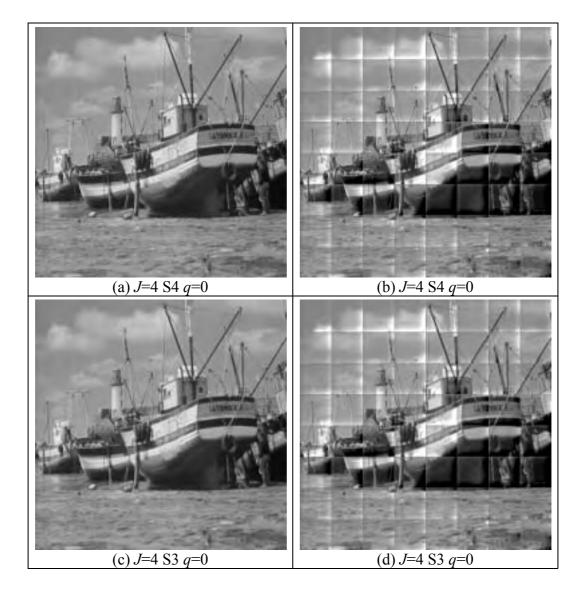

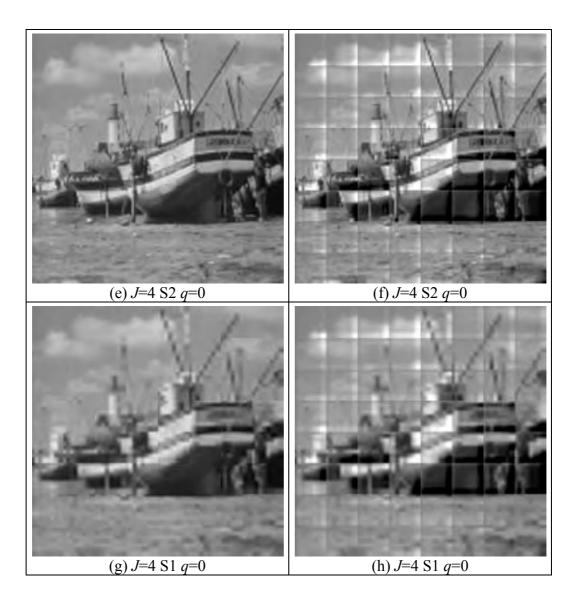

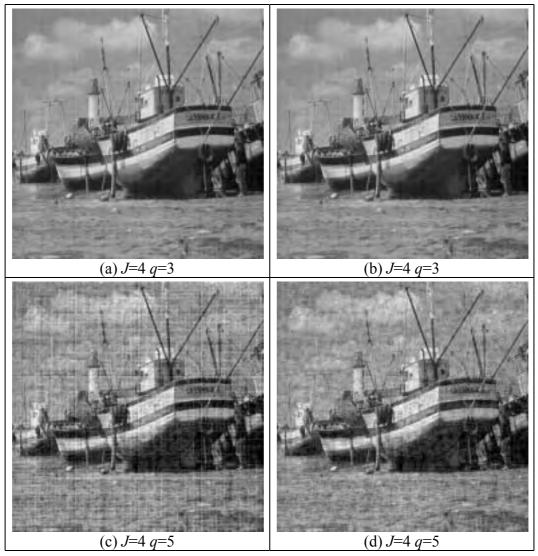

| 4.12. | Effect of tiling to quality degradation. Images on the right side are subjected to zero padding, left side images are filtered using symmetric extension.                                                                                                      | 118 |

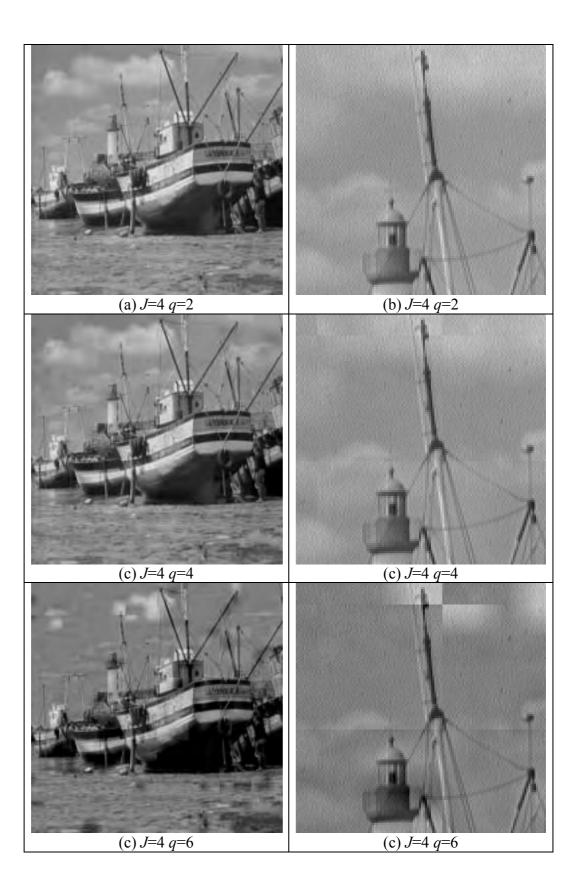

| 4.13. | The effect of quantization of LL sub-band                                                                                                                                                                                                                      | 120 |

| 4.14. | Quantization of the sub-bands. Images on the left are obtained by only truncation in coding and multiplication by $2^q$ in decoding, while images on the right obtained by applying DC adjustment to the truncated coefficients before multiplication by $2^q$ |     |

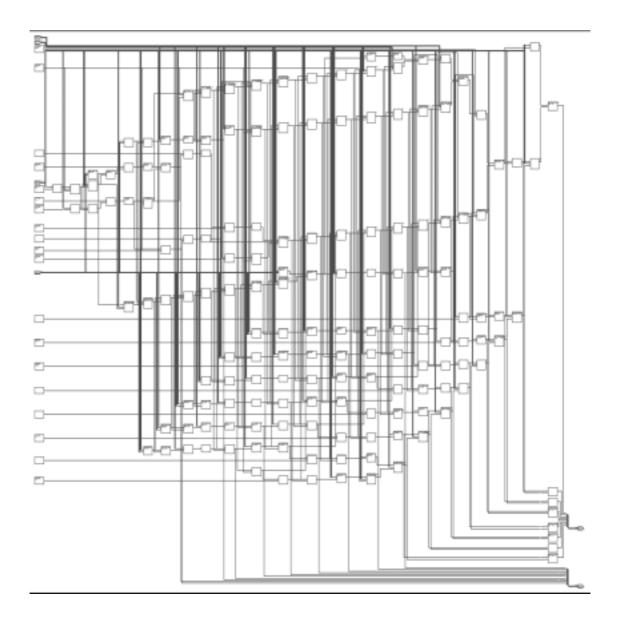

| A.1. | The hierarchical structure of the design                                                     | 136 |

|------|----------------------------------------------------------------------------------------------|-----|

| B.1. | Virtex-E Aarchitecture Overview                                                              | 139 |

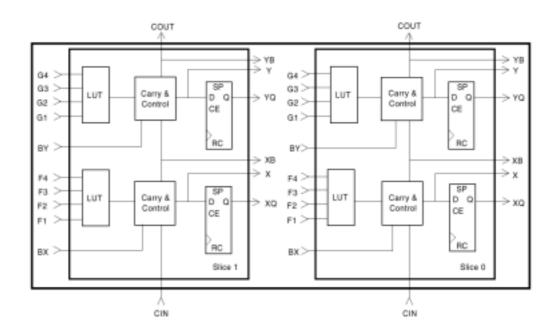

| B.2. | Virtex-E CLB. Each Virtex-E CLB contains four logic cells and CLB is divided into two slices | 141 |

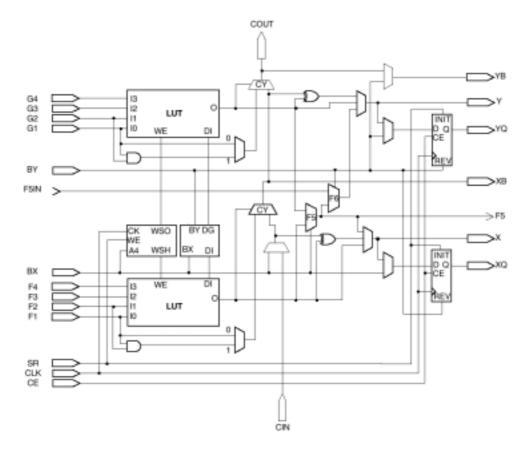

| B.3. | The detailed schematic of a slice. A slice contains two LUTs, two DFFs, and one CY.          | 142 |

| B.4. | Block SelectRAM cell                                                                         | 143 |

| B.5. | Locations of the eight digital delay-locked loops (DLLs) in the device                       | 144 |

| B.6. | Locations of the four global clock buffers (GCLKs) in the device                             | 145 |

# LIST OF ABBREVIATIONS

| 1-D    | One Dimensional                                               |

|--------|---------------------------------------------------------------|

| 2-D    | Two Dimesnional                                               |

| ASIC   | Application Specific Integrated Circuit                       |

| BİLTEN | Bilgi Teknolojileri ve Elektronik Araştırma Enstitüsü         |

| bpp    | Bits per pixel                                                |

| BRAM   | Block Select Random Access Memory                             |

| CCD    | Charge Coupled Device                                         |

| ccs    | Clock Cycles                                                  |

| CLB    | Configurable Logic Block                                      |

| CPU    | Central Processing Unit                                       |

| CY     | Carry Symbol                                                  |

| DC     | Direct Current (Convention for representing constant signals) |

| DCT    | Discrete Cosine Transform                                     |

| DFF    | D Flip-flop                                                   |

| DLL    | Delay Locked Loop                                             |

| DSP    | Digital Signal Processor                                      |

| DWT    | Discrete Wavelet Transform                       |

|--------|--------------------------------------------------|

| EBCOT  | Embedding Block Coding with Optimized Truncation |

| FF     | Flip-Flop                                        |

| FG     | Function Generator                               |

| FPGA   | Field Programmable Gate Array                    |

| GCLK   | Global Clock Buffer                              |

| GEZGİN | Gerçek Zamanlı Görüntü İşleyen                   |

| HPI    | Host Port Interface                              |

| Inf    | Infinity                                         |

| IC     | Integrated Circuit                               |

| ΙΟ     | Input/Output                                     |

| IR     | Infra-red                                        |

| JPEG   | Joint Photograph Experts Group                   |

| KLT    | Karhunen Loeve Transform                         |

| LEO    | Low Earth Orbit                                  |

| LSB    | Least Significant Bit                            |

| LUT    | Look-up Table                                    |

| MAC    | Multiply-and-Accumulate                          |

| MRPA   | Modified Recursive Pyramid Algorithm             |

| MSB    | Most Significan Bit                              |

| MSE    | Mean Square Error                                |

| PE     | Processing Element                               |

|        |                                                  |

| PSNR    | Peak Signal-to-Noise Ratio                  |

|---------|---------------------------------------------|

| QMF     | Quadrature Mirror Filter                    |

| RAM     | Random Access Memory                        |

| RCT     | Reversible Color Transform                  |

| RGB     | Red-Green-Blue                              |

| RPA     | Recursive Pyramid Algorithm                 |

| SIMD    | Single Instruction Multiple Data            |

| SPIHT   | Set Partitioning Hierarchical Trees         |

| SSDR    | Solid State Data Recorder                   |

| SSTL    | Surrey Space Technologies Limited           |

| TCQ     | Trellis Coded Quantization                  |

| TÜBİTAK | Türkiye Bilimsel ve Teknik Araştırma Kurumu |

|         |                                             |

- VLSI Very Large Scale Integrated Circuit

- VQ Vectorial Quantization

### **CHAPTER 1**

#### **INTRODUCTION**

Digital imaging, whether it be professional or recreational, is a common reality today, allowing the capture of images using solid-state devices and image sensor devices instead of traditional film. The basic functioning of a digital camera is by means of recording the incident light through analog-to-digital conversion, thereby creating a digital representation of the image. Digital images have numerous advantages over traditional film images, such as ease of storage, access, transportation and manipulation.

For a digital image to be comparable in quality to an analog image generated through traditional film photography, a considerable amount of digital data should be stored. At 1200 dpi (dots per inch), a 5" by 4" image would translate into a 6000 pixel by 4800 pixel digital image, or 28.8 million pixels total. If each pixel is represented by 24 bits (8 bits for each spectral channel: Red, Green and Blue) this means storing roughly 9.1 Mbytes of digital data. Due to this large storage requirement, in digital imaging equipment, some compression algorithm is generally applied prior to storage.

Image compression algorithms comprise a sequence of treatment to image data such as transform, quantization, coding etc. *Two dimensional discrete wavelet transform*, 2-D DWT, is a powerful one of such transforms used in image compression. This work presents an architecture and an FPGA implementation of the two dimensional discrete wavelet transform for applications where row-based image data is streamed in at high-bandwidths, and local buffering and random accessing the entire image is not feasible. The architecture is especially suited for , but not limited to, multispectral imager systems, such as on board an imaging satellite.

The proposed hardware has been implemented on an FPGA and is part of a JPEG 2000 compression system designed as a payload for a low earth orbit (LEO) microsatellite, which will be launched in September 2003. The fundamental mission of the system is to process (compress) the output of digital imaging sensors in realtime, as the high bandwidth image data is output from the sensors, while storing only a small portion of the incoming image stream at any given time. This work includes the presentation and the report of the optimization of an ASIC co-processor which performs the required tasks before entropy coding in such a system.

This chapter is dedicated to providing introductions to several issues dealt with in this work and is organized as follows: In Section 1.1 a brief introduction to the concept of image compression is given followed by basics in wavelet transform in Section 1.2 and its application in image compression in Section 1.3. In Section 1.4 a method -which constitutes an important reference in this work- used to implement the wavelet transform using a lifting scheme is introduced. Section 1.5 is dedicated to the introduction of the new still image compression standard, JPEG 2000. In Section 1.6 introduces the application of the JPEG 2000 algorithm on-board the imaging satellite BILSAT-1.

In Chapter 2 hardware implementations of the 2-D DWT reported in related literature is presented. Chapter 3 presents in detail the proposed architecture for a 2-D DWT processor in a multi-spectral imaging application environment. Chapter 4 is dedicated to the implementation and simulation results. Chapter 5 summarizes the work done and results obtained, and possibilities of future work is mentioned.

#### **1.1 Image Compression**

An image is represented by a positive scalar function or -as a generalization- a multidimensional vector function of a plane. The value of this function at each point specifies the luminance or brightness of the color components of the picture at that point. Digital images are sampled versions of such functions, where the value of the function is specified only at discrete locations on the image plane, known as *pixels*. Luminance of each pixel is represented in a predefined precision of *B* bits. A typical value for *B* is eight which sufficiently accommodates the dynamic range of the human eye and is suitable for the commonly used computer memory structure since eight bit precision is suitable for existing computer memory structure (1 byte=8 bits).

The prevalent custom is that the samples (pixels) reside on a rectangular lattice of size  $N_1 \times N_2$ . The brightness at each pixel can be any number between 0 and  $2^{B-1}-1$ . The *raw representation* which is the simplest representation of an image is a list of matrix entries which give the brightness value of the corresponding pixel. The storage required for such a list is  $MN_1N_2B$  bits, where M is the number of color components.

In many imaging applications, exact reproduction of the image is not necessary. In this case, one can perturb the image slightly to obtain a shorter representation. If this perturbation is much smaller than the blurring and noise introduced in the formation of the image in the first place, there is no point in using the more accurate representation. Such a coding procedure, where perturbations reduce storage requirements, is known as *lossy* coding. The goal of lossy coding is to reproduce a given image with minimum distortion, given some constraint on the total number of bits in the coded representation.

The underlying reason that digital images can be compressed is the contained redundancy in representation of the images. The example of Nosratinia [1] can be given to illustrate this phenomenon: Suppose that we seek to efficiently store photographs of all natural scenes. In principle, we can enumerate all such pictures

and represent each image by its associated index. Assume we position hypothetical cameras at the vantage point of every atom in the universe (there are roughly  $10^{80}$  of them), and with each of them take pictures in one trillion directions, with one trillion magnifications, exposure settings, and depths of field, and repeat this process one trillion times during each year in the past 10,000 years (once every 0.003 seconds). This will result in a total of  $10^{144}$  images. But  $10^{144} \approx 2^{479}$ , which means that any image in this enormous ensemble can be represented with only 479 bits, or less than 60 bytes. This collection includes any image that a modern human eye has ever seen, including artwork, medical images, and so on, because we include pictures of everything in the universe from essentially every vantage point. And yet the collection can be conceptually represented with a small number of bits. If we assume that images are  $512 \times 512$  and 8-bit, the remaining vast majority of the  $2^{512 \times 512 \times 8} \approx 10^{600,000}$  possible images in the canonical representation are not of general interest because they contain little or no structure, and are noise-like.

The example illustrates the two main properties that image compression algorithms exploit: First, a very small fraction of the possible images that the representation provides are likely to be meaningful. If short code words for likely images and longer codewords for less likely images are used, a much shorter representation of the images can be achieved. This is the fundamental principle of operation of an *Entropy Coder*. Second, in our initial image gathering procedure we assign different representations for images which are visually indistinguishable from the other. Additional reductions in stored image size can be achieved by discretizing our database of images more coarsely. By mapping visually indistinguishable images to the same representation, we reduce the number of code words needed to encode images, at the price of a small amount of distortion.

Discretizing the database of images can be made by means of *quantizing*. Each pixel can be quantized separately, which is known as *scalar quantization*, or a group of pixels can be quantized together, which is called *vector quantization*, VQ. Since each pixel is quantized independent of the others, direct scalar quantization cannot capture the interdependency of the samples, and suffers of distortion at high

compression ratios. In principle, maximum compression that is theoretically possible can be achieved by VQ [1], however VQ reaches optimality only asymptotically as its dimensions increase. Furthermore, computational complexity and delay grow exponentially with the dimension of the VQ. limiting the practicality of VQ. Due to these and other difficulties, most practical image compression algorithms have turned to *transform coding*.

Transform coding consists of scalar quantization applied after a linear transform. This method captures much of the VQ gain, with only a fraction of the effort. Compression is performed in the transform domain. The main purpose of performing a transformation is to make the task of compression easier in the transform domain. Some of the well known transforms applied in transform coding are *the Karhunen-Loéve transform* (KLT), *the discrete cosine transform* (DCT), and *sub-band transforms*.

The success of the transform coding depends on how well the basis functions of the transform represent the features of the signal. A good candidate transformation should be able to offer flexible image representation with decorrelation (to facilitate efficient entropy coding) and good energy compaction in the transform domain (so that fewer quantized coefficients are needed to be encoded and rest can be discarded with minimum distortion). At present, one of the most successful representations is the *wavelet transform*, application of which is a special case of sub-band transform [2]. In Section 1.2 and 1.3 a brief background of the wavelets and applications will be provided. For more background on wavelet theory and wavelet transform one can refer to [3-6].

State-of-the-art wavelet coders such as EZW [7], SPIHT [8], Trellis Coded quantization (TCQ) [9], EBCOT [10] are all derived from the transform coder paradigm. There are three basic components that underlie current wavelet coders: a decorrelating transform, a quantization procedure, and an entropy coding procedure. The next section provides a brief background to wavelets and explain why wavelets are useful for image compression.

#### **1.2 Wavelet Basics**

One of the most commonly used approaches for analyzing a signal f(x) is to represent it as weighted sum of simple building blocks, called *basis* functions [11]:

$$f(x) = \sum_{i} c_i \Psi_i(x) \tag{1.1}$$

where  $\Psi_i(x)$  are basis functions and the  $c_i$  are coefficients, or weights.  $\Psi_i(x)$  are predefined fixed values, and therefore the signal information is contained by the coefficients. If we assume that  $\Psi_i(x)$  are the translates of impulse function, this yields a representation in which coefficients only contain information about the time domain behavior of the signal. As an example for the other extreme, choosing sinusoids as the basis functions yields a Fourier representation that reveals information only about the signal's frequency domain behavior.

For the purpose of signal compression, neither of the representation is ideal. What we would like to have is a representation which contains information about both the time and frequency behavior of the signal. More specifically, a useful transformation should give the frequency content of the signal at a particular instant in time. However, resolution in time ( $\Delta x$ ) and resolution in frequency ( $\Delta \omega$ ) cannot both be made arbitrarily small at the same time because their product is lower bounded by the Heisenberg inequality [6].

$$\Delta x \Delta \omega \ge \frac{1}{2} \tag{1.2}$$

This inequality indicates that a trade off should be done between resolution in time an resolution in frequency. For example it is possible to obtain a good resolution in time if we are satisfied with the low resolution in frequency, and a good resolution in frequency if we are satisfied with the low resolution in time.

For efficient image compression, the aim is to use a transform in which transformed coefficients efficiently contain useful time-frequency information about a signal. By their very nature, low frequency events are spread out (or non-local) in time and high frequency events are concentrated (or localized) in time. This means that if we split the signal's bandwidth in half, and repeat the halving operation on the low-pass portion of the bandwidth, we would have high-pass information analyzed by time-localized (but spread frequency) basis functions, and low-pass information would be analyzed by frequency-localized (but non-local in time) basis functions. Thus, an efficient representation of the signal would be possible.

Suppose that we have the impulse function as the basis function. The impulse function cannot provide information about the frequency behavior of a signal because its support –the interval over which it is non-zero– is infinitesimal. At the opposite extreme are the sinusoids, which cannot provide information about the time behavior of a signal because they have infinite support. Therefore, a compromise should be done between these two extremes: what should be chosen as basis functions,  $\{\Psi_i\}$ , are those having finite support of different widths. The different support widths allow us to trade off time and frequency resolution in different ways; for example, we can analyze large regions of the signal and resolve low frequency details accurately by using wide basis functions, while we can use a short basis function to analyze a small region of the signal to resolve time details accurately.

Basis functions can be chosen as the scaled and translated version of the same prototype function  $\Psi$ , known as the *mother wavelet*. The scaling is an operation in which x is multiplied by a scale factor. If we choose the scale factor to be a power of 2, yielding  $\Psi(2^{v} x)$  where v is some integer, we obtain a set of octave band-pass filters. Since  $\Psi$  has finite support, it will need to be translated along the time axis in order to cover an entire signal. This translation is accomplished by shifting  $\Psi$  in steps of size  $2^{-v}k$ , yielding;

$$\Psi(2^{\nu} x - k), \qquad k \in \mathbb{Z}$$

(1.3)

With the new basis function,  $\Psi_{vk}(x)$ , the *wavelet decomposition of the signal* is represented as :

$$f(x) = \sum_{v} \sum_{k} c_{vk} \Psi_{vk}(x), \qquad (1.4)$$

where

$$\Psi_{vk}(x) = 2^{\frac{v}{2}} \Psi(2^{v} x - k)$$

(1.5)

In order to have an orthonormal set of basis, functions must be multiplied by  $2^{\nu/2}$ . The wavelet coefficients  $c_{\nu k}$  are computed by the *wavelet transform*, which is just the inner product of the signal f(x) with the basis functions  $\Psi_{\nu k}(x)$ :

$$c_{vk} = \left\langle f(x), \Psi_{vk}(x) \right\rangle \tag{1.6}$$

#### 1.2.1 Application of Wavelet Transform in Image Compression

Wavelet-based image coding can be viewed as a form of a sub-band coding. The forward and inverse wavelet transforms can be implemented by a pair of *quadrature mirror filters* (QMFs). Each QMF pair consists of a low-pass filter, H, and a high-pass filter, G which split the input signal's bandwidth in half. The impulse responses of H and G are mirror images, and are related by :

$$g_n = (-1)^{1-n} h_{1-n} \tag{1.7}$$

The impulse response of the forward and inverse transform QMF's are related by :

$$g_n = \hat{g}_{-n} \tag{1.8a}$$

$$h_n = \hat{h}_{-n} \tag{1.8b}$$

Let  $\tilde{g}_n$  and  $\tilde{h}_n$  be the impulse responses of the forward transform and let  $g_n$  and  $h_n$  be the impulse responses of the inverse transform. Note that  $h_n$  is also the mother wavelet function of the orthogonal wavelet transform system.

Output of a filtering operation can be computed by convolving the filter coefficients  $\tilde{h}_k$  with the signal values:

$$\hat{s}_n = \sum_{k=0}^{L-1} \hat{h}_k s_{n-k}$$

(1.9)

where *L* is the number of coefficients, or in other words the *taps* of the filter. The one-dimensional forward wavelet transform of a signal  $s_n$  is performed by convolving  $s_n$  with both  $\tilde{h}_n$  and  $\tilde{g}_n$  and then down-sampling by 2:

$$s_n^{(l)} = \sum_{k=0}^{L-1} \hat{h}_k s_{2n-k}$$

(1.10a)

$$s_n^{(h)} = \sum_{k=0}^{L-1} \hat{g}_k s_{2n-k}$$

(1.10b)

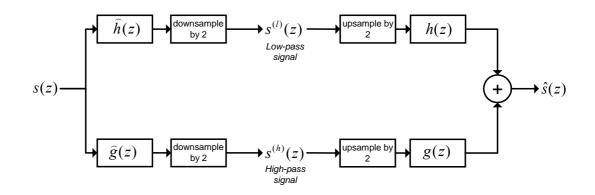

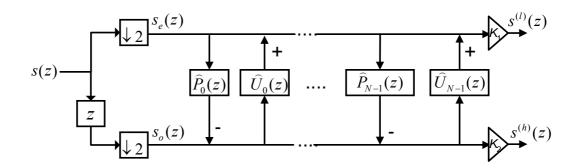

Figure 1.1 shows the one dimensional forward and inverse wavelet transform. The low-pass output of the first stage is filtered for further levels<sup>1</sup>. Figure 1.2 illustrates the two dimensional separable forward wavelet transform for two dimensional signals. Note that throughout this discussion for a 2-D signal f(x,y), x denotes the vertical axis and y denotes the horizontal axis.

<sup>&</sup>lt;sup>1</sup> In literature recursive steps of wavelet transforming is referred to as either *octaves* or *levels*. In this work it is preferred to use the term *level* as in [19].

Figure 1.1 One dimensional forward and inverse wavelet transform. Each QMF pair consists of a low-pass filter, H, and a high-pass filter, G which split the input signal's bandwidth in half.

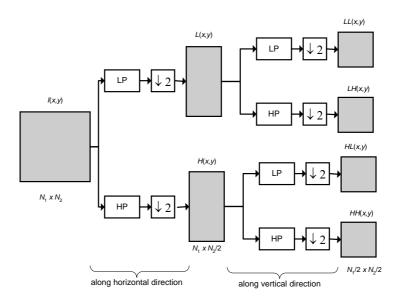

Owed to the separability of the filters, the transform can be performed in two steps each involving one dimensional filtering along different directions. The image I(x,y)is first filtered along the y direction, resulting in a low-pass image and a high-pass image. Since the bandwidth of I along the y direction is split into two, we can safely down-sample each of the filtered images in the y direction by 2 without loss of information and obtain two images L(x,y), and H(x,y). The down-sampling or *decimation* is accomplished by dropping one sample in every two samples. Both L(x,y) and H(x,y) are then filtered along the x direction, and once again we can down-sample the subimages by 2, this time along the x direction resulting four subimages (*sub-bands*) LL(x,y), LH(x,y), HL(x,y), and HH(x,y). As illustrated in Figure 1.2 the 2-D filtering decomposes an image into an *average signal* (LL) and three *detail signals* which are directionally sensitive: LH emphasizes the horizontal image features such as vertical edges and temporal changes along horizontal direction, HL emphasizes the vertical image features, and HH the diagonal features. The sensitivity of the detail signals is a result of the frequency ranges they contain.

Figure 1.2 Two dimensional separable forward wavelet transform

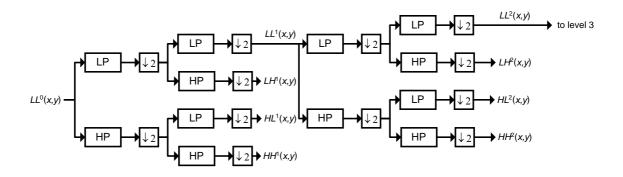

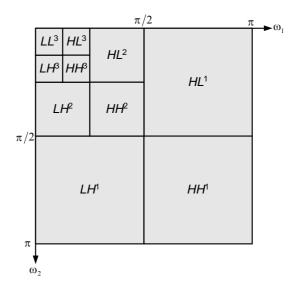

In wavelet compression, the average signal is usually recursively transformed to higher levels as shown in Figure 1.3, the scheme was proposed by Mallat [12]. The wavelet decomposition is also called as *dyadic wavelet transform* or *Mallat tree decomposition*. The pass-band structure of the output signals is illustrated on Figure 1.4 for three levels of wavelet .

Figure 1.3 Dyadic (Mallat Tree) Wavelet Transform. In wavelet compression, the average signal is usually recursively transformed to higher levels.

Figure 1.4 Pass-band structure of Sub-bands for three level wavelet transform

The number of transformations performed depends on several factors, including the amount of compression desired, the size of the original image, and the length of the QMF filters.

After the forward wavelet transform is completed, we have a matrix of coefficients which is equal in size to the original image containing the average signal and the detail signals of each scale. Up to this point we have accomplished no compression, moreover, each iteration of the forward wavelet transform causes the magnitude of the coefficients to grow, so the storage size for the image has actually been increased. Compression is achieved by quantizing and encoding the wavelet coefficients.

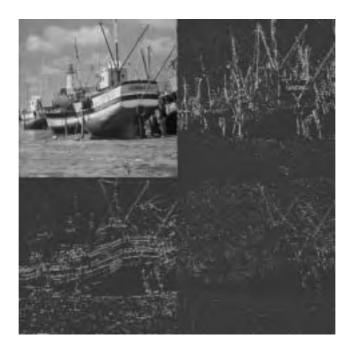

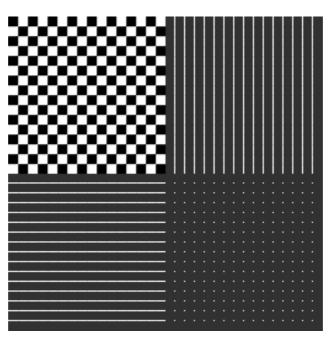

Figure 1.5 shows the wavelet transform of test images. 2.5a is a natural image and 2.5b is a checker board test image. Since the high-pass sub-bands contain samples centered around zero, absolute values of the samples with an offset is used for illustration purposes. Note that the vertical edges and temporal changes along horizontal direction are emphasized in HL sub-band whereas horizontal edges and temporal changes along vertical direction are emphasized in LH sub-band. The LL sub-band contains the coarse information of the image.

(a)

(b)

Figure 1.5 2-D Wavelet Transform outputs: (a) A natural image, (b) A checkerboard test pattern. The vertical edges and temporal changes along horizontal direction are emphasized in HL sub-band, whereas horizontal edges and temporal changes along vertical direction are emphasized in LH sub-band. The LL sub-band, the average signal, contains the coarse information of the image.

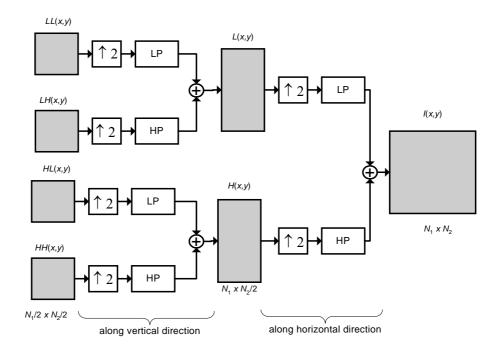

Reconstruction of the original image is by the 2-D inverse wavelet transform which is illustrated in Figure 1.6. The sub-bands are first up-sampled by 2 along the vertical axis (along x) and filtered along vertical axis with the corresponding inverse filters. LL and LH sub-bands are summed up to obtain sub-image L while HL and HH sub-bands are summed up to obtain sub-image H. Then the two sub-images are up-sampled along the horizontal axis (along y) and filtered with the corresponding inverse filters. Finally the outputs are summed up to obtain the reconstructed image, or the LL sub-band for the next iteration.

Figure 1.6 Two dimensional inverse wavelet transform

## 1.2.2 Factoring Wavelet Transforms into Lifting Steps

In this section a brief explanation of the lifting concept and how a QMF filter bank implementation of wavelet transform is factorized into lifting steps is given. More rigorous mathematical analysis of the subject can be found in [13-15].

Lifting factorization of a filter bank involves the *polyphase representation* of filter kernels. The polyphase representation of analysis filters  $\hat{h}$  and  $\hat{g}$  is given by :

$$\hat{h}(z) = \hat{h}_e(z^2) + z^{-1}\hat{h}_o(z^2)$$

(1.11a)

$$\hat{g}(z) = \hat{g}_e(z^2) + z^{-1}\hat{g}_o(z^2)$$

(1.11b)

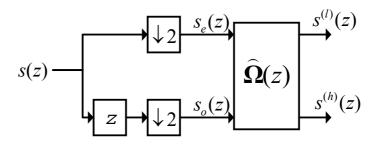

where  $\hat{h}_e$  and  $\hat{g}_e$  contain the even coefficients, and  $\hat{h}_o$  and  $\hat{g}_o$  contain the odd coefficients. The wavelet transform of Figure 1.1 can be represented in polyphase form as illustrated in Figure 1.7. The input signal *s* is first split into even and odd parts, then the *polyphase matrix* is applied to the signals. In the inverse path, first polyphase matrix is applied and then the even and odd signals are joined properly. Polyphase matrix is given as:

$$\widehat{\mathbf{\Omega}}(z) = \begin{bmatrix} \widehat{h}_e(z) & \widehat{g}_e(z) \\ \widehat{h}_o(z) & \widehat{g}_o(z) \end{bmatrix}$$

(1.12)

and the outputs of the transform are expressed as :

$$\left[s^{(l)}(z) \ s^{(h)}(z)\right] = \left[s_{e}(z) \ s_{o}(z)\right] \cdot \widehat{\Omega}(z)$$

(1.13)

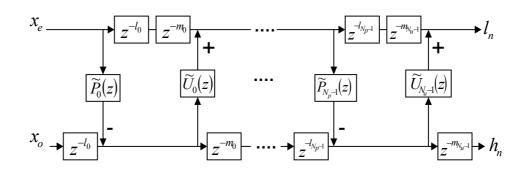

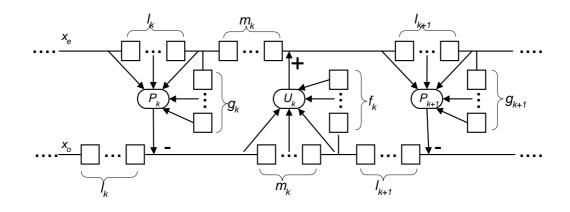

Figure 1.7 Polyphase representation of wavelet transform. The input signal *s* is first split into even and odd parts, then the *polyphase matrix* is applied to the signals.

The polyphase matrix can be factorized into several triangular matrices by *Euclidian algorithm* as follows:

$$\widehat{\mathbf{\Omega}}(z) = \left(\prod_{k=0}^{N-1} \begin{bmatrix} 1 & -\widehat{P}_k(z) \\ 0 & 1 \end{bmatrix} \cdot \begin{bmatrix} 1 & 0 \\ \widehat{U}_k(z) & 1 \end{bmatrix} \right) \cdot \begin{bmatrix} K_1 & 0 \\ 0 & K_2 \end{bmatrix}$$

(1.14)

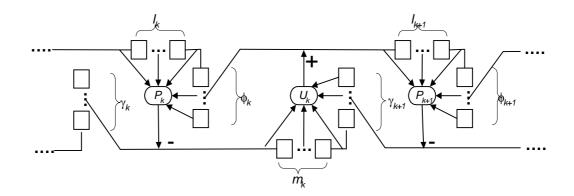

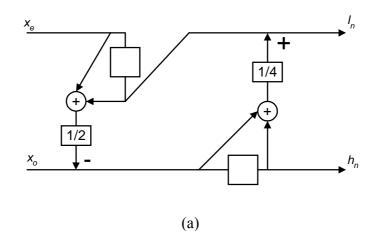

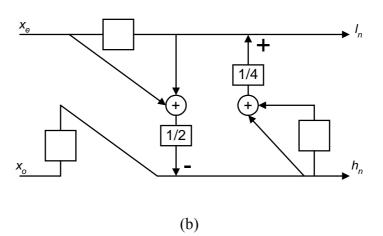

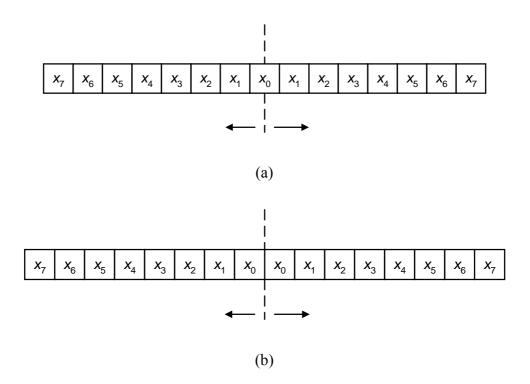

where  $\hat{P}_k(z)$  and  $\hat{U}_k(z)$  are called *prediction* and *update* filters of the lifting steps implementation of wavelet transform, which is illustrated in Figure 1.8. First the low-pass samples (even terms) are filtered by prediction filters,  $\hat{P}_k(z)$ , and are subtracted from the high-pass samples (odd terms) to obtain a "detail" signal. Then, the detail samples are filtered by the update filters,  $\hat{U}_k(z)$  and the low-pass samples are "updated" by adding the update filter outputs. This constitutes a single "lifting step" of the scheme. This lifting procedure is repeated as many times as the number of lifting steps *N*.

Figure 1.8 Lifting steps implementation of wavelet transform

The advantageous of lifting can be listed as follows:

- It is easier to build non-linear wavelet transforms by using lifting. A typical example for non-linear transforms are the transforms that map integers to integers [15]. Such transforms are important for hardware implementations and for lossless image coding.

- 2. Every transform built with lifting is immediately invertible where the inverse transform has exactly the same computational complexity as the forward transform.

- 3. Lifting exposes the parallelism inherent in a wavelet transform. All operations within one lifting step can be done entirely parallel while the only sequential part is the order of the lifting operations.

- 4. Lifting involves poly-phase filtering which provides two channel input feeding, thus the clock cycle required to implement wavelet transform can be reduced.

## 1.3 A New Image Compression Standard : JPEG 2000

JPEG 2000 is an upcoming image compression standard published by the committee of JPEG, Joint Photographic Experts Group to serve the needs of current and future applications that uses still image coding. The committee's first published standard JPEG is a simple and efficient discrete cosine transform (DCT) based lossy compression algorithm that uses Huffman Coding and is restricted to 8 bits/pixel. Though various extensions has appeared to JPEG to provide broader applicability and lossless compression, these extensions introduced only limited capability and faced with the intellectual copyright properties. Since 1996, various image compression algorithms were proposed and evaluated for the new image compression standard, and the one that was published at the end of 2000 by ISO (ISO I5444 | ITU-T Recommendation T.800) has been adopted as the new comprehensive still image compression standard, JPEG2000.

JPEG 2000 has many features, some of which are [16]

- Superior, Low bit-rate compression performance

- Progressive transmission by quality, resolution, component, or spatial locality

- Multiple resolution representation of still images

- Lossy and lossless compression

- Multispectral Image Support

- Random access to bit stream

- Pan and zoom (with decompression of only a subset of the compressed data)

- Compressed domain processing (eg. rotation and cropping)

- Region of interest coding

- More flexible file format

- Limited memory implementations

- Error Resilience

#### 1.3.1 JPEG 2000 Coding Algorithm

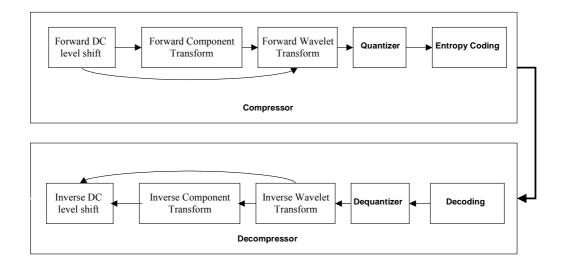

In this section the JPEG 2000 algorithm is described. Figure 1.9 shows the block diagram of the JPEG 2000 coding algorithm. Comparative results are provided in [17-18].

Figure 1.9 Block diagram of JPEG 2000 coding algorithm

The input image is first DC-level shifted, and then component transform is applied. For images having multiple color components, a point-wise decorrelating transform may be applied across the components. However this transform is optional. The standard Part I [19] defines 2 component transforms. These are : 1) the YCrCb transform commonly used in image compression systems and color format exchangers, and 2) the Reversible Component Transform (RCT) which provides similar decorrelation, but allows for lossless reconstruction of color components. Both color transforms are applied to first three components of the image data and the remaining components, if exist, are left unchanged. After the component transform, the image components are treated independently.

A color component can be processed in arbitrary sized non-overlapping rectangular blocks called *tiles* or the entire color component can be processed at a time (i.e. no tiles).

Given a tile, a *J*-level dyadic 2-D wavelet transform is applied. JPEG-2000 Part I offers two filtering methods which differ in filter kernels: Wavelet transform can be performed using either (9,7) filter, floating point wavelet [20], or (5,3) filter, integer wavelet [15]. For lossless compression (5,3) filter must be used. For a *J*-level transformation; from the lowest frequency sub-band (which is denoted in this work by S0), up to the *J*th resolution (which is denoted by S(*J*)), there are J+1 possible resolutions to reconstruct an image.

After wavelet transformation, uniform scalar quantization is applied to all sub-band coefficients. Uniform quantization involves a fixed dead-zone around zero. This corresponds to magnitude division and magnitude flooring. Further quantization can be applied during coding process by truncation of coefficients, thus rate control is achieved. For integer transform quantization step size is essentially –but not necessarily- 1, which means there is no pre-coding quantization, however rate control is achieved by truncation of coefficients as in floating-point transform.

After quantization each sub-band is subjected to *packet partition*, where each subband is divided into regular non-overlapping rectangles. After this step, *code-blocks* are obtained by dividing each packet partition location into regular non-overlapping rectangles. The code-blocks are the fundamental entities for the purpose of entropy coding.

Entropy coding is performed on each code-block independently. A context dependent, binary arithmetic coding is applied to bit planes of code-blocks. Algorithm employs the MQ-Coder which is defined in JBIG-2 standard [21] with some minor modifications.

## 1.4 GEZGIN: A JPEG 2000 Compression Sub-system On-board BILSAT-1

BİLSAT-1 [22] [68] is a 100kg class, low earth orbit (LEO), micro-satellite being constructed in accordance with a technology transfer agreement between TÜBİTAK-BİLTEN (Turkey) and SSTL (UK) and planned to be placed into a 650 km sun-synchronous orbit in Fall 2003. One of the missions of BİLSAT-1 is constructing a Digital Elevation Model of Turkey using both multi-spectral and panchromatic imagers. Due to limited down-link bandwidth and on-board storage capacity, employment of a real-time image compression scheme is highly advantageous for the mission.

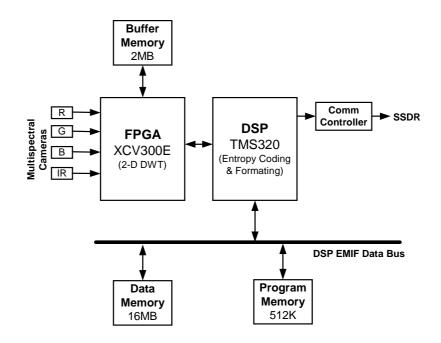

Prof. Dr. Murat Aşkar has initiated resource and development projects which lead to the development of payloads for small satellites [68], one of which was planned to be an image processing subsystem while the other is a multi-spectral camera, COBAN. GEZGIN [23] is a real-time image processing subsystem, developed for BILSAT-1. GEZGIN is one of the two R&D payloads hosted on BILSAT-1 in addition to the two primary imager payloads (a 4 band multi-spectral 26m GSD imager and a 12m GSD panchromatic imager). GEZGIN processes 4 images in parallel, each representing a spectral band (Red, Green, Blue and near Infra-Red) and captured by  $2048 \times 2048$  CCD array type image sensors. Each image pixel is represented by 8-bits. The imaging mission of BILSAT-1 imposes a 5.5 seconds interval for real-time image processing between two consecutive multi-spectral images with 20% overlap in a  $57 \times 57 \text{km}^2$  swat. The image processing consists of streaming in the image data, compressing it with the JPEG2000 algorithm and forwarding the compressed multi-spectral image frames as a single stream to the Solid State Data Recorders (SSDR) of BILSAT-1 for storage and down-link transmission. Compression of image data in real-time is critical in micro-satellites in general, where the down-link and on-board storage capacity are limited. GEZGİN achieves concurrent compression of large multi-spectral images by employing a high degree of parallelism among image processing units.